# occam user group · newsletter

# for all users of occam and the transputer

| Nº 12 | January 1990 |

|-------|--------------|

|-------|--------------|

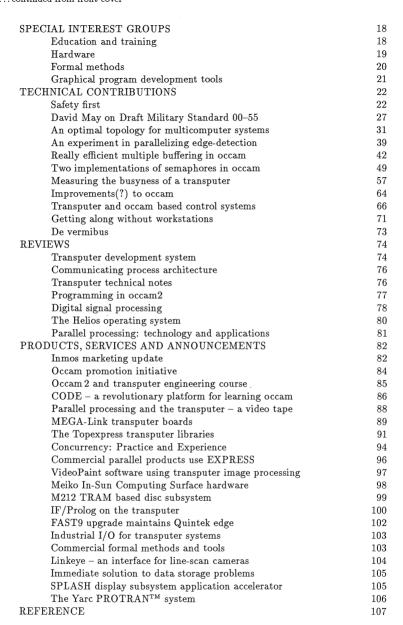

# Contents

| EDITORIAL                                                | 2  |

|----------------------------------------------------------|----|

| Contributions to the newsletter                          |    |

| Occam user group publications                            |    |

| North American transputer users group publications       | 4  |

| FORTHCOMING                                              | 4  |

| Twelfth occam user group technical meeting               | 4  |

| North American transputer users group spring meeting     | 5  |

| Third Japanese transputer/occam international conference | 5  |

| Thirteenth occam user group technical meeting            | 6  |

| North American transputer users group fall meeting       |    |

| Transputing 1991                                         | 7  |

| REPORTS                                                  | 9  |

| Inaugural meeting of the occam user group: Latin America | 9  |

| Eleventh occam user group technical meeting              | 10 |

| Why did the transputer cross The Pond?                   | 14 |

| Second seminar of the Swedish transputer user group      | 15 |

continued on back cover

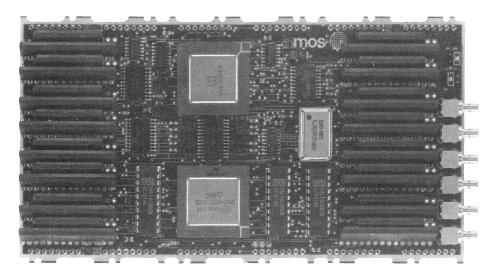

Meiko In-Sun Computing Surface Hardware (see page 98)

occam is a trade mark of the INMOS Group of Companies

# **EDITORIAL**

New groups seem to be springing up all around the world; this issue of the newsletter carries contact addresses for the first time for groups in Sweden and Latin America. We have contributions from as far afield as Brazil, the Basque country, and Bristol. It is all here: from exotic hardware (see for example pages 19, 82, 98 and many of the product announcements) to expressions of concern that software should be as unexciting as possible (see pages 22, 27). I would particularly like to draw your attention to the initiative to promote the occam language (see page 84); and to the CODE system from C-DAC (see pages 86 and 18), an impromptu presentation of which stole the show in the exhibition at the OUG technical meeting in Edinburgh.

For me, perhaps the most noticeable impact that SGS-Thomson have had on Inmos is in the way they are taking their marketing more seriously. Regulars were as astonished as I was, I am sure, to see an Inmos stand at the exhibition in Edinburgh with the company's name on it! I believe that Inmos were also one of the sponsors of the distressingly well-lubricated banquet at that meeting. (A bibulous colleague seated near your most temperate correspondent reports that the sight of full or almost-full bottles of wine being carried away from the tables is always distressing.)

Speaking at the panel session in the Edinburgh meeting, David May was able to confirm exactly one thing about the much-rumoured next-generation transputer. He was happy to dispel any doubt that its code name really is 'H1'. (Later in the bar sources close to Inmos told me a most unlikely tale to explain the name, something about the actor Nigel Hawthorne, and his character Sir Humphrey Appleby.) He was less forthcoming on specifications, although Inmos have made some public hints about the sort of specification at which they are aiming (see page 83). I note that the device is expected in early 1991; could it just be a coincidence that the international joint meeting of user groups (see page 7) is planned for the end of April 1991?

When I first drafted these notes, one of the things I was going to say was that we seem to be getting an increasing number of commercial contributions at occam user group technical meetings. This, I was going to say, is sure sign that there is a growing base of applications out there to report. The Edinburgh meeting, however, turned out to be rather short of papers from the industry – although there were a creditable number of commercial exhibitors. I remain convinced about the strength of the application base, and so am disappointed that we are not seeing enough of the work reported. Let me therefore take this opportunity to encourage readers in the industry to send papers to the OUG technical meetings, and those of its sister organisations of course. Needless to say, the same applies to contributions to this newsletter.

Please forgive me a personal note: I keep being mistaken for the Geraint Jones who works for the National Transputer Centre in Sheffield. I have even been congratulated on moving to a new job there. I trust, Geraint, that if you are ever mistaken for me you are at least as flattered by the mistake. Ladies and gentlemen! it is a common name, but we are two, as far as I know unrelated, and in no way responsible for each other's commissions or omissions.

#### CONTRIBUTIONS TO THE NEWSLETTER

Please contribute announcements, articles, letters about anything that looks as though it belongs in your newsletter. In particular we welcome letters, short articles or news about work being done with occam or transputers; calls for, discussion of, and reports on meetings of the group or related societies; ideas for new ways the group could help its members, or better ways of organizing what we do; details of material published elsewhere in books and journals; information about new products and courses.

Life would be easiest for the editor if you were able to submit material of longer contributions by electronic mail to oug-newsQuk.ac.oxford.prg; or to send either unformatted ASCII files (on an IBM PC compatible floppy disk, or some other medium by negotiation) or clean camera-ready copy to the editor at the address below. Camera-ready copy should be arranged not to look out of place when its linear dimensions are reduced to about 70%, i.e. from A4 to A5.

Pictures are welcome as black-and-white prints, and will be subjected to the same reduction in size. We particularly need shorter and shorter pictures to fill the rapidly closing gap at the bottom of the front page!

# Copy for the next edition must arrive by 25th May 1990.

Geraint Jones Programming Research Group 11 Keble Road Oxford OX1 3QD United Kingdom

Tel: +44 865 273851 Fax: +44 865 273839

Fax: +31 20 22 60 55

oug-news@uk.ac.oxford.prg

#### OCCAM USER GROUP PUBLICATIONS

Occam user group technical meetings are held twice a year. The proceedings of all the recent meetings are published by International Organisations Services BV and are available directly from the publisher.

- ▷ OUG-7, 14-16 September 1987, Grenoble, Parallel programming of transputer based machines, ed. Traian Muntean (pp. 480, \$110.00).

- DUG-8, 27-29 March 1988, Sheffield, Developments using occam, ed. Jon Kerridge (pp. 214, \$50.00).

- ▷ OUG-9, 19-21 September 1988, Southampton, Occam and the transputer research and applications, ed. Charlie Askew (pp. 176, \$50.00).

- ▷ OUG-10, 3-5 April 1989, Enschede, Applying transputer based parallel machines, ed. André Bakkers (pp. 318, \$65.00).

- ▷ OUG-11, 25-26 September 1989, Edinburgh, Developing transputer applications, ed. John Wexler (pp. 206, \$55.00).

IOS Van Diemenstraat 94 1013 CN, Amsterdam The Netherlands

or in the USA and Canada IOS PO Box 2848 Springfield VA, 22152-2848 United States of America

Fax: +1 703 250 47 05

or in Japan

IOS Japan Department

Highway Development Co. Ltd

1st Golden Building, 8-2-9 Ginza

104 Tokyo - Chuoku

Japan

Fax: +81 35 72 86 72

# NORTH AMERICAN TRANSPUTER USERS GROUP PUBLICATIONS

The proceedings of the first two conferences of the North American Transputer Users Group can be obtained by sending a cheque, money order or purchase order to NATUG at the address below.

- b The proceedings of NATUG 2 consist of thirty-one papers, 451 pages in all, for \$40.00.

- ▶ There are still a few copies of the NATUG 1 proceedings available; the price is \$30.00, for 209 pages including full colour illustrations.

When copies of these two proceedings are depleted, IOS will take over the reprinting and sales.

NATUG

C/O G. S. Stiles

Department of Electrical Engineering

Utah State University

Logan, Utah 84322-4120

United States of America

# FORTHCOMING

### TWELFTH OCCAM USER GROUP TECHNICAL MEETING Monday to Wednesday, 2–4 April 1990, University of Exeter, England

The Occam User Group invites all those interested in the programming and application of transputer based architectures to attend its twelfth Technical Meeting at the University of Exeter. The conference includes lectures, an exhibition, a panel session with key speakers, and meetings of the Special Interest Groups. The emphasis of the conference is on the techniques and tools that allow transputers to be used effectively.

The meeting and exhibition will take place in Streatham Court and accommodation will be provided on campus in the Duryard Halls of Residence. The University is situated one mile from the centre of Exeter and its attractive site enjoys fine views over the Exe Estuary and Dartmoor Hills. A conference dinner will take place on Tuesday 3rd April.

All enquiries should be made to the Conference Organiser:

Dr Stephen J. Turner

Fax: +44 392-264067

Department of Computer Science

University of Exeter

Telex: 42894 EXUNIV G

Prince of Wales Road

Steve@uk.ac.exeter.cs

Exeter EX4 4PT

England

# NORTH AMERICAN TRANSPUTER USERS GROUP SPRING MEETING

26-27 April 1990, Santa Clara, California

The 1990 Spring meeting of the North American transputer users group will be held in Santa Clara, California, on 26th and 27th April. Contributions are being solicited in the areas of hardware, software, and applications – particularly embedded and real-time systems. Presentations will be allotted twenty minutes each, with ample additional time for questions; this format will allow for approximately twenty-four talks. Additional papers may be presented at poster sessions if there is sufficient interest. All accepted papers will appear in a published proceedings.

Abstracts of 1000–1500 words must be received by 8th January 1990. Notices of acceptance will be sent out by 22th January, and final drafts of accepted papers will be due by 19th February. Authors should indicate on the abstract whether they would be willing to present the paper in a poster session.

Abstracts – electronic mail submissions are preferred – should be submitted to:

Professor Alan Wagner, NATUG 3 Program Chair wagner@cs.ubc.cdn

Department of Computer Science Tel: +1 604 228-6450

University of British Columbia

Vancouver, BC Canada V6T 1W5

# THIRD TRANSPUTER/OCCAM INTERNATIONAL CONFERENCE

organised by the occam user group Japan 17–18 May 1990, Tokyo, Japan

OUG Japan is pleased to announce the third transputer/occam international conference to be held on 17–18 May 1990 in Tokyo. This is a place to find wide varieties of transputer based parallel processing systems through original refereed papers, invited talks, tutorials and commercial exhibits. The official language of the conference is English. Simultaneous translation from English to Japanese is provided whenever necessary. The registration fee is  $\$20\,000$  and this includes:

- ▶ admission to all technical sessions, tutorials and exhibits,

- ▶ admission to all lunches,

- ▶ admission to the final party.

The conference organizing committee consists of:

Prof. Dr Tosiyasu L. Kunii (Chairman), University of Tokyo;

Prof. Dr Tadao Nakamura, Tohoku University;

Prof. Dr Eiichi Miyamoto, Hokkaido University;

Prof. Dr Shinji Tomita, Kyushu University;

Associate Prof. Dr Mitsuru Ishizuka, University of Tokyo;

Research Associate Dr Shigeki Sugano, Waseda University.

# Call for papers

Full papers in English are solicited and should contain previously unpublished original high-quality results. The submitted paper should be typed, double spaced, about 10-20 pages in length with an abstract of 100-200 words and a maximum of ten keywords. All papers will be peer reviewed and will be published for distribution at the conference and also for later dissemination. Papers must be submitted by 1st January 1990. Acceptance or rejection of the papers will be notified by 1st February 1990. Final camera-ready copy must be provided by 1st April 1990.

For more information, contact:

Mr Kazuto Matsui (Secretary, OUG Japan) Technical Marketing, Inmos Division SGS-Thomson Microelectronics K.K. 4F Nisseki-Takanawa Building 2-18-10 Takanawa Minato-ku Tokyo 108

Japan

Tel: +81 3 280-4125

Fax: +81 3 280-4131

#### THIRTEENTH OCCAM USER GROUP TECHNICAL MEETING 18-20 September 1990, York, England

Advance notice is given of the thirteenth technical meeting of the occam user group, which will take place at the University of York from 18th to user group, which will be provisional deadline for extended abstracts of papers is 4th May 1990. For further information about this meeting contact:

Dr Hussein Zedan Department of Computer Science University of York

Heslington YorkYO1 5DD England

Tel: +44 904 432744 Fax: +44 904 432767 zedan@uk.ac.vork.minster

# NORTH AMERICAN TRANSPUTER USERS GROUP FALL MEETING

12-13 October 1990, Ithaca, New York

Advance notice is given of the fourth meeting of the North American transputer users group which is to be held at Cornell University, New York.

#### TRANSPUTING 1991

First world conference of national occam and transputer user groups 22-26 April 1991, Santa Clara, California

#### Advance announcement

The first world conference of all occam and/or transputer user groups is planned:

| TRANSPUTING 1991 |                                 |

|------------------|---------------------------------|

|                  | Santa Clara, California         |

| Dates:           | week commencing 22nd April 1991 |

The goals of this conference are:

- ▶ to present 'state-of-the-art' research on all aspects of parallel computing based upon communicating process architectures;

- ▶ to demonstrate 'state-of-the-art' products and applications from as wide a range of fields as possible;

- ▶ to progress the establishment of international software and hardware standards for parallel computing systems;

- ▶ to provide a forum for the free exchange of ideas, criticism and information from a world audience gathered from Industry, Commerce and Academia;

- ▶ to establish and encourage an understanding of the new software and hardware technologies enabled by the transputer;

- ▶ to promote an awareness of how these technologies may be applied and what their advantages are.

The conference themes will *include*: education and training issues, formal methods and security, performance and scalability, porting existing systems, parallelisation paradigms, tools, programming languages, support environments, standards and applications.

Applications *include*: embedded real-time control systems, workstations, supercomputing, consumer products, artificial intelligence, databases, modelling, design, data gathering and the testing of scientific or mathematical theories.

The conference programme will contain invited papers from established international authorities in these fields together with submitted papers. All papers will be fully refereed by an international programme committee. Only papers of high excellence will be accepted. The proceedings of this conference will be published internationally and copies will be given to delegates when they register at the start of the meeting.

# Programme committee

The members of the programme committee will be invited experts from Industry and Academia together with existing committee members from the joint organising user-groups based in Australia, France, Germany, India, Japan, Latin America, New Zealand, North America, Sweden, and the United Kingdom.

The aim is to spread the organising load around the world, to ensure that all points of view and expertise are properly represented and to obtain the highest standards of excellence. We shall be seeking endorsements from professional institutions

on all five continents, as well as sponsorship from commercial and governmental organisations.

#### Provisional conference structure

```

PAR

... exhibition / demonstrations (Monday .. Friday)

SEQ

... seminars / workshop (Monday)

... conference papers (Tuesday .. Thursday)

... seminars / workshop (Friday)

```

#### Provisional timetable

| February 1990   | Official publicity and first call for papers, exhibitors and delegates. |

|-----------------|-------------------------------------------------------------------------|

| 1st August 1990 | Deadline for submitted papers.                                          |

$1st\ October\ 1990\$  Notification of acceptance to authors; launch final call for exhibitors and delegates.

6th January 1991 Receive revised camera-ready copy of papers.

22nd April 1991 TRANSPUTING 1991.

# Impact on existing OUG/TUG meetings

The OUG and NATUG will not organise meetings at Easter 1991. Transputing 1991 will subsume the OUG and NATUG meetings normally scheduled for this time.

# Competition

Find a suitable name for the parent organisation for all our existing user groups. You have to do better than

- ▶ WOTUG (the World Occam and Transputer Groups);

- $\,\,\vartriangleright\,$  ATM (the Association for Transputing Machinery).

Also, find a better name for *Transputing 1991*. Prizes are unspecified for now, but will be up to the usual OUG standards. Entries should be sent to the editor of this newsletter.

#### Further information

Companies and other organisation wishing to be associated with *Transputing 1991* should contact the chairman or secretary of their local user group. We also welcome offers of help from individuals with special skills.

Further details will be announced in line with the provisional timetable above. In case of difficulties, please contact Peter Welch (OUG Chairman) or Dyke Stiles (NATUG Chairman).

\*\*Peter Welch\*\*

# REPORTS

# INAUGURAL MEETING OF THE OCCAM USER GROUP: LATIN AMERICA

14-16 September 1989, Florianópolis, Santa Catarina, Brazil Rafael D. Lins, Universidade Federal de Pernambuco

### Invited speakers

MICHEL GIEN, CHORUS SYSTEMES, FRANCE. Michel presented an inspiring overview of distributed operating systems, including a description of the Chorus system applied to various hardware configurations.

S. VEDAT DEMIRALP, UNIVERSITY OF KENT, CANTERBURY, UK. Vedat conducted a two-day tutorial on occam and transputer programming. Demonstrations of occam and C running on a transputer system were included.

DENIS NICOLE, UNIVERSITY OF SOUTHAMPTON, UK. Denis described recent and future MIMD parallel computing architectures including the Esprit P1085 Supernode, the Esprit Genesis project and the just-initiated Puma project to build a 'universal message-passing architecture' in collaboration with Inmos and others,

# Local speakers

CLAUDIO AMORIM, COPPE/UFRJ, RIO DE JANEIRO, RJ. Work at Rio on using occam for numerical analysis was described, including an implementation of a translator from Actus to occam.

CLÉSIO TOZZI, UNICAMP, CAMPINAS – SP. The use of occam and transputers for image recognition and in industrial applications was outlined.

ANTONIO CAROLS RUGGIERO, UNIVERSIDADE SÃO CARLOS, SÃO CARLOS – SP. The proposed use of transputers to implement a dataflow machine and an NMR tomographer was described. The solution of the molecular dynamics problem using transputers was also addressed.

N. Furuya, Unicamp, Campinas – SP . Experience in using parallel C on transputers for the analysis of numerical algorithms was described.

RAFAEL LINS, UNIVERSIDADE FEDERAL DE PERNAMBUCO, RECIFE. Work at Recife on processors for interval arithmetic, on NMR tomography, and on functional language implementations was described.

#### Discussions

All present expressed enthusiasm for the formation of an occam user group in Latin America. Attendees at the meeting included academics from Argentina, Brazil,

and Chile. Hope was expressed that the OUG:LA would help facilitate access to transputer hardware and software in South America.

The next meeting is planned for May 1990 in Petropolis, Rio de Janeiro and it is hoped that members of the group will be able to attend the proposed 'Transputing 1991' in the United States.

### Acknowledgements

The meeting was sponsored by Institutio de Engenharia de Software da Brasil, CNPq, UFPE, Unicamp, UFCS, Projeto Ethos and the British Council, for whose support the participants are deeply grateful. Particular thanks are owed to Prof. E. Tadao Takahashi of Projeto Ethos and Antonio Carols Lariani from IBM Brasil.

#### Contact

For any further information please contact Rafael Lins, who has agreed to act as chairman of OUG:LA, at:

Rafael D. Lins Av. Dr José Rufino 656 Estância 50.781 - Recife - PE Brazil

### Tel: +55 81 251 0713 Fax: +55 81 326 4880

### ELEVENTH OCCAM USER GROUP TECHNICAL MEETING

Monday and Tuesday 25-26 September 1989 University of Edinburgh, Scotland Nigel J. Anderson, University of Edinburgh

transputer.

This meeting, which was held in Edinburgh on the 25th and 26th of September this year, went under the title of Developing transputer applications. The conference was held in the Appleton Tower, part of the campus of the University of Edinburgh, and immediately preceded the Edinburgh Concurrent Supercomputer Project's annual seminar. The site allowed for exhibitions by a number of commercial organisations with interests in parallel processing and the

# The papers

There was a very full program of papers, with eighteen scheduled to be presented in the two days, as well as the now traditional panel session, and presentations by Inmos. The contributors were almost entirely from academic institutions, with the largest number coming from those within the United Kingdom. However, there were also contributions from European institutions, and the United States. One paper could not be presented, due to travel difficulties affecting its author, so the expected contribution from Asia did not occur. The paper - on an Intelligent character reader - is in the proceedings. These were published by IOS, as before, under the title Developing Transputer Applications and edited by John Wexler (see page 3).

The spread of interests covered in the papers was almost as wide as the geographical distribution of the authors. Within the general frame of reference of the meeting, there were three main strands. These can be categorised as operating systems, development tools and new paradigms for particular types of problems.

A brief overview of the papers presented is given below, along with the names of their presenters.

TROS: A REAL TIME KERNEL FOR A FAULT TOLERANT MULTI-PROCESSOR COMPUTER BASED ON ARGUMENT FLOW — ERIC VERHULST, R. LAUWEREINS, R. CUYVERS, J. PEPERSTRAETE, INTELLIGENT SYSTEMS INTERNATIONAL, BELGIUM. This paper describes the design and implementation of a fault tolerant system to provide a load balancing kernel written in occam and t-code, for a multi-user multi-transputer system. The system is designed to produce an environment in which code from more than one user's program may be resident on a single compute element. It describes the topology independence achieved through the use of argument flow techniques, and the fault tolerance achieved against both hardware and software failures.

DYNAMICITY THROUGH OCCAM AND TDS – D. MILLOT, J. VAUTHERIN, UNIVER-SITÉ PARIS-SUD, FRANCE. This paper describes an attempt at dynamic process creation in occam, for the production of pipelines of indefinite length, by the use of self modifying software. The situation on a single transputer, and that for known topologies is considered. An attempt at extension to unknown topologies is also considered

A CASE TOOL FOR DESIGNING DEADLOCK FREE OCCAM PROGRAMS – W. D. CROWE, R. HASSON, P. E. D. STRAIN-CLARK, THE OPEN UNIVERSITY. This paper describes a graphically based tool for designing programs (initially in occam, but potentially for any language which obeys the CSP model). It describes the interface selected, which is a hierarchical one, based on the concept of reusable components, and the tools available within the system for investigating the performance of the program being prototyped.

A DEADLOCK DETECTION TOOL FOR OCCAM — IR WOUTER JOOSEN, PROF. DR IR PIERRE VERBAETEN, UNIVERSITY OF LEUVEN, BELGIUM. This paper discusses the design and implementation of a *static* tool to perform deadlock detection in occam programs. It describes the system, implemented under Unix, produced using the yacc and lex compiler and parser generation tools. It processes the program source, and produces action sequences, which are program execution paths. The important events in such traces are PARbegin, PARend and channel communications. Deadlocks and infinite loops are detected by exhaustive searching of the action sequences, with programmer interaction to provide such things as values for loop counters. The tool is described by the authors as an adjunct to run-time debugging tools, and is seen as having its greatest utility in the design and early implementation stages.

SOLVING PARTIAL DIFFERENTIAL EQUATIONS VIA CELLULAR AUTOMATA: A BINARY AND STATISTICAL APPROACH – F. DESBOIS, A. COSNUAU, Y. MORCHOISNE, ONERA CENTRE DE CALCUL, FRANCE. Most systems for solving

PDEs use physical models, for example, the lattice gas model. The approach described here uses a numerical method, which uses Booleans, and probabilistic methods.

TOWARDS A SOFTWARE ARCHITECTURE FOR SOLID MODELLING SYSTEMS ON PROCESSOR NETWORKS – D. P. MALLON, N. S. HOLLIMAN, P. M. DEW, J. R. DAVY AND A. DE PENNINGTON, UNIVERSITY OF LEEDS. This paper discusses the various steps taken in the production of a machine independent system for solid modeling. It describes a three level model for this, based on the following: a machine architecture level, to allow compatibility between different real machines; a task specification level, which is both application and hardware independent; and a geometric application level, which is an application specific way to express geometric algorithms. The use of 'message to destination' schemes on a number of architectures is discussed, as a method of providing the machine architecture level. As an example of the higher levels, a constructive solid geometry modelling system is described.

AN IRREGULAR DISTRIBUTED SIMULATION PROBLEM WITH A DYNAMIC LOGICAL PROCESS STRUCTURE — MING Q. Xu, Stephen J. Turner, Nie Pin, University of Exeter. This paper discusses the implementation of a host-parasite interaction simulation, with hosts and parasites represented as logical processes. The system uses a modification of the 'time warp' approach, with the addition of logical process creation and deletion, and the system being action driven. That is, it is based on the interactions between logical processes.

A GENERALLY CONFIGURABLE MULTI-GRID IMPLEMENTATION FOR TRANSPUTER NETWORKS — OSAMA EL-GIAR AND TIM HOPKINS, UNIVERSITY OF KENT. Multi-grid is an iterative technique for solving equations, which gains over such approaches as Gaus-Seidel and successive over-relaxation, by using a sequence of grids in their solution. The approach taken computationally is one of dividing the grids into strips for processing. Results are presented for the application with a number of different configurations of the grid step and number of processors, and are compared with results for a similar system on the Intel hypercube.

SELF-ADJUSTING MAPPING: A HEURISTIC MAPPING ALGORITHM FOR MAPPING PARALLEL PROGRAMS ONTO TRANSPUTER NETWORKS — HONG SHEN, ÅBO AKADEMI UNIVERSITY, FINLAND. This paper describes the development of an algorithm for mapping arbitrary process graphs onto arbitrary processor graphs, based on a division of the task into the following units. A grouping module, which attempts to produce a sub-optimal clustering of processes into tasks that can be placed on the processor graph by the placement module. The final module is routing, which produces the connection between the real links and placed tasks and it is expected that all three can be used to work together to find a nearly optimal solution, in a cyclic manner.

INVESTIGATION OF COMMUNICATIONS PATTERNS IN OCCAM PROGRAMS – ROSE-MARY CANDLIN, QUIANGYI LUO, NEIL SKILLING, UNIVERSITY OF EDINBURGH. This paper describes two approaches to examining communications in occam programs. The first, direct measurement, was applied to a real application program on a Meiko computing surface, and the second utilizes discrete event simulation of the

same program. Both systems are described, with some emphasis on the differences between the two approaches, and a comparison of the results obtained by each, giving a good indication that the simulation was producing results close to the performance of the real system.

System configuration for very large database problems — Alan G. Chalmers, Derek J. Paddon, University of Bristol. This paper discussed the implementation of an extension of the process farm approach to load balancing, with a system controller and 2<sup>n</sup> worker processors, each of which was composed of an application process and a number of task and data control processes, to deal with the distributed nature of the data involved. The application of this approach to radiosity calculations was discussed, as was the choice of a topology on which to mount the system.

A COMPARISON OF PARALLEL IMPLEMENTATIONS OF FLUX CORRECTED TRANSPORT CODES — JING-MING JONG, UNIVERSITY OF WASHINGTON, USA AND G. S. STILES, UTAH STATE UNIVERSITY, USA. This paper describes the authors' experience of FCT systems for computational fluid dynamics problems on a number of different architectures, and compares the relative speeds of the algorithm on them. Whilst for pure speed, networks of transputers are nowhere near as fast as true vector supercomputers, when the cost/performance ratios are taken into account networks of transputers score very highly.

SIMULATING NEURAL NETWORKS IN DISTRIBUTED ENVIRONMENTS — JUKKA VANHALLA AND KIMMO KASKI, TAMPERE UNIVERSITY OF TECHNOLOGY, FINLAND. Two types of neural network simulation are discussed, these being the sparse distributed memory model and the Hopfield model. There is interest in implementing neural networks on parallel systems, due to their inherent parallelism. The authors describe their results for the two models, and compare the two as to their suitability for this type of parallelisation.

ATTRIBUTE EVALUATION ON A NETWORK OF TRANSPUTERS — MATTHIJS F. KUIPER, ATZE DIJKSTRA, UNIVERSITY OF UTRECHT, NETHERLANDS. This paper discusses the application of attribute grammars to the problems involved in producing parallel compilers. It describes a static approach which allows program decomposition, and therefore the utilisation of as many of the available processors as possible. This is compared to the approach taken in pipelined parallel compilers, where the number of processors to be used is fixed.

AN OBJECT ORIENTATED STYLE FOR THE MEIKO — MATTHEW CHALMERS, UNIVERSITY OF EAST ANGLIA. This paper describes a novel approach to programming on a Meiko Computing Surface, based on SmallTalk. Objects are composed of their normal activity, and a link to their superclass, allowing inheritance of properties. All of this takes place within the context of a message passing scheme, which passes messages to objects. However, the objects have control over the order in which they accept messages. The original application for which the system, called *Chancer*, was designed was a ray tracer.

C-NET: A C++ BASED LANGUAGE FOR DISTRIBUTED AND REAL-TIME PROGRAMMING — JEAN-MARC ADAMO, ÉCOLE NORMALE SUPÉRIEURE DE LYON, FRANCE. This paper discusses the philosophy and constructs of a C++ based language which contains parallel constructs and exception handling as well as object orientation. It gives the syntax, and examples of the use of the language, which bases its parallelism on that available in occam.

REAL-TIME TRANSPUTER MODELS OF LOW LEVEL PRIMATE VISION — ANDREW B. SMITH AND PETER H. WELCH, THE UNIVERSITY OF KENT. Human vision is thought to consist of an initial parallel stage in which feature data is gathered, followed by a sequential recognition stage. This paper discusses the implementation of a simulation of the parallel stage on a network of transputers. The authors note that their initial, highly parallel scheme is less efficient than one developed later with a much higher degree of sequential activity.

# Social aspects of the meeting

Despite the shortness of the meeting, it was apparent how quickly those attending became a cohesive unit, and how barriers of language and background were quickly overcome. Within the commercials slot, a book entitled *The Transputer Community* was advertised, published by the Edinburgh University Press, being a study of the transputer phenomenon, and covering the development of this community, showing the degree of interest raised by such developments, even among social scientists.

Much praise is due to the meeting organiser, John Wexler, who coped wonderfully with the difficulties inherent in setting up such an event, and edited the proceedings, as well as carrying out his normal duties within the Supercomputer Project. He was also charged with the organisation of the Supercomputer seminar. Despite all this he managed to keep the whole thing running smoothly, and retained his good humour. His crowning moment in this field must have been the conference dinner however, which was very well attended, and universally regarded as being of the very highest quality. It must be said that the organisers of the next meeting will have their work cut out to match it.

#### WHY DID THE TRANSPUTER CROSS THE POND?

As you might expect, the founder's second consecutive absence did not prevent the holding of the third biannual Roger Shepherd memorial joke contest at the occam user group meeting in Edinburgh. Among the repeatable contributions were

- Q: What do you call a ring of T400 transputers?

- A: Unsociable.

Two transputers pass five others who are playing brass instruments in a confined space; says one to the other: 'What's up?'; comes the reply: 'Nothing really – just a bandwidth problem.'

- Q: What would you get if you privatized INMOS?

- A: Lots of H<sub>1</sub>Owners.

(I should explain for readers lucky enough to live outside the target area for the advertisements that the meeting coincided with a pre-privatization publicity campaign for the English and Welsh water boards, which urged everyone to become a H<sub>2</sub>Owner.)

There were a surgeon, and architect and a parallel programmer, who were discussing whose was the oldest profession.

'Mine must be', said the surgeon, 'as God removed a rib from Adam to create Eve – quite a surgical feat.'

'No contest,' said the architect, 'out of chaos God created the ordered garden of Eden – a major architectural project.'

'That's nothing,' said the parallel programmer, 'who do you think created the chaos.'

- Q: Why shouldn't a Transputer run C\_NET?

- A: Because its pins get caught in the mesh.

- Q: What is a transputer user's favourite Christmas carol?

- A: 'occam all ye faithful, joyful and triumphant.'

- Q: What do occam processes and condoms have in common?

- A: Both are safe 99% of the time, and neither can be reused.

Someone claimed that it was Jean-Paul McSartre who said after attending the Edinburgh occam user group meeting, 'Och Aye! therefore occam'. [I think it was someone more like René Cathcart.]

Perhaps the shortest contribution was a piece of paper bearing the single word occam written in a hand remarkably like Iann Barron's. I suspect that if a joke could only have been found for it, tightly coupled embedded systems — much discussed in the panel session — would have made a successful punch-line.

On the basis of audience response, the group's regular clap-o-meter and chairman chose Colin Willcock's – the occam processes that are safe 99% of the time – to receive McTavish's (ostensibly) nuclear-powered self-heating haggis that had appeared in a talk earlier in the day. Alan Chalmers walked away with a larger haggis which was apparently the second prize – for the architect of chaos.

# SECOND SEMINAR OF

# THE SWEDISH TRANSPUTER USER GROUP

21 November 1989, The Royal Institute of Technology, Stockholm Martin Törngren, The Royal Institute of Technology

The Swedish market has been a tough one for the Inmos transputer. When the transputer was introduced it represented new ideas and new technologies. It usually takes some time for a new microprocessor to get accepted and for companies to change to the new microprocessor. Another reason for scepticism and delay is the fact that Inmos was not able to provide sufficient development tools in 1985. Inmos has always emphasized the importance of occam. However, even though many people enjoy occam, it is a new language. There is even now no occam compiler for other computers!

Today, four years after the introduction, things are looking much better. There are now a lot of different development tools available. New transputer chips and modules have appeared. SGS-Thomson gives stability to the transputer product and has introduced dramatic price reductions.

In Sweden many companies and universities have shown interest in the transputer and evaluations have been made. Recently the first transputer based product, an image processing computer, was released in Sweden. In addition to Inmos representatives, sales representatives from other manufacturers like Microway have appeared.

The Swedish Transputer User Group (STUG) was formed in May 1989. STUG now has about sixty members in Sweden. STUG arranges seminars and publishes a newsletter. STUG operates with a very limited budget and has the support of Inmos representatives in Sweden, which handles some of STUG's administrative details. The first STUG seminar was held at The Royal Institute of Technology in Stockholm in May. At this seminar an executive committee was elected to look after the group and it was agreed to publish a newsletter.

#### The seminar

The seminar was hosted by the Department of Machine Elements at the Royal Institute of Technology in Stockholm. Around fifty people from Universities, Technical Universities and companies were represented at the seminar.

The keynote speaker was Stephen Maudsley, application engineer at Inmos, who talked about new transputer products like the new low cost T400. He reported on plans for the future development of the transputer. He gave information on the H1 project, which aims at a transputer with the following characteristics:

- ▷ 10 times faster than todays transputers

- > code compatible with current transputers

- ▷ caches and support for virtual channels

Stephen also mentioned new modules for ethernet with TCP/IP support, SCSI and the VME bus. Other information included the cooperation between Inmos and the ASIC division of SGS-Thomson, the new breakpoint debuggers (initially C and occam) and future optimizing compilers.

After Stephen's talk there was a debate which centered around the following questions:

- Will there be any transputers with I/O on the chip (like the M212)? Answer: Probably no, instead ASICs with link units will be available.

- ▶ Is the transputer used for embedded systems applications? Answer: It is, but you would not necessarily hear about it.

- ▶ How can Inmos, a manufacturer of advanced parallel processing components, produce such low quality man-machine interfaces for their development tools. Answer: ??

- In what way should occam develop? Should it be kept as a secure language or should for instance records and/or recursion be included?

One answer: occam is a very nice language for 'smaller embedded applications' with a static software structure.

- ▶ Do you want an operating system or a library? Should the operating system be easy to modify by the user?

An obvious drawback with the current transputer scheduler is the few priority levels. This limits the use of the transputer in hard real-time applications.

# Other speakers at the seminar

Lars Estreen from the Department of Electronic Motor Drives at KTH had visited the *International conference on applications of transputers* in Liverpool. His overall impression was that the transputer was mainly used for image processing and super computer applications. He also emphasized the lack of an overall transputer standard for operating systems and communications.

Hans Johansson also from the Department of Electronic Motor Drives had attended an occam course arranged by Inmos in Bristol. He briefly reviewed the course and recommended it for people not experienced with the TDS.

Christer Juren from the Swedish Institute of Space Physics had visited the OUG meeting in Edinburgh and the subsequent supercomputer conference. He made a very interesting presentation of the Edinburgh concurrent supercomputer and also detailed the OUG proceedings.

Mariadata representatives of Alsys in Sweden presented the newly validated Ada compiler which however was not yet ready for demonstration.

Peter Ygberg from Bofors Aerotronics talked about his experiences of the Helios operating system which he enjoyed using.

My own contribution presented aspects on using the transputer in real-time control systems for applications in Mechatronics, particularly real-time properties, features which can cause non-deterministic behaviour and how to interface the transputer to sensors and actuators.

Mats Hanson from the Department of Machine Elements at KTH talked about new microprocessors for embedded systems. He particularly described an ongoing Master of Science project for fifteen students with guidance from researchers which aims at building a transputer based robot control system. Mr Hanson also proposed a joint project between SGS-Thomson in Sweden and the department.

The seminar was rounded up by refreshments and a few informal demonstrations. The CVR group showed their image processing computer and Datacraft, sales representatives of among others Microway, displayed quadputer transputer boards. Unfortunately neither Inmos nor Atari with their workstation could make a demonstration.

#### Future

The seminar was a positive one. There's definitely a growing interest of the transputer in Sweden.

STUG intends to publish newsletters shortly after seminars. The deadline for this newsletter is 10th December. The newsletter is written in Swedish but does accept papers in English.

The next seminar has not been scheduled but will probably be in the spring of 1990.

# SPECIAL INTEREST GROUPS

#### EDUCATION AND TRAINING Roger M. A. Peel, University of Surrey

The Education and Training SIG meeting during the twelfth OUG technical meeting in Edinburgh was attended mainly by members of various educational institutions, as well as by representatives of Inmos and several major industrial users of transputers.

Much of the meeting was spent reviewing hardware and software products suitable for use in education. One new product which generated particular interest was the CODE system from C-DAC (Pune, India), which closely emulates the Inmos Transputer Development System, but runs on a personal computer with no subsidiary transputer card (see page 86). Comprising an editor, occam 2 translator and an interpreted run-time environment, one of its major features is an interactive debugger which permits the state of variables and processes to be inspected during program execution. At a one-off price of \$400, and with site licences available for \$4000, this software is likely to be of interest to many members of the educational community.

Other products mentioned were the interfaces, TRAM motherboard and server software for the Acorn Archimedes from Gnome Computers, as well as reminders that the Inmos TDS1 product is freely available for personal computers from Jon Kerridge, and the VAX/Unix version from Peter Welch. Bob Stallard's occam 2 compiler (for Suns, etc.) is available from Loughborough University. Michael Poole (Inmos) announced that their new occam 2 compiler (written in C) could be made available in source form to organisations prepared to commit to porting it to novel non-transputer environments. Support for this activity would however be limited.

The remainder of the meeting was spent discussing how educational support might increase the uptake of transputers by industry. There was support for the suggestion that pre-packaged courses, complete with documentation, discs containing all the example programs and tutorial notes, should be made available to remote educational institutions and to industrial concerns not prepared to send their staff for direct training.

There was also considerable sympathy with the view that many technologists in the field were aware of the benefits of using transputers and occam, but that they were unable to convince their management that parallel program design was not too difficult. There also seemed to be reasons why employers did not want to see design methodologies in external courses. In addition, some engineers often prefer to avoid the concurrent solution because more complicated conventional languages and processors are a greater technical challenge!

Finally, there was muted interest in an occam educator's workshop, although there did not appear to be any convenient dates until 1990.

Roger M. A. Peel

Department of Electronic and Electrical Engineering

University of Surrey

Surrey GU2 5XH

United Kingdom

Tel: +44 483 509284 Fax: +44 483 34139

Telex: 859331 roger@uk.ac.surrey.ee

#### HARDWARE

#### Denis Nicole, University of Southampton

This is a report of the meeting of the Hardware SIG held during the eleventh technical meeting of the OUG at Edinburgh, September 1989. As usual, the group engaged in a wide-ranging discussion about most things transputer.

# Miniaturized transputer arrays

Hugh Webber of the Royal Signals and Radar Establishment described some work, mainly by Kevin Palmer, on the construction of miniature 'Supernode' switched transputer arrays. He has been able to build transputer modules of two types. One is a ceramic module sized two inches by one and a quarter inches which carries a transputer and 256 kbytes of DRAM. The other is a silicon hybrid with the same footprint as a transputer which carries both the transputer and, underneath it, 64 kbytes of DRAM all in a twenty-eight pin package.

They have been able to construct a whole sixteen transputer Supernode including camera, framestore, B007 graphics and LCD display in a  $6'' \times 4'' \times 2''$  cuboid. The system consumes 20 watts and can be powered for four hours by a standard military battery of the same size.

### Dynamic switching

There was some discussion of the use of dynamic reconfiguration of transputer arrays for message passing. The Linda machine from Cogent in the United States implements part of its communications in this way. Considerable care was required to ensure that no random traffic on the links was produced by the reconfiguration of the C004 switches. Some work on a Supernode at RSRE suggested that dynamic switching could also be effective on that architecture.

# Static column addressing

A new UK company, Division, has developed a graphics TRAM which uses static column addressing of dynamic memory. This is implemented in a small set of conventional PALs. Some discussion of the merits of this approach ensued, with J. Kidd suggesting that, while it may be worthwhile for display systems, it is not useful for most other transputer systems.

#### Standardisation

D. Nicole had been approached by M. Jane of the UK transputer initiative with a suggestion that interested users and vendors should attempt to establish hardware standards for transputer systems. An example was presented of a language vendor having to test his compiler on B004, B008 and B001 boards separately. These standards can take several forms: they can enshrine existing practice in such areas as control port addressing, link buffering and TRAM I/O mechanical organisation; they can develop new standards, for example, for miniature TRAMs; they can attempt

to guide new implementations on current transputers towards facilities that will be supported directly in new generation transputers, in such matters as through-routed message-passing protocols; finally, they can attempt to provide a common standard software interface for disparate hardware, such as Supernode/B008/Meiko/Parsytec link switching. Comments and offers of help and guidance to D. Nicole, please.

Communications regarding the hardware SIG should be addressed to:

Denis A. Nicole

Department of Electronics

and Computer Science

The University

Highfield

Southampton SO9 5NH

United Kingdom

Tel: +44 703 787167 Fax: +44 703 592865 dan@uk.ac.soton.ecs

# FORMAL METHODS R. P. Stallard, Racal-Milgo Ltd

A meeting was held at the Edinburgh Technical Meeting of the OUG. There was not much news to report.

I spent much of the time outlining ideas not on occam itself but on what might be the form of the language on top of occam. It is my view that there must be a convergence between use of formal techniques and software engineering. What is needed to promote the occam model is a high level programming environment that maps neatly onto occam. Such a system could be of 'object-orientated' type, but even better would be 'process-orientated'. Such systems have the benefit of clearly defining an interface to a module and also managing the inevitable changes to a software system. All this is possible directly in occam but it is not made compulsory. Why should we still use systems that make straightforward changes so difficult? I hope to produce an article on this topic for the next newsletter.

In the brief time that was left, discussion on adding more features to occam started, I propounded the view that all further developments should be banned (or else we will need to apply Occam's razor to occam). If users want more features they should use a higher level language. The panacea of the perfect programming language has been sought after for almost as long as the Elixir of Eternal Life, you can not make a language suitable for every application. My personal plea remains: please leave occam as an efficient medium level language with fast execution.

Deadlock got its usually mention, it was felt that tools to combat it run the danger of oversimplifying the problem, but some degree of modularization (hiding internal channel intercommunication) obviously helps. It is encouraging that two papers at Edinburgh described tools to detect deadlock. I hope they will soon be available for all of us to use.

R. P. Stallard Racal-Milgo Ltd Station Road Hook, Hants United Kingdom

#### GRAPHICAL PROGRAM DEVELOPMENT TOOLS

a new special interest group

Mike Roberts, City University, London

At the last occam user group meeting I proposed the formation of a 'Graphical program development tools' special interest group. As the suggestion did not meet with quite the hilarity I anticipated (six people were genuinely interested) I decided to test the water with the following short piece. Anyone interested in the formation of the SIG may contact me at the address below.

# What is a graphical program development tool?

Graphical program development tools do, as their name implies, use graphics in the program development process. Many experimental tools have been produced for use in all stages of the sequential software life cycle ranging from high level project management systems to low level tools using graphics in the programming process.

As yet however, few have been produced for parallel systems though many feel that graphical tools may help in that 'Holy grail' of parallel processing – the export of parallel systems and languages into the so called real world.

They fall naturally into two main areas – program visualisation tools and visual programming tools. Program visualisation is the use of computer graphics to enhance program presentation and facilitate the visualisation, understanding and effective use of programs by humans. Visual programming on the other hand is a collection of related techniques through which algorithms are expressed using various graphical representations. In short programming visualisation shows aspects of the program graphically, where as visual programming makes use of graphics as the program input medium. For initial informed introductions to both areas see references [1, 2].

But can such methods aid concurrent programming? I think that they can. Most of the reasons behind the adoption of graphics based programming tools centre on increasing the use of the left side of our brains, little used in the programming process at present. With the increased software complexity often shown in concurrent programs, it makes sense to bring as much as is possible of our underutilised brains to bear upon the task. Several recent reports from within the occam community [3, 4, 5, 6, 7] demonstrate the viability of such tools and can be seen as supporting this opinion.

If sufficient interest is expressed by members of the OUG, I will organize an initial SIG meeting at the Exeter technical meeting.

#### References

- B. A. Myers, The state of the art in visual programming and program visualisation, Report Nº CMU-CS-88-144, Computer Science Department, Carnegie Mellon University, Pittsburg; presented at the British Computer Society Displays Group's Symposium on Visual programming and program visualisation, London, 16 March 1988.

- [2] Nan C. Shu, Visual programming, Van Nostrand Reinhold, New York, ISBN 0-442-28014-9, 1988.

- [3] W.-D. Crowe, R. Hasson, P. E. D. Strain-Clark, A CASE tool for designing deadlock free occam programs, in the Proceedings of the 11th occam user group technical meeting, ed. John Wexler, Developing transputer applications, OUG-11, Edinburgh, IOS, September 1989.

- [4] F. Mourlin, Graphical environment for occam programming, occam user group newsletter Nº 11, July 1989.

- [5] M. Roberts, P. M. Samwell, A visual programming system for the development of parallel software, in the Proceedings of the Second International Conference on Software Engineering for Real Time Systems, Circncester, IEE, September 1989.

- [6] M. Stephenson, O. Boudillet, GECKO: a graphical tool for the modelling and manipulation of occam software and transputer hardware toplogies in the Proceedings of the 9th occam user group technical meeting, ed. Charlie Askew, occam and the transputer – research and applications, OUG-9, Southampton, IOS, September 1988.

- [7] S. Stepney, GRAIL: graphical representation of activity, interconnection and loading, in the Proceedings of the 7th occam user group technical meeting, ed. Traian Muntean, Parallel programming of transputer based machines, OUG-7, Southampton, IOS, September 1987.

Mike Roberts

The Centre for Information Engineering

City University

Northampton Square

London EC1V 0HB

United Kingdom

m.roberts@uk.ac.city

# TECHNICAL CONTRIBUTIONS

#### SAFETY FIRST

Peter Welch, chairman of the occam user group

# Performance – a secondary consideration

I was getting a little alarmed. Recently, the performance of our transputer system shot up overnight – our T800s doubled their MIPS rating from 10 to 20 and their MFLOPS went from 1.5 to 2.3! This upgrade cost us nothing and caused absolutely no disruption to our user service during the conversion. Indeed, our users never noticed a thing – but we now have much more exciting numbers to put on our posters to impress visiting industrialists.

A few compulsory sessions of reading X-window source code soon forced the truth out of our system administrator. These dramatic improvements were brought to us thanks to a new aggressive marketing policy from Inmos! After a few moments of quiet thought, this did not seem to be such a bad thing. In this world, technical excellence is no guarantee of success – it is not even a pre-requisite! Inmos is

well justified in moving to the same level as its competitors and fighting to their rules. After all, there are some exciting questions to be answered. Can four T800s outperform an i860? Will the H1 knock everything else out of sight? Never mind the quality – can you begin to feel the terraflops?

Hang on a moment. Chasing performance figures is not the only basis for impressing world opinion. There is another angle that I do not recall ever seeing promoted in any *transputer* marketing literature:

- > an angle without which all the performance in the world is just candy-floss;

- ▶ an angle on which public attention is beginning to be focussed;

- > an angle upon which the world will soon insist;

- ▶ an angle around which the transputer was conceived;

- > an angle on which other technologies are a little bit wobbly.

With such a basis, surely the marketing people can come up with something fairly macho about...

# Safety – the primary consideration

A 'safety critical' system is one whose failure may lead to loss of, or injury to, life or wallet. The percentage of computer systems that can be classified as safety critical is steadily growing. During the next decade, computers will not only be controlling the big things like commercial airliners, nuclear power stations and railway signals, we will be surrounded by them and dependent on them for most aspects of everyday living – personal communicators, gas cookers, car braking systems, etc. In the near future, almost all computer systems will contain some safety critical components.

The transputer processor, along with the occam programming language, is based upon formal mathematical theories of (parallel) computing [8, 9]. These theories have a long and mature pedigree. Transputer networks and occam processes obey a rich collection of simple algebraic laws [10, 11] that give them a chance of becoming amenable to formal specification, derivation and verification. These properties are an essential bedrock for the routine mass production of safety critical applications. By comparison, most other technologies in practice today are built upon sand.

High performance is a by-product of this discipline. Simple manipulations at all levels of design and implementation preserve the semantics of the system, allowing it to be tuned for various criteria of efficiency. But, performance must always be a secondary consideration – there is no merit in producing the wrong answers faster than all your competitors!

# A little example - some school algebra

Forget about parallel computing. Consider a basic computational notion, common to all types of computing architecture and language: expression evaluation.

Occam expressions have a pure mathematical semantics – i.e. 'what you see is what you get' (WYSIWYG). For instance, the meaning of a sub-expression depends only on what is in that sub-expression and not upon its surrounding context. [In the higher realms of functional programming, this is known as 'Referential Transparency'.]

The practical importance of this is that expressions behave in the way we all learned at school – for example:

$$(a*b) + (a*c)$$

may be replaced by:

$$a*(b+c)$$

and the semantics of the whole program is unchanged. For 'classical' languages (like FORTRAN, Pascal, C, Ada, ...) this is not true: suppose a were a sub-expression whose evaluation side-effected the current state of the system!

Evaluating occam expressions cannot change system state:

- assignment of values to variables (:=) is not an operator and may not be embedded within expressions (unlike in C);

- b the input/output processes (?, !) are not operators and may not be embedded within expressions (unlike many standard i/o functions in other languages e.g. getchar from C);

- ▷ no operators cause state change (unlike ++ in C);

- $\triangleright$  function calls cannot cause state change (unlike those in FORTRAN, Pascal, C, Ada, ...).

# Consequences

A minor consequence of this freedom from side-effects is that the order in which operands are evaluated has no significance. Therefore, in *occam* there is no rule such as: 'operands are evaluated from left to right'. The designer has one less decision to worry needlessly about and the compiler has the freedom to choose the optimum ordering. Simple transformations may be applied – perhaps, by a tool other than the compiler – to assist in such optimisations. Of course, if more than one processing element is available, operand evaluation may also proceed in parallel.

[Actually, C has no rule for ordering the evaluation of operands either. In this case, however, the conditions are ripe for a serious disaster – it's so easy to write code that has several different legal interpretations. If evaluating expressions can have procedural side-effects, then the order in which this happens does matter – even if the language definition pretends it does not!]

The major consequence is the aid to our clear understanding of the meaning of code at this level. The properties are transparent – they are what we expect and there can be no nasty surprises.

These are not considerations of marginal importance. They are a necessary part of the foundations of a sound engineering discipline that will enable the production of safe software for safety critical systems.

If you accept the above arguments, there is an immediate corollary to contemplate: 'classical' programming languages have no safe rôle to play in safety critical applications. Since it is almost inevitable that those languages will nevertheless play major rôles in such systems, we have cause for grave concern.

# Interim Defence Standard 00-55 (Draft)

The Interim Defence Standard 00–55, published as a draft by the UK Ministry of Defence [12], defines 'procedures and technical requirements' for the development of safety critical software.

A crucial new feature is that 'formal' (or, at least, 'rigorous') methods are to be used at all levels of specification, design, implementation and verification. Encouraging news for those of us with a nervous disposition – formal proofs (or 'rigorous arguments') may not completely guarantee our safety, but they certainly increase confidence levels and our present levels could do with a bit of a boost!

The software industry, however, seems to be in a small panic over this standard – largely for the wrong reasons (software people are extremely conservative!). Some proper reasons follow.

The 00-55 standard lists a number of approved formal specification and design techniques. These include both CCS [8] and CSP [9]. However, the document elsewhere prohibits the use of parallel processing (either across multiple 'processors' or within a single 'processor') as an 'unacceptable practice'! We are invited to use CSP for design but we are not allowed to exploit the results from that design!!

There is also a mandate that the programming language used must be 'high-level' and must have a compiler with an 'approved national or international validation certificate'. This seems to be aimed at the Ada world, but is probably also intended to allow other languages with ISO or ANSI standardisations (i.e. C, FORTRAN and Pascal). Unfortunately, none of these languages has a semantics that is simple enough or well-enough defined to be amenable to the use of formal methods (or even rigorous ones). The same is true for any credible subset (or superset) of these languages. The example issue raised earlier in this article is only the start of a long list of problem areas that are deeply embedded in their fundamental design – for further reading, see references [13, 14, 15].

Floating-point arithmetic is also banned! Presumably we are expected to use some fixed-point software instead. It is true that a realisation of floating-point arithmetic cannot be validated by testing. It is also true that one or two manufacturers have recently been embarrassed by some nasty bugs emerging from 'industry standard' hardware implementations. However, fixed-point arithmetic is no less easy to check-out and I know of no formally verified products. On the other hand, the T800 floating-point micro-code was derived through formal transformation of occam source code that carries a formal proof of correctness with respect to a formal specification in Z of IEEE-754 arithmetic [16]. I know in which of these two mechanisms I would rather put my trust!

For additional observations on 00-55, see reference [17].

# Concluding remarks

The fact that the M.o.D. has published 00–55 (with its central compulsory theme on the use of formal methods) is clear evidence that safety considerations are uppermost in the minds of a large group of customers for computer systems. Commercial buyers will certainly follow the military lead and demand at least as high a level of security.

There is a danger that the internal contradictions within 00-55 may give formal

methods a bad name and that industrial systems suppliers may be able to push it away for some while. Marrying formal methods with classical programming languages will always lead to tears – but the problems lie mainly with the latter partners, not the former.

The pressure for safety will get stronger every year, eventually dominating the pressure for performance. Inmos is in an excellent position to capitalise on this market. The T800 demonstrates that performance need not be sacrificed to meet the demands of safety – indeed that high performance is a consequence of high security.

Why does Inmos publicity not:

- ▶ highlight the formal methods being used in the design of the H1?

- ▶ boast about the security improvements delivered by transputer-based parallel computing?

- ▶ shout more loudly about occam?

After this, it would be interesting to find out about all those MIPS, MFLOPS and Mbaud – but these will merely be the icing on the cake!

#### References

- [8] Robin Milner, A Calculus for Communicating Systems, ECS-LFCS-86-7, Laboratory for the Foundations of Computer Science, Edinburgh University, 1986.

- [9] C. A. R. Hoare, Communicating Sequential Processes, Prentice-Hall International, 1986.

- [10] C. A. R. Hoare et al., Laws of Programming, Commun. ACM Vol. 30, Nº 8, pp. 672-686, August 1987.

- [11] A. W. Roscoe and C. A. R. Hoare, Laws of Occam Programming, Technical Monograph PRG-53, Oxford University Computing Laboratory, 1986.

- [12] Ministry of Defence, Requirements for the Procurement of Safety Critical Software in Defence Equipment (Interim Defence Standard 00-55), Directorate of Standardisation, Ministry of Defence, Room 5150A, Kentigern House, 65 Brown Street, Glasgow, G2 8EX, Scotland, May 1989.

- [13] Peter Welch, Going to Ceed?, Internal Memorandum, Computing Laboratory, The University, Canterbury, Kent, CT2 7NF, England, March 1989.

- [14] Roger Shepherd, Compiler Support for Floating-point Computation, Letter to the Editor, Software – Practice and Experience, 18, p. 1193, December 1988.

- [15] Roger Shepherd, Security Aspects of Occam 2, Technical Note 32 (72-TCH-032-00), Inmos Ltd, Bristol, 1987.

- [16] G. Barrett, Formal Methods Applied to a Floating Point Number System, Technical Monograph PRG-58, Oxford University Computing Laboratory, 1987.

- [17] David May, Draft Military Standard 00-55, Internal Memorandum, Inmos Ltd, Bristol, July 1989 (appears in this newsletter).

Peter Welch Computing Laboratory The University Canterbury Kent CT2 7NF United Kingdom Tel: +44 227 764000 x3629 phw@uk.ac.ukc

# DRAFT MILITARY STANDARD 00-55 David May, Inmos Ltd. Bristol

The proposed standard for safety critical software contains many requirements for mathematically proven software. This note comments on these proposals.

#### The state of the art

Over the last twenty years, considerable progress has been made in modelling and reasoning about computer programs. A variety of notations and languages have been developed; some of these are supported by computer-assisted proof systems. Examples of program verification systems are the Boyer-Moore theorem prover, Gypsy, AFFIRM, SDVS, LCF, m-EVES and NuPRL. Although some impressive proofs have been done, the state of the art in mechanised program verification is still limited to small programs (i.e. a few tens of pages of code).

New theories and formalisms to support software engineering have also emerged. These include CCS and CSP for concurrent programs, and VDM and Z for system specification. So far no theorem proving tools for these formalisms have been implemented, but some useful computer-based tools related to them have been developed (e.g. the 'B tool' for Z, and the occam transformation system). However, these do not support the construction of machine checked proofs in an explicit logical calculus.

In summary, it is now clear that formal methods are applicable to several areas of hardware and software design. In some cases, mechanised proof systems have been demonstrated. There have been one or two commercially important applications of formal methods (such as the use of Z and the occam transformation system in the design of the Inmos IMS T800 transputer floating point unit). However, none of the languages and tools have yet reached sufficient maturity for widespread use.

# Programming languages

There are few programming languages suitable for the kind of mathematical verification process outlined in the proposed standard. In order to perform mathematical verification of programs, the programming language must have a mathematical semantics. The semantics must be small enough to allow it to be used in the construction of program proofs – ideally, it must be small enough to be embedded in a proof checker. All of the systems mentioned above employ simple languages or language subsets – these languages have been designed to be simple enough to allow program proofs. No existing internationally standardised language has a simple enough semantics for this purpose. Even if sufficient resources were made available

to construct a mathematical semantics for these languages, it would not be suitable for program proofs.

The best solution (from a technical viewpoint) would be to create a new (international standard?) language for safety-critical software. As it is only necessary to write small programs with simple control structures and simple data structures, a very small language designed for mathematical verification can be used. It would require a simple – and verifiable – compiler. An alternative might be to standardise the occam language (or a language closely related to it) – see the appendix to this note.

# Compilers

There are no *verified* compilers for existing standard languages. The languages are all too big and complex. Further, there is an increasing trend towards the use of optimising compilers. The standard prohibits the use of optimising compilers – but all compilers optimise to some extent. Which optimising techniques are considered unsafe?

Validation is not a substitute for verification. It can be used to show the presence of bugs in the compiler, but not to show their absence. The best approach would be to employ a simple language for which a simple verified compiler can be constructed. An alternative process would be to use proof techniques to prove that the compiler output (instruction level program) implements the high-level language program.

If there is no method of verifying that the assembly language program correctly represents the high level language program, it would be better to write the programs in assembly language and verify them mathematically in terms of a mathematical specification of the machine instructions.

# Programming restrictions

The proposed list of restrictions in the standard appears ad-hoc and inconsistent with the proposed list of design methods. If the use of multiprocessing and parallel processing are both prohibited, where is the need for CSP and CCS? Why has use of goto statements, exceptions and pointers not been prohibited?

Specifically, with reference to section 21 of the draft standard (see figure 1):

- 1. Floating point arithmetic may be dangerous but it seems better to use IEEE arithmetic (for which there is a mathematical specification in Z) than un-specified fixed point arithmetic.

- 2. Although there is no obvious need for the use of recursion in safety-critical software, there is no reason to treat it as a dangerous technique. It is often much easier to prove the correctness of recursive programs than the equivalent non-recursive ones; for safety critical applications there is the additional obligation to prove that the depth of recursion is bounded.

- 3. The problem with interrupts is the interaction between the interrupt service routine and the interrupted program. Is the idea to allow programs which consist of only a timer service routine? If not, this restriction does not seem to achieve anything.

- 21 Unacceptable Practices

- 21.1 This Standard prohibits the use of practices which are unsafe,

- or difficult to analyse such as:

- 1. floating point arithmetic;

- 2. recursion, whether simple or mutual;

- 3. interrupts, except for a timer interrupt at fixed intervals;

- 4. assembly level programming languages;

- 5. dependence on separate elements being executed on parallel asynchronous processors. The complete set of Safety Critical Software modules should run in a single processor;

- 6. multi-processing on a single processor;

- 7. object code patching;

- software architectures that are re-configurable under application program control;

- 9. dynamic memory management.

Figure 1: text of section 21 of the draft standard

- 4. It is dangerous to ban assembly language programming until a verified compiler is available (see above).

- 5. The great success of CCS, CSP (and its implemented subset, occam) is that they provide a design method, mathematical proof tools and associated programming language for constructing secure concurrent systems both for parallel processing and for multiprocessing within a processor. These tools are much more reliable than using complex sequential programs to achieve the same effect. They have been developed over many years specifically to overcome the difficulties of constructing secure real-time systems.

- 6. See above.

- 7. Object code patching should clearly be prohibited.

- 8. It is not clear what 'reconfiguring the software architecture' means.

- 9. Dynamic memory management this is probably best prohibited for the moment.

# Summary

The above remarks can be summarised:

- ▶ The theoretical tools do exist to allow mathematically verified software to be constructed. Although the existing techniques can not cope with large programs, they could be employed for the kind of safety critical programs described in the standard.

- ▷ Existing standard languages and their compilers do not form a suitable basis for mathematical verification. Much smaller, simpler languages are needed. They must be designed with verification in mind from the outset.

- ▶ Much folklore has grown up about which programming techniques are unsafe. In particular, there is a tendency to regard all forms of concurrency and non-determinism with suspicion. This view is wrong. Secure, high-level programming

techniques, supported by rigorous mathematical verification techniques, now exist for programs incorporating parallelism and non-determinism. Indeed, such programs are often *easier* to reason about and test than the alternative (a relatively complex sequential program). It is important not to prohibit the very design techniques which make mathematical verification possible!

➤ A substantial investment will be needed to create – and standardise – the language(s) and tools (proof checkers, verified compilers) needed. It will also be important to consider the relationship with mathematically verified hardware (the specification of a machine instruction set is needed in order to verify the compiler). See the appendix to this note.

Lastly, it should be noted that although the UK has considerable strengths in the theory and practice of program verification, a very substantial investment in training (and re-training) will be needed. It is unlikely that enough people are available to teach these techniques: perhaps the most important first step is a major investment in higher education focused around existing centres such as Oxford University Programming Research Group, Manchester University, Edinburgh University Laboratory for the Foundations of Computing Science and Cambridge University.

# Appendix

# The SAFEMOS project

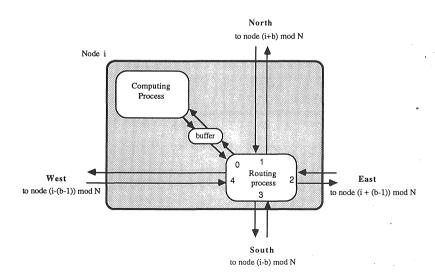

The construction of fully verified systems is currently a research activity. However, commercial interest in formal verification is growing rapidly in view of the increasing use of microprocessors in real-time control applications. The UK IED project SAFEMOS (collaborative project 1036: Inmos, SRI Cambridge, Oxford University, Cambridge University) involves the construction of languages, compilers and hardware for verified systems.