### MEGAFRAME Series

Hardware Documentation Copyright: PARSYTEC GmbH

VMTM

VME - Multi Transputer Module

Technical Documentation

Version 1.1

October 1987

Author : Jürgen Löwenhag ·.

| 1. | Block  | Diagram and General Description                      | •  | •  | • | • | • | • | 4  |

|----|--------|------------------------------------------------------|----|----|---|---|---|---|----|

| 2. | The T  | ransputer Sections                                   | •  | •  | • | • | • | • | 7  |

|    | 2.1.   | Block Diagram and Description .                      | •  | •  | • | • | • | • | 8  |

|    | 2.2.   | Hardware Addresses                                   | •  | •  | • | • | • | • | 9  |

|    | 2.3.   | Software Addresses of the Links                      | •  | •  | • | • | • | • | 9  |

|    | 2.4.   | Bootstrap                                            | •  | •  | • | ٠ | • | • | 9  |

|    | 2.5.   | Error and Analyse                                    | •  | •  | • | • | • | • | 10 |

|    | 2.6.   | Program-controlled Reset                             | •  | •  | • | • | • | • | 11 |

|    | 2.7.   | Jumper Allocation                                    | •  | •  | • | • | • | • | 12 |

| 3. | The VI | Æ – Link adapter Section                             | •  | •  | • | • | • | • | 14 |

|    | 3.1.   | Block Diagram and Description .                      | •  |    | • | • | • | • | 15 |

|    | 3.2.   | Addressing of the VMTM                               | •  | •  | • | • | • | • | 16 |

|    | 3.3.   | Programming of the Data Transfer<br>in Polling- Mode | •  |    | • | • |   | • | 18 |

|    | 3.4.   | Jumper Allocation and Address swi                    | tc | he | s | • | • | • | 22 |

|    | 3.5.   | DIN Connector Pin-out                                | •  | •  | • | • | • | • | 24 |

| 4. | The L  | ink switch Section                                   | •  | •  | • | • | • | • | 26 |

|    | 4.1.   | Functional Description                               | •  | •  | • | • | • | • | 27 |

|    | 4.2.   | Configuration                                        | •  | •  | • | • | • | • | 28 |

|    | 4.3.   | Configuration-Jumpering                              | •  | •  | • | • | • | • | 31 |

| 5. | The L  | ink buffers                                          | •  | •  | • | • | • | • | 36 |

|    | 5.1.   | Local Connections with other Modu                    | 1e | s  | • | • | • | • | 37 |

|    | 5.2.   | Connections in distributed System                    | s  | •  | • | ٠ | • | • | 38 |

| 6. | Techn  | ical Data                                            | •  | •  | • | • |   |   | 41 |

1.

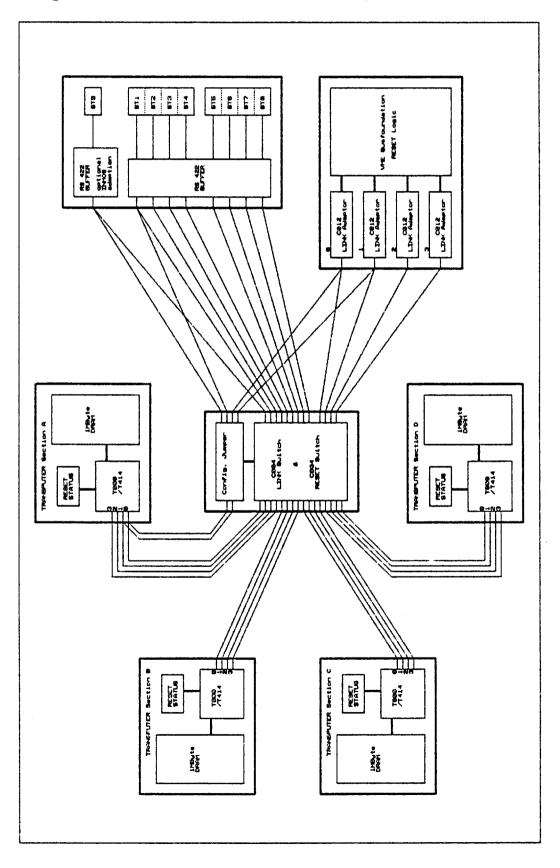

#### 1. Block Diagram and Description

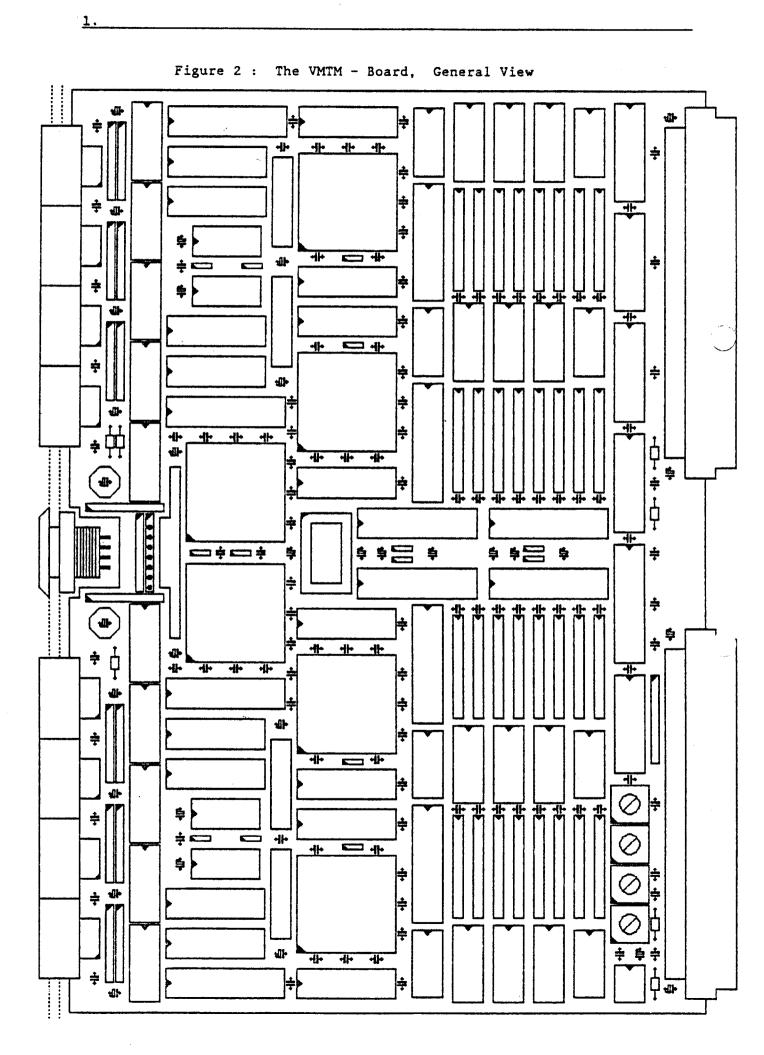

The VMTM VME - Multi Transputer Module has been conceived as a VME- slave board (implementation according to VME-spec. Rev.C: IEC 821, IEEE P1014/D 1.0. Operation modes A24/A32/D8, employed in 32-bit systems).

The board contains four independent transputer nodes based upon the IMS T800 (T414) transputer with 1 MByte DRAM local memory each. This means an on-board computing power of 40 MIPS respectively 6 MFLOPS.

Four link- adapter IMS C012 are available to implement communication channels between the transputer nodes and the VME-bus. Due to this the VMTM Module can be used as a multiuser transputer development system, wich supports up to four users each working on its own independent transputer section . Software to support this under OS-9 and UNIX is available (MEGATOOL Transputer Development System).

Furthermore, there is the possibility to integrate the VMTM module into transputer networks via external link channels. To support this nine RS422 buffered link-channels are led to the front panel. So it is possible to implement an interconnection in case of using several VMTM modules in one VME system, or to control a remote transputer system at distances up to 10 m.

The connectivity of all 29 link channels is accomplished by electronic link switches (IMS C004). This means that all the communication channels on board are software configurable.

- 5 -

1.

2.

### 2. The Transputer Sections

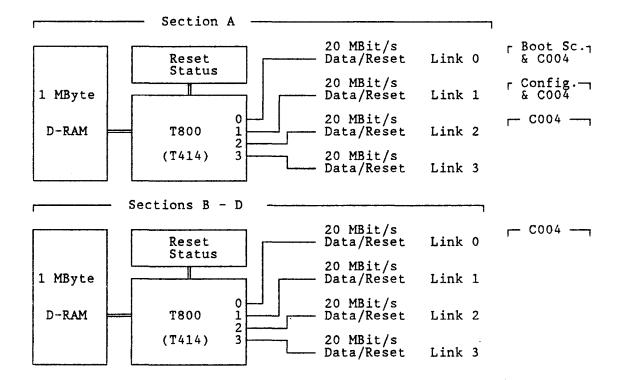

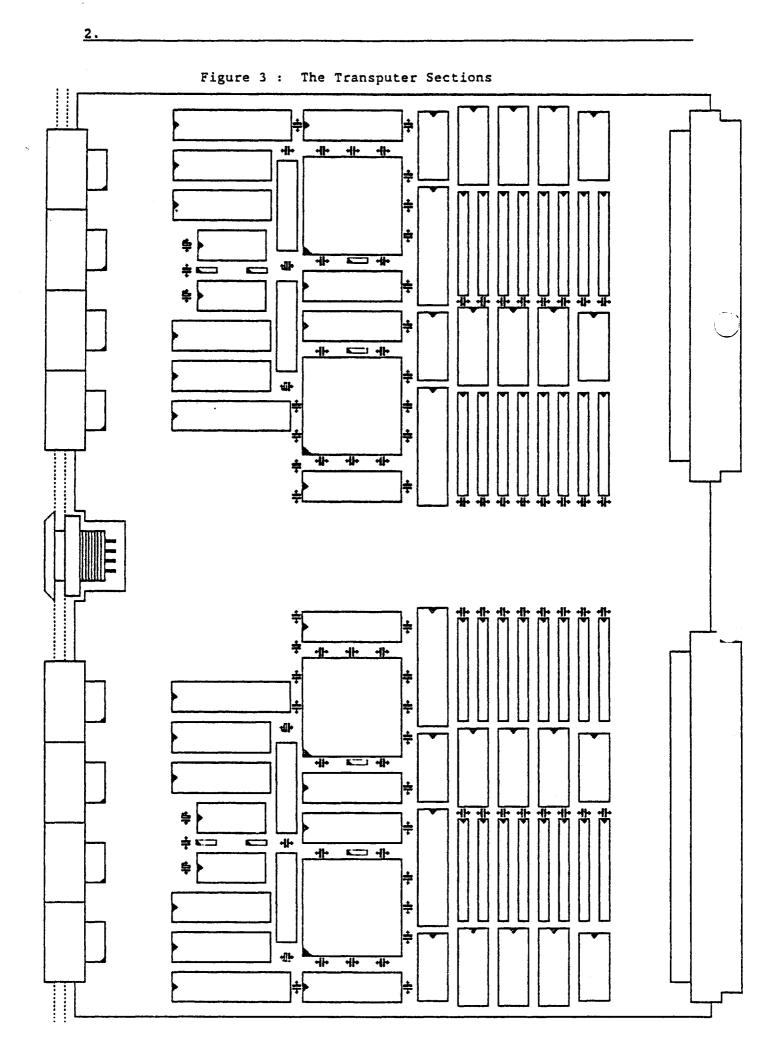

2.1. Block Diagram and Description

Figure 4: Block Diagram of the VMTM - Transputer Section

The VMTM is a 4-Transputer module with up to 40 MIPS processing capability. Each transputer node consists of a T800 (T414) 32 bit transputer, a 20 MHz system clock and 1 MByte dynamic RAM with a 100 ns access time.

The 4 transputer links can be adjusted to 20, 10 or 5 MBit/s working Parallel to each link there exists the possibility of setting up speed. program controlled bi-directional resets. This ensures that within a network each transputer has the possibility, by communication, of controlling the activity of its four immediate neighbours and in the event of an error to reset them and start anew. A status register holds all the error conditions and can be read-out at any time. One bit is provided for the transputer error and one for the address error. In the event of an error, either the analyse condition, an interrupt or an external error is generated according to the settings of the jumper selectors. The following functional description is applied to only one of the four transputer nodes but it is equally valid for any of them.

- 9 -

#### 2.2.

### 2.2. Hardware Addresses

Address space of the T800 (T414)

Hardware Addresses

Addresses in present OCCAM-2-Implementation PLACEment as word address

| 0000 0000 | Reset                    | #2000 0030 |

|-----------|--------------------------|------------|

| 0000 0080 | Status                   | #2000 0020 |

| 0000 0040 |                          | #2000 0010 |

| 800F FFFF | 1 Marte contrine comence | #0003 FFFF |

| 8000 0000 | 1 MByte working memory   | #0000 0000 |

|           |                          | #0000 0000 |

### 2.3. Software - Addresses of the Links

After declaration of the channels the following address allocation is valid for the 4 links of the T800 (T414):

PLACE Link0.Output AT #0 : PLACE Link1.Output AT #1 : PLACE Link2.Output AT #2 : PLACE Link3.Output AT #3 : PLACE Link0.Input AT #4 : PLACE Link1.Input AT #5 : PLACE Link2.Input AT #6 : PLACE Link3.Input AT #7 :

2.4. Bootstrap

Every processor of the VMTM is basically link-booted, that is, the processor awaits its program via a link following every reset. In such a condition, all four links have equal priority. The first information which arrives over one of these links is interpreted as a boot program and is executed accordingly.

#### 2.5.

#### 2.5. Error and Analyse

The VMTM offers the possibility under the error conditions to react with a structured shut-down of all processes. Basically, only two types of errors can occur: program- and address errors. Programming errors, such as the division by zero, an integer overflow or an array overspill is signalled by the transputer by the setting of an error flag. An address error, i.e. accessing an address outside the boards memory, sets a bit in the status-PAL.

According to the jumper selection an error condition will initiate either an analyse condition, an interrupt, generate an external error or do nothing. Analyse mode initiates a controlled shutdown of all processes that means all active processes are systematically run down and the system can be analysed externally after resetting and re-loaded. The actual error condition can be read-out and examined.

If the transputer node is driven as host the analyse facility must be disabled!

The interrupt activates a service routine (waiting for input on OCCAM channel EVENT) which may be programmed by the user. The external error input of the T800 (T414) has, when activated, the same effect as an internal transputer error.

The addresses of the status- PALs are listed above. The bits 0 and 1 have the following meaning when set (active low):

Bit 0: Transputer Error Bit 1: Address Error 2.6.

### 2.6. Program controlled Reset

Parallel to each link a reset line is lead which puts the addressed transputer in the boot-condition. That gives the possibility to watch the activity of the next four neighbours via the links and in the event of an error to execute an aimed reset. Afterwards they can be supplied with a new program code via the links and started anew. The following program example shows the necessary command sequence for the reset:

PROC reset ( VAL INT channel) -- Reset channel 0: channel = 1 -- Reset channel 1: channel = 2 -- Reset channel 2: channel = 4 -- Reset channel 3: channel = 8 INT addr.reset : PLACE addr.reset AT #20000030 : -- Address of the Reset-PAL TIMER clock : VAL INT wait IS 2 : -- 2 times 64 microseconds SEQ addr.reset := 0 -- This sequence enables the addr.reset := 1 -- transmission of a addr.reset := 2 -- Reset. addr.reset := 3 -addr.reset := channel -- set Reset for channel number clock ? time \_\_\_ clock ? AFTER time PLUS wait -- 128 Micro seconds delay addr.reset := 0 -- erase Reset

2.7.

### 2.7. Jumper Allocation

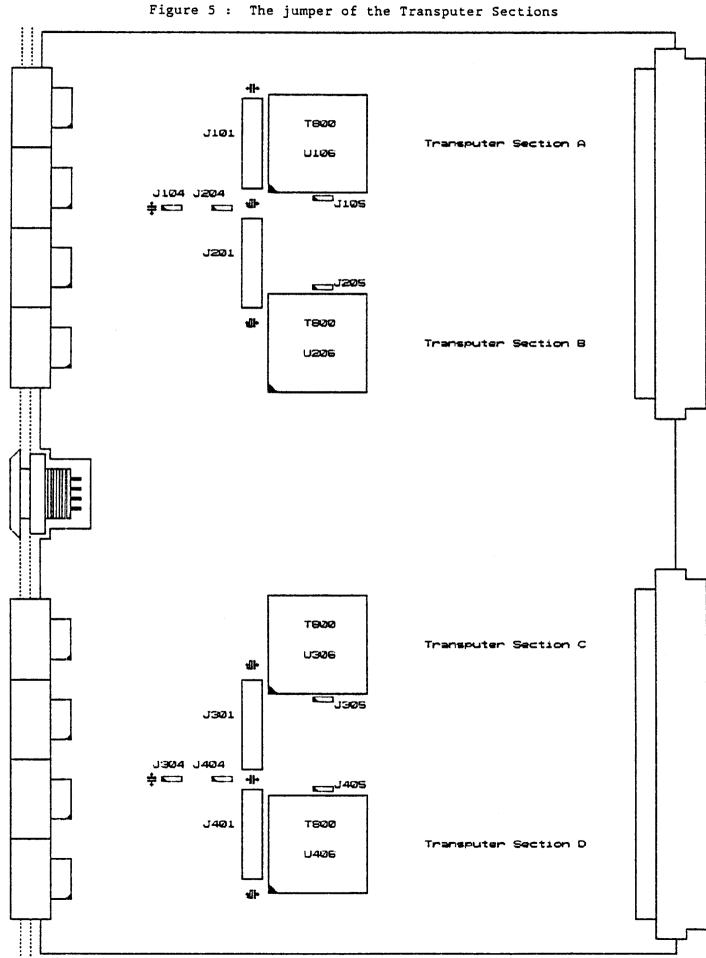

In the following jumper diagrams the position and orientation are adequate to the respective board jumpers; (viewed from the DIN connectors's right-hand side); see also figure 5.

### J101/201/301/401 external Error, Memory access, Link speed, Clock frequency T800 (T414):

|    | A B         | External Error (Event)                                                                                       |

|----|-------------|--------------------------------------------------------------------------------------------------------------|

| 1  | ° - [ ] - ° | enable Event : 2B jumpered<br>disable Event: 2A jumpered                                                     |

| 2  | 0 - 0 - 0   | Memory access:                                                                                               |

| 3  | 0 - 0 - 0   | 30 MHz Transputer, 100 ns RAM: 4B jumpered<br>30 MHz Transputer, 120 ns RAM: 3B jumpered                     |

| 4  | 0 - 0 - 0   | 20 MHz Transputer, 100 ns RAM: 3A jumpered<br>20 MHz Transputer, 120 ns RAM: 4B jumpered                     |

| 5  | 0 - 0 - 0   | Link speed:                                                                                                  |

| 6  | 0 - 0 - 0   | all Links at 20 MBit/s: 5B,6B,7B                                                                             |

| 7  | 0 - 0 - 0   | all Links at 10 MBit/s:         5A,6A,7A           all Links at 5 MBit/s:         5A,6B,7B                   |

| 8  | 0 - 0 - 0   | Link 0 at 20 MBit/s, Link 1-3 at 10 MBit/s: 5B,6A,7B<br>Link 0 at 10 MBit/s, Link 1-3 at 20 MBit/s: 5B,6B,7A |

| 9  | 0 - 0 - 0   | Link 0 at 10 MBit/s, Link 1-3 at 5 MBit/s: 5A,6B,7A<br>Link 0 at 5 MBit/s, Link 1-3 at 10 MBit/s: 5A,6A,7B   |

| 10 | 0 - 0 - 0   |                                                                                                              |

### Clock frequency T800-Processor:

For 20 MHz Transputer: 8A, 9A, 10A jumpered. All other frequencies the same until final definition.

J105/205/305/405 Analyse:

|   | А     | В   |         |          |    |                       |

|---|-------|-----|---------|----------|----|-----------------------|

|   |       |     | Analyse | enable : | 1A | jumpered              |

| 1 | 0 - 0 | - o | Analyse | disable: | 1B | jumpered<br>jumpered. |

3.

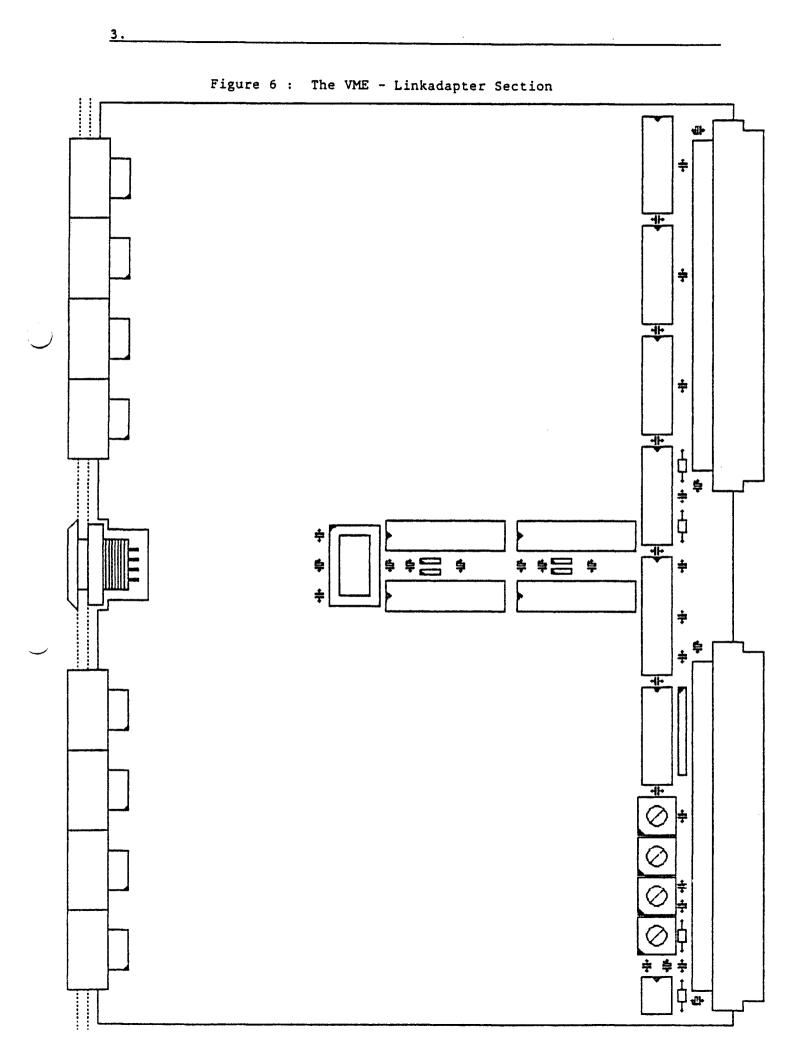

### 3. The VME - Linkadapter Section

3.1. Block Diagram and Description

| Address-<br>decoder | C012 | 0 | <u> </u> | 20 MBit/s<br>Data/Reset | г Boot Sc.¬<br>& COO4<br>г Config                       |

|---------------------|------|---|----------|-------------------------|---------------------------------------------------------|

| Data -              | C012 | 1 |          | **                      | $\begin{array}{c} c c c c c c c c c c c c c c c c c c $ |

| driver              | C012 | 2 |          | *1                      | F- 0004                                                 |

| Reset-<br>logic     | C012 | 3 |          | *                       |                                                         |

|                     |      |   |          |                         |                                                         |

Figure 7: Block Diagram of the VMTM - VME - Linkadapter Section

The VME - link adapter section provides, from the VME-bus side, four IMS C012 link adapters for coupling transputer nodes to a VME system.

The link-adapter IMS C012 is a coupling element between the transputer-communication channels and an 8- bit wide parallel data bus.

On the one hand it has a bi-directional 8-bit I/O-data bus which is coupled to a VME-bus via an appropriate data buffer. On the other hand the integrated link interface enables a serial communication with connected transputers in accordance with the link protocol. These serial data channels can support data transfer rates of 20 Mbit/s (10 Mbit/s jumper-selectable).

The reset functions, which are integral to the link structure according to the MEGAFRAME standard, are supported by the necessary hardware. When a VME- bus has loaded a connected transputer as host transputer via the link adapter, a reset of the appropriate network (e.g. the remaining 3 transputer of the VMTM) to a defined start condition is initiated by the configurer software package.

- 15 -

3.2.

# 3.2. Addressing of the VMTM

|               | Address                                                               | Meaning                                                                                                                                                                                                                        |

|---------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | AM5 - AM0<br>A31 - A8<br>A7 - A4<br>A3 - A0                           | Board Select<br>Board Select<br>Link Select<br>Function Select                                                                                                                                                                 |

| Board Select: | AM5 - AM4                                                             | <pre>3 = Standard Addressing<br/>or<br/>0 = Extended "</pre>                                                                                                                                                                   |

|               | AM3 - AMO                                                             | <pre>D = Supervisory Data     or 9 = Non Privileged Data</pre>                                                                                                                                                                 |

|               | A31 - A28<br>A27 - A24<br>A23 - A20<br>A19 - A16<br>A15 - A8<br>Note: | Addr compare with Select Switch SW4<br>" " SW3<br>" " SW2<br>" " SW1<br>0 = Board Select<br>(Position SW1 - SW4 see figure 8)<br>Standard addressing assumes the<br>adjustment 'F'of the ADDR Select Switches<br>SW4 and SW3 . |

| Link Select:  | Selection of<br>A7 - A4                                               | <pre>the Linkadapter (C012) 8 = Link 3 4 = Link 2 2 = Link 1 1 = Link 0</pre>                                                                                                                                                  |

|               | Note:                                                                 | During write operations up to four<br>links can be simultaneously addressed<br>by adding the corresponding addresses<br>A7 - A4 .                                                                                              |

,

3.2.

Function Select: A3 - A0 F = Stop Reset

| t: | A3  | -  | A0 | F   | =   | Stop    | Reset   |          |        | (RD) / W | /R  |

|----|-----|----|----|-----|-----|---------|---------|----------|--------|----------|-----|

|    |     |    |    | Ď   | =   | Start   | Reset   |          |        | (RD) / W | /R  |

|    |     |    |    | (B) | ) = | Stop    | Reset   |          |        | (RD) / W | /R  |

|    |     |    |    | (9) | ) = | Start   | Reset   |          |        | (RD) / W | /R  |

|    |     |    |    | 7   | #   | Linka   | lapter  | Output   | Stat   | RD / W   | /R  |

|    |     |    |    | 5   | =   | Linka   | lapter  | Input    | Stat   | RD / W   | /R  |

|    |     |    |    | 3   | =   | Linka   | lapter  | Output   | Data   | (RD)/ W  | /R  |

|    |     |    |    | 1   | =   | Linka   | lapter  | Input    | Data   | RD /(V   | /R) |

|    | Not | e: |    | TI  | ne  | funkt   | ions I  | F - 9 ai | re add | lress-   |     |

|    |     |    |    | ti  | riş | gered.  | , that  | means,   | only   | Dummy-   |     |

|    |     |    |    | Da  | ata | i trans | sfer ta | akes pla | ace.   |          |     |

|    |     |    |    | A   | ddı | cesses  | and H   | Read/Wr: | ite N  | íodes i  | In  |

|    |     |    |    |     |     |         |         | not be   |        |          |     |

|    |     |    |    | A   | 11  | acces   | ses are | e 8bit   | (D0-D7 | 7)       |     |

|    |     |    |    |     |     |         |         |          |        |          |     |

- 18 -

3.3.

### 3.3. Programming of the Data Transfer in Polling- Mode

#### Note:

Users with a MEGATOOL transputer development system for OS-9 or UNIX need not care for the following section, as all accesses from host processor are already implemented in the supplied driver software. However, for specialised applictions, the user may wish to directly access the link adapters from the VME master processor.

### Description of the IMS C012 Register Functions:

The four registers are selected by address bits A1 and A2 (see b) 'Addressing of the VMTM'). Should a data byte be registered in the selected register, the data information is taken over by D0 - D7 with /DS0 as well as WRITE and the valid address. In a read cycle a data-byte is put on data lines D0 - D7 with a valid address and /DS0 as well as /WRITE.

The Input-Status-Register (ISR); the Input-Present Statusbit D0 (IP) is set by the link adapter as soon as it has received a data byte via a serial link channel. Upon read-out of the Input-Data-Register the reset of the Input-Present-Statusbit and the output of an Acknowledge via the link channel follows.

The Input-Data-Register (IDR); the Input-Present- Statusbit signals that a data byte has been received via a serial link- channel: this data byte can be read-in by the VME bus; concurrently with the read-in an Acknowledge is transmitted back via a link channel.

The Output-Status-Register (OSR); the Output-ready Statusbit (OR) indicates whether the serial link-channel is ready to transmit a data-byte. Following a reset and the subsequent reception of an Acknowledge via the link-channel a status bit D0 is set. It is reset as soon as a data byte is written into the output data-register.

The Output-Data-Register (ODR); indicates by means of the status- bit D0 that the serial link-channel is primed for transmission and a data byte from the VME bus can be written into the output data- register.

-

3.3.

### Programming examples :

| Register | AddrOffset | D7 | D6   | D5  | D4 | D3   | D2   | D1   | D0 | Access |

|----------|------------|----|------|-----|----|------|------|------|----|--------|

| ISR      | \$0005     | x  | x    | x   | х  | x    | х    | x    | IP | R/W    |

| IDR      | \$0001     | Da | ta-B | yte | In | put  | from | Lin  | k  | Read   |

| OSR      | \$0007     | x  | х    | x   | x  | x    | х    | x    | OR | R/W    |

| ODR      | \$0003     | Da | ta-B | yte | Ou | tput | to l | Link |    | Write  |

Link 0:

Constants :

| INPDATA | EQU | \$01 |

|---------|-----|------|

| OUTDATA | EQU | \$03 |

| INPSTAT | EQU | \$05 |

| OUTSTAT | EQU | \$07 |

| STRTRES | EQU | \$0D |

| STOPRES | EQU | \$0F |

Soft- Reset of the Link- Interface- Adapter :

Entry with A1 : BBK Board Addr. D1 : Link No. ( 0 - 3 )

| MOVE.L | \$10,D2           |   |                             |

|--------|-------------------|---|-----------------------------|

| ASL.L  | D1,D2             |   |                             |

| MOVE.B | STRTRES(A1,D2),D4 | ; | Trigger for Start Softreset |

| BSR    | WAIT              | ; | 5 Microseconds              |

| MOVE.B | STOPRES(A1,D2),D4 | ; | Trigger for Stop Softreset  |

| BSR    | WAIT              | ; | 5 Microseconds              |

| RTS    |                   |   |                             |

.

### 3.3.

Block Send to Transputer Network : Entry with A0 : Memory Startaddr. A1 : BBK Board Addr. D0 : Transfer Count ( 32 Bit ) D1 : Link No. ( 0 - 3 ) MOVE.L \$10,D2 ASL.L D1,D2 LEA OUTDATA(A1,D2),A2 LEA OUTSTAT(A1,D2),A3 MOVE.L \$10,D2 ASL.L D1, D2 CLR D3 ; Bitpointer for Output Ready L0: BTST D3,(A3) ; Output ready ? L0 BEQ MOVE.B (A0)+,(A2) ; Byte to Link Adapter SUBQ #1,D0 ; Block End ? BGT LO L1: BTST D3,(A3) ; await last Acknowledge BEQ L1 RTS

Block Receive from Transputer Network : Entry with A0 : Memory Startaddr. A1 : BBK Board Addr. D0 : Transfer Count ( 32 Bit ) D1 : Link No. ( 0 - 3 ) MOVE.L \$10,D2 ASL.L D1,D2 LEA INPDATA(A1,D2),A2 LEA INPSTAT(A1,D2),A3 CLR ; Bitpointer for Data Present D3 L0: BTST D3,(A3) ; Data present ? BEQ LO MOVE.B (A2),(A0)+ ; Byte from Link Adapter SUBQ #1,D0 ; Block End ? BGT L0 RTS

3.4.

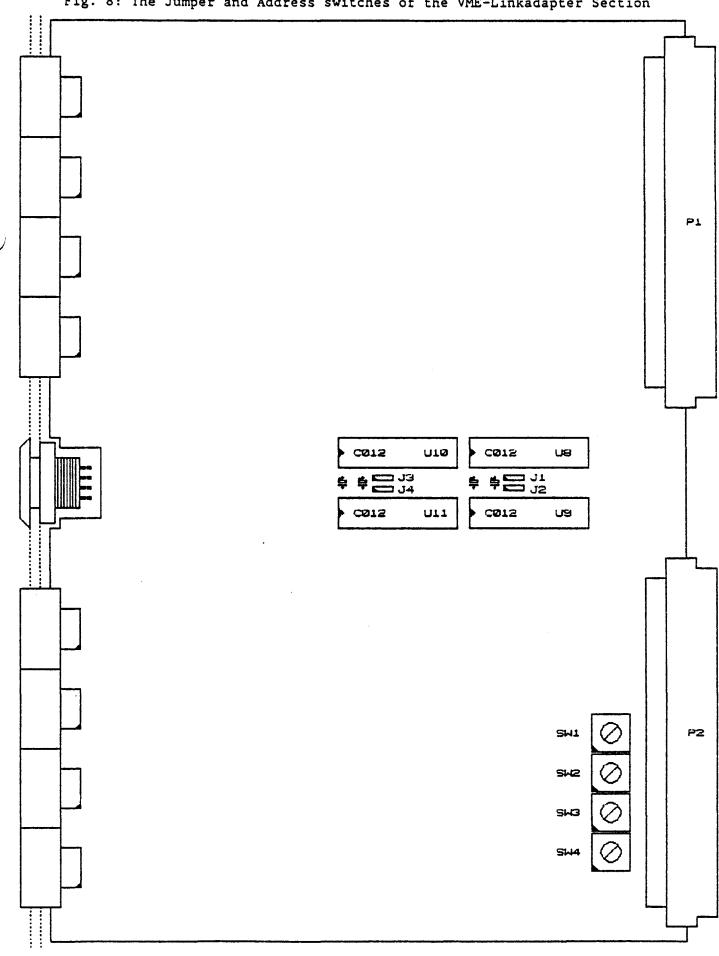

3.4. Jumper Allocation and Address switches

J1, J2, J3 and J4 Link speed of the Linkadapter (C012):

AB10 MBit/s :1Bjumpered1o - o - o20 MBit/s :1Ajumpered

(Position J1 - J4 see fig. 8)

Correspondence Linkadapter-Channel <-> Jumper:

0 1 -1 2 -2 -3 \_ 3 4

Fig. 8: The Jumper and Address switches of the VME-Linkadapter Section

- 24 -

### 3.5.\_\_\_\_

3.5. PIN-out of the 96-way DIN Connectors

DIN-Connector P1:

|    | с                                     | b                                       | a           |

|----|---------------------------------------|-----------------------------------------|-------------|

| 1  |                                       |                                         |             |

| 2  |                                       |                                         |             |

| 2  |                                       |                                         |             |

|    |                                       |                                         |             |

| 4  |                                       |                                         |             |

| 5  |                                       |                                         |             |

| 6  | •••••••                               |                                         |             |

| 7  |                                       |                                         |             |

| 8  |                                       |                                         | D7          |

| 9  | GND                                   |                                         | GND         |

| 10 |                                       |                                         |             |

| 11 | GND                                   |                                         |             |

| 12 | /SYSRESE1                             | Τ                                       | /DS1        |

| 13 | /LWORD                                |                                         | /DS0        |

| 14 | •                                     |                                         | ,           |

| 15 |                                       |                                         | 1           |

| 16 |                                       |                                         | /DTACK      |

| 17 |                                       |                                         | GND         |

| 18 | · · · · · · · · · · · · · · · · · · · | ······································  | /AS         |

| 19 |                                       |                                         | GND         |

| 20 |                                       |                                         | /IACK       |

| 20 | A17                                   | ····· GND ····                          | ···· / IAOK |

|    |                                       |                                         |             |

| 22 | A16                                   |                                         |             |

| 23 |                                       | GND                                     |             |

| 24 |                                       |                                         |             |

| 25 |                                       |                                         |             |

| 26 | A12 .                                 |                                         | A5          |

| 27 | All .                                 |                                         | A4          |

| 28 | A10                                   |                                         | A3          |

| 29 | A9                                    |                                         | A2          |

| 30 |                                       |                                         |             |

|    | A8                                    |                                         | A1          |

| 31 | A8                                    | • • • • • • • • • • • • • • • • • • • • | A1          |

а

### 3.5.

### DIN-Connector P2:

|                                                    | с                                      | Ъ                                      |

|----------------------------------------------------|----------------------------------------|----------------------------------------|

| 1<br>2<br>3                                        |                                        | VCC<br>GND                             |

| 4<br>5<br>7<br>8<br>9                              |                                        | A24<br>A25<br>A26<br>A27<br>A28<br>A29 |

| 10<br>11<br>12<br>13                               | · · · · · · · · · · · · · · · · · · ·  | A30<br>A31<br>GND<br>VCC               |

| 14<br>15<br>16<br>17<br>18<br>19<br>20<br>21       |                                        |                                        |

| 22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>30 | •••••••••••••••••••••••••••••••••••••• | GND                                    |

| 31<br>32                                           |                                        | GND<br>VCC                             |

4. The Link switch Section

<u>4.</u>

### 4.1. Functional Description

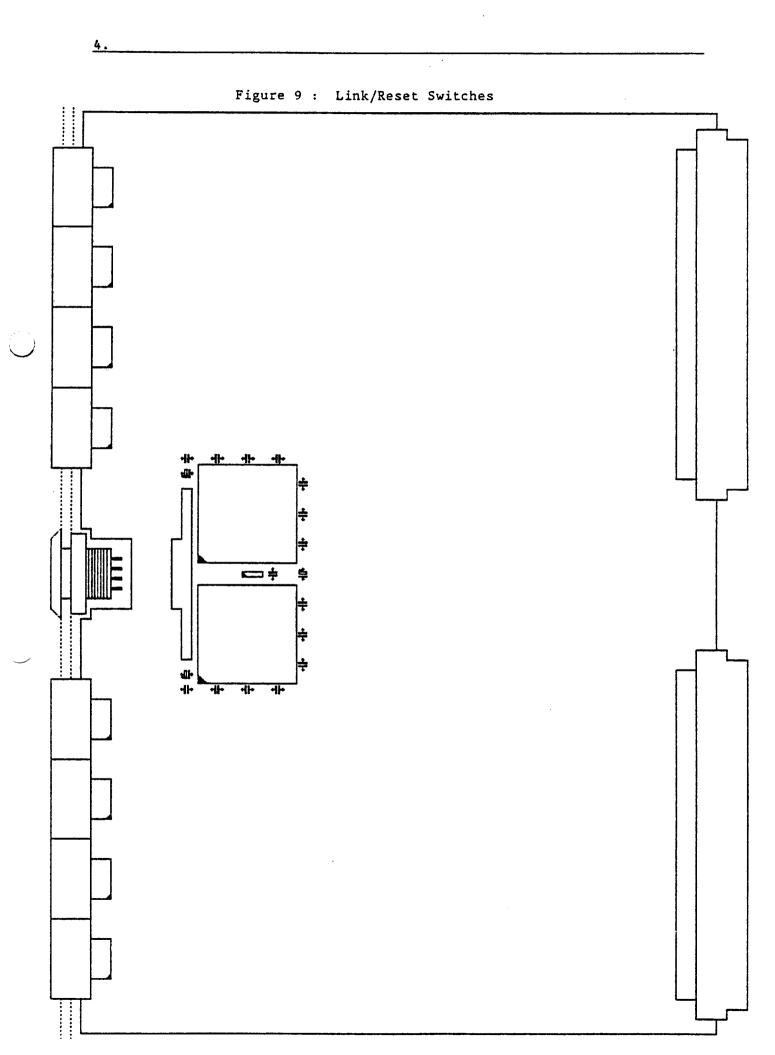

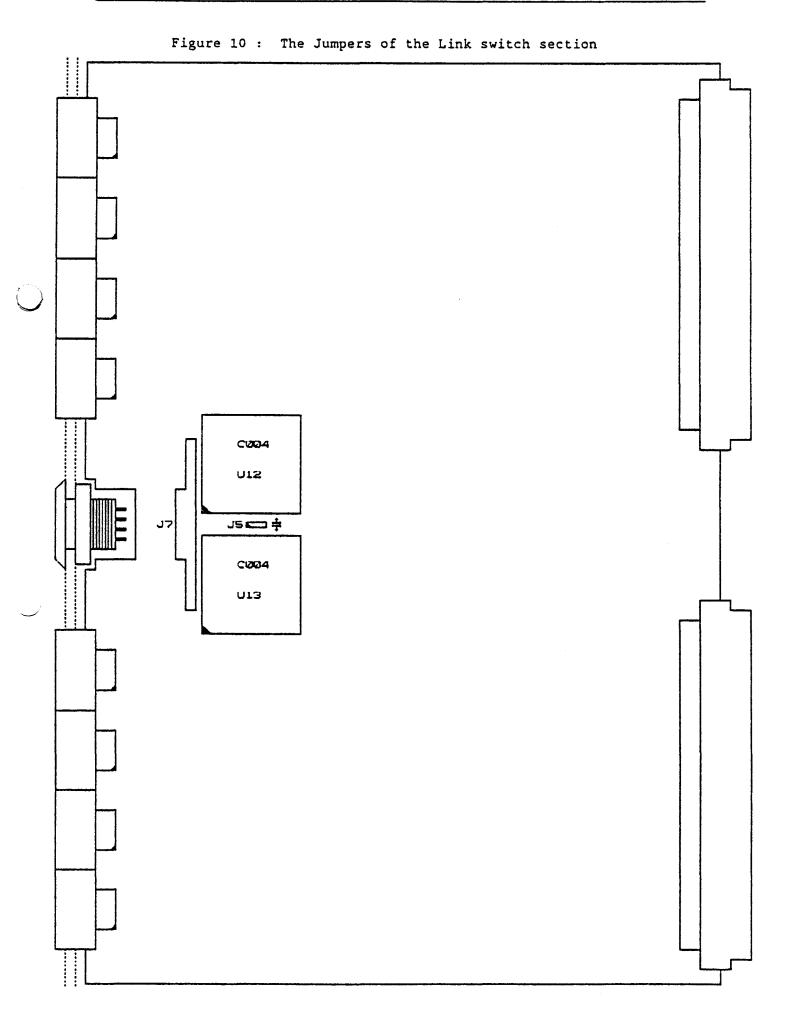

Through the employment of electronic link switches 'IMS COO4' the user is able to switch as desired to the various on-board functions. The configuration is the result of a suitable initialisation of the link switches via their configuration link.

As a reset is implemented in parallel to every link function in accordance with the Megaframe specifications, this reset function is automatically carried out by a second switch. In this manner both switches are initialised in parallel.

The link switch 'IMS COO4' can handle data rates of 0 to 20 MBit/s (10 MBit/s; see J5). The configuration link works with 10 or 20 MBit/s (selectable by jumper J5).

4.2.

### 4.2. Configuration

The link switch IMS C004 is internally constructed as a 32 x 32 ways to 1 multiplexer. Each of these multiplexers is controlled by a 6 bit register. An input is selected by 5 of the bits as a data source for a corresponding output; the 6th bit will enable or disable the connection. These registers can be written into, and read from via the C004's configuration link.

The inputs and outputs are numbered from 0 to 31. The configuration code consists of one, two or three bytes. The configuration information which is sent to the C004 configuration link contains then the following tabulated information:

| Information (Bytes) | Function                                                                                                                                                                      |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [0][input][output]  | Connects 'input' to 'output                                                                                                                                                   |

| [1][link1][link2]   | 'linkl'is connected to 'link2'.This connects<br>the input from 'link1' to the output of<br>'link2' and vice versa.                                                            |

| [2][output]         | Determines which input is connected to the<br>'output'. The highest value bit of the byte<br>indicates whether the connection is made (1)<br>or open (0).                     |

| [3]                 | This byte must be sent at the end of every<br>configuration sequence. The appropriate<br>connections are made and the data trans-<br>mission can be commenced over this link. |

| [4]                 | Resets the switch. All connections are dis-<br>abled and the outputs returned to ground.                                                                                      |

| [5][output]         | The 'output' is opened.                                                                                                                                                       |

| [6][link1][link2]   | The connection between the output 'linkl'<br>and the input 'link2' is opened.<br>Correspondingly, the output 'link2'is opened<br>from the input 'link1'.                      |

- 29 -

4.2.

The following table contains the arrangement of the C004 link- channel numbers and the corresponding link functions on the VMTM-board:

| Link-Channel No. | On-Board           | Link-Function |

|------------------|--------------------|---------------|

| [0]              | Transputer Section | 'A' Link O    |

| [1]              | 17                 | Link 1        |

| [2]              | ۲                  | Link 2        |

| [3]              | ۲                  | Link 3        |

| [4]              | Transputer Section | 'B' Link O    |

| [5]              | ."                 | Link 1        |

| [6]              | ۲                  | Link 2        |

| [7]              | ,                  | Link 3        |

| [8]              | Transputer Section | 'C' Link O    |

| [9]              | "                  | Link 1        |

| [10]             | H                  | Link 2        |

| [11]             | 11                 | Link 3        |

| [12]             | Transputer Section | 'D' Link 0    |

| [13]             | *                  | Link 1        |

| [14]             | Ħ                  | Link 2        |

| [15]             | Ŧ                  | Link 3        |

| :                |                    |               |

4.2.

| Link-Channel-No. | On-Board Link-                         | Function |

|------------------|----------------------------------------|----------|

| [16]             | external Link                          | St.9     |

| [17]             | nc                                     |          |

| [18]             | nc                                     |          |

| [19]             | nc                                     |          |

| [20]             | Link-Adapter Section                   | Link 0   |

| [21]             | H                                      | Link 1   |

| [22]             | Η                                      | Link 2   |

| [23]             | H                                      | Link 3   |

| [24]             | external Link                          | St.5     |

| [25]             | n                                      | St.6     |

| [26]             | ······································ | St.7     |

| [27]             | ······································ | St.8     |

| [28]             | n n                                    | St.2     |

| [29]             | ······································ | St.1     |

| [30]             | M                                      | St.3     |

| [31]             | η                                      | St.4     |

,

.

- 30 -

•

4.3.

### 4.3. The Configuration-Jumper

Jumper J7 determines wich source will load the section 'A' transputer via its link 0. Jumper J7 selects the configuration source as well. The following possibilities are available:

J7 Configuration

|    | A   | В       | a)   | The booting of the transputer is done<br>by the VME-Bus via the CO12 Link-Adap-                       |

|----|-----|---------|------|-------------------------------------------------------------------------------------------------------|

| 1  |     | 0 - 0   |      | ter link 0, and                                                                                       |

| 2  |     | 0 — 0   | i.   | the transputer configures the COO4 via its link 1:                                                    |

| 3  | -   | 0 - 0   |      | 1B, 3B, 10B, 11B, 12B, 13B, 14B, 15B, 16B,                                                            |

| 4  |     | 0 - 0   |      |                                                                                                       |

| 5  |     | 0 - 0   |      | 6A, 9A jumpered;                                                                                      |

| 6  | 0 - | - 0 - 0 | ii.  | the configuration of the C004 is enabled                                                              |

| 7  | 0 - | - 0 - 0 |      | via the VME-Bus by means of the CO12<br>link-adapter link 1:                                          |

| 8  | 0 - | - 0 - 0 |      | 3B, 4B, 7B, 9B, 10B, 11B, 12B, 13B, 14B,                                                              |

| 9  | o - | - 0 - 0 |      | 15B, 16B, 17B jumpered;                                                                               |

| 10 | 0 - | - 0 - 0 |      |                                                                                                       |

| 11 | 0 - | - 0 - 0 | iii. | a source external to the VMTM- Board<br>configures the COO4 by use of the external<br>link-plug St.1: |

| 12 | 0 - | - 0 - 0 |      | 1B, 3B, 4B, 6B, 8B, 10B, 11B, 12B, 13B,                                                               |

| 13 | 0 - | - 0 - 0 |      |                                                                                                       |

| 14 |     | o — o   |      | 16B, 17B jumpered.                                                                                    |

| 15 |     | 0 - 0   |      |                                                                                                       |

| 16 |     | 0 — 0   |      |                                                                                                       |

| 17 |     | 0 - 0   |      |                                                                                                       |

| 18 |     | 0 - 0   |      | >                                                                                                     |

4.3.

|    | A   |         | b)     | The transputer is loaded via the external link-plug St.9                         |

|----|-----|---------|--------|----------------------------------------------------------------------------------|

| 1  |     | 0 - 0   |        | (8-way round socket), and                                                        |

| 2  |     | 0 - 0   | i.     | the transputer configures the COO4 via<br>its link l:                            |

| 3  |     | 0 - 0   | i<br>I |                                                                                  |

| 4  |     | 0 - 0   |        | 6A, 9A, 10A, 11A, 12A, 13A,                                                      |

| 5  |     | 0 - 0   |        | 1B, 2B, 14B, 15B jumpered;                                                       |

| 6  | o - | - 0 - 0 | ii.    | the configuration of the C004 is enabled<br>via the VME-Bus by means of the C012 |

| 7  | 0 - | - 0 - 0 |        | link-adapter link 1:                                                             |

| 8  | 0 - | - 0 - 0 |        | 10A, 11A, 12A, 13A,                                                              |

| 9  | o - | - 0 - 0 |        | 2B, 4B, 7B, 9B, 14B, 15B, 17B jumpered;                                          |

| 10 | o - | - 0 - 0 | iii.   | a source external to the VMTM- Board                                             |

| 11 | o - | - 0 - 0 |        | configures the COO4 by use of the external<br>link- plug St.1:                   |

| 12 | 0 - | - 0 - 0 |        | 10A, 11A, 12A, 13A,                                                              |

| 13 | o - | - 0 - 0 |        |                                                                                  |

| 14 |     | 0 - 0   |        | 1B, 2B, 4B, 6B, 8B, 17B jumpered.                                                |

| 15 |     | 0 - 0   |        |                                                                                  |

| 16 |     | 0 - 0   |        |                                                                                  |

| 17 |     | 0 - 0   |        |                                                                                  |

| 18 |     | 0 - 0   |        | >                                                                                |

•

.

- 32 -

В A 0 - 0 1 2 0 - 0 3 0 - 0 4 o - o5 0 - 0 6 0 - 0 - 0 7 0 - 0 - 08 0 - 0 - 09 0 - 0 - 010 0 - 0 - 0 11 0 - 0 - 012 0 - 0 - 0 13 0 - 0 o — 14 o — o 15 0 - 0 16 0 - 0 17 o — o 18 o — o

the configuration of the C004 is enabled via the VME-Bus by means of the C012 link-adapter link 1: i. 2B, 3B, 4B, 5B, 7B, 9B, 14B, 15B, 16B, 17B, 18B jumpered; a source external to the VMTM- Board configures the C004 by use of the external link- plug St.1: ii. 1B, 2B, 3B, 4B, 5B, 6B, 8B, 16B, 17B, 18B jumpered.

The transputer of the section 'A' is exclusively accessed via the link switch, and .. c)

- 33 -

4.3.

# 4.3.

# J5 Configuration-link transmission speed:

|   | A B       | 10 MBit/s : | 1B | jumpered |

|---|-----------|-------------|----|----------|

| 1 | 0 - 0 - 0 | 20 MBit/s : | 1A | jumpered |

•

- 36 -

5.

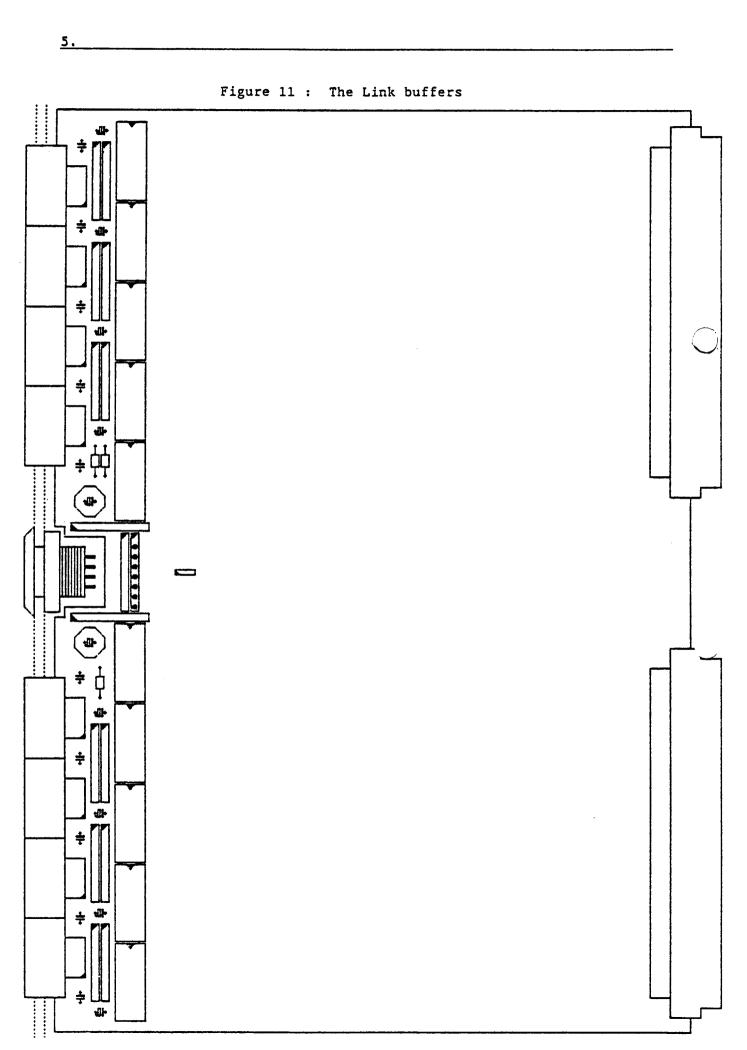

### 5. The Link buffers

In order to be able to employ the VMTM module in larger networks, nine external link channels have been provided (St.1 ... St.9). In the link buffer section, the internal TTL link channel signals are transformed to the RS422 standard. This measure ensures a considerably higher security of the data transmission over large distances.

### 5.1. Local Connections with other Modules

Link cabling between several boards within the equipment is effected by user operated flat-cable connections located on the front panel.

10-way connector pin-out (St. 1 -8)

| RESET-IN +  | 1 | 0 0 | 2  | RESET-IN -  |

|-------------|---|-----|----|-------------|

| LINK-IN +   |   |     |    |             |

|             |   |     | 6  |             |

| LINK-OUT -  | 7 | 0 0 | 8  | LINK-OUT +  |

| RESET-OUT - | 9 | 0 0 | 10 | RESET-OUT + |

- 38 -

5.2.

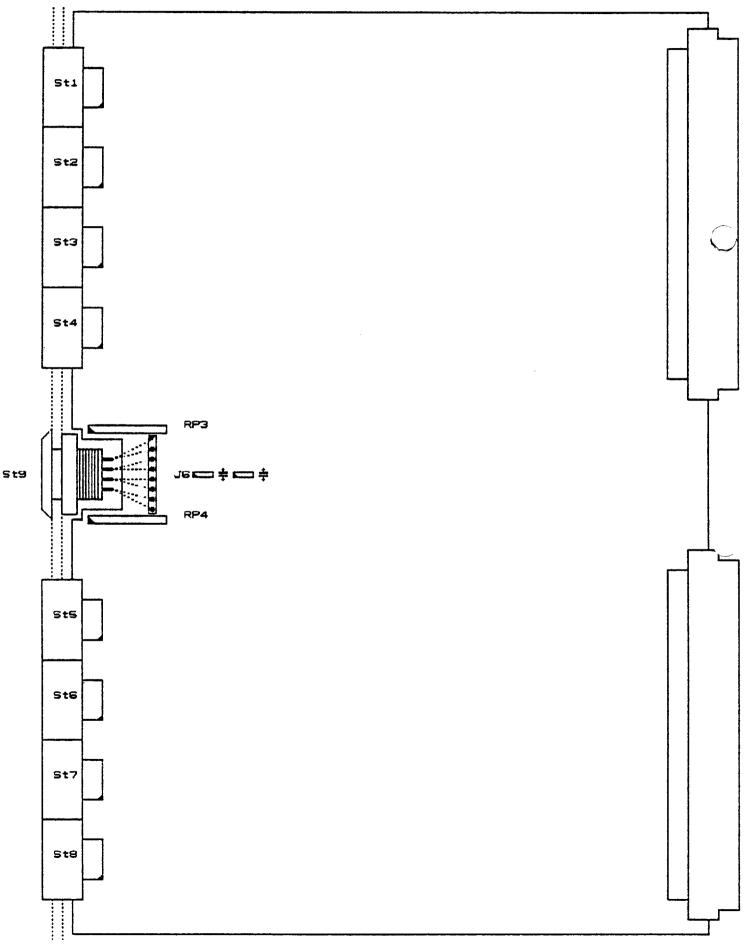

#### 5.2. Connections in distributed Systems

Screened twisted-pair cables are used for the links in the distributed transputer systems. In the VMTM module these connections are made via the link-plug St.9. Distances of up to 10 m may be covered using a transmission rate of 20 Mbit/s. Greater distances may be covered by setting the transmission rate to 10 or 5 Mbit/s.

Furthermore it is possible to adopt the INMOS-Standard via this link channel.

This is accomplished by changing the resister-network position from 'RP3' over to 'RP4':

Position 'RP3': MEGAFRAME - Standard Position 'RP4': INMOS - Compatibily.

Furthermore, jumper J6 can be configured accordingly:

J6 Standard choice:

|   | A B       | MEGAFRAME - Standard: | 1A | jumpered |

|---|-----------|-----------------------|----|----------|

| 1 | 0 - 0 - 0 | INMOS -Compatibility: | 1B | jumpered |

Using the INMOS- adaption the maximal transmission distance is reduced to 1.50 m!

### St. 9

8-way round socket pin-out ( Lemosa EGG 2B308CNL)

| o   | 0 | 0   |                   |

|-----|---|-----|-------------------|

| 2   | 1 | 8   |                   |

| o 3 |   | 7 o | viewed from front |

| 4   | 5 | 6   |                   |

| 0   | 0 | 0   |                   |

| MEGAFRAME-Standard I                                                                                                         | NMOS-Compatibility                                                          |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Pin Function                                                                                                                 | Pin Function                                                                |

| 1 RESET-OUT +<br>2 RESET-OUT -<br>3 LINK-OUT +<br>4 LINK-OUT -<br>5 LINK-IN -<br>6 LINK-IN +<br>7 RESET-IN -<br>8 RESET-IN + | <pre>1 nc 2 RESET-OUT 3 LINK-OUT 4 GND 5 nc 6 LINK-IN 7 RESET-IN 8 nc</pre> |

.

Figure 12 : The Jumpers of the Link buffer Section

6.

6. Technical Data

VME- Spec. Rev.C: IEC 821, IEEE P1014/D 1.0 Modes of operation: A24/A32/D8

Link-buffers: 9 \* RS-422, link I/Os match cable impedance of 100 Ohm, open link inputs have logic zero level (no signal)

Board: standard double euro card 233.5 \* 160 mm ,  $\cdot$ 7-layer multilayer DC-Voltage-Supply: 5.0 V ± 5 $\chi$

max. Current: 4.5 A