# GRAPHICS DATABOOK

Second Edition 1990

INMOS is a member of the SGS-THOMSON Microelectronics Group

# **INMOS Databook series**

Transputer Databook Military and Space Transputer Databook Transputer Development and *i***q** Systems Databook Memory Databook Graphics Databook Digital Signal Processing Databook Transputer Applications Notebook: Architecture and Software Transputer Applications Notebook: Systems and Performance

Copyright © INMOS Limited 1990

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate; however, no responsibility is assumed for its use, nor for any infringement of patents or other rights of third parties resulting from its use. No licence is granted under any patents, trademarks or other rights of INMOS.

INMOS is a member of the SGS-THOMSON Microelectronics Group.

INMOS document number: 72 TRN 204 01

| 1  | INMOS                                                       | 1   |

|----|-------------------------------------------------------------|-----|

| 2  | Graphics overview                                           | 5   |

| 3  | IMS G171 high performance colour look-up table              | 13  |

| 4  | IMS G176/176L high performance colour look-up table         | 37  |

| 5  | IMS G178 high performance colour look-up table              | 63  |

| 6  | IMS G300B colour video controller                           | 87  |

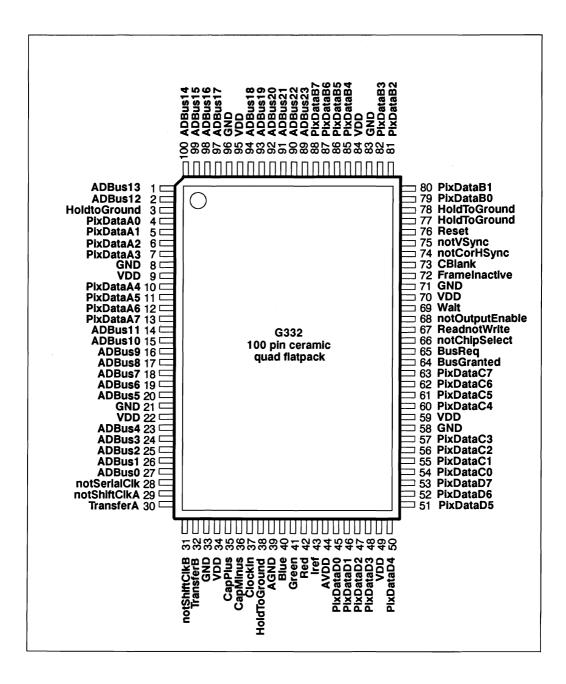

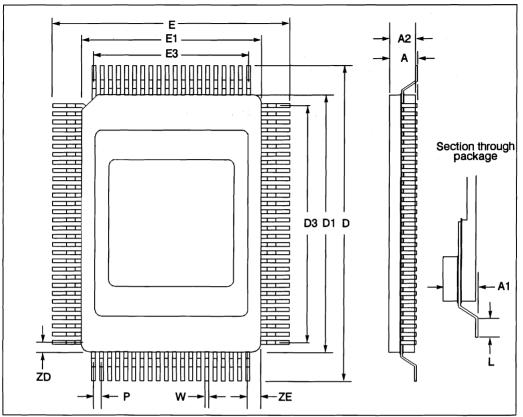

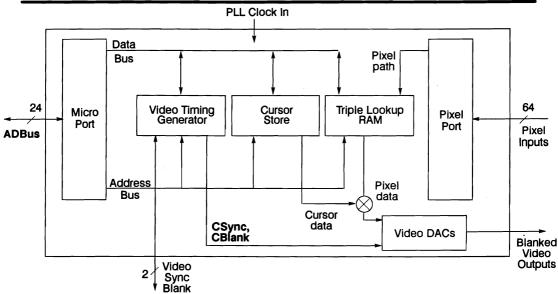

| 7  | IMS G332 colour video controller                            | 139 |

| 8  | IMS G364 colour video controller                            | 171 |

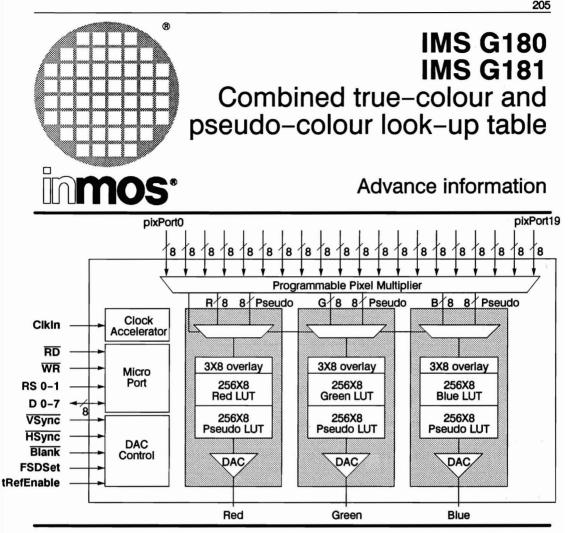

| 9  | IMS G180/G181 combined true and pseudo-colour look-up table | 205 |

| 10 | Designing with INMOS CLUTS                                  | 219 |

| 11 | Designing with INMOS CVCs                                   | 233 |

| A  | Quality and reliability                                     | 243 |

| в  | Graphics glossary                                           | 249 |

# Contents

|   | Prefac | Preface xi  |                                               |    |  |  |  |

|---|--------|-------------|-----------------------------------------------|----|--|--|--|

| 1 | INMO   | INMOS       |                                               |    |  |  |  |

|   | 1.1    | Introductio | on                                            | 2  |  |  |  |

|   | 1.2    |             | n                                             | 2  |  |  |  |

|   |        |             |                                               |    |  |  |  |

|   | 1.3    | -           | nd reliability                                | 3  |  |  |  |

|   | 1.4    | Future dev  |                                               | 3  |  |  |  |

|   |        | 1.4.1       | Research and development                      | 3  |  |  |  |

|   |        | 1.4.2       | Process developments                          | 3  |  |  |  |

| 2 | Grap   | hics ove    | erview                                        | 5  |  |  |  |

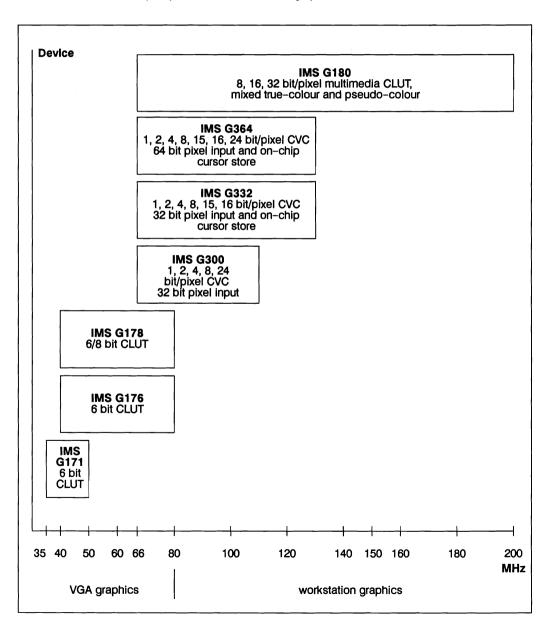

|   | 2.1    | The advar   | ncing graphics market                         | 6  |  |  |  |

|   | 2.2    |             | d colour representation                       | 6  |  |  |  |

|   |        | 2.2.1       | Where does a CLUT fit into a graphics system? | 7  |  |  |  |

|   | 2.3    |             | S CLUT history                                | 7  |  |  |  |

|   |        | 2.3.1       | The INMOS VGA compatible CLUT range           | 8  |  |  |  |

|   |        | 2.3.2       | Choosing your device - functionality          | 8  |  |  |  |

|   |        | 2.3.3       | Choosing your CLUT – speed selection          | 8  |  |  |  |

|   |        | 2.3.4       | Colour Video Controllers                      | 9  |  |  |  |

|   |        | 2.3.5       | High-Performance CLUTs                        | 10 |  |  |  |

| 3 | IMS    | G171 hig    | h performance colour look–up table            | 13 |  |  |  |

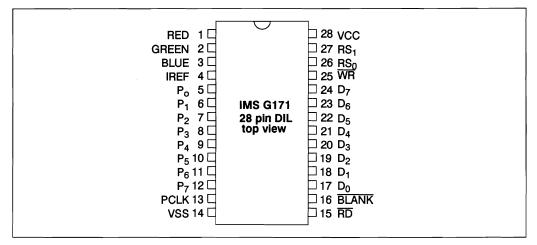

|   | 3.1    | Pin desig   | nations                                       | 14 |  |  |  |

|   |        | 3.1.1       | Pixel interface                               | 14 |  |  |  |

|   |        | 3.1.2       | Analogue interface                            | 14 |  |  |  |

|   |        | 3.1.3       | Microprocessor interface                      | 15 |  |  |  |

|   |        | 3.1.4       | Power supply                                  | 15 |  |  |  |

|   |        | 3.1.5       | Internal registers                            | 16 |  |  |  |

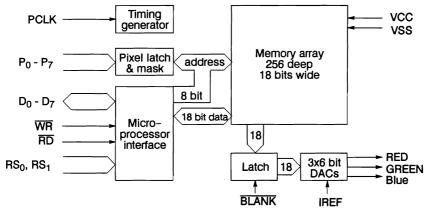

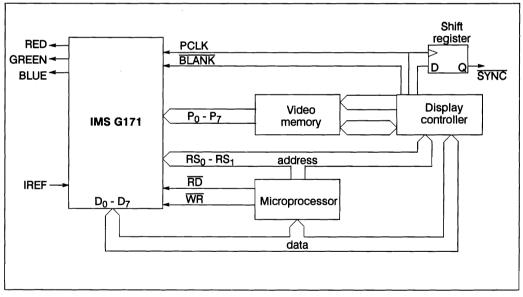

|   | 3.2    | Device de   | escription                                    | 17 |  |  |  |

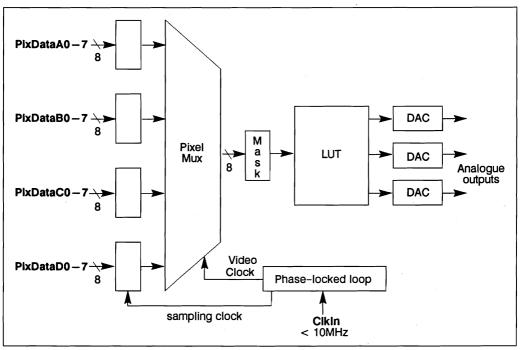

|   |        | 3.2.1       | Video path                                    | 17 |  |  |  |

|   |        | 3.2.2       | Analogue outputs                              | 18 |  |  |  |

|   |        | 3.2.3       | Microprocessor interface                      | 18 |  |  |  |

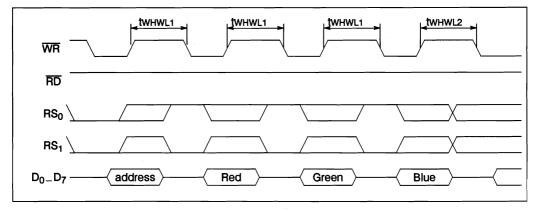

|   |        | 3.2.4       | Writing to the look-up table                  | 18 |  |  |  |

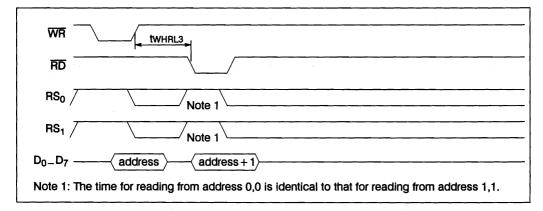

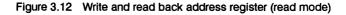

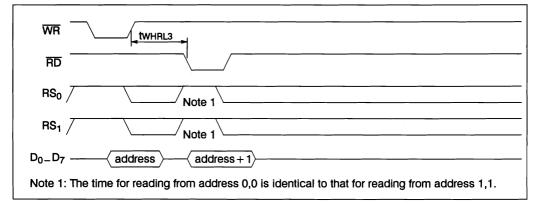

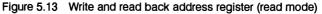

|   |        | 3.2.5       | Reading from the look-up table                | 19 |  |  |  |

|   |        | 3.2.6       | Asynchronous look-up table access             | 19 |  |  |  |

|   |        | 3.2.7       | The Pixel Mask register                       | 19 |  |  |  |

|   | 3.3    | Electrical  | specifications                                | 19 |  |  |  |

|   |        | 3.3.1       | Absolute maximum ratings                      | 19 |  |  |  |

|   |        | 3.3.2       | DC operating conditions                       | 20 |  |  |  |

|   |        | 3.3.3       | DAC characteristics                           | 21 |  |  |  |

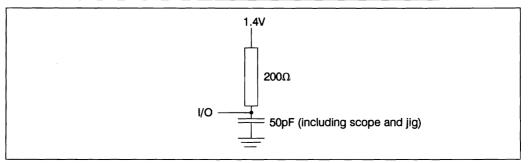

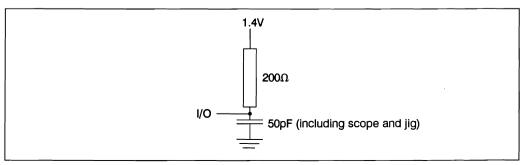

|   |        | 3.3.4       | AC test conditions                            | 21 |  |  |  |

|   |        | 3.3.5       | Capacitance                                   | 22 |  |  |  |

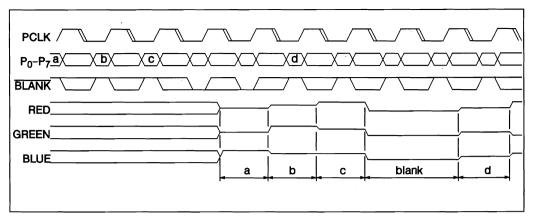

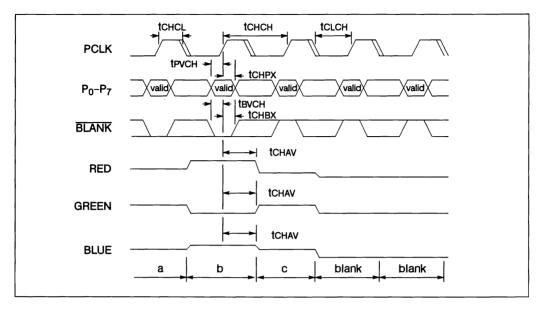

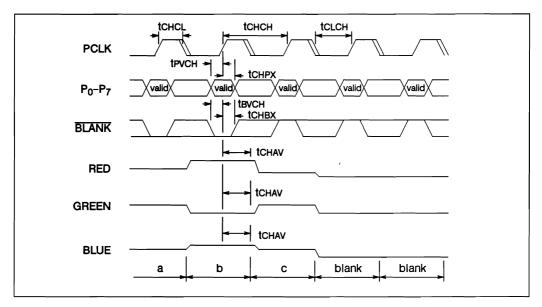

|   |        | 3.3.6       | Video operation                               | 22 |  |  |  |

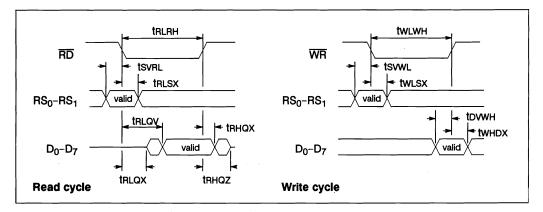

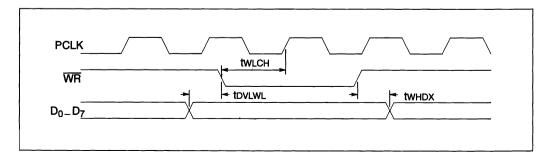

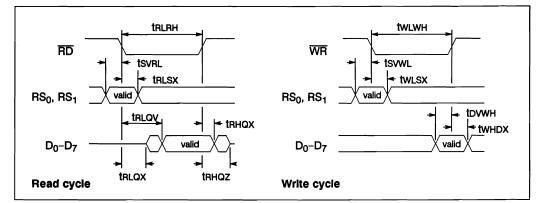

|   | _      | 3.3.7       | Microprocessor interface operation            | 24 |  |  |  |

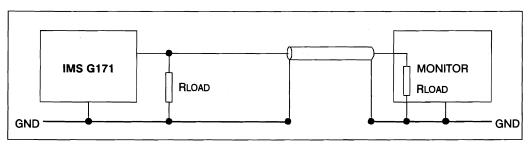

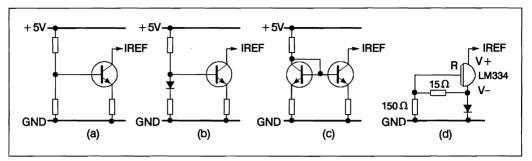

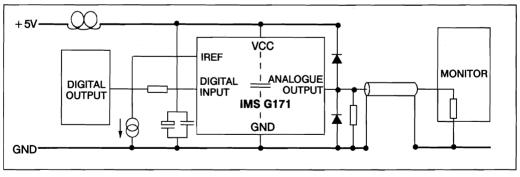

|   | 3.4    | Designing   | g with the IMS G171                           | 28 |  |  |  |

|   |        | 3.4.1       | Board layout – general                        | 28 |  |  |  |

|   |        | 3.4.2       | Power supply decoupling                       | 28 |  |  |  |

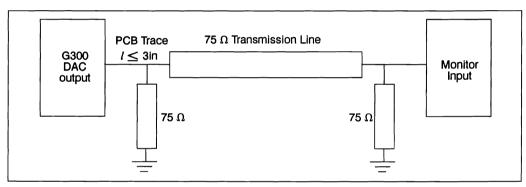

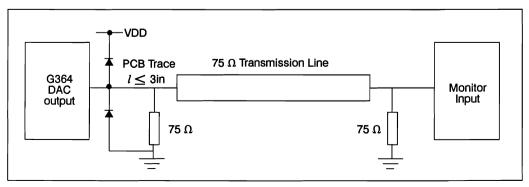

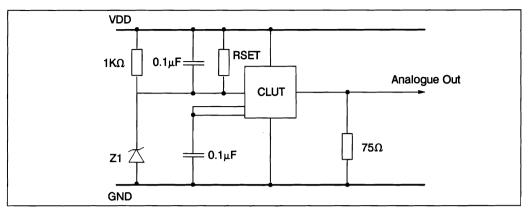

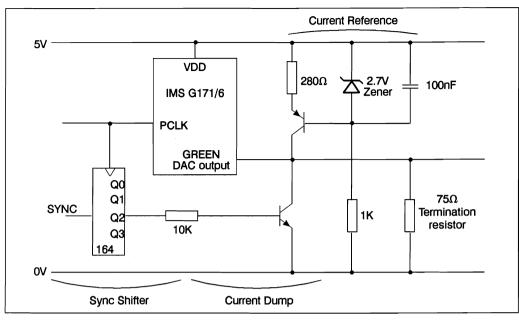

|   |        | 3.4.3       | Analogue output - line driving                | 28 |  |  |  |

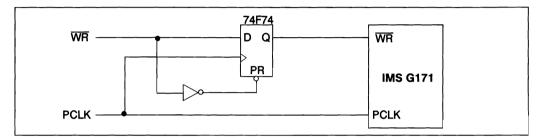

|   | 3.5         | 3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.4.8 | Analogue output – protection         Digital input termination         Current reference – design         Current reference – decoupling         Pixel Mask register synchronisation         specifications | 29<br>29<br>29<br>30<br>30<br>30 |

|---|-------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

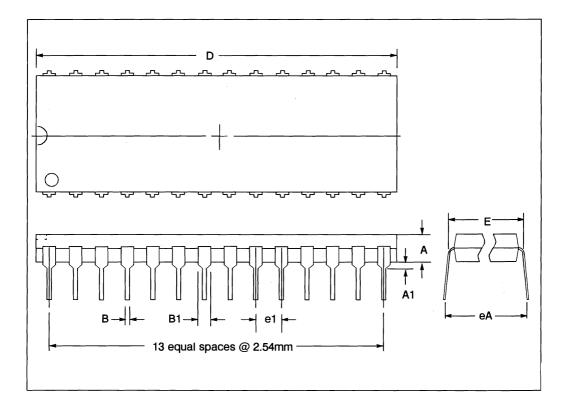

|   | 3.5         | 3.5.1<br>3.5.2                            | 28 pin dual-in-line package<br>Ordering information                                                                                                                                                         | 32<br>32<br>35                   |

| 4 | IMS         | G176/17                                   | 76L high performance colour look-up table                                                                                                                                                                   | 37                               |

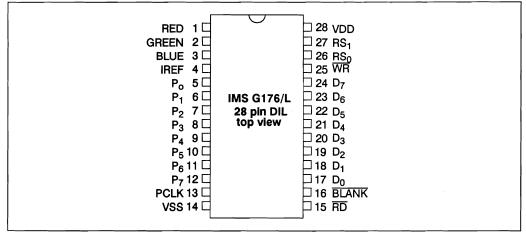

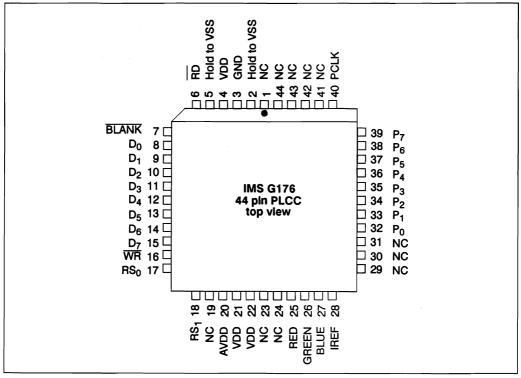

|   | 4.1         | Pin desig                                 | gnations                                                                                                                                                                                                    | 38                               |

|   |             | 4.1.1                                     | Pixel interface                                                                                                                                                                                             | 38                               |

|   |             | 4.1.2                                     | Analogue interface                                                                                                                                                                                          | 38                               |

|   |             | 4.1.3                                     |                                                                                                                                                                                                             | 39                               |

|   |             | 4.1.4                                     | Power supply                                                                                                                                                                                                | 39                               |

|   |             | 4.1.5                                     | Internal registers                                                                                                                                                                                          | 40                               |

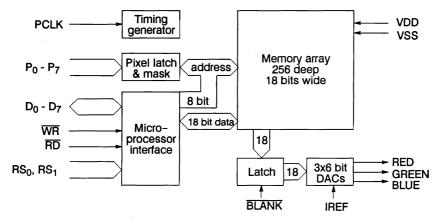

|   | 4.2         | Device d                                  | escription                                                                                                                                                                                                  | 41                               |

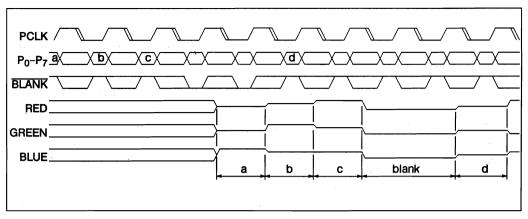

|   |             | 4.2.1                                     | Video path                                                                                                                                                                                                  | 41                               |

|   |             | 4.2.2                                     | Analogue outputs                                                                                                                                                                                            | 42                               |

|   |             | 4.2.3                                     | Microprocessor interface                                                                                                                                                                                    | 42                               |

|   |             |                                           | Writing to the look-up table                                                                                                                                                                                | 42                               |

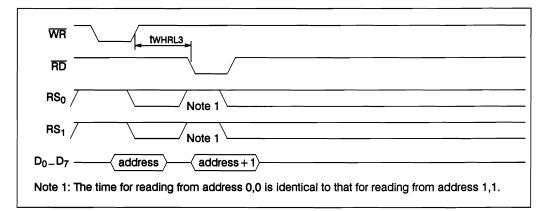

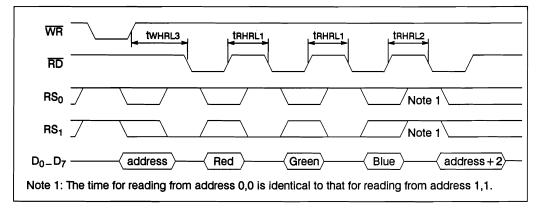

|   |             |                                           | Reading from the look-up table                                                                                                                                                                              | 43                               |

|   |             |                                           | Asynchronous microprocessor interface access                                                                                                                                                                | 43                               |

|   |             |                                           | The Pixel Mask register                                                                                                                                                                                     | 43                               |

|   | 4.3         | Electrical                                | specifications                                                                                                                                                                                              | 43                               |

|   |             | 4.3.1                                     | Absolute maximum ratings                                                                                                                                                                                    | 43                               |

|   |             | 4.3.2                                     | DC operating conditions                                                                                                                                                                                     | 44                               |

|   |             |                                           | DC electrical characteristics                                                                                                                                                                               | 44                               |

|   |             | 4.3.3                                     | Power down                                                                                                                                                                                                  | 45                               |

|   |             | 4.3.4                                     | DAC characteristics                                                                                                                                                                                         | 46                               |

|   |             | 4.3.5                                     | AC test conditions                                                                                                                                                                                          | 46                               |

|   |             | 4.3.6                                     |                                                                                                                                                                                                             | 47                               |

|   |             | 4.3.7                                     |                                                                                                                                                                                                             | 47                               |

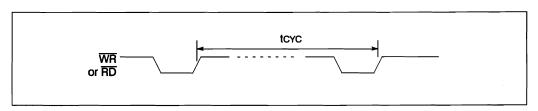

|   |             | 4.3.8                                     | Microprocessor interface operation                                                                                                                                                                          | 49                               |

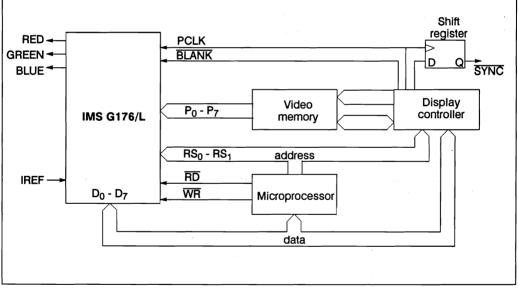

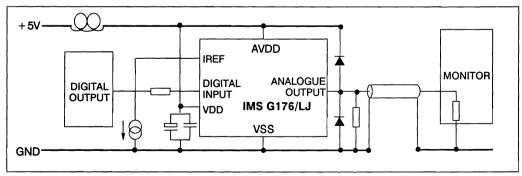

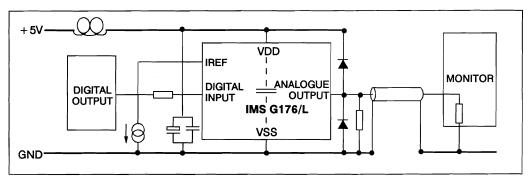

|   | 4.4         | Designin                                  | g with the IMS G176/L                                                                                                                                                                                       | 53                               |

|   |             | 4.4.1                                     | Board layout – general                                                                                                                                                                                      | 53                               |

|   |             | 4.4.2                                     | Power supply decoupling                                                                                                                                                                                     | 53                               |

|   |             | 4.4.3                                     | Analogue output – line driving                                                                                                                                                                              | 53                               |

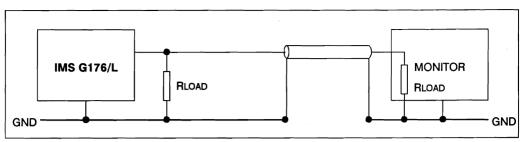

|   |             |                                           | Double termination                                                                                                                                                                                          | 53                               |

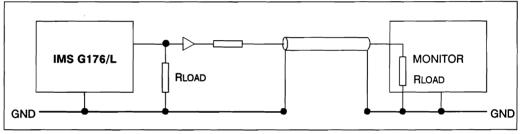

|   |             |                                           | Buffered signal                                                                                                                                                                                             | 54                               |

|   |             | 4.4.4<br>4.4.5                            | Analogue output – protection                                                                                                                                                                                | 54<br>54                         |

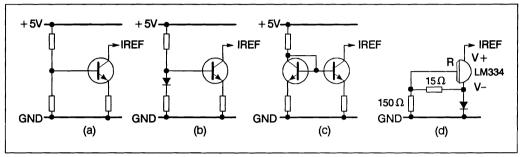

|   |             | 4.4.5<br>4.4.6                            | Digital input termination                                                                                                                                                                                   | 54<br>54                         |

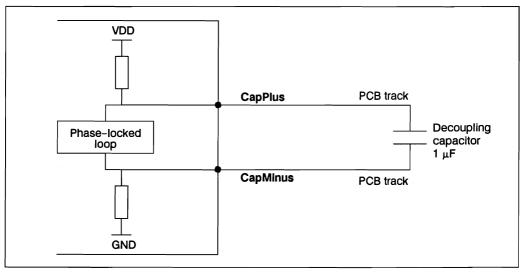

|   |             | 4.4.7                                     | Current reference – decoupling                                                                                                                                                                              | 55                               |

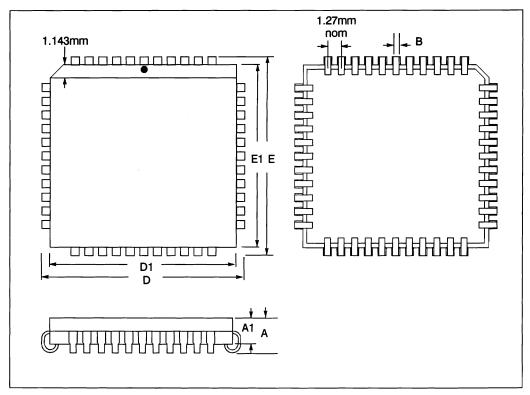

|   | 4.5         |                                           | specifications                                                                                                                                                                                              | 56                               |

|   | ч. <b>О</b> |                                           |                                                                                                                                                                                                             |                                  |

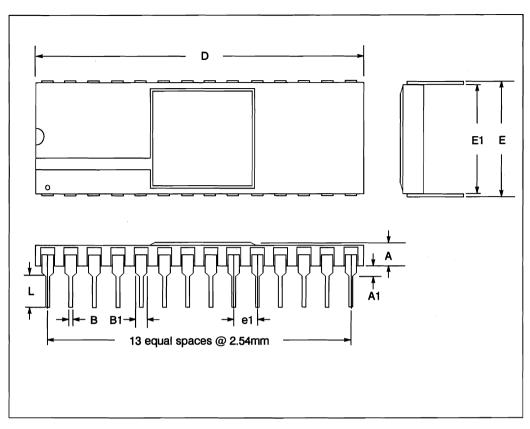

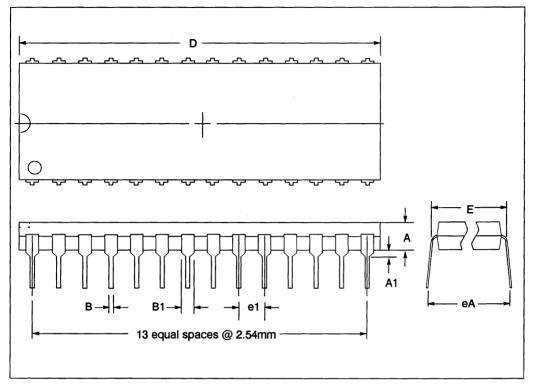

|   |             | 4.5.1<br>4.5.2                            | 28 pin dual-in-line package                                                                                                                                                                                 | 56                               |

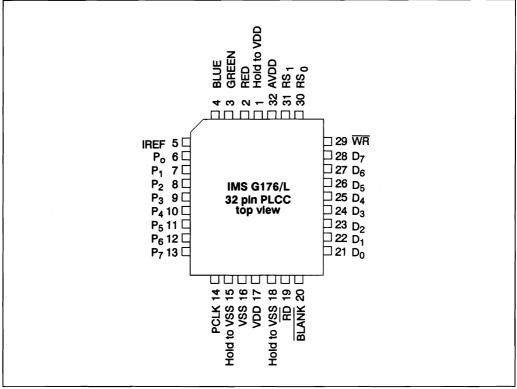

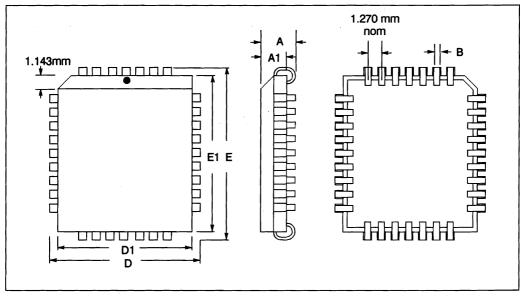

|   |             | 4.5.2<br>4.5.3                            | 32 pin plastic leaded-chip-carrier package                                                                                                                                                                  | 58<br>60                         |

|   |             | 4.5.3<br>4.5.4                            | 44 pin plastic leaded-chip-carrier package                                                                                                                                                                  | 62                               |

|   |             | 4.0.4                                     |                                                                                                                                                                                                             | 02                               |

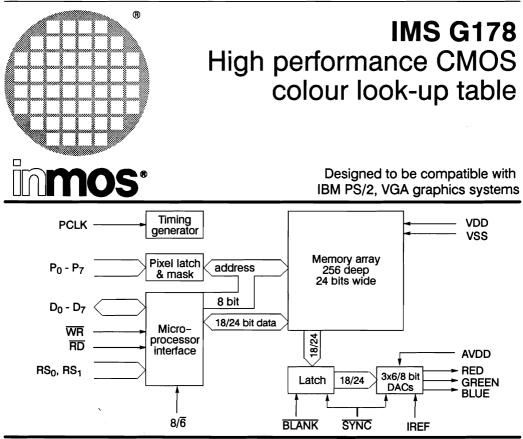

| IMS | G178 hig                                                                                     | gh performance colour look-up table                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1 | Pin desig                                                                                    | nations                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 5.1.1                                                                                        | Pixel interface                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 5.1.2                                                                                        | Analogue interface                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 5.1.3                                                                                        | Microprocessor interface                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 5.1.4                                                                                        | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 5.1.5                                                                                        | Internal registers                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

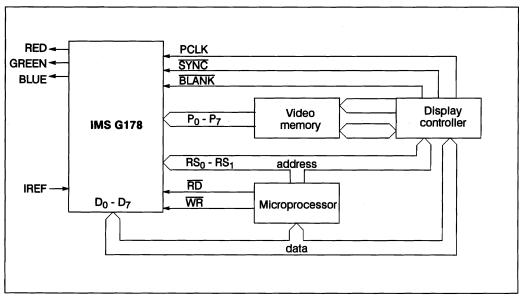

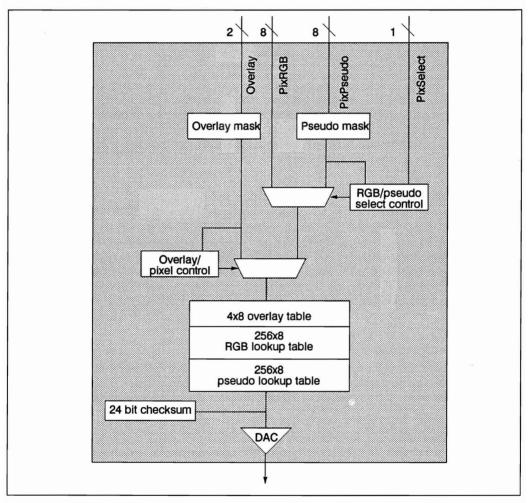

| 5.2 | Device d                                                                                     | lescription                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

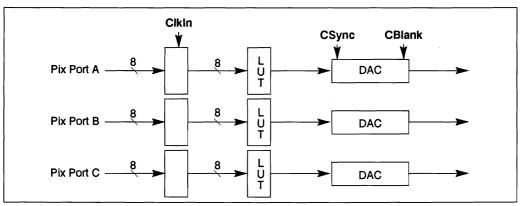

|     | 5.2.1                                                                                        | Video path                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

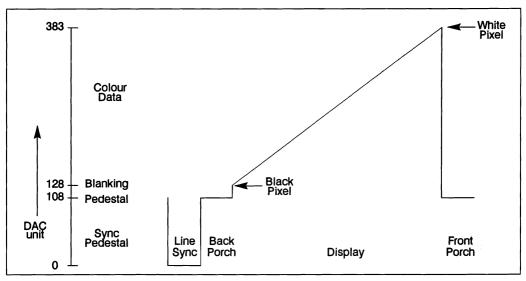

|     | 5.2.2                                                                                        | Analogue outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 5.2.3                                                                                        | Microprocessor interface                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.3 |                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 5.3.2                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72<br>73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

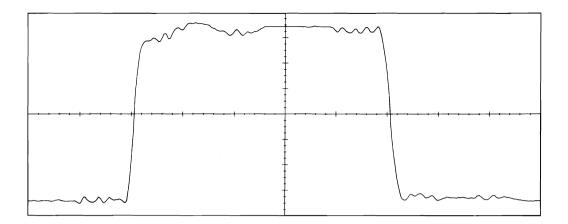

|     |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

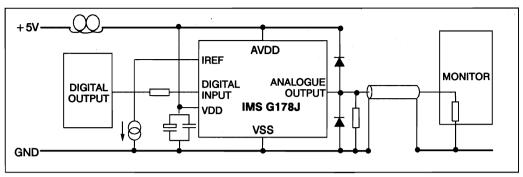

| 5.4 |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

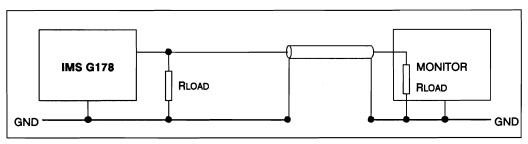

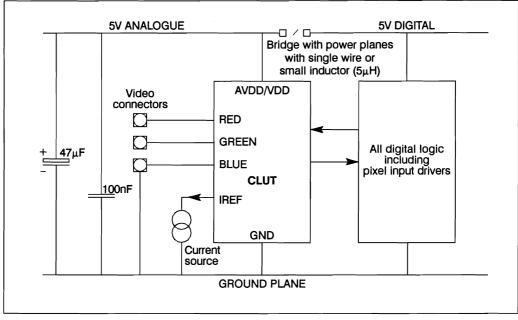

| 0   |                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

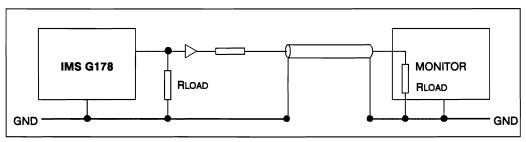

|     | •••••                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

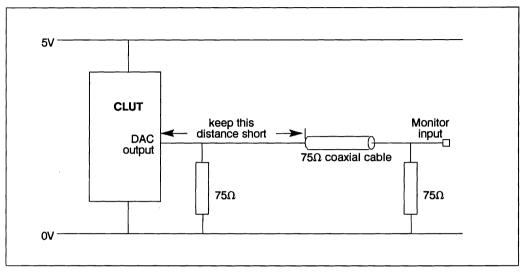

|     |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

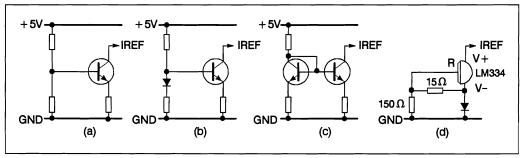

|     |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 5.4.5                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

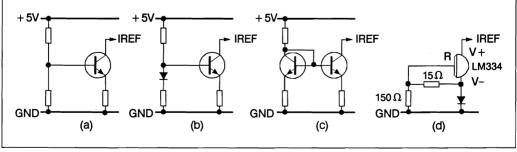

|     | 5.4.6                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | 5.4.7                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

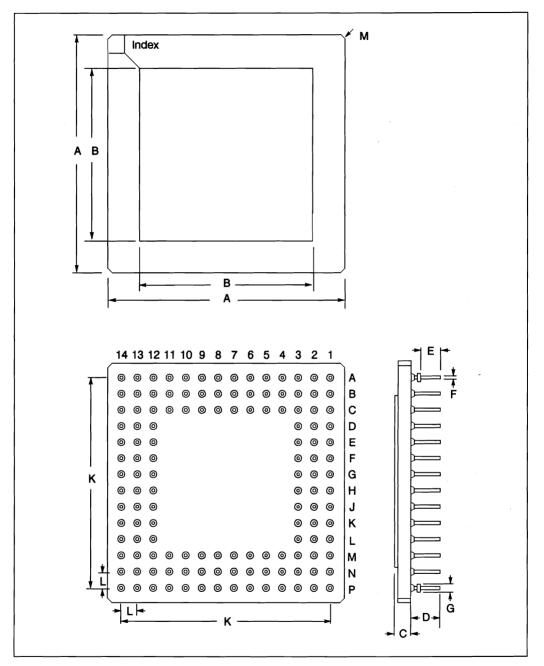

| 5.5 | Package                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

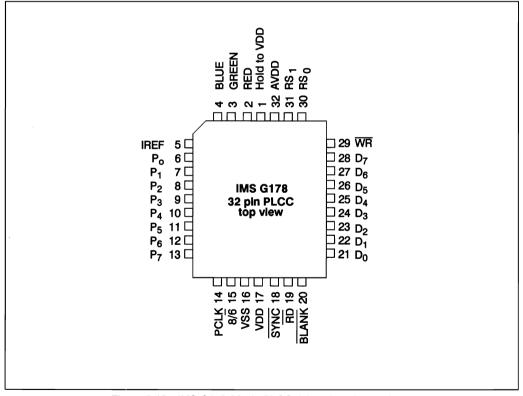

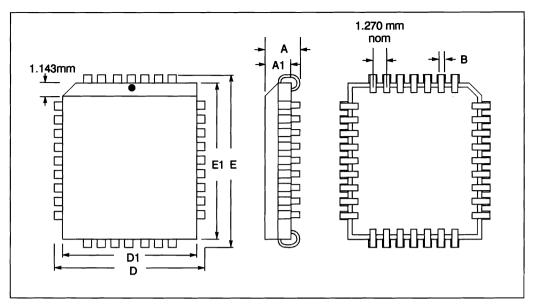

|     | 5.5.1                                                                                        | 32 pin plastic leaded-chip-carrier package                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

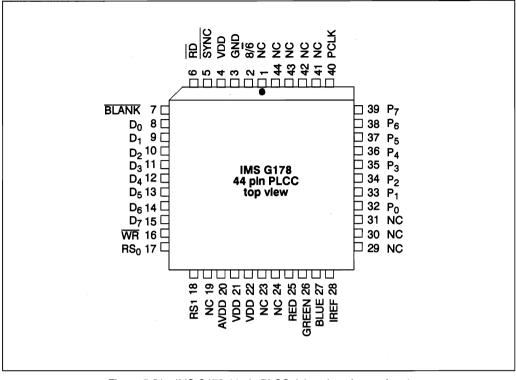

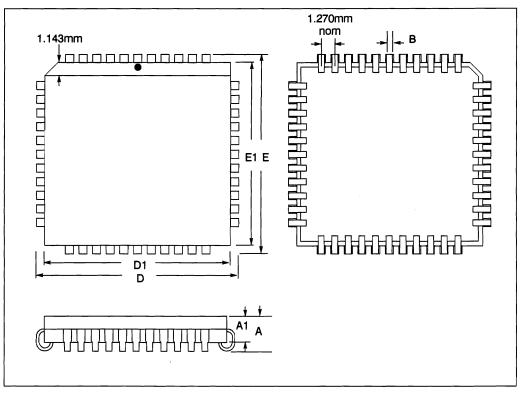

|     | 5.5.2                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |