# occam 2.1 Toolset User Guide

August 1995

© SGS-THOMSON Microelectronics Limited 1995. This document may not be copied, in whole or in part, without prior written consent of SGS-THOMSON Microelectronics.

. Immos<sup>®</sup>, IMS, occam and DS-Link<sup>®</sup> are trademarks of SGS-THOMSON Microelectronics Limited.

SCS-THOMSON is a registered trademark of the SGS-THOMSON Microelectronics Group.

Windows is a trademark of Microsoft Corporation.

This product incorporates innovative techniques which were developed with support from the European Commission under the ESPRIT Projects:

- P2701 PUMA (Parallel Universal Message-passing Architectures)

- P5404 GPMIMD (General Purpose Multiple Instruction Multiple Data Machines).

- P7250 TMP (Transputer Macrocell Project).

- P7267 OMI/STANDARDS.

Document Number: 72 TDS 366 02

# Contents overview

#### **Basics**

| 1 | Introduction to transputers            | An introduction to transputers and transputer programming.                                              |

|---|----------------------------------------|---------------------------------------------------------------------------------------------------------|

| 2 | Overview of the toolset                | An introduction to the OCCAM 2.1 toolset and its features including descriptions of the tools provided. |

| 3 | Getting started                        | Shows the command sequences to generate a simple occam 2.1 program using the toolset.                   |

| 4 | Developing programs for the transputer | An overview of the program development cycle using the toolset.                                         |

| 5 | An example program                     | Describes an example program for a single transputer, showing how it is built and run.                  |

| 6 | Programming in occam                   | Gives further information on program development, assuming a single transputer target.                  |

| 7 | Configuring<br>transputer programs     | Describes the configuration language and how to use it to configure software on transputer networks.    |

| 8 | Loading application programs           | Describes how to load programs onto the target transputer network.                                      |

| 9 | Access to host services                | Describes the access to host i/o using the libraries.                                                   |

#### Advanced techniques

| 10 | Advanced use of the<br>configurer         | Describes additional facilities provided by the configurer.                                       |

|----|-------------------------------------------|---------------------------------------------------------------------------------------------------|

| 11 | Mixed language<br>programming             | Describes how to mix C and OCCAM code at source and configuration levels.                         |

| 12 | Low level<br>programming                  | Describes techniques such as code insertion,<br>dynamic code load and extraordinary use of links. |

| 13 | EPROM programming                         | Describes converting a program into EPROM code.                                                   |

| 14 | ST20450 memory<br>interface configuration | Describes how to configure the memory interface of the ST20450.                                   |

| 15 | Performance<br>improvement                | Describes how to maximize the performance of occam transputer programs.                           |

## Appendices

| Α | Equivalent data types        | Lists type equivalents in C and OCCam.                  |

|---|------------------------------|---------------------------------------------------------|

| В | Transputer code<br>insertion | Defines the assembly code insertion facilities.         |

| С | Glossary                     | A glossary of terms.                                    |

| D | Bibliography                 | Lists literature and documentation for further reading. |

# Contents

| Contents overviewi |             |                                                  |    |

|--------------------|-------------|--------------------------------------------------|----|

| Contents iii       |             |                                                  |    |

| Prefa              | Preface vii |                                                  |    |

| Part               | 1: Bas      | sics                                             | 1  |

| 1                  | Introdu     | ction to transputers                             | 3  |

|                    | 1.1         | Transputers                                      | 3  |

|                    | 1.2         | Programming models                               | 6  |

|                    | 1.3         | Transputer products                              | 6  |

| 2                  | Overvie     | ew of the toolset                                | 9  |

|                    | 2.1         | Introduction                                     | 9  |

|                    | 2.2         | Toolset features                                 | 9  |

|                    | 2.3         | Standard object file format                      | 10 |

|                    | 2.4         | occam 2.1 compiler                               | 10 |

|                    | 2.5         | Multi-language linker                            | 12 |

|                    | 2.6         | Configuration system                             | 12 |

|                    | 2.7         | Mixed language programming                       | 13 |

|                    | 2.8         | Toolset summary                                  | 13 |

| 3                  | Getting     | started                                          | 15 |

|                    | 3.1         | Introduction                                     | 15 |

|                    | 3.2         | Running the examples                             | 15 |

|                    | 3.3         | The example program                              | 16 |

|                    | 3.4         | Compiling and linking for other transputer types | 20 |

|                    | 3.5         | Using the Makefile generator                     | 21 |

| 4                  | Develo      | ping programs for the transputer                 | 23 |

|                    | 4.1         | Program development using the toolsets           | 23 |

|                    | 4.2         | Compiling                                        | 27 |

|                    | 4.3         | Tools for building executable code               | 28 |

|                    | 4.4         | Loading and running programs                     | 31 |

|                    | 4.5         | Program development and support                  | 32 |

|                    | 4.6         | EPROM programming                                | 33 |

|                    | 4.7         | Mixed language programming                       | 33 |

|                    | 4.8         | File types and filename extensions               | 34 |

|                    | 4.9         | Error reporting                                  | 37 |

|                    | 4.10        | Host dependencies                                | 37 |

|                    | 4.11        | Unsupported options                              | 40 |

#### Contents

| 5 | An ex  | ample program                                   | 41 |

|---|--------|-------------------------------------------------|----|

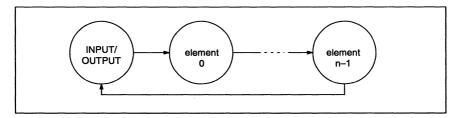

|   | 5.1    | Overview of the program                         | 41 |

|   | 5.2    | The channel protocol                            | 43 |

|   | 5.3    | The sorting element                             | 44 |

|   | 5.4    | The input/output process                        | 45 |

|   | 5.5    | The calling program                             | 46 |

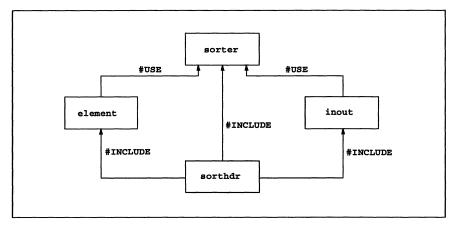

|   | 5.6    | Compiling the program                           | 46 |

|   | 5.7    | Linking the program                             | 47 |

|   | 5.8    | Configuring and collecting the program          | 47 |

|   | 5.9    | Running the program                             | 48 |

|   | 5.10   | Automated program building                      | 48 |

| 6 | Progr  | amming in occam                                 | 49 |

|   | 6.1    | Host channels                                   | 49 |

|   | 6.2    | occam error handling                            | 50 |

|   | 6.3    | Library i/o                                     | 53 |

|   | 6.4    | Alias and usage checking                        | 53 |

|   | 6.5    | Using separate vector space                     | 54 |

|   | 6.6    | Sharing source between files                    | 56 |

|   | 6.7    | Separate compilation                            | 56 |

|   | 6.8    | Using imakef                                    | 58 |

|   | 6.9    | Libraries                                       | 58 |

| 7 | Config | guring transputer networks                      | 61 |

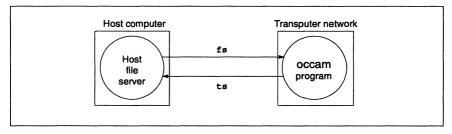

|   | 7.1    | Introduction to configuration                   | 61 |

|   | 7.2    | Configuration model                             | 62 |

|   | 7.3    | Hardware description                            | 68 |

|   | 7.4    | Software description                            | 76 |

|   | 7.5    | Mapping description                             | 78 |

|   | 7.6    | Example – a pipeline sorter on four transputers | 83 |

|   | 7.7    | Summary of configuration steps                  | 87 |

| 8 | Loadi  | ng application programs                         | 89 |

|   | 8.1    | Introduction                                    | 89 |

|   | 8.2    | Tools for loading                               | 89 |

|   | 8.3    | The boot from link loading mechanism            | 90 |

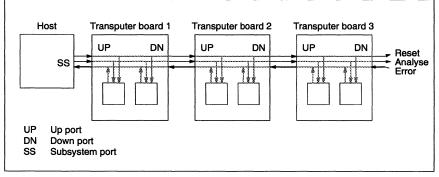

|   | 8.4    | Boards and subnetworks                          | 91 |

|   | 8.5    | AServer and the AServer database                | 93 |

|   | 8.6    | Skip loading                                    | 94 |

|   | 8.7    | Clearing error flags                            | 96 |

| 9   | Access  | s to host services                                        | 99  |

|-----|---------|-----------------------------------------------------------|-----|

|     | 9.1     | Introduction                                              | 99  |

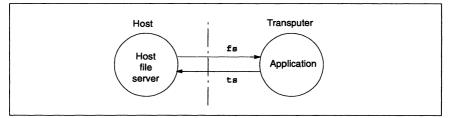

|     | 9.2     | Communicating with the host                               | 99  |

|     | 9.3     | Accessing the host from a program                         | 101 |

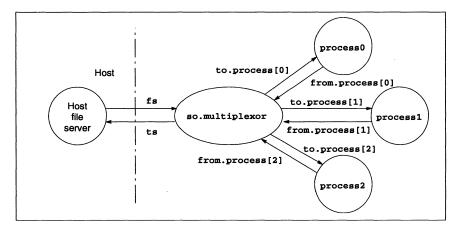

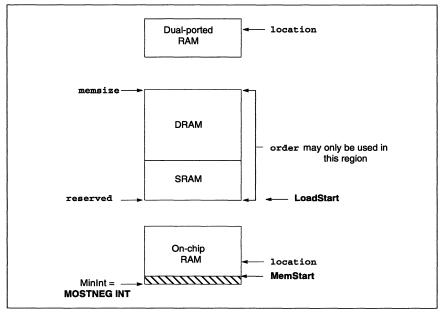

|     | 9.4     | Multiplexing processes to the host                        | 101 |

| Par | t 2: Ad | vanced techniques                                         | 105 |

| 10  | Advand  | ced use of the configurer                                 | 107 |

|     | 10.1    | Support for INQUEST                                       | 107 |

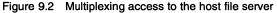

|     | 10.2    | Code and data placement                                   | 107 |

|     | 10.3    | Channel communication – configuration techniques          | 112 |

|     | 10.4    | Control of routing                                        | 114 |

|     | 10.5    | Example – optimized filter test program                   | 121 |

| 11  | Mixed   | language programming                                      | 125 |

|     | 11.1    | Mixed language programs                                   | 125 |

|     | 11.2    | Occam interface procedures                                | 146 |

| 12  | Low le  | vel programming                                           | 157 |

|     | 12.1    | Allocation                                                | 157 |

|     | 12.2    | Retyping channels and creating channel array constructors | 161 |

|     | 12.3    | Code insertion                                            | 163 |

|     | 12.4    | Dynamic code loading                                      | 167 |

|     | 12.5    | Extraordinary use of links                                | 172 |

|     | 12.6    | Scheduling                                                | 176 |

|     | 12.7    | Setting the error flag                                    | 177 |

| 13  | EPROM   | ۸ programming                                             | 179 |

|     | 13.1    | Introduction                                              | 179 |

|     | 13.2    | Processing options                                        | 181 |

|     | 13.3    | The EPROM tool: ieprom                                    | 182 |

|     | 13.4    | Producing ROM-bootable code                               | 182 |

|     | 13.5    | Summary of EPROM tool steps for different configurations  | 183 |

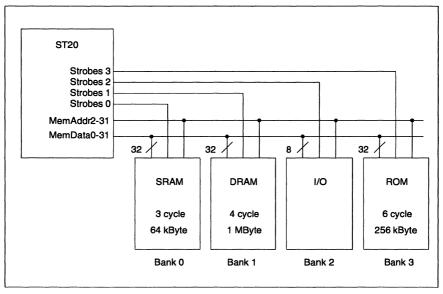

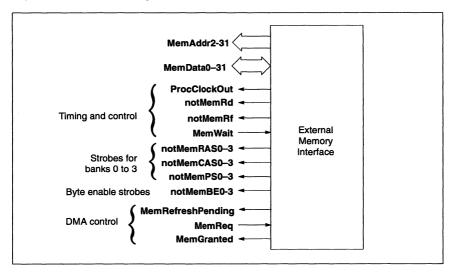

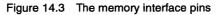

| 14  | ST2045  | 50 memory interface configuration                         | 185 |

|     | 14.1    | The memory interface                                      | 186 |

|     | 14.2    | General parameters                                        | 189 |

|     | 14.3    | Timing                                                    | 190 |

|     | 14.4    | Configuring for no external memory                        | 191 |

|     | 14.5    | Configuring for SRAM                                      | 192 |

|     | 14.6    | Configuring for DRAM and Video RAM                        | 195 |

|     | 14.7    | Configuring for ROM                                       | 199 |

|     | 14.8    | Configuring for non-memory devices                        | 199 |

| 15   | Perform  | mance improvement                          | 205 |

|------|----------|--------------------------------------------|-----|

|      | 15.1     | Introduction                               | 205 |

|      | 15.2     | Trade-offs and issues                      | 205 |

|      | 15.3     | Obtaining information                      | 210 |

|      | 15.4     | Command line switches                      | 211 |

|      | 15.5     | Compiler optimizations                     | 215 |

|      | 15.6     | Source code optimizations                  | 216 |

|      | 15.7     | Summary                                    | 228 |

|      | 15.8     | Maximizing multiprocessor performance      | 230 |

|      | 15.9     | Dynamic load balancing and processor farms | 233 |

|      |          |                                            |     |

| Арр  | pendice  | es                                         | 235 |

| A    | Equiva   | lent data types                            | 237 |

| в    | Transp   | uter code insertion                        | 247 |

| С    | Glossa   | ry                                         | 253 |

| D    | Bibliog  | raphy                                      | 263 |

| Inde | <b>x</b> |                                            | 267 |

# Preface

#### Host versions

The documentation set which accompanies the OCCAM 2.1 toolset is designed to cover all host versions of the toolset:

- IBM 386 PC compatible running MS-DOS

- Sun 4 systems running SunOS or Solaris.

#### About this manual

This manual is the User Guide to the occam 2.1 toolset.

The manual describes the use of the toolset in developing programs for running on the transputer. The manual is divided into two parts; *Basics* which describes each of the main stages of the development process, how to configure OCCAM programs for the transputer and how to build and load them. It also includes a *Getting started* tutorial. The *Advanced Techniques* part is aimed at more experienced users. The *Appendices* contain some reference material, a glossary of terms and a bibliography. Some chapters are in common with other toolsets e.g. *Developing programs for the transputer* and *Mixed language programming*.

#### About the toolset documentation set

The toolset documentation set comprises the following volumes:

le Od

occam 2.1 Reference Manual

Toolset Reference

Language and libraries Reference

• occam 2.1 Toolset User Guide

This manual.

• occam 2.1 Reference Manual

Provides a description and definition of the OCCAM 2.1 programming language, including the changes from OCCAM 2.

Toolset Reference Manual

Provides reference material for each tool in the toolset, including command line options, syntax and error messages. Many of the tools in the toolset are generic

to several toolset products e.g. the occam 2.1 toolset and the ANSI C toolset and the documentation reflects this. The appendices provide details of toolset conventions, transputer types, memory configuration files and the configuration languages.

#### • OCCAM 2.1 Language and Libraries Reference Manual

Provides a language reference for the toolset and implementation data. A list of the library routines provided is followed by detailed information about each function and procedure.

#### Other documents

Other documents provided with your toolset product include:

Delivery manual

This document gives installation data and is host specific.

#### Transputer targets supported by this toolset

The first generation of IMS T2xx, T4xx and T8xx transputers are referred to as the 'T2/T4/T8-series'. The new product family based around the IMS T9000 transputer is referred to as the 'T9-series'. The ST20450 may be called an ST20 or the IMS T450 depending on the context, and is included in the T2/T4/T8-series family unless otherwise stated.

The documentation set provided with this toolset tends to be generic, e.g. it covers different transputer types and in some cases different programming languages: C and occam. The occam 2.1 toolset supports occam 2.1 running on T2/T4/T8-series and ST20450 transputers. References in the documentation to other languages or transputer targets should be ignored.

#### **Documentation conventions**

The following typographical and notational conventions are used in this manual:

| Bold type   | Used to emphasize new or special terminology.                                                                                         |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Teletype    | Used to distinguish command line examples, code fragments, and program listings from normal text.                                     |

| Italic type | In command syntax definitions, used to stand for an argument of a particular type. Used within text for emphasis and for book titles. |

| Brackets [] | Used in command syntax to denote optional items on the command line.                                                                  |

| Braces { }  | Used to denote optional items in a command syntax which may be repeated.                                                              |

| Ellipsis    | Used to denote a range or the continuation of a series. For example, in syntax definitions denotes a list of one or more items.       |

| 1           | In command syntax, separates two mutually exclusive alternatives.                                                                     |

| viii        | SGS-THOMSON                                                                                                                           |

# Part 1: Basics

# Introduction to transputers

This chapter introduces transputers and the programming models which may be adopted when designing programs for the transputer. It describes the main features of the transputer and transputer systems, and introduces the transputer model of parallel processing.

# 1.1 Transputers

1

Transputers are high performance microprocessors that support parallel processing through on-chip hardware and external communication links. They can be used singly or connected one-to-another by their serial links in application-specific ways. They may be used as powerful dedicated microprocessors or as building blocks for complex parallel processing networks.

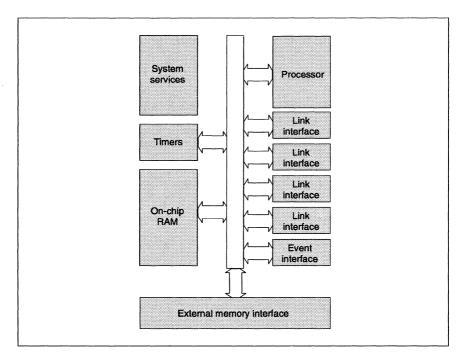

The transputer is a complete microcomputer on a single chip. In addition to hardware support for concurrent programming and inter-processor communication it contains:

- Very fast (single cycle) on-chip memory.

- A programmable memory interface that allows external memory and memory mapped devices to be added with the minimum of supporting logic.

- Real time clocks.

- On the T8 series, an integral floating point unit.

Figure 1.1 shows the generalized architecture of a transputer with four links.

#### 1.1.1 Transputer links

Links are high performance communications interfaces. They allow processes running on connected processors to exchange data and synchronize their activity. Support for link communications is implemented in hardware on each transputer chip. Communications down links operate concurrently with the processing unit and data can be transferred simultaneously on all links. Most transputers have four links except the IMS T400 transputer which has just two links.

Transputer links allow tools such as debugging programs to examine memory directly from a remote processor. Links also provide a means of loading programs onto a network from the host down a single transputer link. Alternatively a network can be loaded via links from a ROM on a single transputer. Both these models are supported by the transputer toolsets. For ease of development, stand-alone systems and software are generally developed using a hosted system and then the software is put into a ROM as a final development stage.

#### **1.1 Transputers**

T2/T4/T8-series transputer links consist of two wires, one in each direction, and uses an asynchronous bit-serial (byte-stream) protocol. Each bit received is sampled five times and hence the links are referred to as over-sampled links (OS-Links). Each link provides a pair of channels, one in each direction and can operate at up to 20 Mbits/sec, providing a bidirectional bandwidth of 2.4 Mbytes/sec.

Figure 1.1 Transputer architecture

#### 1.1.2 Process scheduling

Each transputer has a highly efficient run-time scheduler for time-sharing user application processes running on the same transputer. Within a single transputer, communication between processes is supported using *channels*. Processes waiting for input or output or waiting for a processor to become available, consume no CPU resources, and process context switching time is less than one microsecond. This means that most applications require no operating system, with a corresponding improvement in performance and cost savings.

The scheduling mechanism may also be used for performing interrupts, which makes interrupt-handling simple and reliable.

4

#### 1.1.3 Real time programming

The transputer has features which provide direct hardware support for real-time programming. The key features are:

- Direct and efficient implementation of parallel processes in hardware.

- Two priority levels for parallel processes.

- Simple implementation of interrupt-handling software.

- Easy programming of software timers, allowing close control of timing and nonbusy polling.

- Placement of variables and PORTS at specific addresses in memory, for accessing memory mapped devices.

Direct support for these features can be found in the current range of transputer toolsets, which use a common code format to facilitate code compatibility between languages.

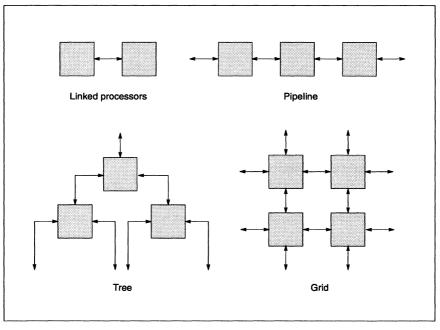

Figure 1.2 Transputer networks

#### 1.1.4 Multi-transputer systems

Multi-transputer systems can be built very simply using the two or four high speed links; only two or four wires are required to connect two links together. The circuitry to drive each link is on the transputer chip.

Transputers may be connected by their links in many configurations, depending on the needs of the application. Some possible arrangements of networks of transputers are illustrated in figure 1.2.

# 1.2 Programming models

Programs developed for running on a single transputer can be designed using traditional sequential programming methods or they can be designed to exploit parallelism, either to simplify the software or to make the software portable onto multi-processor systems.

Parallelism can be designed into a program at two levels by dividing the program into a number of independent communicating sequential processes capable of operating in parallel. Such processes can either be run on a single transputer, using the transputer's hardware scheduler, or on a network of transputers. Programs designed for running on a network of transputers must use the parallel processing model; see section 1.2.1.

Sequential programs can be run on a single transputer. Such programs can exploit the transputer architecture and software support provided by the toolsets and systems products, as described in section 1.3.

## 1.2.1 Parallel processing model

The abstract programming model which the transputer supports is the Communicating Sequential Process (CSP) model, based on the idea of independent parallel *processes* communicating through *channels*. A channel is a one-way, point-to-point communication path that allows processes to exchange data and synchronize their activity. Further details can be found in *Communicating Sequential Processes* by C.A.R. Hoare, published by Prentice Hall International.

Each process is built from any number of parallel processes, so that an entire software system can be described in the form of a hierarchy of intercommunicating parallel processes. This model is consistent with many modern software design methodologies.

Communication between processes is synchronized. When data is passed between two processes the output process does not proceed until the input process is ready and vice versa.

Communication between software processes running on the same transputer takes place through internal channels implemented as words in memory; communication between processes running on connected processors is driven by the link interfaces and takes place through the transputer links.

# 1.3 Transputer products

There is a complete family of transputer devices, including 32-bit and 16-bit processors, link switches and link adaptors for interfacing to other processors and devices.

A wide range of SGS-THOMSON TRAnsputer Modules (TRAMs) and motherboards is available for specific hosts. A TRAM is a transputer with an amount of memory and possibly some other application specific hardware, mounted on a circuit board. TRAMs can be interconnected via links to build systems based on a number of motherboard architectures. SGS-THOMSON transputer board products can be used for:

- · Developing and debugging transputer software,

- · Improving system performance (as accelerator boards),

- · Loading software onto embedded systems,

- Building specific transputer networks,

- Specific applications such as SCSI interfacing.

#### 1.3.1 Toolset products

The transputer toolsets are complete software cross-development systems for transputers. They allow transputers to be programmed sequentially and in parallel using high-level languages, making optimum use of the transputer's built-in parallel features. The combination of access to parallelism from a high level language and a set of tools for configuring and loading programs on transputer-based systems forms a powerful development system for all sequential, parallel and embedded software applications.

# 2 Overview of the toolset

This chapter introduces the occam 2.1 toolset. It describes the main features of the toolset and provides introductions to the occam 2.1 compiler, the toolset linker, the configuration system, and mixed language programming. A summary of the toolset components is given at the end of this chapter.

# 2.1 Introduction

The occam 2.1 toolset is a software cross-development system for transputers, hosted on a 386 PC with MS-DOS or a Sun 4 system with SunOS. It consists of an occam 2.1 compiler, a multi-language linker, configuration and code collection tools and program development tools.

The program development tools include a librarian, an object code lister, a makefile generator, memory interface configurers and EPROM programming tools. Together with the compilation system, these form an integrated support and development environment for the programming of transputers and transputer-based hardware.

The toolset is supplied with INQUEST and host interface software. INQUEST includes an interactive and post-mortem debugger and various profiling tools. The INQUEST tools are described in the *INQUEST User and Reference Manual*. The host interface software includes an application loader and a host file server.

## 2.2 Toolset features

This toolset incorporates a number of important features:

- · Standard object code format generated by the compiler and linker.

- An updated OCCAM 2.1 compiler with language improvements, facilitating full exploitation of a programming model designed to support parallelism.

- A configuration language which is an extension to OCCAM and facilitates the mapping of software to hardware. The language supports:

- Automatic placement of channels using software routing and multiplexing processes. The ability to place channels manually is also retained as an option.

- Placement of code and data at specific memory addresses.

- Support for mixed language programming through the configuration system and by specific support in the compiler.

- Support for ST20450 (T450) targets, featuring the following:

- byte and half word instructions used to support 8-bit and 16-bit integer operations;

- PORTS implemented using the device access instructions on ST20450 processors;

- o memory configuration.

# 2.3 Standard object file format

The current range of transputer toolsets generate object code in an intermediate form known as *TCOFF* (*T*ransputer *C*ommon *O*bject *File Format*), that can be processed by other tools in the toolset. This standard has been adopted for the development of transputer toolsets and enables modules written in different languages to be freely mixed in the same system.

# 2.4 occam 2.1 compiler

The occam 2.1 compiler compiles occam source code contained within standard host format text files. Any text editor that produces ASCII files can be used to create the occam source. occam source code must conform to the definition of occam 2.1 which is described in the occam 2.1 Reference Manual. The compiler implements a number of non-standard language extensions, as described in Appendix A in the occam 2.1 Toolset Language and Libraries Reference Manual.

The compiler targets the current range of T2/T4/T8-series transputers and the ST20450. Code may be generated for specific processor types or for related groups, as described in Appendix B in the *Toolset Reference Manual*.

Code may be generated in HALT, STOP, or UNIVERSAL occam error modes. The error mode must be the same (or compatible) for all object files which are to be linked together, and must be the same as the linker error mode.

#### 2.4.1 Programming model

The occam programming model consists of parallel processes communicating over channels. Processes may be on the same or different processors, communicating over internal channels or transputer links.

OCCAM 2.1 has been optimized for the architecture of the transputer – parallelism is expressed directly in the language. The use of a formal mathematical framework enables OCCAM code to be extensively checked at compile time and supports formal program proving and optimization. The inherent security of OCCAM code coupled with efficient use of the transputer's parallel features make it a powerful tool for the development of concurrent systems.

#### 2.4.2 Language extensions

The compiler implements a number of language extensions. These are compiler-dependent and do not form part of the Occam 2.1 definition.

Directives supported are **#INCLUDE**, **#USE**, **#COMMENT**, **#IMPORT**, **#OPTION** and **#PRAGMA**. **#PRAGMA** supports a number of compiler-dependent functions, including foreign language code import and name translation. These are fully described in section 3.13 of the *Toolset Reference Manual*.

Other language extensions supported by the compiler are:

- assembly code insertion;

- memory placement;

- extended channel retyping.

See Appendix A of the *Occam 2.1 Toolset Language and Libraries Reference Manual* for details.

#### 2.4.3 occam libraries

A comprehensive set of libraries and include files is supplied with the toolset. They include the *compiler libraries* which form part of the standard support for the occam language and a set of *user libraries* for use by the applications programmer.

The compiler libraries are used internally by the compiler; they are not intended for general use by the programmer, although some routines have been made visible (see Chapter 2 in the *Occam 2.1 Toolset Language and Libraries Reference Manual*). The compiler automatically loads the correct set of routines for the selected error mode and transputer type. Compiler libraries are specified to the linker by means of target-specific *linker indirect files*; see section 4.3.1.

The user libraries provide application-level support. There are libraries to support:

- single length, double length, and T4-optimized maths;

- file-based and stream-based i/o;

- string handling;

- type conversion;

- link error handling;

- CRC coding;

- debugging.

Constants and definitions are supplied in include files. See the *occam 2.1 Toolset* Language and Libraries Reference Manual for details.

#### 2.4.4 Low level programming

Sequences of transputer instructions can be embedded in OCCAM code using the ASM construct. This can be useful for optimizing critical sections of code, but the facility should not be over used because it reduces the compiler's opportunity to check code.

A set of procedures is provided which enables a separately compiled and linked OCCAM procedure to be loaded and called at run-time and incorporated in a running OCCAM program. This facility is aimed at experienced toolset users.

Full descriptions of these facilities are given in Chapter 12.

## 2.5 Multi-language linker

The toolset linker takes compiled code and libraries and generates a linked unit in TCOFF format. Input code can be generated by any compiler which generates TCOFF code, for example, the ANSI C compiler icc. Linker indirect files (command scripts to the linker) may be used to specify operations to the linker; for example, as in the linker indirect files provided with the toolset for referencing the compiler libraries; see section 4.3.1.

Linker directives, which must be referenced using linker indirect files, may be used to modify the content of the linked unit. Linker directives are described in section 10.4 of the *Toolset Reference Manual*.

# 2.6 Configuration system

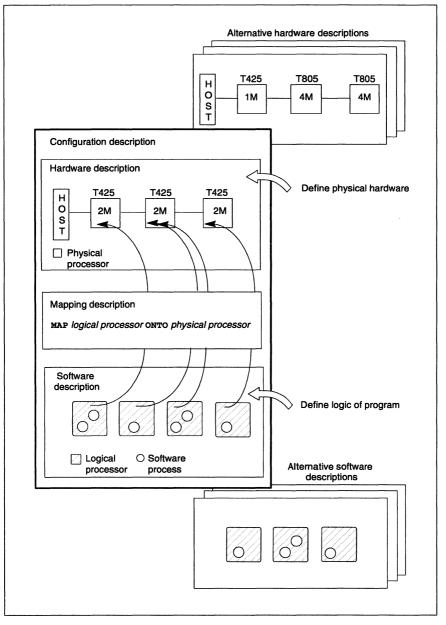

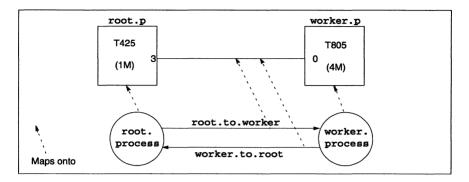

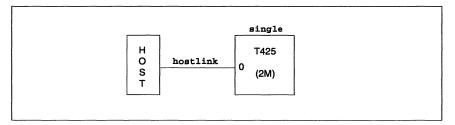

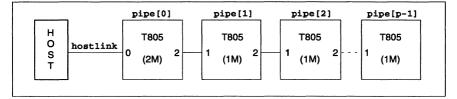

The configurer occonf generates configuration information for transputer networks from a textual *configuration description* containing separate descriptions of hardware and software. Mapping of software to hardware is performed according to a mapping description written by the user, while the mapping of channels to links can be performed automatically by the configurer or be specified by the user.

The tool prepares the program for configuring on a specific arrangement of transputers by analyzing the configuration file and creating a configuration data file for the code collector tool to read. The code collector then generates the program image which may be loaded onto the hardware.

The configuration language used to write the configuration description is an extension of occam. It allows software and hardware networks to be described separately and joined by an optional software-to-hardware description. The language is a simple declarative language incorporating high-level constructs such as replication and conditional statements.

#### 2.6.1 Software routing and multiplexing

The configurer uses software routing and multiplexing software to implement channel communication over *virtual links*. This allows many *virtual channels* to use a single physical link between processors and enables processes on non-adjacent processors to communicate directly.

Software routing and multiplexing is performed automatically by the configurer and requires no intervention on the part of the programmer. Generally, existing configuration

code can be reused – virtual routing will be employed where required unless virtual routing is specifically disabled by the configurer **NV** option.

#### 2.6.2 Code and data placement

Normally, the configurer will use up the available memory accessible to a processor by allocating the various parts of the application from the lowest address upwards. However, it is sometimes necessary to specify exactly where a piece of code or data should reside. The configurer allows the user to state where the code, workspace (stack) or vectorspace of an OCCAM program must be placed in memory.

The transputer has some very fast RAM which the application may be required to use in a special way. The configurer can also be told to avoid this area of memory so that the user has free access to it.

# 2.7 Mixed language programming

The use of standard TCOFF format allows compiled and linked modules from different language sources e.g. C and OCCAM, to be mixed in the same system. Individual linked units in TCOFF format can be mixed in any combination and placed on any processor in the network.

Calling modules written in other languages is also possible. For example, OCCAM can call C by using library routines to set up and terminate the static and heap areas. C can call OCCAM using the IMS\_nolink pragma which directs the C code to be compiled without a static base parameter, or a dummy static base parameter can be declared in the OCCAM code.

In all mixed language calls, parameters and return values passed must be of the correct type. Lists of type equivalents between C, and OCCAM are given in chapter 11. Where character sets differ between languages, translate pragmas available in the compilers can be used to create acceptable aliases.

# 2.8 Toolset summary

The components of the toolset, excluding the INQUEST tools, are summarized in table 2.1. Descriptions of the tools can be found in chapter 4 which also describes the main stages of program development.

| Tool     | Description                                                                                                                                                                    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| icollect | The toolset code collector. Collects linked units into a single file for loading on a<br>transputer network. Takes as input a configuration data file or a single linked unit. |

| iemit    | The transputer memory configuration tool. Used for evaluating and defining memory<br>configurations for later incorporation into ROM programs.                                 |

| ieprom   | The EPROM program formatter tool. Formats transputer bootable code for input to ROM programmers.                                                                               |

| ilaunch  | The Windows launch tool. Used for setting Windows environment parameters.                                                                                                      |

| ilibr    | The toolset librarian. Builds libraries of compiled code.                                                                                                                      |

| ilink    | The toolset linker. Resolves external references and links separately compiled units into a single file.                                                                       |

| ilist    | The binary lister. Disassembles and decodes object code and displays information in a readable form.                                                                           |

| imakef   | The Makefile generator. Generates Makefiles for input to make programs.                                                                                                        |

| imap     | The map tool which gives the addresses of functions and variables used by the<br>program.                                                                                      |

| imem450  | The memory configuration tool for T450 targets. Used for evaluating and defining the<br>memory configuration.                                                                  |

| irun     | The application loader. Used for loading built programs onto the target.                                                                                                       |

| iset     | The Windows parameter tool. Used for setting Windows environment parameters.                                                                                                   |

| oc       | The occam 2.1 compiler. Compiles code for the current range of transputers.                                                                                                    |

| occonf   | The occam configurer. Reads a configuration description and produces a<br>configuration data file for the code collector.                                                      |

Table 2.1 The occam 2.1 toolset

.

# 3 Getting started

This chapter contains a tutorial that shows you how to compile, link, and run a simple example program on a single transputer.

A more complex programming example illustrating separate compilation can be found in chapter 5. A detailed description of program development is given in chapter 4. chapter 7 provides examples of multi-transputer programming.

## 3.1 Introduction

In order to create and run a transputer executable file, the following steps must be followed:

- 1 The source files are compiled with the occam 2.1 compiler. The compiler creates from each source file an object file.

- 2 The object files are linked together along with any libraries required, to create a file known as a linked unit. Each linked unit contains the code and data necessary to execute as a main program.

- 3 The linked units are then configured onto a transputer network and collected to create a bootable program. In the case of a single program on a single transputer, there is a short cut available here. However, it is strongly recommended that development is made by using the full facilities of the configurer. The INQUEST tools do not support unconfigured programs, and there are many other advantages to configuring which will become apparent as the procedures are described.

- 4 The program is then loaded and run from the host by using irun. The bootable program contains everything necessary for execution on the transputer network and it will start automatically after it has been loaded.

## 3.2 Running the examples

In the following examples, the programs are compiled and executed on a single IMS T425 with 1Mbyte of memory available. If you have a different model of transputer, then you should make the necessary changes to the command lines and configuration file as indicated. Command line options for specifying other transputer types are listed in appendix B of the *Toolset Reference Manual*.

The examples assume the existence of

• an environment variable **TRANSPUTER** which defines the name of a *connection* to a target network on which to load the program, and

• an AServer database file to define that connection.

See the *Delivery Manual* which accompanies this toolset and the *irun* documentation (chapter 15 of the *Toolset Reference Manual*) for more details.

The examples also assume the existence of the environment variable ISEARCH, which gives the tools a search path to find libraries and include files which are not in the current directory. See the *Delivery Manual* for details.

The tutorial assumes that you have a *boot from link* board. If you have a *boot from ROM* board or other non-standard hardware, refer to the manufacturer's documentation.

#### 3.2.1 Sources

Source files for the example used in this chapter are supplied with the toolset under the examples directory.

#### 3.3 The example program

The example program is contained in the file simple.occ.simple.occ reads a name from the keyboard and displays a greeting on the screen. The program uses the library hostio.lib and the include file hostio.inc. The configuration description is in the file simple.pgm.

The program is listed below with line numbers.

```

1.

#INCLUDE "hostio.inc" -- contains SP protocol

2.

PROC simple (CHAN OF SP fs, ts)

3.

#USE "hostio.lib"

4.

[1000]BYTE buffer :

5.

BYTE result:

6.

INT length:

7.

SEO

8.

so.write.string

(fs, ts,

"Please type your name :")

so.read.echo.line

9.

(fs, ts, length, buffer, result)

10

so.write.nl

(fs, ts)

11.

so.write.string

(fs, ts, "Hello ")

12.

so.write.string.nl (fs, ts,

[buffer FROM 0 FOR length])

13.

so.exit

(fs, ts, sps.success)

14. :

```

Line 1 in the program includes the file hostio.inc. This file contains the definition of the protocol SP, used to communicate with the host file server, and a number of constants that are used in conjunction with the host i/o library. This line must be the first line because line 2 refers to the SP protocol defined in hostio.inc.

The procedure simple is then declared. All the working code is contained within this procedure. The host i/o library hostio.lib is referenced by the #USE directive in

line 3. This library contains all the procedures used by the program. See chapter 4 in the *occam 2.1 Toolset Language and Libraries Reference Manual* for descriptions of these routines.

Before the body of the procedure, a number of variables are declared. buffer holds the input string, length refers to the number of characters in the name read from the keyboard, and result is used by the library routine to indicate whether or not the read was successful. The result is ignored by this example for the sake of simplicity; it is assumed that screen writes and keyboard reads always succeed. The working code is contained within a SEQ, indicating that the statements which follow are to be executed sequentially. All of the statements are calls to library routines in hostio.lib. The code prompts for a name on line 8, reads the name from the keyboard on line 9, and displays a greeting on the screen in lines 11 and 12.

The last statement, on line 13, calls a library procedure which terminates the host file server, returning control to the host operating system. Without this statement the program would finish and appear to hang, and the server would have to be terminated explicitly by interrupting from the keyboard.

#### 3.3.1 Compiling the program

In order to compile the program for an IMS T425 use the following command line:

oc simple -t425

The compiler performs the necessary syntax, alias and usage checks, inserts code to perform run-time error checking, and creates a file called simple.tco. Because the source file has the default extension of .occ you can omit the extension on the command line.

The target processor is given as an IMS T425; for information about compiling for other transputer types, see section 3.4.

By default, the compiler enables interactive debugging with INQUEST and compiles the program in HALT mode; see chapter 3 of the *Toolset Reference Manual* for a description of the modes.

#### 3.3.2 Linking the program

To use the result of your compilation it must be linked with the libraries that it uses.

To link the program type:

ilink simple.tco hostio.lib -t425 -f occama.lnk

This program uses hostio.lib and various target-specific compiler libraries. hostio.lib is directly specified on the command line. The correct compiler libraries are referenced in the linker indirect file occama.lnk which is specified by the F option.

The **F** option introduces a *linker indirect file* which is used to link in the correct compiler libraries. For more details see chapter 10 in the *Toolset Reference Manual*. If interactive debugging were required then the debugging libraries should be linked in, as described in the *INQUEST User and Reference Manual*.

It is necessary to specify to the linker what the transputer target is. The toolset can produce code for a range of transputers and the linker must then be told which the actual target will be. In this example the chosen target is an IMS T425.

The linked program will be written to the file simple.lku. As no output file is specified, the file is named after the input file and the default link extension .lku is added. By default the program is linked in HALT mode.

In more complex programs, libraries may be dependent on other files and libraries. To ensure all necessary libraries are linked into a program, the *imakef* tool may be used with a suitable make program, as described in section 3.5.

#### 3.3.3 Configuring the program

In order to configure the program, a description is required of the network it is to run on. The file simple.pgm contains such a description.

You should look at this file and edit it if it does not correspond to the hardware you actually have. For example check which link is connected to the host, the transputer type, and memory size.

The file simple.pgm contains the following:

```

NODE p :

ARC hostarc :

NETWORK

DO

SET p(type, memsize := "T425", 1024 * 1024)

CONNECT p[link][0] TO HOST WITH hostarc

:

#INCLUDE "hostio.inc"

#USE "simple.lku"

CONFIG

CHAN OF SP fs, ts :

PLACE fs, ts ON hostarc :

PROCESSOR p

simple(fs, ts)

;

```

In order to configure the application for the network, the configurer is invoked as follows:

occonf simple.pgm

This produces a file called simple.cfb which contains all the information about where the different parts of the program are to be placed.

#### 3.3.4 Collecting the program

The final build stage is to collect all the parts of the program with the bootstrap and loading and routing code and combine them into a file which can be loaded onto the transputer for execution. This is done by the collector tool icollect. The collector is invoked as follows:

icollect simple.cfb

The result is the executable *bootable* file simple.btl.

#### 3.3.5 Running the program on a transputer board

To load the bootable file onto a transputer board and run it, use the application loader tool irun.

On a Sun, the irun command line can be entered at a SunOS prompt. On a PC running Windows, the irun command may be entered on the command line of a DOS window if ilaunch is running. Alternatively irun may be started in the normal Windows manner using the file manager **Run.** command or an icon.

The irun command line is:

irun simple.btl

The connection to the transputer board is taken from the **TRANSPUTER** environment variable.

The command line specifies the file to be booted. The command has the effect of resetting the target network, opening communication between the host and the target, and loading the program onto the target network. For further information about *irun* options see chapter 15 in the *Toolset Reference Manual*.

Figure 3.1 shows an example of the screen display obtained by running simple.btl for a user called John.

```

Please type your name :John

Hello John

```

Figure 3.1 Example output produced by running simple.bt1

#### 3.3.6 A short cut to creating a bootable file

For single-transputer programs booted from transputer links attached to a host, an alternative method can be used to create the .btl file. This method is not applicable

to stand-alone systems nor to systems which boot from ROM, and requires the program to be contained within a *single linked unit*. The INQUEST debugger cannot be used to debug programs created in this way. This facility is provided for compatibility with previous versions of the toolset and is not recommended.

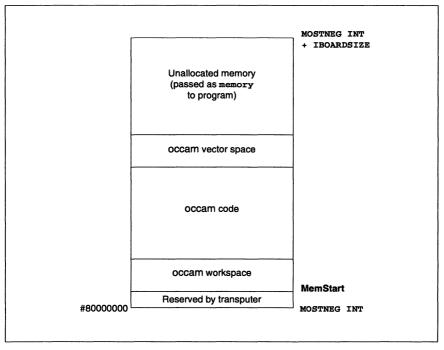

Non-configured programs require a fixed procedural interface, because the parameters cannot be defined in the configuration description. Line 2 of simple.occ on page 16 would therefore become:

PROC simple (CHAN OF SP fs, ts, []INT free.memory)

The free.memory parameter represents the spare memory not allocated by the tools. The total size of the memory available is taken from the environment variable IBOARDSIZE.

Unconfigured programs must always use a similar parameter list. A modified version of the program can be found in the examples directory under the name simple3.occ.

To make use of the short cut, compile and link the simple3.occ in the same way as in the previous example. Then, omitting the configurer stage, invoke the collector directly on the linked unit, adding the  $\tau$  option to the command line. The  $\tau$  option directs the collector to build a bootable file from a single linked unit.

```

icollect simple3.1ku -t

```

The bootable file simple3.btl is created. This can be loaded and run in the same way using irun.

#### 3.4 Compiling and linking for other transputer types

If you are using a transputer other than an IMS T425 you should specify the appropriate target transputer type for the compilation and linking operations. Appendix B in the *Toolset Reference Manual* describes the options available. The same processor type must be specified to the compiler, linker, and in configuration description, otherwise an error is reported. In addition, you must specify the correct linker indirect file for the selected target, in order to link in the correct compiler libraries; see chapter 10 of the *Toolset Reference Manual*).

For example, to compile and link the program simple.occ so that it will run on a T800, T801 or T805:

oc simple -t800 ilink simple.tco hostio.lib -f occam8.lnk -t800

Similarly for an ST20450:

```

oc simple -t450

ilink simple.tco hostio.lib -f occam450.lnk -t450

```

Modify simple.pgm to match the transputer type and memory size of your hardware and run occonf on the modified file. Then collect and load the program as before.

## 3.5 Using the Makefile generator

As an alternative method of program building, the toolset Makefile generator imakef can be used. This tool can produce a Makefile for any type of file that can be built with the toolset tools. See chapter 12 in the *Toolset Reference Manual* for a full description of the tool.

imakef serves two purposes:

- It enables the user to generate a makefile which can be used to generate a target file automatically (e.g. a bootable file) without having to manually request the intermediate stages of program development, i.e. compiling, linking, configuring etc.

- For more complex programs, comprising several modules, it simplifies the incorporation of changes to the program by identifying dependencies and incorporating them into the Makefile so that only the affected parts need to be rebuilt.

In order that imakef can identify file types, target processor types and error modes, a different system of file extensions must be used to that used in the examples above. See section 12.3 in the *Toolset Reference Manual* for a description of the system.

To create a Makefile for the configured simple program, use the following command:

imakef simple2.bt1

This directs imakef to build a makefile to create a bootable file simple2.btl. The .btl extension tells imakef to refer to a configuration description file simple2.pgm. This file can be found under the examples directory. Within the .pgm file, the correct file extension is used to reference the linked unit for imakef. For example:

#USE "simple.c5h"

tells imakef that the Makefile must compile the program for an IMS T425 in HALT error mode. For other transputer types and error modes use different suffixes, as described in section 12.3 in the *Toolset Reference Manual*.

imakef generates the Makefile simple2.mak. To build the program run your make

program using the Makefile simple2.mak:

make -f simple2.mak

This creates the bootable file simple2.bt1 which can be run in the normal way using irun.

# 4 Developing programs for the transputer

This chapter gives an overview of the program development cycle using the OCCAM 2.1 toolset. It briefly describes the purpose of each tool and outlines how to use them in developing, configuring, loading and running transputer programs from the host system. The chapter also gives brief details of environment variables, and host dependencies. Chapter 8 describes loading and running the built application on the target hardware.

Further information about the tools for building and loading code can be found in the *Toolset Reference Manual*. The INQUEST debugging, profiling and analysis tools are described in the *INQUEST User and Reference Manual*.

# 4.1 Program development using the toolsets

Programs are developed on the user's host system before down-loading for execution on either a single transputer or a network of transputers.

Executable code may be loaded onto a transputer either from ROM or from the host system. Code from the host file system is loaded via a single transputer link from the host to the *root transputer*, i.e. the transputer connected to the host. Code is propagated to any other transputers in the network via the interconnecting transputer links.

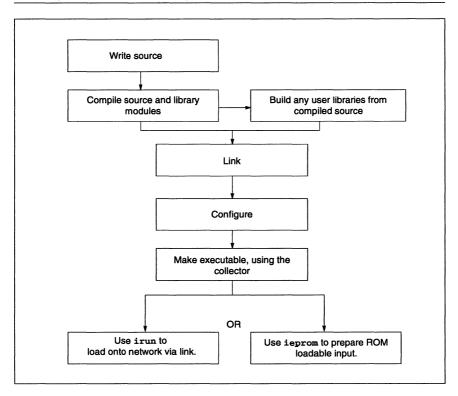

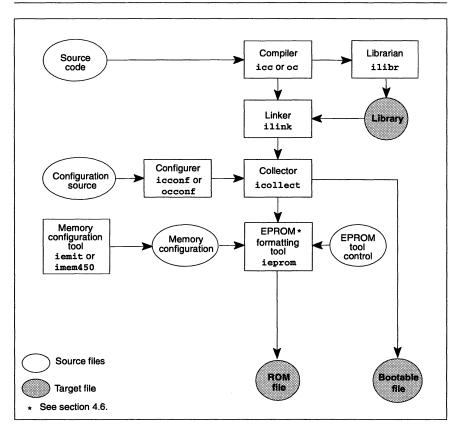

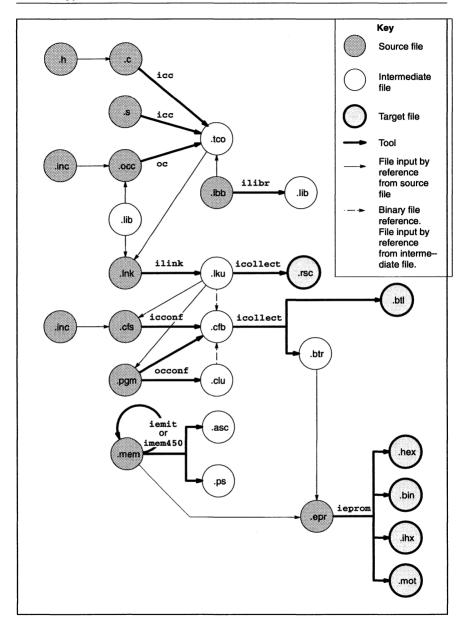

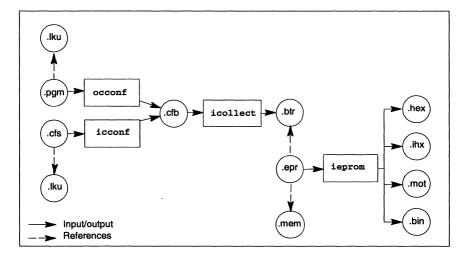

Creation of executable code for a transputer or transputer network takes several stages involving the use of specific tools at each stage. Figure 4.1 summarizes the main development stages and figure 4.2 illustrates how the tools are used to build a program.

The following sections concentrate on how to develop programs which are loaded from the host system. Any system that is to be loaded from ROM when completed, is normally loaded from the host during development and then converted to loading from ROM as a final development stage. Developing programs for loading from ROM is described briefly in section 4.6 and more fully in chapter 13.

#### 1 Software design

The software designer can specify the components of a system in terms of communicating processes. The overall design can be directly expressed using the support provided for multi-tasking and parallel programming.

Alternatively conventional sequential programs can be developed for running on a single transputer.

Figure 4.1 Main development stages

#### 2 Write the source

Source code can be written using any ASCII editor available on the host system. Code can be divided between any number of source files. Source code must conform to the syntax required by the particular language compiler used. For C this is the ANSI standard; Occam source code must conform to the Occam 2.1 language definition.

#### 3 Compile the source

Each source file is compiled using the appropriate language compiler to produce one or more compiled object files in TCOFF format. Each file must be compiled for the appropriate transputer type or for a transputer class covering several compatible types. (More information about transputer types and classes is given in the Appendix B of the accompanying *Toolset Reference Manual*). Commonly used object code can be combined into libraries using the toolset librarian illibr.

Figure 4.2 Program build model

## 4 Link the compiled units

The compiled object files and libraries are linked together using the toolset linker ilink. This generates a single file called a *linked unit* in which all external references are resolved. The linking operation links in the library modules required by the program, which are selected by transputer type from the compiled library code. Object files for input to the linker can be generated by any TCOFF compatible compiler.

Programs developed for the transputer may comprise one or more linked units, created from separately compiled code and library modules. Linked units are assigned to run on a single transputer or one processor of a network of transputers during configuration. A linked unit is the smallest unit of code which may be placed on a transputer.

#### 5 Configure the program

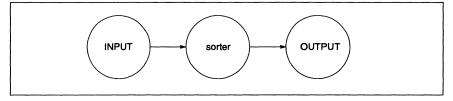

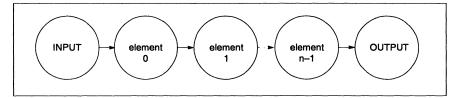

Configuration is the process of defining how the application is to be run on the hardware. It is achieved by writing a *configuration description*, assigning linked units to specific processors and connecting them by channels. By changing the configuration description it is possible to run a program on either a single transputer or on different network topologies. The description is processed by the configurer tool to produce a *configuration binary file*. Configuration is used for both single and multi-processor transputer programs.

The language used to write the configuration description is determined by the toolset. The C toolset provides a common configurer, icconf which can be used to configure programs written in C or OCCAM. Using icconf, modules written in different languages can be mixed at configuration level. The OCCAM toolset configurer occonf is designed to exploit the parallel programming model of the OCCAM language and is specific to the OCCAM toolset.

#### 6 Generate an executable file

Before a program can be run it must be made executable, i.e. *bootable*. This involves adding bootstrap and loading information. The result is a single executable file that it can be directly loaded onto the target. The collector can also include debugging and profiling kernels.

This is achieved using the collector tool icollect. The configuration binary file generated by the configurer is read by the collector. The collector can generate either a file which is suitable for loading onto the target hardware from the host via a hardware serial link or one for loading from ROM. The default behavior of the tool is to produce a boot-from-link bootable.

Whether a boot-from-ROM bootable is generated is determined by command line options specified to the configurer prior to creating the configuration binary file.

#### 7 Memory configuration

Some transputers (IMS T400, T414, T425, T800, T805) have a programmable memory interface which may be optionally configured using iemit. This tool generates a memory configuration file which can then be loaded into ROM; see section 4.6.

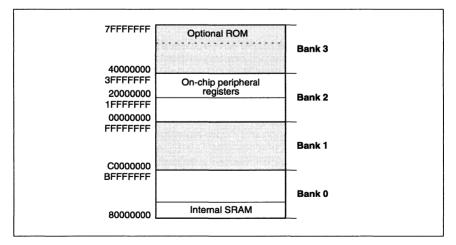

For the ST20450 (T450) transputer a memory configuration file is needed if there is any external memory. The memory configuration code for T450 TRAM modules is held in a ROM, so the memory interface will automatically be configured when the hardware is reset. Memory configuration files for other ST20450 hardware are generated using imem450. Generating such files is described in chapter 14.

#### 8 Load and run the program

A bootable boot-from-link file is loaded and run on the target hardware down a hardware serial link using the application loader irun, as described in

chapter 8. Once loaded the code begins to execute immediately. The application loader maintains the environment that supports the program's communication with the host.

Program development is supported by additional tools which provide facilities for creating object code libraries, automating the program build, and obtaining information about object files.

#### 4.1.1 Compatibility with previous toolset releases

For single transputer programs the configuration stage of the development process can be omitted. Instead bootable code can be generated directly from the linked unit by specifying a collector command line switch.

This mode of development is not recommended, however, and code built in this way cannot be debugged with the INQUEST interactive debugger.

If this mode is used, then the environment variable **IBOARDSIZE** should be set up; see section 4.10.3.

# 4.2 Compiling

The occam 2.1 compiler produces compiled code for a specific processor type or for a group of related processors called a transputer class. This compiler supports the IMS T212, M212, T222, T225, T400, T414, T425, T800, T801, T805 and ST20450 (also known as the T450). Each compiler has the same set of options to select the target transputer; these are listed in the Appendix B of the *Toolset Reference Manual*. The role of transputer types and classes in compilation and program development is also described in that appendix.

The compiler is capable of compiling code in one of three error modes. The standard error modes are HALT system and STOP process. A special mode, UNIVERSAL, enables code to be compiled so that it may be run in either HALT or STOP mode. The target processor and error mode must be specified for each compilation, using options on the command line. By default the compiler compiles for HALT mode, and when compiling for this error mode you may omit the error mode option. The error modes are described in section 6.2.1.

The compiler enables interactive debugging by default unless the compiler  $\mathbf{D}$  or  $\mathbf{Y}$  option is used.

The current range of transputer compilers generate code files in a format known as *TCOFF* (Transputer Common Object File Format). This standard has been adopted for the development of transputer compilers and enables modules written in different languages to be freely mixed in the same system.

Supplied with the Toolset is a set of libraries which provide run-time support, input and output operations, mathematical functions etc. The libraries supplied with this toolset are introduced in chapter 2.

Support is also provided for language extensions, interactive debugging, assembler inserts and software configuration of a network. Other operating features of the compiler may be changed by options and directives; see chapter 3 in the *Toolset Reference Manual*.

If the compiler detects any errors, a source file name and line number is displayed with an explanatory message and a portion of the source code surrounding the error.

If the compilation succeeds, the compiler creates a new object file in the current directory. The filename for the new file may be specified on the command line, or the default filename is derived from the name of the source file with the file extension .tco.

Detailed information about the compiler and libraries can be found respectively in the *Toolset Reference Manual* and the *Language and Libraries Reference Manual* supplied with this toolset.

# 4.3 Tools for building executable code

Three tools are used in sequence to generate the executable file from compiled object code:

- ilink the toolset linker which links separately compiled units

- occonf the configurer tool which generates a configuration binary file.

- icollect the code collector which generates an executable file for a transputer network from the configuration data file.

The configurer works on a configuration source file written by the programmer. The output of the configurer is an information file which is processed by the collector to generate an executable file. The executable file contains all the information needed to distribute, load, and run the program on a specific network of transputers.

## 4.3.1 Linker - ilink

The toolset linker ilink links separately compiled modules or object files and libraries together, resolving external references and generating a single *linked unit*. Linked units are referenced directly from configuration descriptions to map software onto specific arrangements of transputers.

The default output file is derived from the name of first file listed either on the command line or in a linker indirect file.

If required, the compiler libraries are automatically loaded by the compiler unless specifically disabled with the compiler  $\mathbf{E}$  option. If you are unsure whether your program uses the compiler libraries it is best to always link in the appropriate library anyway. Only library modules actually used by the compiled code will be included in the linked code file. The correct library for your program depends on the transputer type used for the compilation.

By default, the order in which the code modules are specified on the command line determines their order within the linked unit, library modules being placed after the separately compiled modules. This default can be overruled by using the compiler directive **#PRAGMA LINKAGE** and the linkage directive **#section**; see sections 3.13.7 and 10.4.6 in the *Toolset Reference Manual*. These directives enable the user to prioritize the order in which modules are linked together and so influence the use of on-chip RAM.

#### Linker indirect files

A linker indirect file is a text file containing a list of files and commands to the linker. Libraries to be linked in with the program may be listed in a linker indirect file, which is specified on the linker command line using the F option. The usual extension for a linker indirect file is .lnk. For OCCAM code, linker indirect files may be generated by imakef.

For example, a linker indirect file hello.lnk, listing all the files to be linked may be then the following command line will cause the linker to link the listed files for an IMS T425:

ilink -f hello.lnk -t5

Standard linker indirect files, which specify the compiler libraries, are supplied with the toolset, and may be explicitly specified on the command line or **#included** in a userwritten indirect file. The correct standard linker indirect file must be specified, depending the type of the target transputer, as shown in table 4.1. For further details of the compiler libraries see the Occam 2.1 Toolset Language and Libraries Reference Manual.

| Linker indirect file | Target transputers       |

|----------------------|--------------------------|

| occam2.lnk           | T212, M212, T222, T225   |

| occama.lnk           | T400, T414, T425, TA, TB |

| occam450.lnk         | ST20450                  |

| occam8.lnk           | T800, T801, T805         |

Table 4.1 Standard Occam linker indirect files

Each standard linker indirect file contains a list of OCCAM library files which may be required to be linked, but which are additional to those explicitly referenced by the program. These include compiler libraries and support for interactive debugging. Depending on the other inputs and options specified on the command line the linker will select the libraries it requires from the list supplied in the indirect file.

For example, the following linker indirect file will link hello.tco with the host i/o library and the compiler library:

hello.tco hostio.lib #include occama.lnk

If the above lines are in the file hello.lnk then the linker command line

ilink -f hello.lnk -t5

is equivalent to:

ilink hello.tco hostio.lib -f occama.lnk -t5

#### Mixed language programs

Mixed language programs require an appropriate linker indirect file for each language used.

For OCCAM, one of the indirect files listed in table 4.1 is always used. When the main program is written in C, one of the standard C start-up files should be used, as described in the *ANSI C Toolset User Guide*. However, if an OCCAM program calls functions written in C then it must be linked with C modules. In this case the standard C start-up files are not suitable and one of the C linker indirect files without a main entry point definition should be used. These linker files should also be used when incorporating a C program into an OCCAM program as if it were an OCCAM process.

For further details of mixed language programming, see chapter 11.

### 4.3.2 Configurer – occonf

The configurer generates configuration information for transputer networks from a textual *configuration description*. The tool prepares distribution information about a specific arrangement of transputers by analyzing the configuration description and creating a configuration binary file for the code collector tool to read.

Configuration descriptions are written using a transputer *configuration language* appropriate to the configurer used. The occonfiguration language is described in chapters 7 and 10.

#### 4.3.3 Code collector - icollect

Configured code cannot be loaded directly onto a transputer network for two reasons:

- 1 Object code produced by the linker and compiler tools contains extra information required by some tools. This information must be removed before the program can be loaded.

- 2 Code to be run on a board which boots from link, such as the IMS B008, requires the addition of bootstrap information to initialize the processor, load the program and start it running.

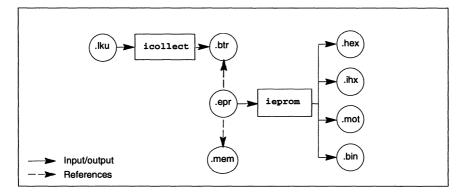

Extraneous data is removed and a boot-from-link bootstrap is added by the code collector icollect.

The code collector takes the binary file generated by the configurer (which refers to the linked code) and generates a single file that can be loaded and run on a transputer network. The collector generates all loading code. The output from the collector contains bootable code modules together with distribution information that is used by the loading code to place the correct code on each processor.

The collector may also generate non-bootable output files which may be dynamically loaded or loaded into ROM or RAM.

# 4.4 Loading and running programs

Boot-from-link code for single transputers and transputer networks is output from icollect and is loaded onto the transputer hardware using the host file server supplied with the toolset and described below. Boot-from-ROM code is processed by the EPROM programming tool and is introduced in section 4.6.

Chapter 8 describes how to load and run application programs in more detail.

### 4.4.1 Host file server

The AServer is provided with the Toolset, which can act as a combined host server and application loader tool. When invoked to load a program it both loads the code onto the transputer hardware and provides run-time services on the host for the transputer program including screen, keyboard and file i/o.

The version of the AServer supplied will depend on the host and hardware interface supported by the toolset. Chapter 8 describes how to load application programs onto the target hardware. The application loader irun is part of the AServer and is described in more detail in chapter 15 of the *Toolset Reference Manual*.

The AServer can be extended and customized by adding extra services, such as graphics servers. With the AServer, this can be done without modifying the standard host file server. Details of how to add services are given in the *AServer Programmers' Guide*.

#### 4.4.2 Skip bootables

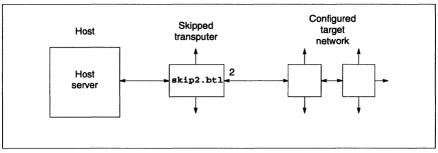

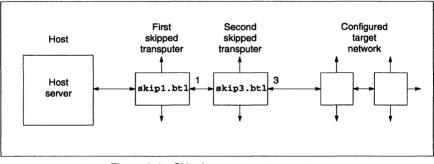

The skip bootables allow an application to run on a transputer subnetwork which is not directly connected to the host, but is connected via one or more intermediate transputers. For example, the root transputer (the transputer directly connected to the host) may not be part of the target network.

One or more of the skip bootables skipn.btl is loaded before loading the application code. Each skip bootable makes one transputer pass on everything it receives, so it becomes transparent to the software. Any code loaded is passed to the next transputer, and host communications are passed between that transputer and the host. Skipped transputers must not appear in the configuration.

The skip bootables are described in more detail in section 8.6.

# 4.5 Program development and support

Several tools are provided to assist in program development:

- ilibr the librarian which generates libraries of compiled code.

- ilist the binary lister which decodes and displays object files.

- imakef the Makefile generator which creates Makefiles for use with make automatic build utilities.

- imap the map tool which generates a memory map of the functions and variables used by the program.

#### 4.5.1 Librarian - ilibr

The librarian *ilibr* creates libraries of compiled code for use in application programs. A library is a concatenation of compiled files called modules. The linker only links in the library modules that are required. Code compiled by compatible TCOFF toolsets can be mixed in the same library. Libraries and the librarian are discussed in section 6.9.

### 4.5.2 Binary lister - ilist

The binary lister ilist decodes object code files and displays data and information from them in a readable form. Command line options select the category and format of data to be displayed. The lister can display symbolic names, code listing, the modular structure and indexing of libraries and external reference data.

For details of ilist see chapter 11 in the Toolset Reference Manual.

#### 4.5.3 Makefile generator - imakef

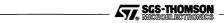

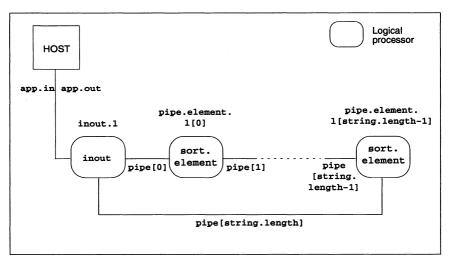

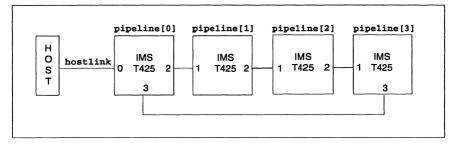

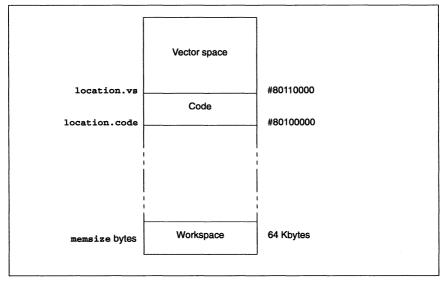

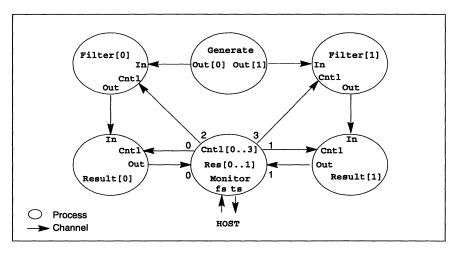

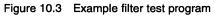

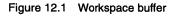

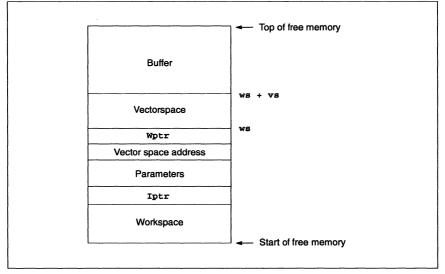

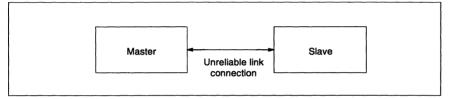

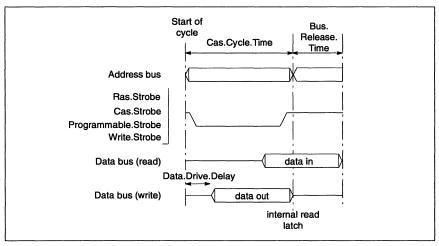

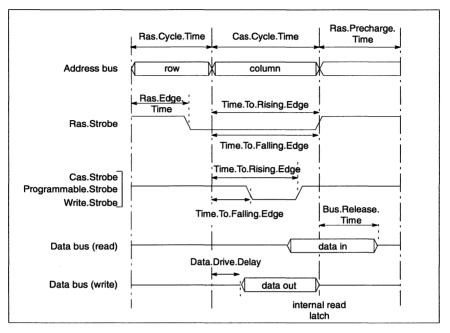

The Makefile generator imakef creates Makefiles for specific program compilations. Coupled with a suitable make build utility, it can automate building of executable code and greatly assist with code management and version control. A make utility is not supplied with the toolset.