# occam<sup>®</sup> user group · newsletter

for all users of occam and the transputer

Nº13

# July 1990

# Contents

| $^{2}$ |

|--------|

| 3      |

| 4      |

| 5      |

| 5      |

| 5      |

| 6      |

| 7      |

| 9      |

| 11     |

| 14     |

| 14     |

|        |

continued on back cover

Bill Roscoe receives the symbol of a Queen's Award for Technological Achievement from the Lord Lieutenant of Oxfordshire; with from left to right Tony Hoare, Tony Cox, Geoff Barrett, Michael Goldmsith, and David Shepherd (see page 74)

occam is a trade mark of the INMOS Group of Companies

# EDITORIAL

The fellow in the fancy dress on the front cover – the one holding the glass brick – is Bill Roscoe, receiving on behalf of Oxford University Computing Laboratory a Queen's Award for Technological Achievement from the Lord Lieutenant of Oxfordshire, representing the Queen. This award and a matching one to Inmos are a pat on the back for a team effort that yielded practical benefits: friends of the formal method will welcome these awards as recognition of the synergy of sound engineering practice and sound mathematical research. We should do what we can to use this sort of publicity to draw attention to the benefits of 'doing it properly'. In case you do not know it already, you will find the story behind the award on page 74.

If that seems to you like a bit of English parochialism, you will also find in this newsletter the usual spread of contributions. In keeping with the new geography of the nineties, let me offer you a report on the things *parallel* in Bulgaria (page 20) as well as Japan (page 30); and contributions from as far apart as Cornell and Moscow, Silicon Valley and Hong Kong, Exeter and Tokyo, Buenos Aires and 'somewhere in the Baltic'.

Looming ever larger on the horizon is the joint meeting of user groups in California next spring – Transputing 1991 – details of the call for papers for which you will find on page 14. Your ideas are also solicited for the workshops and tutorials that will happen at the same time, and indeed any good ideas you have to make this meeting the success it deserves to be would be welcomed by the committee. Who knows, we may even see the H1 there.

Speaking for the metropolitan occam user group for a moment, let me draw your attention to the intention to form a new special interest group dealing with development of the occam language (page 38). There is a lot going on, driven partly by the need for a higher-level means of expressing parallel programs than we now have, and partly of course by the potential capabilities of new generations of transputers and similar devices. If enough people are interested, the new group will meet at the York meeting (page 6).

Recent hardware developments seems to have been going all-out for performance, with a competition between the like of transputer boards with i860 on them (for example see page 83), and some spectacularly 'solid' lumps of very high-performance store-and-transputer on tiny TRAMs (see for example page 80). If you are looking for an affordable way to play with transputers – 'play' is pronounced 'teach' where I come from – the star of the show at the Exeter meeting, and a few other meetings too no doubt, has to be the *transputer education kit* from CSA (see pages 34 and 72).

## Name of a dog: 'Rover'

Those of you who were at the last meeting of the occam user group, in Exeter, may recall Peter Welch publicly raising the matter of a potential change of name for the group. At the risk of being confused with the British 'Liberal Democratic Party' (is it really called that still?) allow me to expand on the subject. ('Could you compose

#### Nº 13 July 1990

something...?' he said; why it ends up being me I do not know.)

There is apparently a perception 'out there' that anything called the *occam user* group cannot have anything to do with transputers; perhaps even that it is a club for rather odd European academic computing types. This does not match the 'forum for all users of the transputer' slogan in the chairman's address (Newsletter N? 10), nor the intention that occam should encompass 'not only the transputer but also its best applications, languages, support tools and methods.' We do need to make it clear that we are a forum for all users of the transputer – manufacturers, system designers, researchers through to end-users.

When all else fails, try changing the name. Peter suggests that we consider as possibilities:

- ▷ occam user group (original flavour);

- ▷ transputer user group;

- ▷ occam and transputer user group;

- ▷ transputer and occam user group;

- ▷ association for transputing machinery...

or any other good ones that come up. It is intended to put this to the membership at the forthcoming York meeting. What's in a name? Quite a lot perhaps.

Geraint Jones, 10 June 1990

## CONTRIBUTIONS TO THE NEWSLETTER

Please contribute announcements, articles, letters about anything that looks as though it belongs in your *Newsletter*. In particular we welcome letters, short articles or news about work being done with occam or transputers; calls for, discussion of, and reports on meetings of the group or related societies; ideas for new ways the group could help its members, or better ways of organizing what we do; details of material published elsewhere in books and journals; information about new products and courses.

Life would be easiest for the editor if you were able to submit material of longer contributions by electronic mail to **oug-news@uk.ac.oxford.prg**; or to send either unformatted ASCII files (on an IBM PC compatible floppy disk, or some other medium by negotiation) or clean camera-ready copy to the editor at the address below.

Camera-ready copy should be arranged not to look out of place when its linear dimensions are reduced to about 70%, i.e. from A4 originals to the A5 page size of this booklet. (This means: make sure your type is not too small!) Pictures are welcome as black-and-white prints, and will be subjected to the same reduction in size.

Copy for the next edition must arrive by 23rd November 1989.

Geraint Jones Programming Research Group 11 Keble Road Oxford OX1 3QD United Kingdom Tel: +44 865 273851 Fax: +44 865 273839 oug-news@uk.ac.oxford.prg

## PROCEEDINGS OF USER GROUP MEETINGS

Proceedings of the meetings of both the occam user group and the North American transputer user group are now published for the groups by the IOS Press, and should be ordered directly from the publishers.

The following volumes are available: in the Occam User Group Progress Reports series (prices in Dutch guilders/US dollar prices in the USA and Canada only)

- ▷ OUG-7, 14-16 September 1987, Grenoble, Parallel programming of transputer based machines, ed. Traian Muntean (pp. x+480, fl.230/\$110).

- ▷ OUG-8, 27-29 March 1988, Sheffield, Developments using occam, ed. Jon Kerridge (pp. vii+214, fl.92/\$50).

- ▷ OUG-9, 19-21 September 1988, Southampton, Occam and the transputer research and applications, ed. Charlie Askew (pp. vii+176, fl.92/\$50).

- ▷ OUG-10, 3-5 April 1989, Enschede, Applying transputer based parallel machines, ed. André Bakkers (pp. viii+318, fl.130/\$65).

- ▷ OUG-11, 25-26 September 1989, Edinburgh, Developing transputer applications, ed. John Wexler (pp. x+206, fl.115/\$55).

- ▷ OUG-12, 2-4 April 1990, Exeter, Tools and techniques for transputer applications, ed. Stephen J. Turner (pp. vii+244, fl.130/\$69).

and in the NATUG Progress Reports series

▷ NATUG-1, 5-6 April 1989, Salt Lake City, Utah, ed. G. S. Stiles (pp. 166, fl.120/ \$60).

- ▷ NATUG-2, 18-19 October 1989, Durham, North Carolina, ed. John A. Board, Jr. (pp. 462, fl.230/\$115).

- ▷ NATUG-3, 26-27 April 1990, Santa Clara, California, ed. Alan Wagner (pp. x+352, fl.190/\$ 95).

IOS also publish the most recent proceedings of others of the user groups,

- ▷ Proceedings of the 3rd transputer/occam international conference, Tokyo 1990, ed. Tosiyasu L. Kunii and David May (pp. x+308, fl.170/\$89).

- ▷ ATOUG-3, Proceedings of the 3rd Australian transputer and occam user group conference, Melbourne, 1990, ed. T. Bossomaier, T. Hintz and J. Hulskamp, (approximately 200 pages, fl.120/\$60).

and the proceedings of the international conferences on the applications of transputers organised under the auspices of the UK SERC/DTI 'Transputer Initiative'.

They are available from bookshops or direct from the publisher, either individually or on continuation orders.

Fax: +31 20 22 60 55

IOS Van Diemenstraat 94 ou ei agyd m 1013 CN, Amsterdam The Netherlands or in the USA and Canada IOS Postal Drawer 10558 Burke, VA 22009-0558 United States of America Fax: +1 703 250 47 05

or in Japan

IOS Japan Department Highway Development Co. Ltd 1st Golden Building, 8-2-9 Ginza 104 Tokyo – Chuoku Japan

Fax: +81 35 72 86 72

#### SIG publications

The proceedings of last year summer's international conference organised by the Artificial Intelligence SIG have appeared as the first volume of the *Wiley Communicating Process Architecture Series*, series editor David May.

▷ Parallel Processing and Artificial Intelligence, ed. Mike Reeve and Steven Ericsson Zenith, (pp. xvi+291; £29.95); John Wiley & Sons, 1989.

## NEWSLETTER BACK ISSUES

The first ten issues of the *OUG Newsletter* are now out of print. The principal information of continuing value in the early issues is the bibliography of articles related to occam and the transputer. I have all this information in a text file on VAX, and when I have worked out the easiest way to turn this into an acceptable printed document I will be producing a bibliography booklet which will be sent to all members.

Additions to the bibliography and to the list of members will no longer appear in the *Newsletter* as we now have plenty of material without them. Supplements to or re-issues of both these documents will now be produced on an ad hoc basis, but we hope at least once a year. These will be mailed to everyone on the occam user group membership list. *Michael Poole, INMOS*

## FORTHCOMING

#### TROLLIUS WORKSHOP

Cornell Theory Center, Cornell University, Ithaca, New York 24–26 July 1990

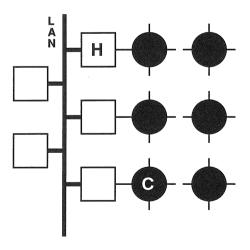

The Advanced Computing Research Institute (ACRI) of the Cornell Theory Center will be offering a three-day workshop on the Trollius programming environment for distributed-memory multicomputers.

Attendees will learn how to program and monitor parallel applications under Trollius Release 2.0. In addition, sessions will be offered on the design of the Trollius operating system, on use of special programming tools, and on porting Trollius. Guest speakers from industry will discuss related development projects.

Attendees will gain hands-on experience with the ACRI's transputer-based multicomputers, and will be given an opportunity to work on individual application programs. Attendees who are committed to using Trollius for existing projects are invited to remain through July 27, for in-depth consulting.

Attendees should have previous experience with UNIX systems, and in programming with C or FORTRAN. Previous experience in parallel programming is not required. The workshop will begin at 9:00 am on Tuesday, July 24 and end by 4:30 pm on Thursday, July 26. It will take place in the Theory Center Training Facility, Engineering/Theory Center Building, Cornell University, Ithaca, NY.

#### Accommodation

The following accommodations are within walking distance of the Theory Center Training Facility and many restaurants and shops. Attendees are responsible for their own reservations and meals. Paid parking is available three blocks from the Training Facility. Commercial airport limousine service is also available.

- Collegetown Motor Lodge Half a mile from Theory Center: 312 College Avenue, Ithaca, NY 14850; 607-273-3542, \$59-\$61 per night. Blocks of rooms have been reserved for this workshop. Please mention this when making your reservation.

- The Peregrine House Bed and breakfast, half a mile from Theory Center: 140 College Avenue, Ithaca, NY 14850; 607-272-0919, \$62-\$72 per night including breakfast.

#### Registration

Registration is limited to thirty people. The registration fee is \$75.00 for academic attendees, and \$150.00 for corporate attendees. This includes course materials and refreshments at breaks. Applications and payment must be received by June 12, 1990. Applicants should receive notification of the final selection by June 22.

To apply for this workshop, please contact the Conference Coordinator: e-mail registrations may be sent to donna@tcgould.tn.cornell.edu, and surface mail registrations and payment may be sent to

Tel: +1 607 255-8686

Donna Smith Conference Coordinator Theory Center Cornell University 265 Olin Hall Ithaca New York, 14853-5201 United States of America

## THIRTEENTH OCCAM USER GROUP TECHNICAL MEETING University of York, England 18-20 September 1990, York

The Occam User Group invites all those interested in the Programming and Application fo Transputer based Architectures to attend its thirteenth technical meeting which will take place at the University of York from 18th to 20th September 1990. The meeting will include invited speakers, submitted papers, exhibitions, a panel session with key speakers, and meetings of the Special Interest Groups. Full details of the meeting appear in separate publicity, or can be obtained from the meeting organiser:

Dr Hussein Zedan Department of Computer Science University of York York YO1 5DD England Tel: +44 904 432744 Fax: +44 904 432767 zedan@uk.ac.york.minster

## EDINBURGH PARALLEL COMPUTING CENTRE FIRST ANNUAL SEMINAR

James Clerk Maxwell Building, The King's Buildings, University of Edinburgh Monday 24th September 1990

The Edinburgh Parallel Computing Centre, inaugurated in January 1990, is an interdisciplinary focus for parallel computing projects involving research groups within the University of Edinburgh, with industrial partners and academic users throughout Europe. It incorporates research, service and commercial divisions, as well as participants from University departments, and affiliates from industry. Its function is to enable the exploitation of parallelism in all kinds of problem-solving by creating and making accessible expertise, tools and facilities. It supports applications work through research into the fundamentals of parallelism, development of support tools, parallel supercomputing services, consultancy, training and user support, and industrial liaison.

The Centre's principal computing resources include a 400-transputer Meiko Computing Surface, providing nationally networked multi-user access, a 64-processor Parsytec system, and a 4096-processor AMT Distributed Array Processor. It is also responsible for service on a second DAP and on a new Computing Surface of 64 i860 nodes, targeted on 'grand challenge' problems of science and engineering. The Centre also coordinates activities with other parallel hardware in participating departments, such as DEC Fireflies, a DEC VAX 6340 symmetrical multiprocessor, and a Sequent Symmetry.

The Centre is supported by industry (including a major contribution from Meiko Limited), the University of Edinburgh, Lothian Regional Council, and by the Department of Trade and Industry, with major recurrent funding from the Science and Engineering Research Council and from the Computer Board.

The Centre's first annual seminar provides an overview of its activities, the hardware configurations and the software environment, and presents a selection of research projects in science, engineering and artificial intelligence from the expanding community of some two hundred active users. It also offers demonstrations of the local computing resources, and of software developed on them. The Parallel Computing Centre subsumes the Edinburgh Concurrent Supercomputer Project, and the seminar continues the series begun by the Project's Annual Seminars. It is open to anyone with interests in the development and application of parallel computing.

The seminar begins with the formal opening of the Edinburgh Parallel Computing Centre by Professor E. W. J. Mitchell, Chairman of the Science and Engineering Research Council. The keynote speech will be given by Daniel Hillis, founder of Thinking Machines Corporation.

#### Programme

08.30 Registration and coffee

- 09.30 Opening of the Edinburgh Parallel Computing Centre: Prof E. W. J. Mitchell FRS, Chairman of SERC; Sir David Smith FRS, Principal, University of Edinburgh

- 09.40 Edinburgh Parallel Computing Centre status: Overview: D. J. Wallace; Service and utilisation: M. W. Brown; Industrial affiliation: D. B. Mercer

- 10.30 Coffee

- 11.00 Keynote speaker W. D. Hillis (Thinking Machines Corporation)

- 11.50 S. F. Reddaway (Active Memory Technology): Parallel data transforms

- 12.10 Computing surface software environments

- 12.30 Lunch and demonstrations

- 13.50 to 17.00 in three parallel streams:

- ▷ Applications talks will include:

- Molecular graphics

- Theorem-proving using MISD parallelism

- Simulating a shared-memory multiprocessor architecture

- QCD on i860s; a UK Grand Challenge

- o Neural nets for oil-well faces determination

- Database searching on the DAP

- o Parallel implementations of the adaptive Hough transform

- Mapping commercial CFD codes onto Transputer systems

- ▷ Tools and methods talks will include:

- Linda/Prolog

- Simulation tools for parallel computers

- Performance programming for i860s

- Cellular automata on Transputers: the CAPE environment

- Constructive Solid Geometry

- Genetic algorithms for process planning

- 3-d surface tracking

- The heteroarchitecture project: SIMD and MIMD together

- ▷ Demonstrations

Presentations will be twenty-minute talks. There will be eight in each stream, with a break for tea and coffee from 15.10 to 15.40.

17.00 Close

#### Venue

The seminar will be held in the James Clerk Maxwell Building at the King's Buildings, the University's 'science campus' in South Edinburgh. This is some ten miles from Edinburgh Airport, and two and a half miles South of the city centre.

#### Fees

The seminar fee is  $\pounds$ 55. This includes admission, lunch, refreshments, and a Directory describing system, utilities and application developments within the EPCC and its user community. There is no charge for industrial affiliates or registered academic users of the Centre's services.

Fees must be paid in Sterling, by cheque or banker's draft or credit card (Access/ Eurocard/Mastercard/Visa can be accepted). Fees are NOT refundable except in the event of cancellation of the Seminar.

## Accommodation

Delegates can book accommodation for any nights from 20th to 24th September. This will be provided in the Pollock Halls, about one mile North of the King's Buildings and a mile South of the city centre. We are providing accommodation for several days in advance of the meeting for the convenience of those who are also attending the 13th Technical Meeting of the Occam User Group, which takes place in York shortly before the Seminar, on Tuesday–Thursday 18th–20th September.

## Industrial Affiliation

An Industrial Affiliation Scheme exists to foster collaboration with industry and to promote awareness and exploitation of concurrent computing. The annual seminar forms part of a two day meeting organised for Industrial Affiliates. Members and Partners should complete and return the separate form which is being sent to them.

This seminar is sponsored by:

▷ DTI/SERC Transputer Initiative

and co-sponsored by:

The British Computer Society (Parallel Processing Specialist Group)

▷ The Institute of Physics (Computational Physics Group)

▷ The Scottish Development Agency

Contact for more information:

CEP Consultants Ltd 26-28 Albany Street Edinburgh EH1 3QH Great Britain phone: +44 31 557 2478 fax: +44 31 557 5749

## SYMBOLS VERSUS NEURONS? Joint IEE and OUG Colloquium IEE, Savoy Place, London 1st October 1990

## Advance Announcement

This one-day meeting is being organised by the Institution of Electrical Engineers (Professional Group Committee C4 Artificial Intelligence) in collaboration with the

occam user group newsletter

Occam User Group (Artificial Intelligence Special Interest Group). It will take place at the London headquarters of the IEE (Savoy Place, London WC2R 0BL) on 1st October 1990.

This colloquium will be the second International Conference of the OUG Artificial Intelligence SIG.

## Aims of the Colloquium

In recent years, transputer-based parallel computers have gained in significance as a platform for the development of AI applications and tools. Sub-symbolic or neo-connectionist approaches are occupying a growing position at the side of classical symbolic approaches. This colloquium will highlight this development with a comparison between symbolic and connectionist approaches and their implementations. In posing the question 'Symbols versus Neurons?' a forum will be provided for directly tackling the central conflict of the AI debate today.

## Conference Programme

#### Keynote speakers

- ▷ Professor Tom Addis (University of Reading, UK), Knowledge and the Structure of Machines

- Pau Bofill (Barcelona Polytechnic, Spain) and José del Millan (EC, Ispra, Italy), A Systolic Algorithm for Back Propagation: Mapping onto a Transputer Network

#### Invited speakers

- Professor Kimmo Kaski (Oxford University, UK), Simulating Neural Networks in Distributed Environments

- Professor E. von Goldammer (Universität Lübeck, West Germany), Neural Nets

Applications in Medicine

- Professor André Bakkers (Twente University, Enschede, The Netherlands), Applications of Neural Control

- Dr Jean Sallantin (CRIM, France), Artificial Intelligence for Genomic Interpretation

- Dr Lyubomir Stoychev (IMS, Sofia, Bulgaria), Relational and Differential Logic for Knowledge Processing

- ▷ Dr Terence C. Fogarty (Bristol Polytechnic, UK), Using the Genetic Algorithm to Adapt Intelligent Systems

- Reem Bahgat (Imperial College, London, UK), Symbolic Constraint-Based Reasoning in PANDORA

- Joachim Stender (Brainware GmbH, Berlin, West Germany), Machine Learning Applications on Transputers

- Zoltan Schreter (Universität Zürich, Switzerland), Connectionism A Link between Psychology and Neuroscience?

- Steffen Schulze-Kremer (Freie Universität, Berlin, West Germany), Inductive Protein Structure Analysis using Transputers

## Further Information

The conference programme has been planned by Joachim Stender, chairperson of the OUG AI SIG. Further information on the content of this programme should be addressed to:

| Joachim Stender/Eva Hillebrand<br>Brainware GmbH | Tel: $+49 30 463 30 58$<br>Fax: $+49 30 469 46 49$ |

|--------------------------------------------------|----------------------------------------------------|

| Gustav-Meyer-Allee 25                            |                                                    |

| D-1000 Berlin 65                                 |                                                    |

| West Germany                                     |                                                    |

| or to:                                           |                                                    |

| Professor T. Addis                               | Tel: +44 734 875123                                |

| Department of Computer Science                   | Fax: $+44 734^{\circ}751994$                       |

| University of Reading                            |                                                    |

| P O Box 220                                      |                                                    |

| Whiteknights                                     |                                                    |

| Reading                                          |                                                    |

| Berkshire RG6 2AX                                |                                                    |

| United Kingdom                                   |                                                    |

## **Registration Details**

This meeting will be advertised by the IEE in the normal manner for its colloquia series. All bookings will be handled by the IEE on their registration forms. (These are not yet available.) At the moment, it is anticipated that the registration fee will be the normal one (i.e.  $\pounds 26.50$  for IEE members and  $\pounds 43.50$  for non-members, pounds sterling). OUG members may also qualify for the reduced fee.

In the meantime, delegates wishing to attend should send their names and addresses to:

Professor P. H. Welch Computing Laboratory University of Kent Canterbury Kent CT2 7NF United Kingdom Tel: +44 227 764000 Fax: +44 227 762811 phw@uk.ac.ukc

#### FIRST NORDIC TRANSPUTER SEMINAR

Provisionally located onboard a Viking Line ferry, between Sweden and Finland 5-7 October 1990

#### Call for speakers and abstracts

The aim of this seminar is to provide a forum for users of transputer-related technology in the Nordic countries. Researchers and application developers from academia, industry and government are invited to present results and experiences from their work.

#### The seminar

The provisional site for the seminar is a ferry between Stockholm and Helsinki. All standard conference facilities like slide- and overhead-projectors will be available. Themes for the seminar may include, but are not limited to the following:

- ▷ real-time systems

- ▷ super-computing

- ▷ artificial intelligence

- ▷ modelling and simulation with occam

- data acquisition

- ▷ future transputer and occam projects

- ▷ HW/SW design methods

- ▷ industrial applications

The seminar aims at giving a representative survey of current transputer activities in the Nordic countries. There should also be excellent opportunities for informal contacts with fellow transputer users. Workshops are being planned and we hope to involve all seminar attendees. We welcome suggestions on particular themes for workshops. We also welcome proposals from any person or group that wishes to run such a workshop.

Commercial companies will be invited to have exhibitions and demonstrations at the seminar.

#### Sponsors

- ▷ TH's Elektronik AB, Sweden

- ▷ Peder Pedersen AS, Denmark

- ▷ Tahonic AS, Norway

- ▷ ITT Disti, Finland

## Programme committee

- ▷ Arne Sommerfelt, Senter for Industriforskning, Oslo, Norway

- ▷ Bjørn Rudberg, Forsvarets forskningsinstitutt, Norway

- ▷ Kari Leppälä, Technical Research Centre, Oulu, Finland

- ▷ Ralph Back, Åbo Akademi, Finland

- ▷ Jan Bardino, R.C. International, Århus, Denmark

- > Jesper Nørly, Technical University of Denmark, Lyngby, Denmark

- Martin Tørngren, Royal Institute of Technology, Stockholm, Sweden

- Lars Estreen, Royal Institute of Technology, Stockholm, Sweden

- Niklas Ljung, TH's Elektronik AB, Sweden

## Invited speakers

Representatives from Inmos will hold talks on the following topics:

▷ Future Inmos products, H1 the next generation transputer, the future of occam.

Current status of the transputer, what market niche does the transputer hold in competition with other processors like Intel i860, Harris RTX 2000, Motorola 88000, AMD29000, i960, etc.

We are currently contacting several other potential speakers from central departments of transputer related activities.

## Contributors

Speakers are invited to submit an extended abstract of 2-4 pages. Accepted abstracts will be collected in a seminar proceedings report, which will be distributed at the seminar.

The abstracts should be submitted in A4 format and ready for photo-copying. Please avoid colour photographs or other illustrations that are not well rendered by photo-copiers. Names, titles and institution of all authors should be on the first page of the abstract. If there are several co-authors the speaker at the seminar should be indicated.

In addition to the abstract we would like to have the full mailing address, telephone number, fax number and e-mail address (if available) of the author(s) to be notified. The abstracts should be mailed to the committee member closest to you in the list below:

| Kari Leppälä                         | Bjørn Rudberg                  |

|--------------------------------------|--------------------------------|

| Technical Research Centre of Finland | Forsvarets forskningsinstitutt |

| Computer Technology Laboratory       | Box 25                         |

| Box 201 (Kaitoväylä 1)               | N-2007 Kjeller                 |

| SF-90571 Oulu                        | Norway                         |

| Finland                              |                                |

| Jesper Nørly                         | Martin Tørngren                |

| Technical University of Denmark      | DaMek/Machine Elements         |

| Building 421 – IK                    | Royal Institute of Technology  |

| DK-2800 Lyngby                       | 10044 Stockholm                |

| Denmark                              | Sweden                         |

|                                      |                                |

## Deadlines

15 August 1990: Deadline for submission of extended abstract.1 September 1990: Accepted speakers will be notified before this date.1 September 1990: Deadline for seminar enrolment and payment of fee.

14 September 1990: Final seminar program is distributed.

5 October 1990: Ferry leaves Stockholm, returning on 7th.

## Fees and accommodation

The seminar registration fee will be around 1000-1500 Swedish Kronor, the exact amount will be published later. The fee will include accommodation and meals on

the ferry. Requests for further information and booking details regarding the seminar should be directed to:

Niklas Ljung TH's Electronik AB Box 3027 16303 Spånga Sweden Tel: +46-8-362970 Fax: +46-8-7613065

## NORTH AMERICAN TRANSPUTER USERS GROUP FALL MEETING

Cornell Theory Center, Cornell University, Ithaca, New York 10–11 October 1990

#### Call for papers

The 1990 Fall meeting of the North American Transputer Users Group will be held in Ithaca, New York, on October 11 and 12. Contributions are being solicited in the areas of hardware, software, and applications. Presentations will be allotted 20 minutes each, with ample additional time for questions; this format will allow for approximately 24 talks. Additional papers may be presented at poster sessions if there is sufficient interest. All accepted papers will appear in a published proceedings.

Abstracts of 1000–1500 words must be received by 15 June 1990. Notices of acceptance will be sent out by 1 July, and final drafts of accepted papers will be due by 1 August. Authors should indicate on the abstract whether they would be willing to present the paper in a poster session.

Abstracts (electronic mail submissions of the abstracts are preferred) should be submitted to:

David L. Fielding Cornell Theory Center Cornell University 265 Olin Hall Ithaca, NY 14853 United States of America. +1 (607) 255-8686 fielding@tcgould.tn.cornell.edu

## TRANSPUTING 1991 First world conference of national transputer and occam user groups Santa Clara, California 22-26 April 1991

The first world conference of all Transputer and/or Occam User Groups will take place at:

| TRANSPUTING 1991 |                                 |  |

|------------------|---------------------------------|--|

| Place:           | Santa Clara, California         |  |

|                  | at the Sunnyvale Hilton         |  |

| Dates:           | week commencing 22nd April 1991 |  |

#### Call for Papers

The goals of this conference are:

- ▷ to present 'state-of-the-art' research on all aspects of parallel computing based upon communicating process architectures;

- ▷ to demonstrate 'state-of-the-art' products and applications from as wide a range of fields as possible;

- ▷ to progress the establishment of international software and hardware standards for parallel computing systems;

- ▷ to provide a forum for the free exchange of ideas, criticism and information from a world audience gathered from Industry, Commerce and Academia;

- ▷ to establish and encourage an understanding of the new software and hardware technologies enabled by the transputer;

- ▷ to promote an awareness of how these technologies may be applied and what their advantages are.

The conference themes will *include*: education and training issues, formal methods and security, performance and scalability, porting existing systems, parallelisation paradigms, tools, programming languages, support environments, standards and applications.

Applications *include*: embedded real-time control systems, workstations, supercomputing, consumer products, artificial intelligence, databases, modelling, design, data gathering and the testing of scientific or mathematical theories.

The conference programme will contain invited papers from established international authorities in these fields together with submitted papers. The international programme committee, presided over by Professor P. H. Welch (OUG Chair), is now soliciting papers on all areas described above. All papers will be fully refereed. Only papers of high excellence will be accepted. The proceedings of this conference will be published internationally and copies will be given to delegates when they register at the start of the meeting.

## Programme committee

The members of the programme committee will be invited experts from Industry and Academia together with existing committee members from the joint organising user-groups based in Australia, France, Germany, India, Japan, Latin America, New Zealand, North America, Sweden, and the United Kingdom.

The organising load is being spread around the world, to ensure that all points of view and expertise are properly represented and to obtain the highest standards of excellence.

## Instructions to authors

Seven copies of submitted papers (not exceeding 16 pages – single-spaced, A4 or US 'letter') must reach one of the Program Committee members nominated below before 1st October 1990. Authors will be notified of acceptance by 15th November 1990. Final camera-ready copy will be required by 6th January 1991.

A submitted paper should be a draft version of the final camera-ready copy. It should contain most of the information, qualitative and quantitative, that will appear in the final paper, i.e. it should not be just an extended abstract. Please submit your paper to the committee member closest to you in this list:

Professor P. H. Welch Chair, OUG Computing Laboratory The University Canterbury Kent CT2 7NF United Kingdom Tel: +44 227 764000 Fax: +44 227 762811 Professor T. L. Kunii Chair, OUG Japan Dept of Information Science University of Tokyo 7-3-1 Hongo, Bunkyo-ku Tokyo Japan Tel: +81 3 816 1783 Fax: +81 3 818 4607 Dr J. Hulskamp Chair, AOTUG Department of Communication and Electrical Engineering Royal Melbourne Institute of Technology GPO Box 2476V Melbourne 3001 Australia

Tel: +61 3 660 2453 Fax: +61 3 662 1060 Dr D. Stiles Chair, NATUG Dept of Electrical Engineering Utah State University Logan UT, 843222-4120 United States of America Tel: +1 801-750 2806 Fax: +1 810 750 2992

Dr K. S. Venkatesh Centre for the Development of Advanced Computing 2/1 Brunton Road Bangalore – 560 025 India Tel: +91 812 575781 Fax: +91 812 563183

Dr R. Lins Chair, OUG: Latin America Department de Informatica Universidade Federal de Pernambuco P O Box 7851 50739-Recife-PE Brazil Tel: +55 812 713052 Fax: +55 813 264880 (The British Council)

#### Conference structure

## PAR ... exhibition / demonstrations (Monday .. Friday) SEQ ... seminars / workshop (Monday) ... conference papers (Tuesday .. Thursday) ... seminars / workshop (Friday)

## Call for tutorials and workshops

On the Monday of Transputing 1991, we shall be holding some tutorials on the fundamental principles underlying *transputer* technologies and various design paradigms for exploiting them. On the Friday, we shall be running several workshops that will focus directly on a range of specialist themes (e.g. real-time issues, formal methods, AI, super-computing, ...).

We welcome suggestions from the community for particular themes which should be chosen for these tutorials and workshops. In particular, we welcome proposals from any group that wishes to run such a tutorial or workshop. A submission should give details of the proposed programme, numbers of people to attend (minimum and maximum) and how much equipment (if any) is needed for support. Please submit your suggestions and/or proposals to one of the Committee listed above by 1st October 1990.

## Further information

Companies and other organisation wishing to be associated with Transputing 1991 should contact either Peter Welch or Dyke Stiles at the addresses above.

## THE 4TH TRANSPUTER/OCCAM INTERNATIONAL CONFERENCE Tokyo, Japan 21-24 May 1991

Following the successful and timely international third conference, OUG Japan is pleased to announce the *Fourth Transputer/Occam International Conference* to be held on 21st-24th May 1991 in Tokyo. This year we set 'Concurrency: from formalism to implementation' as the main theme of the conference. The topics include (but are not restricted to):

- ▷ formalism, specification and design;

- ▷ concurrent system development;

- ▷ application cases;

- ▷ practice and experiences;

- ▷ hardware and software;

- ▷ architecture.

This series of conferences has been a place to find a wide variety of Transputer based parallel processing systems through original refereed papers, invited talks, tutorials and commercial exhibits. The official language of the conference is English. Simultaneous translation from English to Japanese is provided whenever necessary. The registration fee is  $\pm 40\,000$  and this includes:

- ▷ a copy of the conference proceedings;

- ▷ admission to all technical sessions, tutorials and exhibits;

- ▷ admission to all lunches;

- $\triangleright$  admission to the final party.

## Call for papers

Full papers in English are solicited and should contain previously unpublished original high-quality results.

Please submit five copies of the paper to:

Prof. Dr Tosivasu L. Kunii Program Chairman The 4th Transputer/Occam International Conference Department of Information Science Faculty of Science The University of Tokyo 7-3-1 Hongo Bunkyo-ku, Tokyo 113 Japan

Phone: +81 3-812-211 x 4116 Fax: +81 3-818-4607 kunii@is.s.u-tokyo.ac.jp

The submitted paper should be typed, double spaced, about 10-20 pages in length with an abstract of 100-200 words and a maximum of 10 keywords. All papers will be peer reviewed and will be assessed with regard to their quality and relevance. The proceedings will be published for distribution at the conference and also for later dissemination. Submitted papers must be received by the program chairman by 1st December 1990. Acceptance or rejection of the papers will be notified by 15th January 1991. Final camera-ready papers must be received by the program chairman before 10th March 1991.

For tutorial proposals and any suggestions contact:

| Tel: +44 454 616616 |

|---------------------|

| Fax: +44 454 617910 |

|                     |

|                     |

|                     |

|                     |

|                     |

For local arrangements contact:

Mr Kazuto Matsui, Secretary Occam User Group, Japan SGS-Thomson Microelectronics KK **INMOS Business Centre** Nisseki Takanawa Building 4th Floor 18-10 Takanawa 2-chome Minato-ku, Tokyo 108 Japan

Tel: +81 3-280-4125 Fax: +81 3-280-4131

## NORTH AMERICAN TRANSPUTER USERS GROUP FALL MEETING Duke University, Durham North Carolina 18-19 October, 1989 John A. Board, Duke University

The second 'official' meeting of the North American transputer users group was held on 18–19 October 1989 in Durham, North Carolina; Duke University served as academic sponsor of the event. Approximately 120 researchers from the USA, Canada, and five other countries were joined by about a dozen vendors of transputerrelated products at this most successful meeting.

A full technical program over the two days included 26 delivered papers and several more poster contributions covering a very broad range of hardware, software, and applications topics. Two invited talks described major transputer projects under way in the United States. T. Bowen *et al.* from Bellcore are using transputers to prototype large high performance distributed databases that are essential in providing telephone services. D. G. Shea from IBM Yorktown Heights described his group's experience in designing and now using VICTOR, a family of transputer research workstations with from 16 to 256 nodes.

A session on performance evaluation tools provided evidence of the increasing hardware and especially software lengths people are willing to go to for more detailed information about the performance of their algorithms on transputer networks. A hardware and applications session described data acquisition and control applications of the transputer, a transputer-based computer input device for disabled persons, and the use of transputers for dataflow applications and in hypercube architectures.

Communications and network topologies were the subject of a session in which strategies for run-time reconfiguration and deadlock-free packet switching were discussed. Systolic computing on transputer arrays also received attention.

The second day of the meeting was dominated by discussions of applications and software environments. A session on physical and mathematical applications described work in parallel neural network simulation, parallel simulated annealing, and fast parallel multiplication. There is increasing interest in operating systems and message routing/task farming kernels for message passing architectures; papers on the current status of Linda and ALPS (from Ohio State) along with a paper describing a graphical design environment for transputer systems development filled a session on operating systems and environments. The issue of operating systems for transputer networks is of such importance to users here that a special session on this subject was planned for NATUG 3, to which all developers of such systems kown to us were invited.

The final session on software and algorithms described several efforts in bringing logic (AND/OR process models) and object-oriented (C\_NET and C++) programming to transputer systems. There were also discussions of implementing bin-packing algorithms and wavefront algorithms on transputer networks.

All attendees were interested, as always, in comments from various SGS Thomson/INMOS representatives about present and future transupter products. I think my personal feelings are proably typical of those of many in attendance; I have been worried about stagnation in the transputer family especially in light of the rash of 'killer micros' – the various high performance RISC chips – announced in the last year, but I am also encouraged by the renewed vigour Thomson seems to be bringing the the transputer effort.

John Board

jab@dukee.egr.duke.edu

General and Program Chair, NATUG 2 Dept. of Electrical Engineering Duke University Durham NC 27706 United States of America

## LETTER FROM BULGARIA Hugh Glaser and Chris Jesshope, University of Southampton

In March we attended the Workshop on Parallel Distributed Processing in Sofia, Bulgaria, organised by the Centre for Informatics and Computer Technology on behalf of the Bulgarian Academy of Sciences.

The Academy and Centre have had long-standing links with UK academic institutions, notably the Dataflow and Parsifal projects at Manchester, as well as Functional programming at Imperial and Electronics at Southampton. A number of these contacts were present, as well as academics from the City University and universities in Belgium, France, Greece, East and West Germany and the USSR.

Any of the participants at the workshop would expect a report to begin by noting that the social programme was very enjoyable. As most of us arrived early there was time to view the sites of Bulgaria. We visited the famous Rila monastery, a remarkable Escher-like construction, and took a stroll at the top of a (almost) snowcovered mountain, as well as seeing some of the beautiful countryside. One aspect of Bulgaria that Western visitors always find difficult to reconcile is the staggering difference between city and country life; it appears like a hundred year discontinuity in time. Continuing with the social aspects, the food was always acceptable, and often quite excellent. The organisation of both the social and technical programmes seemed to run effortlessly (although this was only an impression), and our hosts made strenuous efforts to ensure we were comfortable.

The workshop programme was split about half and half between Bulgarian presentations and foreign visitors. Since much of the non-Bulgarian work is familiar to UK researchers, it is perhaps more interesting to discuss the Bulgarian contributions.

Much has clearly happened since we attended the previous workshop one year ago. The political changes have probably not changed the technical directions very significantly, but they do now suffer from the familiar uncertainty about future funding levels as they await the decisions of the politicians, who in their turn await the decision of the people. The subjects of the presentations were quite different, however. Last year there was a considerable variety of subjects: as well as papers on networks and transputers, there were papers on functional and dataflow programming, and some excellent descriptions of their vector-processing supercomputer and high fidelity numerical analysis package; this year the emphasis was almost entirely on networks, transputers, and their use. The only variety was provided by the foreigners.

Apart from the social and technical programmes, we were invited to visit the institutes and one of their manufacturing plants. At the institute we were shown their supercomputer and their prototype multi-transputer system (48 transputer), which they expect soon to extend to a 72 transputer machine. This year we were shown around the Pravez personal computer plant, and it was rather intimidating to see the level of investment that has taken place, along with the capacity for expansion. It was also rather exciting to finally spot a British machine among all the US and West German hardware.

Towards the end of the workshop our hosts reported, with some excitement, that they had been asked to consider the possibility of holding next year's occam user group meeting in Bulgaria, perhaps on the Black Sea. Although neither of us have ever visited this area, it is well known to us through information provided by a Bulgarian research student who has been working in this department. The climate is Mediterranean and the sea is consistently warm, being 18–25°C during May to September. What is more, during one of the excellent meals in Sofia, one of our hosts entertained us with stories of how he had manipulated Bosses and Unions ruthlessly in order to acquire a yacht for his institute, for the recreation of the employees. Who knows; it may be OUG at sea! On the evidence of this visit it is clear that such a meeting would be both enjoyable and interesting.

| Hugh Glaser                                    | Tel: +44 703 593670 |

|------------------------------------------------|---------------------|

| Department of Electronics and Computer Science | Fax: +44 703 593045 |

| University of Southampton                      | Telex: 47661        |

| Southampton SO9 5NH                            | hg@uk.ac.soton.ecs  |

| United Kingdom                                 |                     |

## POSTCARD FROM EXETER Tony Curtis, University of Kent

Even the most neutral of observers would have noticed a biblical theme to the Exeter OUG. A comment to the effect of 'I expect it will snow next' proved to be all too prophetic. I wonder where the plagues of locusts went? As is usual for Devon, the weather played its normal tricks, however we plucky delegates ploughed on regardless of the climatic variations.

The campus itself is rather on the hilly side, and has not completely succumbed to a proliferation of concrete at every available site. Thus there are still plenty of wooded and green areas on campus, which are nice to see.

On to the conference itself. It followed the usual three day format with papers, exhibitions from various companies and product announcements, and of course gastronomic excesses.

The papers were as varied as one might expect. Most aspects of computing were represented from real-time control of robots to graphical programming environments. There were some useful ideas about monitoring channels in one talk through to transformational methods for program generation in another. Something for everyone really. One speaker was unable to attend due to illness, but the day was saved by Peter Welch who nimbly stepped in and gave a talk about standards and safetycritical systems.

The remuneration for the presentations was a bottle of beer (which is apparently lethal and should not be drunk until the next century!) and a bottle of wine (presumably less damaging).

The lecture theatre was the largest one in the Statistics department, which was where all the talks and exhibitions were held. The lecture theatre itself showed distinct signs of having been in the middle of a botanical explosion with flowers strewn along the stage at the front. Fortunately no speakers became lost in the flowers.

The exhibitions were held along the corridor outside the lecture theatre. Both software and hardware were represented ably by companies such as Transtech, Division and CSA, who had an inexpensive transputer board on display. INMOS also gave a product announcement during which the availability of the source of an occam compiler was indicated. This should certainly open up the use of occam to other systems; occam needs to be seen as accessible if it is to gain acceptance outside of purely transputer-based systems (i.e. abstracted from the hardware aspects).

The culinary content of the conference was increased somewhat by the conference meal on the Tuesday evening. It was held in the long refectory in Devonshire House, which is the main Student Union building and is also where the lunches were held. An inpromptu speech from Derek Partridge, who is head of the computer science department at Exeter wound up the meal; for someone who was not expecting to have to give a speech he extemporised very well!

Slotted into all this high living were the Special Interest Groups (SIGs). Unable to clone myself, I only attended three.

The graphical tools SIG focused on the type of information that should or could be extracted for real-time monitoring. Other topics of discussion included windowing programming tools for parallel programming.

The operating systems SIG had become just 'environments'. This did not seem to stop people talking about operating systems. Naturally, the main ones discussed were those with which attendees had had experience. These included MEiKOS, Helios, and GENESIS amongst others. No one knew all that much in detail about Mach or Chorus, but the general consensus was that this seemed to be about the right way of doing things. The emergence of Amoeba in the near future was also mentioned. The SIG was also adjudged to be interested in programming tools for parallel processing. Specific mention was given to MEiKO's CS Tools package as a usable system.

The third SIG I attended was the AI one. This spent all its time talking about the organisation (or not) of a one-day conference or colloquium which will focus on the two main threads of AI research today, namely the neural versus the symbolic approach (see page 9).

As ever, the Roger Shepherd Memorial Joke Contest was held toward the end of the conference. There appeared to be a distinct dearth of jokes this time, with some efforts being scribbled down just beforehand. The prize went to a University of Kent concoction, this being the one about occam programmers and sharp culinary tools. On the whole though, one feels that this selection of jokes lacked a certain something. As for why it is a 'memorial' contest, who knows? Roger looked well enough, or does he know something we do not?

The big debating point was about the change of name from 'occam user group' to something which reflected the group's activities more closely. The 'Association for Transputing Machinery' seemed to be a favourite, though personally I would like to retain a reference to the software side in the name. As Occam's Razor doesn't say...

Nomini non sunt multiplicanda praeter necessitatem

Names should not be multiplied beyond necessity

so perhaps the list from which to choose should be kept small.

The conference was organised by the computer science department at Exeter. Special thanks are due to Stephen Turner for all the work he put into keeping us in order and editing the proceedings. Thanks are also in order for the secretarial and support staff who kept everything else going.

## HOW MANY LINKS DOES IT TAKE TO SCREW IN A TRANSPUTER?

In celebration its patron's re-appearance at the occam user group meeting in Exeter, there was held a Roger Shepherd Resurrection Joke Contest. The man himself was prevailed upon to read out the contributions, subject to some real-time precensorship, and amongst the printable contributions were:

Q: How do you tell an Inmos salesman that you need an array of T400s?

A: Give him a ring or hit him with a pipe!

That got a very frosty reception, as did

Q: Why do you keep transputers in anti-static foam?

A: To stop them getting a shock from their community charge.

For non-UK readers 'community charge' is the official name of a relatively new and absolutely unpopular local tax in Britain. (Whoever heard of a popular tax?)

Q: Why do occam programmers eat with their fingers?

A1: Security forbids their using forks.

Me I liked that one, but then there was

A2: They don't use knives because common sense suggests they aren't allowed sharp objects.

and to growing audience sympathy

A3: Because they aren't used to using advanced tools.

Cutting. Very cutting.

Q: What have the evolution of the T400 and man in common?

A: The missing link(s).

Q: What's the difference between an ant scratching and an oug speaker?

A: You can hear an ant scratching.

Well, perhaps if you had been there...

Q: What will still have eighty-four legs?

A: The H1 design team if it meets Pistorio's schedule.

Best not to comment on that one perhaps.

Q: Why don't occam programmers use suitcases?

A: Because they fold all their clothes up and put them in their pockets.

Then there was a signed contribution from  $The \ Lads$  describing a number of familiar sounding names:

Division 'The Pirhana brothers' Transtech 'East London wide boys' Meiko 'Arthur Daley Software' Inmos 'Hammer and Axe boys'

If you don't understand that, all the better for all concerned. (The editor of the newsletter, the publishers, and my maiden aunt all wish to make clear that any resemblance of the purely fictional characters in the preceding joke to companies or persons alive or deceased is purely for the purposes of ridicule, and has nothing to do with us, squire; you want The Lads.) It seems a bit hard on Meiko who seemed not to be represented at the exhibition this time, despite having paid for a stand.

Your correspondent found himself unexpectedly pressed into service as clap-ometer and on the basis of audience response awarded the first choice of bottle to Colin Willcock (have regulars readers heard this name before?) for the advanced tools, and the second bottle to John Fisher for the stridulating hymenopterous emmet. (Why is my spelling checker complaining?) It was not clear which winner came off best in their choice between red plonk and a very small bottle of a very potent brew that needed to be preserved into the next century before being drunk. gj

## NORTH AMERICAN TRANSPUTER USERS GROUP SPRING MEETING Sunnyvale, California 26-27 April 1990 Alan Wagner, University of British Columbia

The third NATUG meeting was held April 26 and 27th in the center of the Silicon Valley. About 120 people attended the meeting, approximately 10% of the participants were from outside of North America. In total there were over 30 presentations, 21 papers in the regular sessions, 6 papers in a special session on software systems and environments, and a further 4 papers in the poster session. There were 13 vendors present with a variety of hardware and software products. The proceedings have been published by IOS Press under the title *Transputer Research and Applications 3*.

As usual, the meeting attracted papers from throughout the world. About 40% of the presented papers were from outside North America. The international participation was most welcome and gave us the opportunity to learn more about what our overseas counterparts are doing. The papers broadly fell into two categories: applications, and software systems and environments. The first day was devoted to transputer-related algorithms and applications, several of which involved specially designed hardware or transputer configurations. The technical sessions were as follows:

TransAcq: real-time data acquisition and analysis system for optical spectroscopy, Brad V. Duncan, Linda S. Powers and G. S. Stiles;

- The development of a visual telephone for the deaf: using transputers for real-time image processing, Scott Galuska;

- ▷ Using the transputer in the design of high performance architectures dedicated to the implementation of OSI transport protocol, Christophe Diot and Michel Ng. X. Dang;

- ▷ TCP/IP Networking using transputers, Roger M. A. Peel;

- Revised simplex method on a network of T800 transputers, J. Luo, F. Bruggeman and G. L. Reijns;

- ▷ Transputer implementation of the EM algorithm for PET image reconstruction, Fred U. Rosenberger, Gerald C. Johns, David G. Politte and Charles E. Molnar;

- ▷ The fast multipole algorithm on transputer networks, John A. Board, Jr. and James F. Leathrum, Jr.;

- ▷ A parallel-processing subsystem for the generation of 3D cardiac images from CT, Scott R. Cannon and Stephen J. Allan;

- Molecular dynamics simulations on a systolic ring of transputers, K. Boehncke, H. Heller, H. Grubmuller and K. Schulten;

- ▷ Simulation of self-organizing neural nets: a comparison between a transputer ring and a connection machine CM-2, K. Obermayer, H. Heller, H. Ritter and K. Schulten;

- Parallelizing, using process-and-data-decomposition (PADD) approach on a multiring transputer network – an example, Hamid R. Arabnia and Mary R. Robinson;

- ▷ Hardware voting of transputers in real-time nMR fault-tolerant systems, J. Standeven and M. J. Colley;

- ▷ Transputer-based multi-robot simulation, Hubertus Franke, D. Shea and L.C. Zai;

- ▷ Partitioned, replicative neural networks for co-operative robot systems, Martin J. Dudziak.

The last talk of the day was by Andy Rabagliati from Inmos on the H1, the nextgeneration transputer. He discussed mainly the memory organization of the H1.

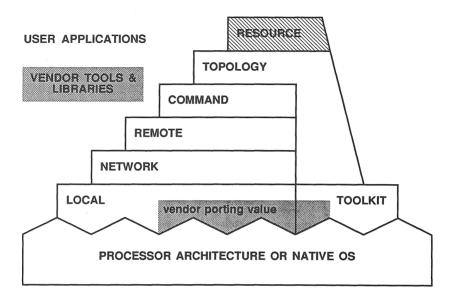

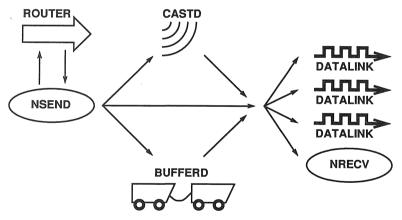

The morning of the second day was devoted to the special session organized by Dyke Stiles on topology-independent programming systems. Each participant gave a presentation and the talks were followed by a panel discussion. The presentations included:

- ▷ Deadlock-free parallel programming on transputer networks, Prasad Vishnubhotla from Ohio State University,

- ▷ The Express/Cubix system, Adam Kolawa from Parasoft;

- ▷ *Helios*, Jason Cockroft from MIMD Systems;

- ▷ System-level parallel programming based on Linda (a call to standards), Wm Leher;

- ▷ Dynamic parallel programming, Jan Graat from Parsec;

- ▷ Muliptle language programming with STRAND, John Florentin from Birkbeck College;

- ▷ Process level parallelism in a UNIX environment, Paul King from Real Time Systems;

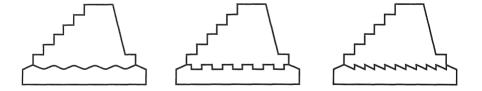

▷ The Trollius programming environment for multicomputers, Dave Fielding et al. It was clear from the presentations that transputer languages, systems and environments have matured considerably over the last year. These systems provide at one level or another a topology-independent approach to programming transputers. I hope that in the coming year as these systems become more widely available we will all have a better opportunity to evaluate them.

The afternoon of the second day was devoted to software systems and environments. The following papers were presented:

- ▷ Multigraph for the transputer, Ben Abbott, Csaba Biegl and Janos Sztipanovits;

- ▷ Graphical visualization of distributed algorithms, Oliver Vornberger and Klaus Zeppenfeld;

- ▷ A visual programming system for the transputer, M. Roberts and P. M. Samwell;

- ▷ An efficient and flexible implementation of ALT, S. W. Lau and F. C. M. Lau;

- ▷ A dynamic distributed system using remote procedure calls in a message passing system, Tom Hintz and Mark Phillips;

- ▷ A virtual architecture for investigating dynamic load balancing on transputer networks, I. A. Horton and S. J. Turner;

- ▷ Mapping search graphs onto arbitrary transputer networks (or making PROLOG parallel), Douglas Eadline.

Posters were presented during the breaks on Thursday afternoon and Friday. These included:

- ▷ On the performance of ALT in Occam, K. M. Shea and F. C. M. Lau;

- ▷ A transputer-based motion detection/tracking algorithm, Andrew P. Bernat and James Rupel;

- A transputer fault-tolerant processor, Jorge L. Ortiz, Willie L. McCoy and Michael M. Thomas;

▷ Applications of transputer interface to DSP vector processor, Richard L. Tutwiler. There were, for the first time, awards given for the best presentations. Ballots were distributed to all participants and tallied after the meeting. First place went to Wm Leher for his talk entitled 'System-level parallel programming based on Linda (a call to standards)' and second place went to Scott Cannon for his talk on a parallel-processing subsystem for the generation of 3D cardiac images.

NATUG4 is scheduled for 11-12th October at Ithaca, New York (see page 14).

The first world transputer meeting is scheduled for April 1991 (see page 14) and will also be held in the Silicon Valley. Those of us who attended NATUG 3 can attest to the beauty of California at this time of year. Sunnyvale lived up to its name. Most of the social events were held pool-side in an informal and relaxed atmosphere. I would like to encourage our international colleagues to make the pilgrimage to Silicon Valley next year.

## THE THIRD TRANSPUTER/OCCAM INTERNATIONAL CONFERENCE Tokyo, Japan 17th-18th May 1990 Kazuto Matsui, OUG Japan

The third transputer/occam international conference was held in Tokyo. This time we invited key speakers from the UK, sponsored by the British Council and Inmos Ltd. The emphasis of this conference was to present recent progress, survey basic principles and architectural overviews through invited papers and tutorials including some parallel processing applications. A CSP short course was also provided by Dr Jeff Sanders, Oxford University, in the tutorial session. The student session was an experiment to explore the potential of using transputers and occam to teach students, and doing research with them on parallel processing.

The CSP Short Course and student session were held at the Sanjo Kaikan Conference Hall on campus at the University of Tokyo on 15th and 16th May. The rest of the sessions and exhibitions were held at Seiryo Kaikan beside the Hibiya High School on 17th and 18th May. As the official language was English, we provided simultaneous translation from English into Japanese and vice versa. This enabled us to communicate well with each other throughout the conference.

### CSP short course (Jeff Sanders)

Around a hundred people attended this short course, which was a first trial in Japan as far as I know. Dr Jeff Sanders prepared three texts for us ('An introduction to CSP', 'An incremental specification of the Sliding-Window Protocol', and his handout material) and taught us the main ideas of CSP. Initially there was a barrier to be overcome because most of the CSP notation was unfamiliar to us, but his superb teaching technique and his personality changed our attitude to learning CSP. All of the students, university teachers and industrial people were impressed by his teaching. Some people were were getting enthusiastic to learn more about CSP. Thank you, Dr Sanders! I sincerely recommend people in other countries that you should also take an opportunity to study CSP, otherwise you will not really understand what occam and the transputer are.

#### A modular, decentralised, transputer-based architecture for multi-sensor data fusion (Hugh Durrant-Whyte)

A fully decentralised architecture for data fusion problems was discussed. As this architecture takes the form of a network of sensor nodes, computation is performed locally and communication occurs between any nodes and this has many desirable properties.

#### Reasoning about distributed algorithms in CSP: application to remote sensing (Jeff Sanders)

CSP is a higher level language from which occam code can be obtained by routine down-coding but which is supported by a body of laws and a hierarchy of semantic models. That is why occam is used for the implementation of concurrent algorithms. Its simplicity and efficiency make it appealing for that purpose.

#### Student session

#### Parallel processing of quadtree images (Ryo Mukai)

To improve the speed of image processing, parallel processing of quadtrees was investigated. Parallelising the computation of convolutions could not be made to achieve a good efficiency because the algorithm and the structure of the network requires a great deal of communication. Eventually some people suggested a useful idea to solve this problem.

#### Divide and conquer in parallel processing (Shigeru Chiba)

'Divide and conquer' is a major technique in the solution of large problems, dividing them into smaller parts. Exploiting parallelism in this technique gains more efficiency. To implement this technique in parallel, both ring and tree topologies were tried and the ring topology was slightly faster than the tree.

## Network and Topology (I)

#### Transputers and routers: components for concurrent machines (David May)

David May talked about why the router and latency-hiding method will be important when many transputers are connected. VLSI routers can provide routing between a large number of links, minimising network delays. Very fast routers with fewer links can be constructed using high-speed technology. Transputers and routers can be combined on VLSI chips to provide network nodes. This functionality will be supported by the next transputer.

#### Implementing functional languages on networks of transputers (Chris Howson)

A graph reducer for lazy functional languages using a network of transputers was reported. The main concern was correctly to transmit directed acyclic graphs from one transputer to another.

A general configurable multigrid implementation for the solution of three-dimensional elliptic equations on a transputer network (Osama El-Giar)

The implementation of a generally configurable version of the full multigrid method on arrays of transputers was made. The design of a parallel algorithm to allow for the easy distribution of computation for the case of Poisson's equation was presented.

## Image Processing

### A visual interface for a transputer network and its application to moving image analysis (Wiwat Wongwarawipat)

A VIT (Visual Image for Transputer) system was constructed to perform high-speed parallel image-processing on a transputer network. The major application of this system is to analyse moving-object image-data, projected onto an image plane, and to get the shape and displacement of the object at the same time.

#### Parallel 2D-FFT algorithm on practical multiprocessor systems (Kazuhito Itoh)

An algorithm for the direct computation of a two-dimensional fast Fourier transform was considered. Mesh, 2D torus and rectangular implementations were made. Although the interprocessor communication time increases, the number of multiplications can be reduced to three-quarters of that required for conventional indirect 2D-FFT.

#### Design and implementation of software-based real-time video codec using multi-transputer architecture (Masahiro Ichikawa)

A software based real-time video codec using multi-transputer architecture was implemented. The coding algorithm was based on the CCITT standard. By using several suitable parallel processing methods, a fully programmable real-time video codec was developed. Real-time operation will be achieved using QCIF at the rate of ten frames per second when one hundred transputers are used.

## Network and topology (II)

#### TéNOR: a symbolic configurer for the SuperNode architecture (Jean Marc Adamo)

A symbolic configurer for the SuperNode machines was presented. TéNOR makes it possible to describe network configurations symbolically. TéNOR automatically checks whether the described topology meets the architectural constraints of the SuperNode machine and produces a configuration for the transputer network.

#### Implementing recursion on a double ring topology (J. L. Jacquemin)

Recursion was implemented on transputers by using a double-ring topology. This solution gives some major advantages. An efficiency reaching 90% can be expected.

## Scientific applications

#### Scientific applications on transputer arrays: some experiments in MIMD parallelism (Tony Hey)

A survey of some problems inhibiting the use of parallel processing was presented, along with an overview of useful computational models and programming paradigms for parallel machines based on transputer arrays.

#### A design methodology for synthesising one-dimensional systolic algorithms (Youji Iihuni)

A method for synthesising 1–D systolic arrays from a serial algorithm having triple do-loops was proposed. Six systolic algorithms for the LD decomposition and two systolic algorithms for least-squares were synthesised.

## A scientific application on a transputer system (Makoto Nishizaki)

A general scientific application system was implemented on transputers. A simulation program called CSSL (Continuous System Simulation Language) has been running only on sequential computers. A parallel implementation was developed using a PROLOG parser which generates occam source code. This could help many people who have to convert sequential codes into parallel ones.

## Parallel algorithms (I)

#### Modelling queries in relational databases for parallel processing (J. L. Jacquemin)

Some research in optimising parallel queries in relational databases was presented. The feasibility of this modelling was explained, consisting of the following stages: standardising query structures; building the query tree; transformation algorithm; and parallel processing.

#### Graph theory on a transputer array (James Allwright)

Finding the largest graph of a given valency and diameter is essentially the problem of network design expressed in the precise terms of graph theory. Here a heuristic algorithm to search for solutions to the problem was developed, based on Lin and Kernighan's algorithm for the travelling salesman problem.

## Parallel algorithms (II)

### A decentralised dynamic scheduling scheme for transputer networks (Satoshi Nishimura)

A new scheme for mapping dynamically created tasks onto a transputer network was proposed. The scheduler on each processor inspects the loads of the neighbouring processors and transfers excessive tasks to less loaded processors. It is now planned to implement the dynamic scheduling scheme on transputer networks.

Variations on the ALT implementation on the transputer (Dennis N. M. Ho)

This paper reported some of analysis and experiments with the occam ALT and PRI ALT constructs. It discussed the efficiency of the ALT realised on the transputer.

#### Progress towards an interactive solid modelling system on parallel computers (Peter Dew)

Research into parallel algorithms and systems is needed to support the computational geometry algorithms that arise in the automation of design and manufacture of solid parts and assemblies. The primary purpose of the system is to provide a realistic environment to evaluate the performance and scalability of parallel algorithms and software.

## FAST ROUTING IN JAPAN J. W. Sanders, Oxford University

The six-pm-Sunday direct flight from Heathrow to Tokyo is as kind a way of travelling to Japan as present airlines allow. The UK contingent – Peter Dew (Leeds), Hugh Durrant-Whyte (Oxford), David May (Inmos) and I – with only one smoker amongst four was split in inverse proportion to that of the JAL flight: our first warning of Japanese air space. In Tokyo we joined Tony Hey (Southampton, on leave at IBM Watson), the remaining invited speaker at the OUG conference starting in a day and a half.

But first a hundred or so of the participants had booked in for a  $1\frac{1}{2}$  day CSP course. I took it, slowly, through an introductory overview, through the most important parts of Hoare's book, then through a case study on communications protocols. No matter how careful the English presentation, language is a problem in Japan; but handouts help, and the enterprising Kimio Maruyama had translated my *Introduction to CSP* into Japanese, for release with the video of the lectures.

#### Nº 13 July 1990

Sixty more participants joined us for the third Japanese OUG meeting. In the first invited address Hugh Durrant-Whyte presented a decentralised design for Kalman filtering, and applied it to multi-sensor data fusion. In this lovely example of a distributed algorithm it is far from obvious that pairwise communications, achieved by relay through intermediate nodes, are done consistently. Proof of that fact would be an interesting exercise. (Durrant-Whyte had obviously confirmed it for some representative cases.)

In his address David May discussed the consequences of Valiant's observations on general-purpose parallel machines, introduced a router chip, and showed how it might be used effectively. One important comment that seemed to lack general appreciation: extra concurrency (allocation of excess processes to processors) helps to cover communication delays between processors. That is to be contrasted with the impulse to assign one process to each processor in order to gain maximum 'efficiency'.

Tony Hey surveyed MIMD parallelism and neatly reinforced May's talk by reporting experiments that measured execution time. He drew attention to the need for portability and generality of parallel machines and to the need for higher-level languages to drive them.

Peter Dew reported progress on a transputer-based solid-modelling system, called *Mistral-3*. The idea was to choose an architecture that permitted parallelism to be determined by the application. For that, care was taken in the choice of data structures: a hierarchically-ordered spatially-divided solid model was selected, and decentralised operations (like ray tracing) implemented in terms of it.

For further details, and for the other talks, the reader is referred to the proceedings (*Transputer/occam Japan 3*, edited by T. L. Kunii and D. May, IOS Press, 1990; see page 4 of this newsletter, also the preceding report on the meeting itself). However it is worth mentioning the high standard of two student papers. Both were given by undergraduates in the Kunii Laboratory at the University of Tokyo and both experimented with the use of tree-like networks of transputers. That evening we visitors were taken to dinner by Professor Kunii at a restaurant he has been frequenting for thirty years. I had the pleasure of discovering, with the aforementioned students, recursive definitions of graphs of small diameter; we found them to be more accessible than the usual pictures (like that of the Petersen graph).

After dinner, at about 9:30 pm, Kunii showed the visitors over his laboratory. His secretary was still there, working hard. On Friday evening after the conference I travelled to Sendai by *Shinkansen* (the bullet train) with Professor Nakamura. En route, at 9:55 pm, my companion's watch alarm sounded. He explained that on a normal working day that indicated he had 15 minutes to catch the last bus home. It seems that much of evening television in Japan is aimed at women; men stay in their offices until quite late. Indeed the day's *sumo* bouts are only covered at about 11:00 pm.

On Saturday most of the other visitors headed home from Tokyo. In Sendai I began phase two of my trip: visiting various labs selected by the British Council. I began with Nakamura's group, including Kobayashi and Horiguchi, in the Department of Mechanical Engineering at Tohoku University. Their primary interest is in general-purpose pipelines and, with experience of three such pipelines behind them, they prefer the transputer one—largely because of the ease of programming in occam. On Saturday morning about thirty students attended my seminar outlining how Z