# **RG-750** VME Graphics Board User's Manual

# Rastergraf, Inc.

1804-P SE First St. Redmond, OR 97756

(541) 923-5530 FAX (541) 923-6575

web: http://www.rastergraf.com

email: <a href="mailto:support@rastergraf.com">support@rastergraf.com</a>

Release 2.0

November 8, 2006

# NOTICES

Information contained in this manual is disclosed in confidence and may not be duplicated in full or in part by any person without prior approval of Rastergraf, Inc. Its sole purpose is to provide the user with adequately detailed documentation to effectively install and operate the equipment supplied. The use of this document for any other purpose is specifically prohibited.

The information in this document is subject to change without notice. The specifications of the RG-750 graphics board and other components described in this manual are subject to change without notice. Although it regrets them, Rastergraf, Inc. assumes no responsibility for any errors or omissions that may occur in this manual. Customers are advised to verify all information contained in this document.

The electronic equipment described herein generates, uses and may radiate radio frequency energy, which can cause radio interference. Rastergraf, Inc. assumes no liability for any damages caused by such interference.

Rastergraf, Inc.'s products are **not** authorized for use as critical components in medical applications such as life support equipment, without the express consent of the president of Rastergraf, Inc. This product has been designed to operate with VMEbus computers and other compatible user-provided equipment. Connection of incompatible hardware is likely to cause serious damage. Rastergraf, Inc. assumes no liability for any damages caused by such incompatibility.

Rastergraf, Inc. assumes no responsibility for the use or reliability of software or hardware that is not supplied by Rastergraf, or which has not been installed in accordance with this manual.

Rastergraf is a trademark of Rastergraf, Inc.

All other trademarks and copyrights are the property of their respective owners.

Copyright © 2006 by Rastergraf, Inc.

## PREFACE

This manual contains hardware and operating information for the RG-750 color graphics board. The standard configuration for the RG-750 includes 1 Mbyte of DRAM for instruction storage, 1Mbyte of VRAM, an RS-232 serial interface for mouse or serial use, an AT keyboard interface, on-board AFGIS firmware, interface PAL set -PS25, and programmable video displayed in a 60Hz non-interlace format for use with VGA & SVGA video monitors. The RG-750 also has an optional interface for the Planar EL7768MS electroluminescent flat panel.

The RG-750 offers the following six programmable resolutions:

640h x 480v x 4 640h x 480v x 8 800h x 600v x 4 800h x 600v x 8 1024h x 768v x 4 1024h x 768v x 8

The RG-750 is available in one basic configuration with the options listed below.

## Options

To specify an option(s), add the option letter(s) to the basic part number. For example, RG-750-M4 would specify the basic configuration with 4 Mbytes of DRAM.

| Opt <u>i</u> on | Description                           | A24 Address | A32 Address |  |

|-----------------|---------------------------------------|-------------|-------------|--|

| -PS25           | Interface PAL Set E00000h E000 0000h  |             |             |  |

| -PS26           | Interface PAL Set D00000h D000 0000h  |             |             |  |

| -PS27           | Interface PAL Set 800000h 8000 0000h  |             |             |  |

| -PS28           | Interface PAL Set A00000h A000 0000h  |             |             |  |

| -CP             | Custom Interface PAL Set xxxxxh xxxxh |             |             |  |

| -50Hz           | Specifies 50 Hz video timing          |             |             |  |

| -M4             | Specifies 4 Mbytes of DRAM            |             |             |  |

| -EL1            | Interface and Firmware for EL7768MS   |             |             |  |

| -BNC            | Optional RGB BNC video connectors     |             |             |  |

## **Related Documents**

AFGIS Instruction Set Manual AFGIS Programming Manual AFGIS Assembler Manual AFGIS C Graphics Library Reference Manual AFGIS C Programming Manual AFGIS Application Interface Manual TMS34010 User's Guide (available from Texas Instruments

## Limited Warranty

Rastergraf, Inc warrants to the original purchaser that this product is free from defects in material and workmanship under normal use for a period of 1 year from date of shipment.

Rastergraf, Inc. will, at its option, repair or replace the product if Rastergraf, Inc. determines it is defective within the warranty period and it is returned to Rastergraf, Inc., freight prepaid.

Rastergraf, Inc. shall be under no obligation to furnish warranty service if:

- 1. Attempts to repair or service the product are made by personnel other than representatives of Rastergraf, Inc.

- 2. Modifications are made to the hardware or software by personnel other than representatives of Rastergraf, Inc.

- 3. Damage results from connecting the hardware to incompatible equipment.

There is no implied warranty of fitness for a particular purpose. Rastergraf, Inc is not liable for any consequential damages.

# TABLE OF CONTENTS

| 1.0 Introduction                                           | 1.0  |

|------------------------------------------------------------|------|

| 1.1 Overview                                               | 1.1  |

| 1.2 Features                                               | 1.2  |

| 2.0 Installation                                           | 2.0  |

| 2.1 Board Installation                                     | 2.1  |

| 2.2 Board Layout                                           | 2.1  |

| 2.3 Jumper Options                                         | 2.2  |

| 2.3.1 J1 Interrupt Request Select                          | 2.3  |

| 2.3.2 J2 A24/A32 Address Select                            | 2.4  |

| 2.3.3 J3 Run/Halt at Power-up                              | 2.4  |

| 2.3.4 J5 Resolution Select/Configuration                   | 2.5  |

| 2.3.5 J6 Clock Select                                      | 2.6  |

| 2.3.6 J7 RS-232 TxD/RxD                                    | 2.6  |

| 2.3.7 J8 RS-232 RTS/CTS                                    | 2.6  |

| 2.3.8 J19 Testable Strap                                   | 2.7  |

| 2.4 LEDs                                                   | 2.7  |

| 2.5 Connectors                                             | 2.7  |

| 2.5.1 DB15 Video Output Connector                          | 2.8  |

| 2.5.2 BNC Video Connectors                                 | 2.8  |

| 2.5.3 Planar EL7768MS Electroluminescent Display Connector | 2.9  |

| 2.5.4 AT Keyboard Connector                                | 2.11 |

| 2.5.5 RS-232 Serial Connector                              | 2.12 |

| 2.5.6 VMEbus Pin Assignment                                | 2.13 |

| 3.0 Operation                                              | 3.0  |

| 3.1 Power Up Display                                       | 3.1  |

| 3.2 Operation Overview                                     |      |

| 3.3 RG-750 Host Interface Registers                        |      |

| 3.3.1 Data Transfer Convention                             |      |

| 3.3.2 Transferring Data                                    | 3.3  |

| 3.4 RG-750 Memory                                          |      |

| 3.4.1 RG-750 Memory Map                                    |      |

| 3.4.2 EPROM                                                |      |

| 3.4.3 DRAM                                                 |      |

| 3.4.4 Fixed RAM                                            | 3.5  |

# TABLE OF CONTENTS

| 3.4.5 VRAM                                        | 3.6  |

|---------------------------------------------------|------|

| 3.4.6 RS-232 Interface                            | 3.7  |

| 3.4.7 Programing the 2691 UART                    | 3.7  |

| 3.4.8 Keyboard Interface                          |      |

| 3.4.9 Video DAC                                   | 3.9  |

| 3.4.10 Control Register                           |      |

| 3.4.11 Remapping DRAM with ROMDIS                 | 3.10 |

| 3.5 Status Register                               | 3.10 |

| 3.6 Interrupts                                    | 3.11 |

| 3.7 Interrupts to the RG-750 from the VMEbus      | 3.11 |

| 3.7.1 From host to the RG-750                     |      |

| 3.7.2 Resetting the RG-750 with the NMI Interrupt |      |

| 3.8 Interrupts to the VMEbus from the RG-750      | 3.13 |

| 3.9 Coordinate System                             |      |

| ) Specifications                                  | 4.0  |

| 4.1 Operating Environment                         | 4.1  |

| 4.2 DC Power Requirements                         | 4.1  |

| 4.3 Video Output                                  | 4.1  |

| ····                                              |      |

## Appendix A

| Interface PAL Set EquationsA.0 |

|--------------------------------|

|--------------------------------|

## Appendix B

| VME CPU to RG-751 Data Transfers B.0 |

|--------------------------------------|

|--------------------------------------|

# **1.0 INTRODUCTION**

# **Chapter Contents:**

| The RG-750 Color Graphics Board |

|---------------------------------|

| 1.1 Overview                    |

| 1.2 Features                    |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

|                                 |

## The RG-750 Color Graphics Board

## 1.1 Overview

The RG-750 is a high performance 6U graphics board, powered by the TMS34010 graphics processor, and designed for VMEbus applications. Major features of the RG-750 are its on-board AFGIS firmware with over 250 highly optimized graphics primitives for easy graphics programing, its ability to support real-time multi-tasking operating systems with its unique pointer based graphics environment, its advanced hardware architecture with mouse and keyboard interfaces, and extensive C programing support.

The RG-750 is ideal for simple embedded system applications, because it is easy to program and because it does its own local graphics processing, freeing the VMEbus host to do other things while the RG-750 is creating graphics in parallel.

The real power and versatility of the RG-750 is evident when it is used with real-time multi-tasking operating systems that require several tasks to independently generate graphics on the video screen. Each task can have its own colors, font, screen position, etc., and can independently create graphics on the video screen without affecting the colors, font, screen position, etc. of any other task.

Each task can have its own private pointer based graphics environment with all the necessary buffers, variables, and low level drawing parameters. The host processor (typically the driver) selects the environment for the current task by updating a pointer in Fixed RAM before the task runs any graphics code. Because the graphics environment is pointer based, switching the environment takes little time, typically less than 15 usecs, which has a minimal impact on the task's allocated time slice.

The RG-750 is supported with the AFGIS C Graphics Library which has over 125 high level C functions which have been optimized for use with the on-board AFGIS firmware. A driver is typically required for use with the AFGIS C Graphics Library and today's modern real-time operating systems. Drivers are available for several of the popular real-time operating systems, and custom driver development is available from Rastergraf, Inc. for operating systems not currently supported with drivers.

The driver and AFGIS C Graphics Library are easy to install, and once installed, allow the user to begin using the RG-750 without regard for the details of the hardware interface, as these are handled by the driver. The C functions provided by the AFGIS C Graphics Library are linked at compile time, and in effect extend the C functions of the system's C compiler to include those provided by the AFGIS C Graphics Library.

The combination of advanced hardware architecture, optimized on-board graphics primitives, and extensive C programing support, make the RG-750 an ideal low cost, high performance solution for many of today's challenging graphics opportunities.

## 1.2 Features

The RG-750 provides the following major features and options:

• Programmable Resolutions:

640h x 480v x 4/8

800h x 600v x 4/8

1024h x 768v x 4/8

- 16/256 Colors

- Interlaced or non-interlaced video

- TMS34010 Graphics Processor

- 1 Mbyte of DRAM (option for 4 Mbytes)

- 1 Mbyte of VRAM

- Mouse and Keyboard Interfaces

- Video DAC with 256x24 color look up table (Bt478)

- On-board firmware with over 250 highly optimized graphics primitives to draw text, windows, circles, arcs, polygons, fills, fatlines, pattern fills and more!

- Fast graphics environment switching, less than 15 usec to support real-time tasks

- Supports parallel processing for improved system performance

- Interrupts to and from the VMEbus

- Sync polarity options

- Sync on green option

- Application interface to extend the on-board graphics primitives with downloaded TMS34010 code.

# 2.0 INSTALLATION

| Chapter Contents: |                                                                |

|-------------------|----------------------------------------------------------------|

|                   |                                                                |

|                   | 2.1 Board Installation                                         |

|                   | 2.2 Board Layout                                               |

|                   | 2.3 Jumper Options                                             |

|                   | 2.3.1 J1 Interrupt Request Select                              |

|                   | 2.3.2 J2 A24/A32 Address Select                                |

|                   | 2.3.3 J3 Run/Halt at Power-up                                  |

|                   | 2.3.4 J5 Resolution Select/Configuration                       |

|                   | 2.3.5 J6 Clock Select                                          |

|                   | 2.3.6 J7 RS-232 TxD/RxD                                        |

|                   | 2.3.7 J8 RS-232 RTS/CTS                                        |

|                   | 2.3.8 J19 Testable Strap                                       |

|                   | 2.4 LEDs                                                       |

|                   | 2.5 Connectors                                                 |

|                   | 2.5.1 DB15 Video Connector                                     |

|                   | 2.5.2 BNC Video Connectors                                     |

|                   | 2.5.3 Planar@ EL7768MS Electroluminescent<br>Display Connector |

|                   | 2.5.4 AT Keyboard Connector                                    |

|                   | 2.5.5 RS-232 Serial Connector                                  |

|                   | 2.5.6 VMEbus Connector                                         |

\_

## 2.1 Board Installation

Install the RG-750 board in a VMEbus card slot. The RG-750 must plug into VMEbus connectors P1 and P2.

#### CAUTION!

Switch off power to the VMEbus before installing the RG-750 to avoid possible damage to the graphics board or host hardware.

## 2.2 Board Layout

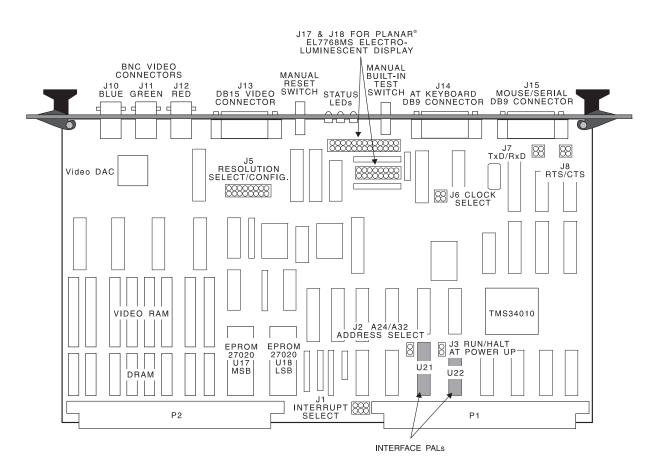

The RG-750 graphics board contains several jumper options, connectors and status LEDs, as shown in Figure 2.1. Connectors are provided for interfacing the RG-750 to a video monitor (J10, J11, J12 and J13), Planar® electroluminescent display (J17 and J18), keyboard (J14), and serial device (J15).

Figure 2.1 RG-750 Board Layout

## 2.3 Jumper Options

The following jumper options, as shown in Figure 2.2, are available on the RG-750. Figure 2.1 indicates the jumper locations. Use shorting clips or wirewrap wire to select the jumper options.

| JUMPER | DESCRIPTION                     |  |

|--------|---------------------------------|--|

| J1     | Interrupt Request Select        |  |

| J2     | A24/A32 Address Select          |  |

| J3     | Run/Halt at Power-up            |  |

| J5     | Resolution Select/Configuration |  |

| J6     | Clock Select                    |  |

| J7     | RS-232 TxD/RxD Swap             |  |

| J8     | RS-232 CTS/RTS Swap             |  |

| J19    | Testable Strap                  |  |

Figure 2.2 Jumper Summary

## 2.3.1 J1 Interrupt Request Select

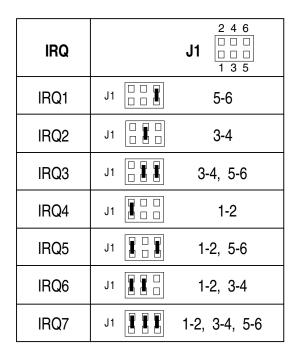

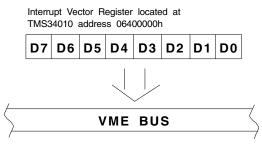

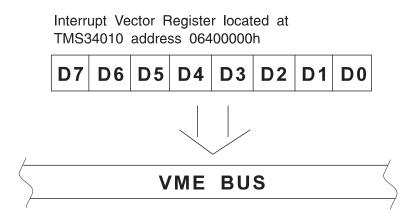

The RG-750 generates an interrupt to the host and outputs an 8 bit interrupt vector in response to an interrupt acknowledge, as shown in Figure 2.4. The interrupt can be routed to any of the 7 VMEbus interrupt lines, IRQ1-IRQ7, by installing jumpers in J1 as shown below in Figure 2.3.

Figure 2.3 IRQ Select

## 2.3.2 J2 A24/A32 Address Select

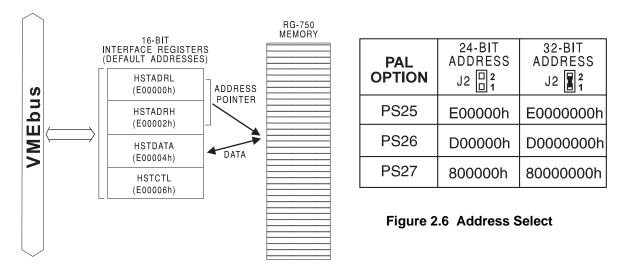

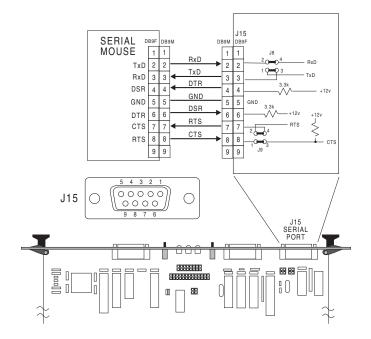

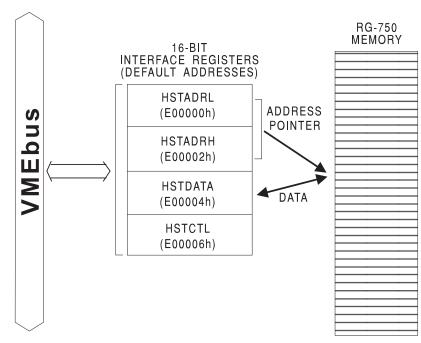

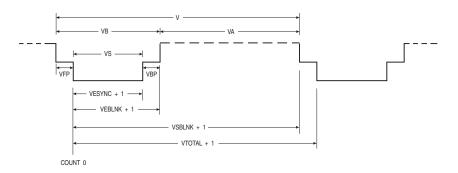

The VMEbus interfaces to the RG-750 via four 16-bit Host Interface Registers located in a 256-byte page in VMEbus memory space (see Figure 2.5). All data transfers between the VMEbus and the RG-750 are via these registers. The four 16-bit Host Interface Registers can be located in 24-bit or 32-bit VMEbus address space by configuring jumper J2 (see Figure 2.6). With a jumper installed in J2, a 32-bit address is selected. With no jumper installed in J2, a 24-bit address is selected.

The base addresses are determined by the Interface Register PALs U21 and U22, and can be changed by programing a new PAL set (see Appendix A for PAL equations) or by ordering a custom Interface PAL set from Rastergraf, Inc.

Figure 2.5 VMEbus Interface

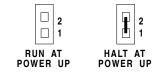

## 2.3.3 J3 Run/Halt at Power-up

The RG-750 can be jumpered at J3 to come up running (no jumper at J3) or halted (jumper installed in J3) at power-up. For normal operation, the RG-750 should be jumpered to come up running.

Figure 2.7 Run/Halt at Power-Up Jumper

## 2.3.4 J5 Resolution Select/Configuration

Jumper J5:1-2, 3-4, 5-6, and 7-8 are used to select the graphics board resolution (see Figure 2.8). The remaining jumpers of J5 are used for other options as shown in Figures 2.9 and 2.10.

| RESOLUTION                  | <b>J5</b> $(2 4 6 8 0 12 14 16)$<br>(1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |

|-----------------------------|------------------------------------------------------------------------------|

| 640h x 480v x 4             | J5 00000000                                                                  |

| 640h x 480v x 8             | J5 <b>1</b> 0000000                                                          |

| 800h x 600v x 4             | J5                                                                           |

| 800h x 600v x 8             | J5                                                                           |

| 1024h x 768v x 4            | J5                                                                           |

| 1024h x 768v x 8            | J5                                                                           |

|                             | J5                                                                           |

|                             | J5                                                                           |

| EL7768MS<br>640h x 480v x 4 | J5                                                                           |

|                             | J5 J 5                                                                       |

|                             | J5 L B B B L L L L                                                           |

|                             | J5 <b>1 1 1 1 1 1 1 1 1 1</b>                                                |

## Figure 2.8 Resolution Jumper Select

| FUNCTION |          | <b>J5</b><br><b>1</b> 3 5 7 9 11 13 15 |

|----------|----------|----------------------------------------|

| SYNC ON  | ENABLED  | J5                                     |

| GREEN    | DISABLED | J5                                     |

| H SYNC   | NEGATIVE | J5                                     |

| POLARITY | POSITIVE | J5                                     |

| V SYNC   | NEGATIVE | J5                                     |

| POLARITY | POSITIVE | J5                                     |

Figure 2.9 Function Select

|                | <b>J5</b> 2 4 6 8 10 12 14 16<br>1 3 5 7 9 11 13 15 |

|----------------|-----------------------------------------------------|

| DEBUG DISABLED | J5                                                  |

| DEBUG ENABLED  | J5                                                  |

## Figure 2.10 Debug Enable

## 2.3.5 J6 Clock Select

This jumper is used to select the clock for the TMS34010 graphics processor (see Figure 2.11).

| TMS34010<br>CLOCK | 2 4<br>J6 □ □<br>1 3 |

|-------------------|----------------------|

| not used          | J6                   |

| 40.00 MHz         | J6 📕 1-2             |

| not used          | J6 🗌 🖁 3-4           |

| not used          | J6 📕 1-2, 3-4        |

Figure 2.11 Clock Select Jumper

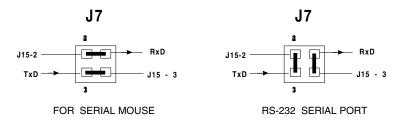

## 2.3.6 J7 RS-232 Transmit/Receive (TxD/RxD)

RS-232 transmit (TxD) and receive data (RxD) can be swapped by installing a jumper in J7, as shown in Figure 2.12.

Figure 2.12 RS-232 TxD and RxD Data Lines

## 2.3.7 J8 RS-232 Handshake (RTS/CTS)

Two RS-232 handshake signals, RTS and CTS can be swapped by installing jumpers in J8 as shown in Figure 2.13.

Figure 2.13 RS-232 RTS and CTS Handshake Lines

## 2.3.8 J19 Testable Strap

This jumper provides two testable bits that may be sampled to provide configuration information. The state of the bits in the status register reflect the configuration of J19. If a jumper is installed between pins one and two, bit D10 of the status register will be read as a zero, otherwise it will be a one. If a jumper is installed between pins three and four, bit D11 of the status register will be read as a zero, otherwise it will be read as a zero, otherwise it will be read as a zero, otherwise it will be read as a zero.

In AFGIS firmware versions 3.11a and later, J19 1-2 is used to enable or disable the power-up display as shown in Figure 2.14. In AFGIS firmware versions 3.11 and below, J19 1-2 is not used.

| TESTABLE<br>STRAP            | 2 4<br>J19 □ □<br>1 3 |

|------------------------------|-----------------------|

| Power-up<br>Display enabled  | J19                   |

| Power-up<br>Display disabled | J19                   |

Figure 2.14 Testable Strap Jumper

## 2.4 LEDs

Three LEDs on the RG-750 provide status information (see Figure 2.1).

## Red LED:

The red LED lights when an error is detected. The red LED can be user programmed with the LED opcode.

## Yellow LED:

The yellow LED lights when the board is accessed by the VMEbus.

## Green LED:

The green LED blinks when the TMS34010 is in the idle loop. The green LED can be user programmed with the LED opcode.

## 2.5 Connectors

The RG-750 board has connectors for VMEbus, VGA/SVGA video monitor, an AT keyboard, a serial port, and a Planar EL7768MS EL Flat Panel display (see Figures 2.17 and 2.18). Connector signals and cabling requirements are described in the following pages.

| REFERENCE<br>NUMBER | DESCRIPTION                                                                | CONNECTOR<br>TYPE |

|---------------------|----------------------------------------------------------------------------|-------------------|

| P1                  | VMEbus connector                                                           | 96-pin            |

| P2                  | VMEbus connector                                                           | 96-pin            |

| J10                 | Video Connector - Blue [optional]                                          | BNC               |

| J11                 | BNC                                                                        |                   |

| J12                 | BNC                                                                        |                   |

| J13                 | Video Connector                                                            | DB15              |

| J14                 | AT Keyboard Connector                                                      | DIN-5F            |

| J16                 | Serial Port Connector                                                      | DB9M              |

| J17                 | J17 Video Connector for Planar® EL7768MS<br>Electroluminescent VGA Display |                   |

| J18                 | Video Connector for Planar® EL7768MS<br>Series Electroluminescent Display  | 2x8 pin header    |

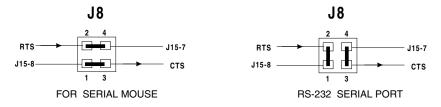

## 2.5.1 DB15 Video Output Connector and 2.5.2 BNC Video Connectors

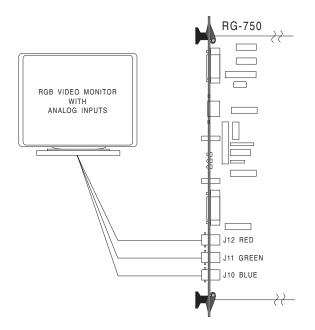

A VGA or SVGA video monitor can be connected to the RG-750 DB15F connector J13 (see Figure 2.15) or to BNC connectors J12 (red), J11 (green), and J10 (blue), as shown in Figure 2.16.

Figure 2.15 DB15 Connection To Video Monitor

Figure 2.16 BNC Connection To Video Monitor

## 2.5.3 Planar@ EL7768MS Electroluminescent VGA Display Connector

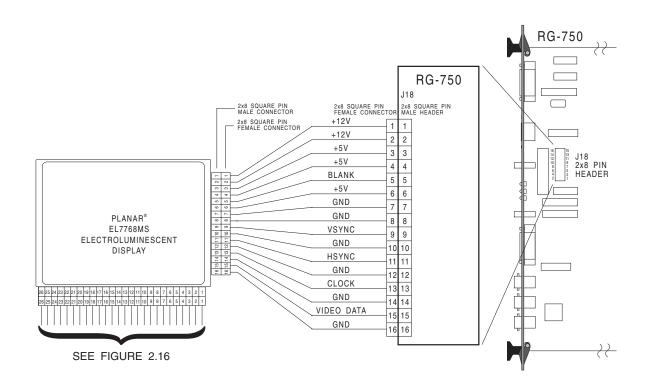

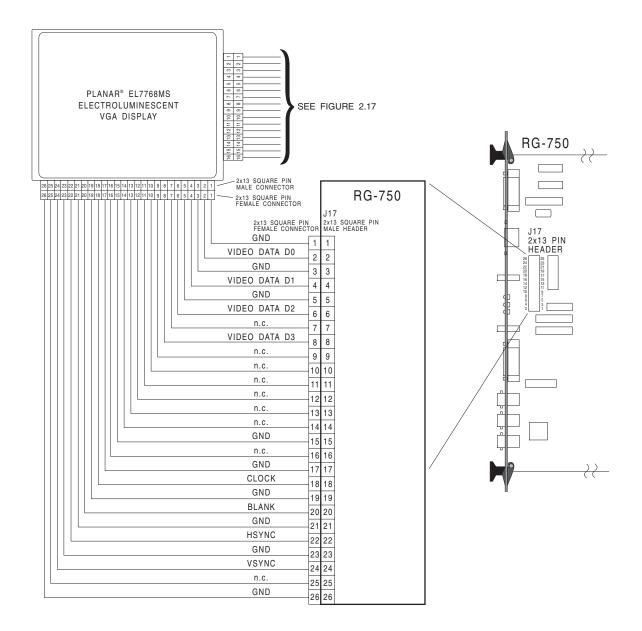

A Planar EL7768MS electroluminescent flat panel display can be connected to the RG-750 with two flat ribbon cables as shown in Figures 2.17 and 2.18.

Figure 2.17 16 Pin Connection To Planar EI7768MS Display

Figure 2.18 26 Pin Connection To Planar EI7768MS Display

## 2.5 Connectors (continued)

## 2.5.4 AT Keyboard Connector

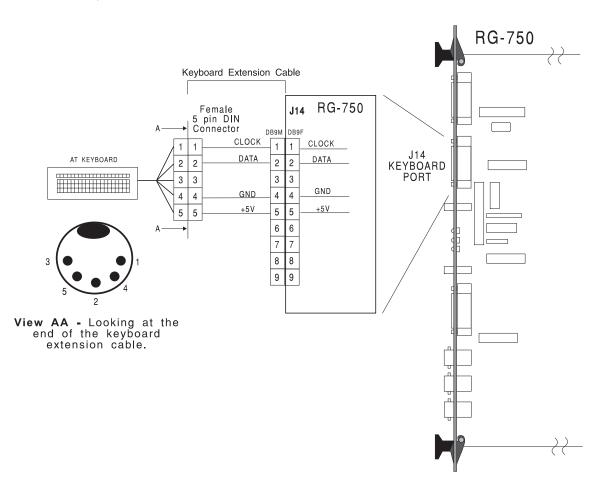

Connector J14 provides an interface to a standard AT keyboard (see Figure 2.19). The RG-750 keyboard firmware works with an AT style keyboard - it does not operate with PC or XT keyboards, which have a different interface.

Figure 2.19 AT Keyboard Connection To J14

## 2.5 Connectors (continued)

## 2.5.5 RS-232 Serial Connector

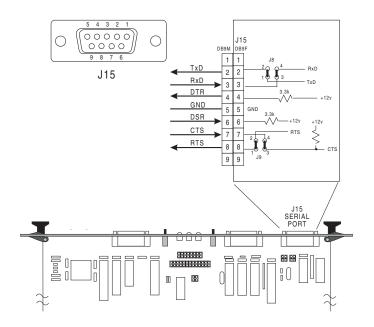

RS-232 connector J15 can be configured for serial data transfer or for use with a serial mouse by configuring the jumpers at J7 & J8, as shown in Figures 2.20 & 2.21.

Figure 2.20 RS-232 Serial Data Configuration

Figure 2.21 Serial Mouse Configuration

## 2.5 Connectors (continued)

## 2.5.6 VMEbus Pin Assignments

Figure 2.22 shows the VMEbus P1 and P2 connector pin assignments used by the RG-750 Graphics board.

|       | P1       |         |       |       | F     | 2     |       |

|-------|----------|---------|-------|-------|-------|-------|-------|

| PIN # | ROW A    | ROW B   | ROW C | PIN # | ROW A | ROW B | ROW C |

| 1     | D0       | D8      | 1     |       |       |       |       |

| 2     | D1       | D9      | 2     |       |       |       |       |

| 3     | D2       | BG0IN*  | D10   | 3     |       |       |       |

| 4     | D4       | BG0OUT* | D11   | 4     | A24   |       |       |

| 5     | D4       | BG1IN*  | D12   | 5     | A25   |       |       |

| 6     | D5       | BG1OUT* | D13   | 6     | A26   |       |       |

| 7     | D6       | BG2IN*  | D14   | 7     | A27   |       |       |

| 8     | D7       | BG2OUT* | D15   | 8     | A28   |       |       |

| 9     | BG3IN*   | 9       | A29   |       |       |       |       |

| 10    | BG3OUT*  | 10      | A30   |       |       |       |       |

| 11    | 11       | A31     |       |       |       |       |       |

| 12    | DS1*     | 12      |       |       |       |       |       |

| 13    | DS0*     | LWORD*  | 13    |       |       |       |       |

| 14    | WRITE*   | AM5     | 14    | D16   |       |       |       |

| 15    | A23      | 15      | D17   |       |       |       |       |

| 16    | DTACK*   | AM0     | A22   | 16    | D18   |       |       |

| 17    | AM1      | A21     | 17    | D19   |       |       |       |

| 18    | AS*      | AM2     | A20   | 18    | D20   |       |       |

| 19    | AM3      | A19     | 19    | D21   |       |       |       |

| 20    | IACK*    | A18     | 20    | D22   |       |       |       |

| 21    | IACKIN*  | A17     | 21    | D23   |       |       |       |

| 22    | IACKOUT* | A16     | 22    |       |       |       |       |

| 23    | AM4      | A15     | 23    | D24   |       |       |       |

| 24    | A7       | IRQ7*   | A14   | 24    | D25   |       |       |

| 25    | A6       | IRQ6*   | A13   | 25    | D26   |       |       |

| 26    | A5       | IRQ5*   | A12   | 26    | D27   |       |       |

| 27    | A4       | IRQ4*   | A11   | 27    | D28   |       |       |

| 28    | A3       | IRQ3*   | A10   | 28    | D29   |       |       |

| 29    | A2       | IRQ2*   | A9    | 29    | D30   |       |       |

| 30    | A1       | IRQ1*   | A8    | 30    | D31   |       |       |

| 31    | -12 VDC  | +12 VDC | 31    |       |       |       |       |

| 32    | +5 VDC   | 32      |       |       |       |       |       |

Figure 2.22 VMEbus Connectors P1 & P2 Pin Assignments

# 3.0 OPERATION

## **Chapter Contents:**

- 3.1 Power Up Display

- 3.2 Operation Overview

- 3.3 RG-750 Host Interface Registers

- 3.3.1 Data Transfer Convention

- 3.3.2 Transferring Data

- 3.4 RG-750 Memory

- 3.4.1 RG-750 Memory Map

- 3.4.2 EPROM

- 3.4.3 DRAM

- 3.4.4 Fixed RAM

- 3.4.5 VRAM

- 3.4.6 RS-232 Interface

- 3.4.7 Programming the 2691 UART

- 3.4.8 Keyboard Interface

- 3.4.9 Video DAC

- 3.4.10 Control Register

- 3.4.11 Remapping DRAM

- 3.4.12 Status Register

- 3.5 Interrupts

- 3.6 Interrupts to the RG-750 from the VMEbus

- 3.6.1 Host Interrupts

- 3.6.2 Resetting the RG-750 with NMI Interrupt

- 3.7 Interrupts to the VMEbus from the RG-750

- 3.8 Coordinate System

## 3.0 Overview of RG-750 Operation

## 3.1 Power Up Display

The RG-750 creates a display at power up, indicating the resolution of the current display mode. The display resolution is programmable, and can be changed with the CONFIG opcode. The parameter following the CONFIG opcode changes the resolution as follows:

0000 = 640h x 480v x 4 0001 = 640h x 480v x 8 0002 = 800h x 600v x 4 0003 = 800h x 600v x 8 0004 = 1024h x 768v x 4 0005 = 1024h x 768v x 8

The default resolution is 640h x 480v x 4.

#### 3.2 Operation Overview

When programing the RG-750 using an RGI driver and AFGIS C graphics library, the details of loading and executing instructions are transparent to the user, as the driver interfaces to both the operating system and the RG-750. The user merely calls the specified C graphics functions from the AFGIS C graphics library, and the resulting code is passed to the driver, which interfaces appropriately with the RG-750.

However, the RG-750 can be programed directly with AFGIS opcodes. AFGIS opcodes are 16 bit instructions which may have 16 bit parameters, similar to most assembly languages. AFGIS opcodes are executed by the on-board firmware after they have been loaded into RG-750 memory. The default location for loading AFGIS opcodes is 03100000h. Execution of these opcodes begins when the host issues a HINT0 interrupt to the RG-750. The list of AFGIS opcodes (display list) must end with the EODL opcode, which causes display execution to cease when the EODL opcode is processed. When the EODL instruction has been executed by the RG-750, AFGIS firmware will issue an interrupt to the VMEbus or set the EODLFLAG, indicating to the host that display execution has been completed.

HINTO causes execution to begin at the address in Fixed RAM location HINTO\_AFG\_ENTRY. The default value in HINTO\_AFG\_ENTRY is 03100000h, but can be changed by the host to any valid TMS34010 address, and display execution will begin at the specified address in response to HINTO. HINTO\_AFG\_ENTRY is located in Fixed RAM at 030000C0h.

See the AFGIS Instruction Set Manual for more information.

## 3.3 RG-750 Host Interface Registers

The VMEbus interfaces to the RG-750 via four 16-bit Host Interface Registers located in a 256-byte page in VMEbus address space. All data transfers between the VMEbus and the RG-750 are via these registers, and data must be transferred 16 bits at a time. The four

16-bit Host Interface Registers can be located at one of two base addresses by configuring jumper J2. The two base addresses are determined by the Interface Register PALs U21 and U22, and can be changed by programing new PALs (see Appendix A for

PAL equations) or by ordering a custom Interface PAL set from Rastergraf, Inc.

## Figure 3.1 Host Interface Registers

## 3.3.1 Data Transfer Conventions

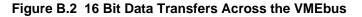

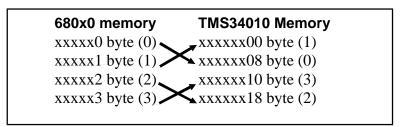

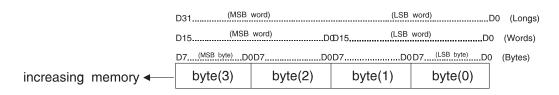

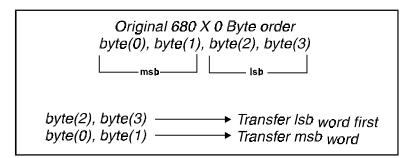

The RG-750 supports little endian format. Words, 16 bit values, can be transferred from VMEbus memory to RG-750 memory across the VMEbus without modification. Bytes (8 bit values) must be byte swapped and longs (32 bits values) must be word swapped before transfer. See Appendix B for more information.

## 3.3.2 Transferring Data

Data is transmitted to or from the RG-750 by specifying the TMS34010 32-bit memory address in HSTADRL and HSTADRH, and then by writing or reading a 16-bit data word to or from the HSTDATA register. The TMS34010 moves the data from RG-750 memory to the HSTDATA register for a read operation, or from the HSTDATA register to the specified memory location on the RG-750 graphics board for a write operation. The TMS34010 is a bit-addressable machine. AFGIS opcodes must be loaded on word boundaries (the four lsbs of the address loaded into HSTADRL must be zero). Bits in the HSTCTL register can be set to cause the address value in HSTADRL/H to increment automatically on reads or writes, to pass interrupts to the RG-750, and to control the TMS34010 graphics processor. See the TMS34010 User's Guide available from Texas Instruments for a complete description of the TMS34010 host interface.

#### HSTADRL

| A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 | A0 |

|----------------------------------------------------|----|

|----------------------------------------------------|----|

#### HSTADRH

| A31 | A30 | A29 | A28 | A27 | A26 | A25 | A24 | A23 | A22 | A21 | A20 | A19 | A18 | A17 | A16 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

## HSTDATA

| D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 | 6 D5 D4 D3 D2 D1 D0 |

|-------------------------------------|---------------------|

|-------------------------------------|---------------------|

#### HSTCTL

| BIT | NAME   | DESCRIPTION                                    |

|-----|--------|------------------------------------------------|

| 15  | HLT    | Halts TMS34010 processing                      |

| 14  | CF     | Flushes the cache                              |

| 13  | LBL    | Lower byte last                                |

| 12  | INCR   | Increments address after each read             |

| 11  | INCW   | Increments address after each write            |

| 10  |        | reserved                                       |

| 9   | NMIM   | Selects the mode for the nonmaskable interrupt |

| 8   | NMI    | Enables the nonmaskable interrupt              |

| 7   | INTOUT | Sends output interrupt from TMS34010 to host   |

| 4-6 | MSGOUT | Buffers an output message code                 |

| 3   | INTIN  | Sets input interrupt from host to TMS34010     |

| 0-2 | MSGIN  | Buffers an input message code                  |

Figure 3.2 Host Interface Registers Bit Assignments

## 3.4 RG-750 Memory

## 3.4.1 RG-750 Memory Map

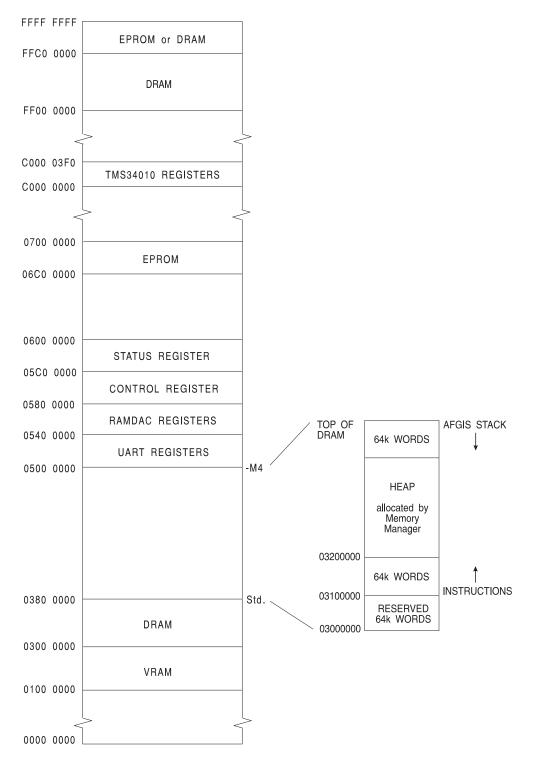

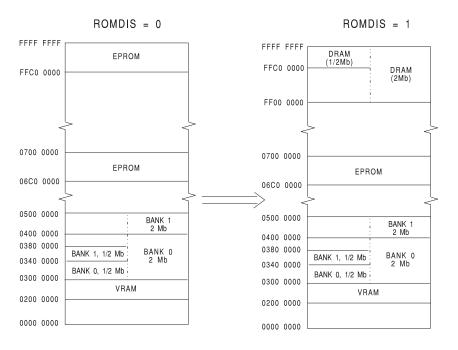

Memory on the RG-750 board includes EPROM, DRAM, video RAM, and memory-mapped registers, as shown in Figure 3.3.

Figure 3.3 RG-750 Memory Map

## 3.4.2 EPROM

AFGIS firmware resides in two 27020 EPROMs on the RG-750 graphics board. U17 is the msb EPROM, which contains data bits D8 through D15. U18 is the lsb EPROM, which contains data bits D0 through D7.

## 3.4.3 DRAM

The RG-750 can be configured with 1 or 4 Mbytes of DRAM. DRAM is used by AFGIS firmware for instruction storage, for temporary storage of screen data, and for downloaded code. The first 64k words of DRAM are reserved for use by AFGIS firmware. The rest of DRAM, starting at 03100000h, is available for user code, and is managed by the AFGIS memory manager.

The AFGIS memory manager returns an address to the start of a block of DRAM requested by the user with the R\_ALLOC opcode. Memory is allocated starting at the beginning of available DRAM (03100000h).

The default location for downloading and executing AFGIS opcodes is also 03100000h. DRAM at this address and above (AFGIS heap) is controlled by the AFGIS memory manager and will be allocated to the first request for memory with the R\_ALLOC opcode. To avoid memory usage conflict, a block of memory should be requested from the AFGIS memory manager for AFGIS opcode processing (If the R\_ALLOC opcode is never used to allocate memory for any other purpose, AFGIS opcodes can be safely run at 03100000h without allocating memory for opcode processing).

## 3.4.4 Fixed DRAM Interface

The first 24 words of DRAM, starting at 03000000h are designated as Fixed RAM and contain flags, addresses, and parameters for access by the VMEbus host. Fixed RAM values are either 16 or 32 bits long, and may have restricted access. R means the location may be read by the host, but it may not be modified. R/W means that the location may be read from or written to by the host. Fixed RAM is organized as shown on the next page. See the *AFGIS Instruction Set Manual* for additional information.

| ADDRESS   | NAME            | SIZE | ACCESS | DESCRIPTION                                                                                               |

|-----------|-----------------|------|--------|-----------------------------------------------------------------------------------------------------------|

| 03000000h | EODLFLAG        | 16   | R/W    | = 0 when the RG-750 is busy.<br>= 1 when the RG-750 is not busy.                                          |

| 03000010h | KBDFLAG         | 16   | R/W    | <ul><li>= 0 when there is no keyboard data.</li><li>= 1 when keyboard data is available</li></ul>         |

| 03000020h | MSEFLAG         | 16   | R/W    | <ul><li>= 0 when there is no mouse/serial data.</li><li>= 1 when mouse/serial data is available</li></ul> |

| 03000030h | ERRFLAG         | 16   | R/W    | <ul><li>= 0 when no errors have been detected.</li><li>= 1 when an error has been detected.</li></ul>     |

| 03000040h | IDLEFLAG        | 16   | R/W    | Set to 1 on each pass of idle loop, approx.<br>every 10 usec. Not cleared by AFGIS firmware.              |

| 03000050h | DI_COUNT        | 16   | R      | 60hz continuous counter, updated by AFGIS.                                                                |

| 03000060h | INTOUTMASK      | 16   | R/W    | RG-750 to host interrupt enable mask.                                                                     |

| 03000070h | HOST_FIELD0     | 16   | R/W    | Reserved for host use.                                                                                    |

| 03000080h | HOST_FIELD1     | 32   | R/W    | Reserved for host use.                                                                                    |

| 030000A0h | ENV_PTR         | 32   | R/W    | Address of current graphics environment.                                                                  |

| 030000C0h | HINT0_AFG_ENTRY | 32   | R/W    | AFGIS display list address. Used by HINT0                                                                 |

| 030000E0h | HINT1_TMS_ENTRY | 32   | R/W    | TMS assembly code address. Used by HINT1                                                                  |

| 03000100h | GPTABLE_PTR     | 32   | R      | Address of global pointer table.                                                                          |

| 03000120h | DEFAULT_ENV_PTR | 32   | R      | Address of default environment.                                                                           |

| 03000140h | DPAGEADDR       | 32   | R      | Current display page address.                                                                             |

#### Figure 3.4 Fixed RAM Parameters

## 3.4.5 VRAM

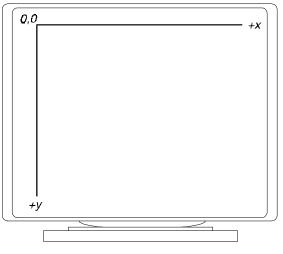

Video RAM, VRAM, holds the image displayed on the video screen. VRAM is normally written to by the TMS34010 graphics processor on the RG-750 as a consequence of AFGIS opcode processing. However, image data can also be downloaded directly into VRAM by the VMEbus host. The beginning of VRAM, 0200 0000h, corresponds to the top left corner of the video screen.

VRAM is organized as a 1K x 1K buffer for 8 bits/pixel configurations, and as a 1K x 2K buffer for 4 bits/pixel configurations.

#### RG-750 Memory (continued)

## 3.4.6 RS-232 Serial Interface

The RS-232 Serial Interface can be used for a serial mouse (with Microsoft format) or it can be used to connect a serial device to the RG-750. The handshake lines (RTS, DTR, etc.) can be reversed at J7 and J8 to allow use of a flat cable connected to a DB9 connector. The serial interface uses the Signetics 2691 UART, which is a programmable device with many options. The bit assignments for the 2691 registers are shown below.

## 3.4.7 Programing the 2691 UART

The 2691 Universal Asynchronous Receiver/Transmitter (UART) has quadruple buffered receiver data registers and a fully programmable data format. The baud rate for the receiver and transmitter can be selected from 9 fixed rates. The UART contains eight registers that determine its mode of operation (see Figure 3.5 and Figure 3.6). Refer to the Signetics 2691 UART data sheet for additional information

| ADDRESS   | DESCRIPTION                      | DEFAULT CONTENTS |

|-----------|----------------------------------|------------------|

| 05000000h | MR1 - Mode Register 1            | 13h              |

| 05000000h | MR2 - Mode Register 2            | 17h              |

| 05000010h | CSR - Channel Status Register    | 0BBh             |

| 05000020h | CR - Command Register            | 0A5h             |

| 05000040h | ACR - Auxillary Control Register | 78h              |

| 05000050h | IMR - Interrupt Mask Register    | 04h              |

| 05000060h | CTUR - Counter Register High     | 00h              |

## Figure 3.5 2691 UART Power Up Register Values

The 2691 UART is configured by the AFGIS firmware at power up as follows:

- 9600 baud

- 8bits/character

- 1 stop bit

- $\cdot$  no parity

- Transmit Data line controlled by CTS handshake

- RTS asserted. RTS is deasserted when the receive buffer becomes full.

- DTR always asserted

- DSR always asserted

Use the SERUART opcode to reprogram the 2691.

## 3.4 RG-750 Memory (continued)

|      | BIT 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BIT 6                                          | BIT 5             | BIT 4             | BIT 3                                            | BIT 2                                                                   | BIT 1                                            | BIT 0                                            |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------|-------------------|--------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--|

| MR1  | RxRTS<br>CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RxINT<br>SELECT                                | ERROR<br>MODE     | PARITY MC         |                                                  | PARITY BITS PER CHAR<br>TYPE                                            |                                                  |                                                  |  |

|      | 0 = no<br>1 = yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0=RXRDY<br>1 = FULL                            |                   |                   | 0 = even<br>1 = odd                              |                                                                         |                                                  |                                                  |  |

| MR2  | CHANNEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MODE                                           | Tx RTS<br>CONTROL | Tx CTS<br>ENABLE  | STOP BIT I                                       | ENGTH                                                                   |                                                  |                                                  |  |

|      | 00 = norma<br>01 = auto e<br>10 = local | cho<br>oop                                     | 0 = no<br>1 = yes | 0 = no<br>1 = yes | 0 = 0.563<br>1 = 0.625<br>2 = 0.688<br>3 = 0.750 | 4 = 0.183  5 = 0.875  6 = 0.938  7 = 1.000                              | 8 = 1.563<br>9 = 1.625<br>A = 1.688<br>B = 1.750 | C = 1.813<br>D = 1.875<br>E = 1.938<br>F = 2.000 |  |

| CSR  | ACR(7) = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CLOCK SEL<br>): 50 - 38.4k  <br>: 75 - 19.2k b | baud              |                   | ACR (7) = 0                                      | MITTER CLOCK SELECT<br>) = 0: 50 - 38.4k baud<br>) = 0: 50 - 38.4k baud |                                                  |                                                  |  |

| CR   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | NEOUS CON                                      |                   |                   | DISABLE<br>Tx                                    | ENABLE<br>Tx                                                            | DISABLE<br>Rx                                    | ENABLE<br>Rx                                     |  |

|      | see UART o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | data sheet                                     |                   |                   | 0 = no<br>1 = yes                                | 0 = no<br>1 = yes                                                       | 0 = no<br>1 = yes                                | 0 = no<br>1 = yes                                |  |

| ACR  | BRG SET<br>SELECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | COUNTER                                        | MODE & SO         | URCE              | POWER<br>DOWN<br>MODE                            | MPO FUNC                                                                | TION SELE                                        |                                                  |  |

|      | 0 = set1<br>1 = set2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | see UART o                                     | data sheet        |                   | 0 = on<br>1 = off                                | see UART                                                                | data sheet                                       |                                                  |  |

| ISR  | MPI PIN<br>CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MPI PIN<br>STATE                               |                   | COUNTER<br>READY  | DELTA<br>BREAK                                   | RxRDY/<br>FULL                                                          | TxEMT                                            | TxRDY                                            |  |

|      | 0 = no<br>1 = yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0 = low<br>1 = high                            | not<br>used       | 0 = no<br>1 = yes | 0 = no<br>1 = yes                                | 0 = no<br>1 = yes                                                       | 0 = no<br>1 = yes                                | 0 = no<br>1 = yes                                |  |

| CTUR | 8 MSBs OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | COUNTER/                                       | TIMER VALU        | JE                |                                                  |                                                                         |                                                  |                                                  |  |

| CTLR | 8 LSBs OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | COUNTER/T                                      | IMER VALU         | E                 |                                                  |                                                                         |                                                  |                                                  |  |

## Figure 3.6: 2691 UART Register Contents

## 3.4.8 Keyboard Interface

An AT style keyboard can be connected to the RG-750 at J14. AFGIS firmware decodes the keyboard scan codes, stores the ASCII codes in RAM, and informs the VMEbus host of available keyboard data via an interrupt or a polling register in fixed RAM.

## 3.4 RG-750 Memory (continued)

## 3.4.9 Video DAC (Bt478)

RS-343 video is generated by the RG-750 with a Bt478 type Video DAC. The Video DAC has a 256 x 24 color look up table, allowing a user to select 256 colors from a palette of 16 million. The Video DAC registers are located as shown below:

| ADDRESS   | DESCRIPTION            |

|-----------|------------------------|

| 05400000h | Write Address Register |

| 05410000h | Data Register          |

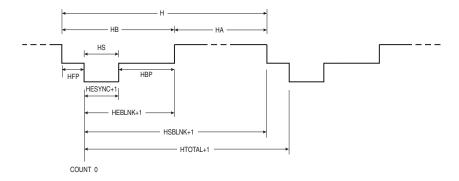

## 3.4.10 Control Register