# VMEBOOK

# Table of Contents

#### Introduction How to Use This Book Section 1. The VICO068A VMEbus Interface Controller Introduction to the VIC068A Chapter 1.1 1.1.1 Description 1.1.2 Features Summary VIC068A Signal Descriptions Chapter 1.2 1.2.1 VMEbus Signals 1.2.2 Local Signals 1.2.3 Buffer Control Signals Chapter 1.3 Overview of the VIC068A 1.3.1 Resetting the VIC068A 1.3.2 The VIC068A VMEbus System Controller 1.3.3 VIC068A VMEbus Master Cycles 1.3.3.1 Master Write-Posting 1.3.3.2 Indivisible Cycles 1.3.3.3 Deadlock 1.3.3.4 Self-Access 1.3.4 VIC068A VMEbus Slave Cycles 1.3.4.1 Slave Write-Posting 1.3.5 Address Modifier (AM) Codes 1.3.6 VIC068A VMEbus Block Transfers 1.3.6.1 MOVEM Master Block Transfers 1.3.6.2 Master Block Transfers with Local DMA 1.3.6.3 Slave Block Transfers 1.3.7 VIC068A Interrupt Generation and Handling Facilities 1.3.8 Interprocessor Communication Facilities Chapter 1.4 System Controller Operations 1.4.1 VMEbus Arbitration 1.4.2 The VMEbus Arbitration Timeout Timer 1.4.3 The VMEbus Transfer Timeout Timer 1.4.4 The BGi Daisy-Chain Driver 1.4.5 The IACK\* Daisy-Chain Driver

| Chapter 1.5 | VIC068A VMEbus Master Operations                    |

|-------------|-----------------------------------------------------|

|             | 1.5.1 VMEbus Requests                               |

|             | 1.5.2 Release Modes                                 |

|             | 1.5.2.1 Release On Request (ROR)                    |

|             | 1.5.2.2 Release When Done (RWD)                     |

|             | 1.5.2.3 Release On Clear (ROC)                      |

|             | 1.5.2.4 VMEbus Capture and Hold (BCAP)              |

|             | 1.5.2.5 Release Under RMC* Control                  |

|             | 1.5.3 VIC068A VMEbus Master Write Cycle             |

|             | 1.5.4 VIC068A VMEbus Master Read Cycle              |

|             | 1.5.5 Master Write Posting                          |

|             | 1.5.6 Indivisible Cycles                            |

|             | 1.5.6.1 Indivisible Single-Address Cycles (ISACs)   |

|             | 1.5.6.2 Indivisible Multiple-Address Cycles (IMACs) |

|             | 1.5.7 Deadlock                                      |

|             | 1.5.7.1 Undetectable Deadlocks                      |

|             | 1.5.8 Self-Access                                   |

|             | 1.5.9 VMEbus/Local Bus Data and Port Size           |

|             | 1.5.10 Fair Request Timeout                         |

|             | 1.5.11 Address-Only Cycles                          |

|             | 1.5.12 The Address Modifiers for Master Cycles      |

| Chapter 1.6 | VIC068A VMEbus Slave Operations                     |

|             | 1.6.1 The Valid Slave Select                        |

|             | 1.6.2 The Local Bus Request                         |

|             | 1.6.3 The Local Bus Grant                           |

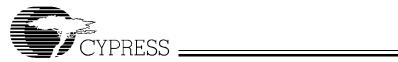

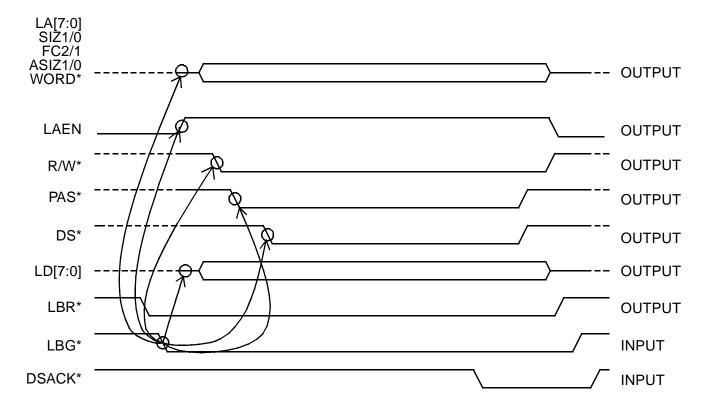

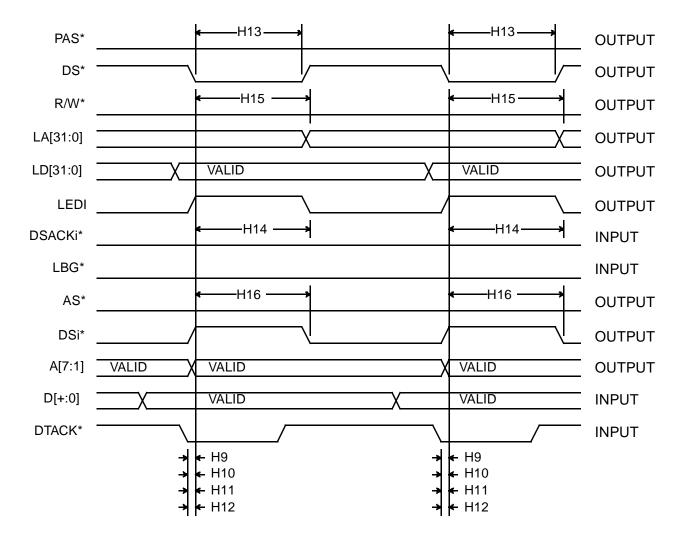

|             | 1.6.4 Local Bus Timing                              |

|             | 1.6.5 VMEbus/Local Bus Data and Port Size           |

|             | 1.6.6 The Latched Bus Interface                     |

|             | 1.6.7 Slave Write Posting                           |

|             | 1.6.8 Slave Acknowledge Timing (SAT)                |

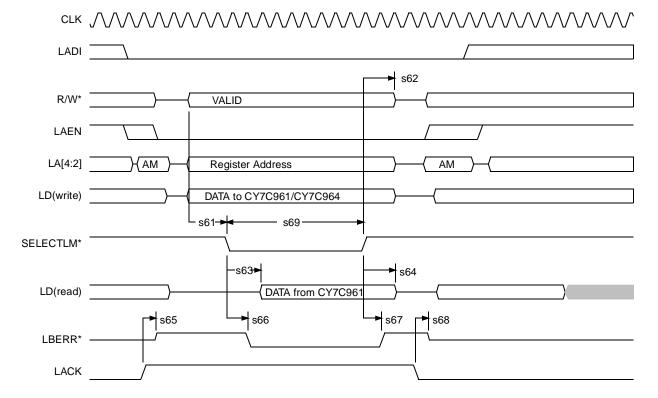

| Chapter 1.7 | VIC068A Control Register Access                     |

|             | 1.7.1 Control Registers                             |

|             | 1.7.2 Control Register Access                       |

| Chapter 1.8 | Interprocessor Communication Facilities             |

|             | 1.8.1 Valid ICF Selection                           |

|             | 1.8.2 Interprocessor Communication Registers        |

|             | 1.8.3 Interprocessor Communication Global Switches  |

|             | 1.8.4 Interprocessor Communication Module Switches  |

| Chapter 1.9 | Interrupts                                          |

|             | 1.9.1 VMEbus Interrupter                            |

|             | 1.9.2 The VIC068A VMEbus Interrupt Handler          |

|             | 1.9.3 Local Interrupt Handler                       |

|             | 1.9.4 The FCIACK Cycle                              |

|             | 1.9.5 The Error/Status Interrupts                   |

|             | 1.9.6 Interrupt Priority Order                      |

- 1.9.7 Clock-Tick Interrupt Generator

- 1.9.8 Interrupt Control Registers

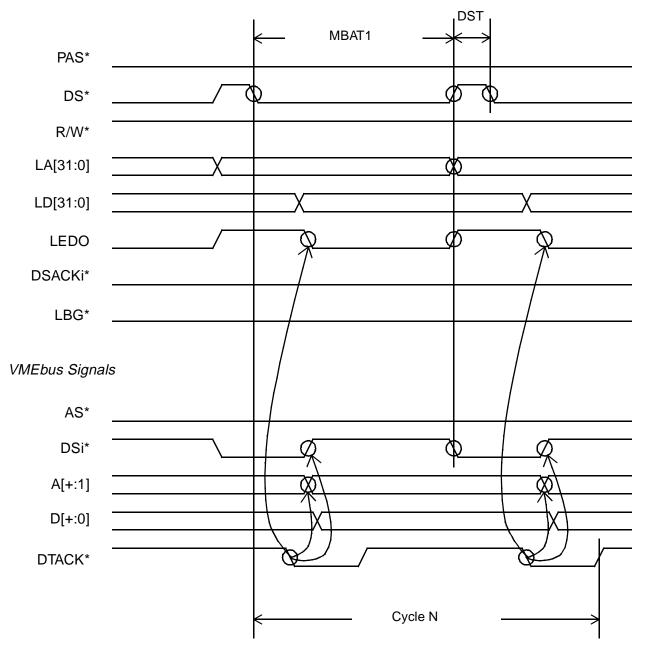

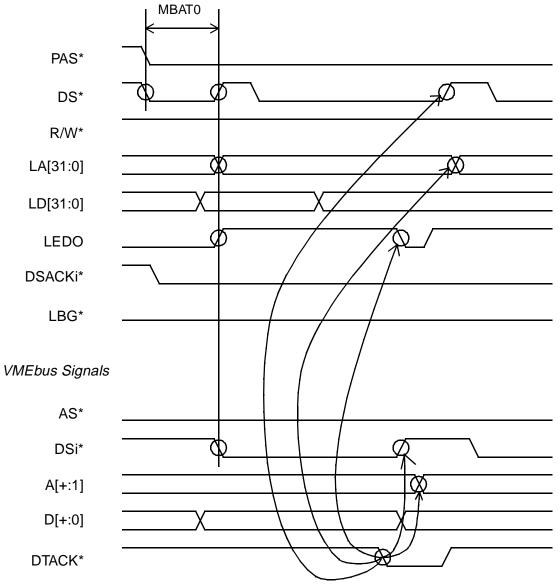

- <u>Chapter 1.10</u> VIC068A Block Transfer Functions

- 1.10.1 VIC068A Master Block Transfer

- 1.10.1.1 Block Transfers with Local DMA

- 1.10.1.2 MOVEM Block Transfers

- 1.10.1.3 Buffer Control Signals During Master Block Transfers

- 1.10.1.4 Performing Block Transfers to VMEbus Slaves Not Supporting Block Transfers

- 1.10.2 VIC068A Slave Block Transfers

- 1.10.3 Buffer Control Signals During Slave Block Transfers

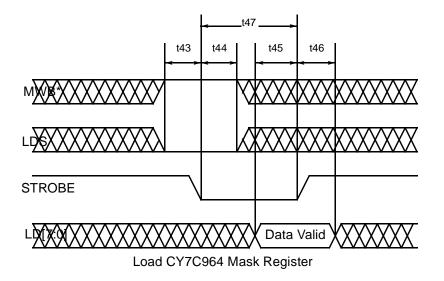

- 1.10.4 Using the CY7C964 for Additional Block Transfer Support

- <u>Chapter 1.11</u> Miscellaneous Features

- 1.11.1 Resetting the VIC068A

- 1.11.1.1 Internal Reset

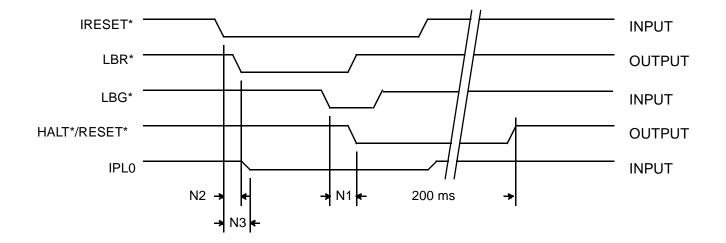

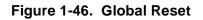

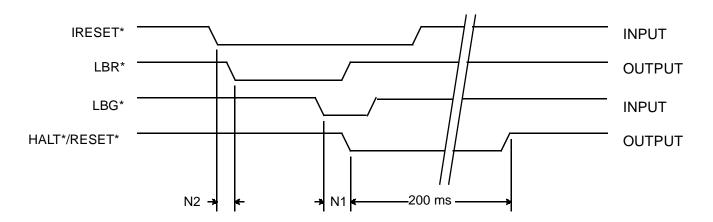

- 1.11.1.2 Global Reset

- 1.11.1.3 System Reset

- 1.11.1.4 Power-On Reset

- 1.11.2 The Local Bus Timeout Timer

- 1.11.3 The DRAM Refresh Controller

- 1.11.4 Rescinding Outputs

- 1.11.5 Turbo Mode

- 1.11.6 Metastability Delays

- Chapter 1.12 VIC068A Register Map and Descriptions

- Chapter 1.13 VIC068A AC Performance Specifications

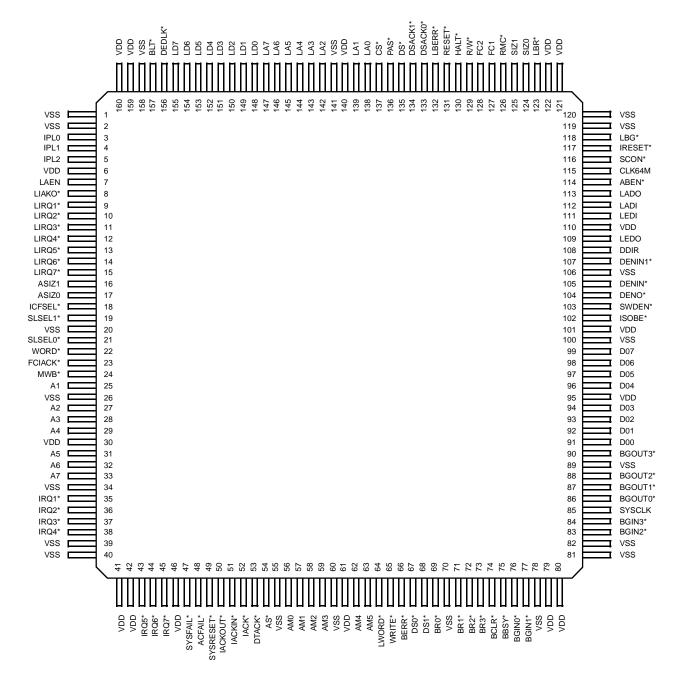

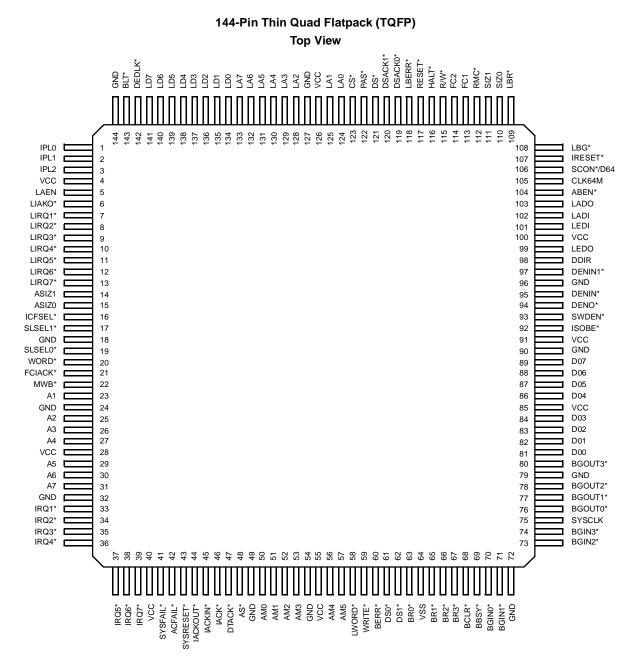

- Chapter 1.14 VIC068A Signal List and Pinouts

- Chapter 1.15 VIC068A Simulation Waveforms

- Chapter 1.16 DC Performance Specifications

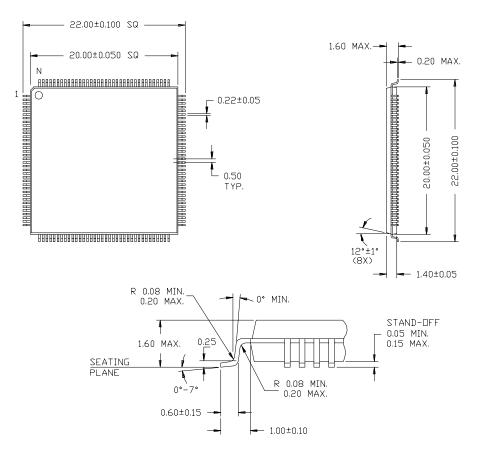

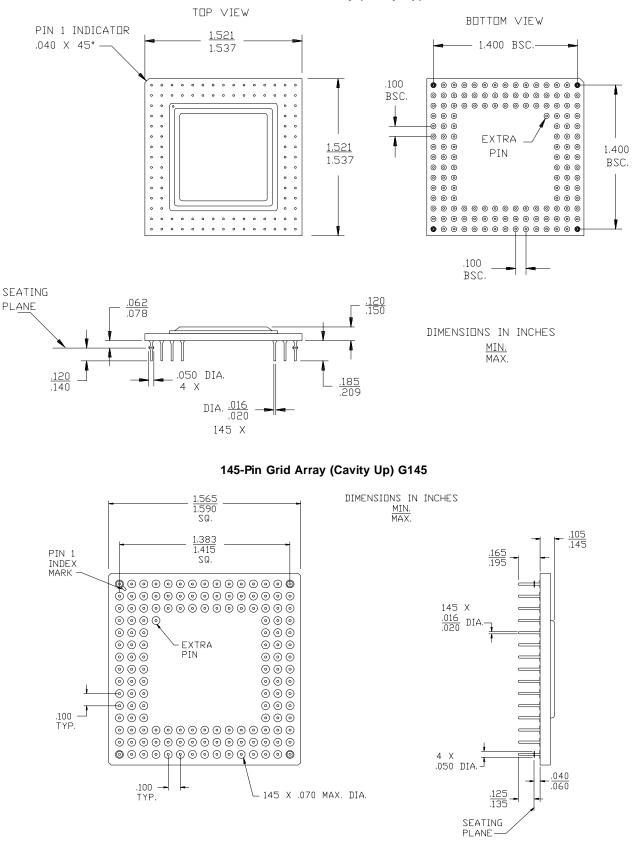

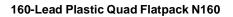

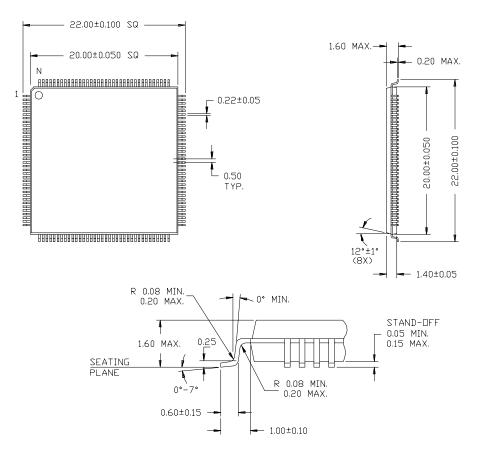

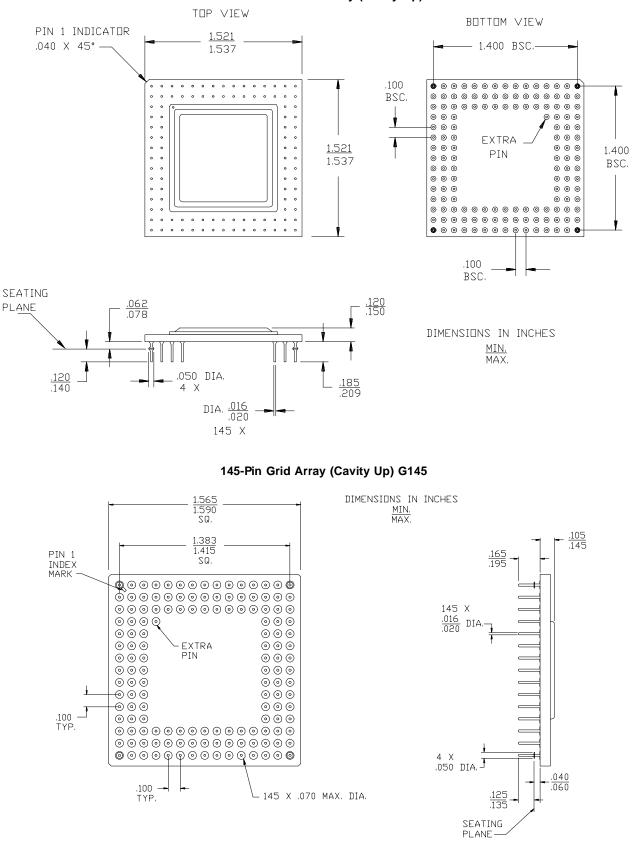

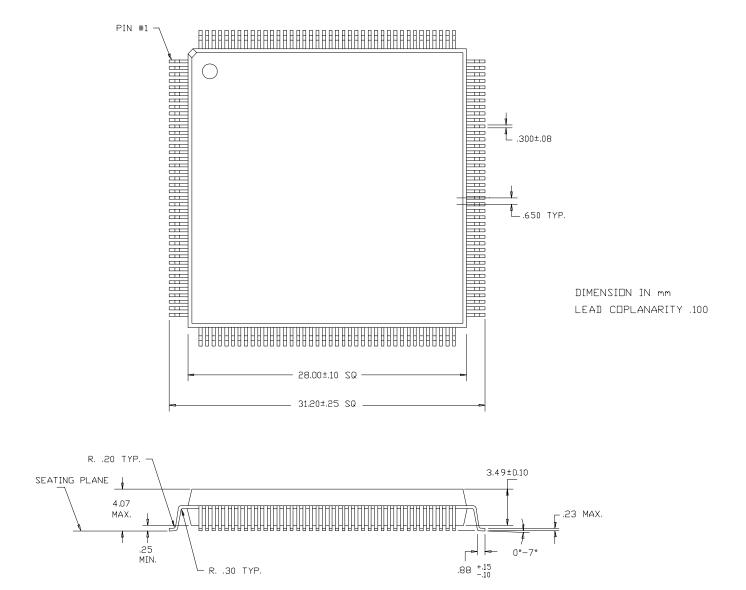

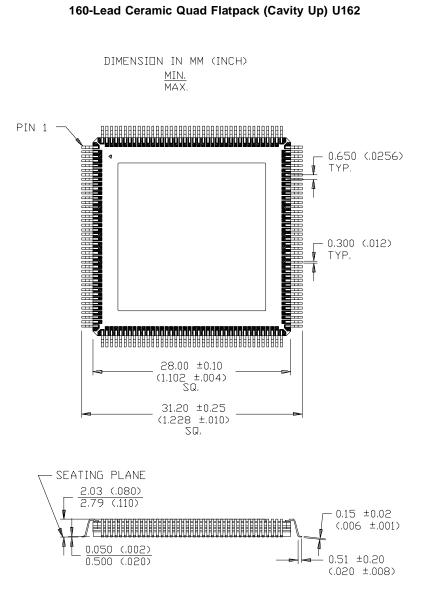

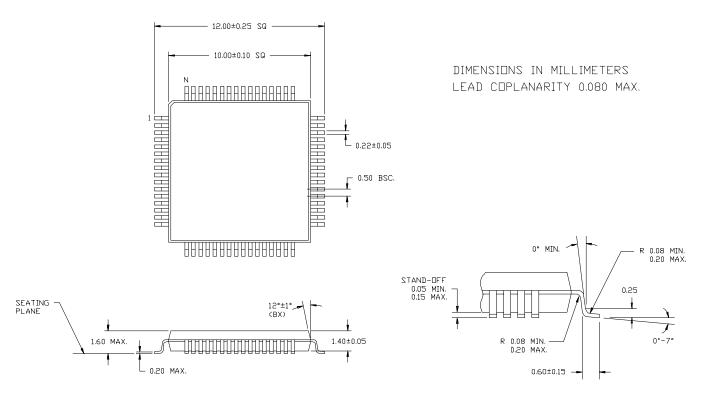

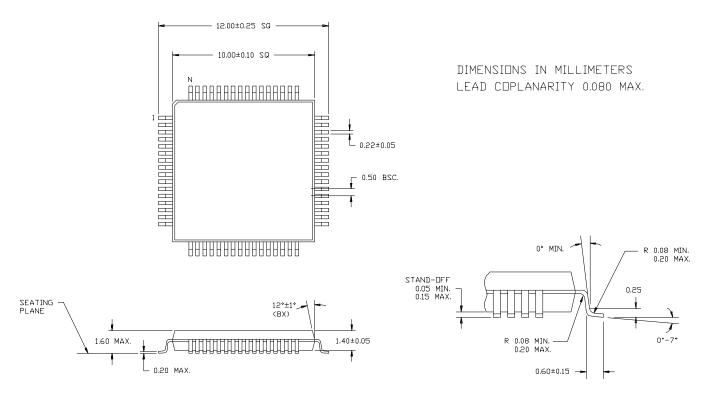

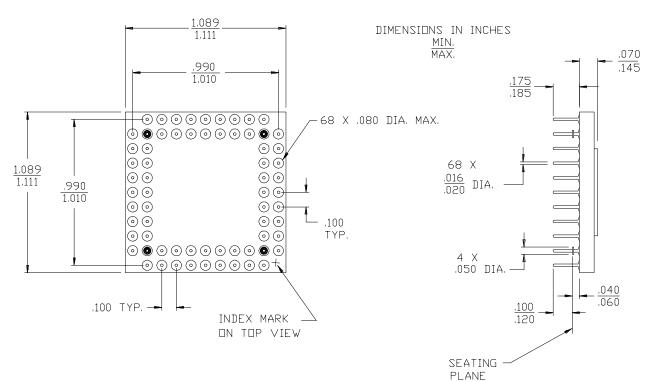

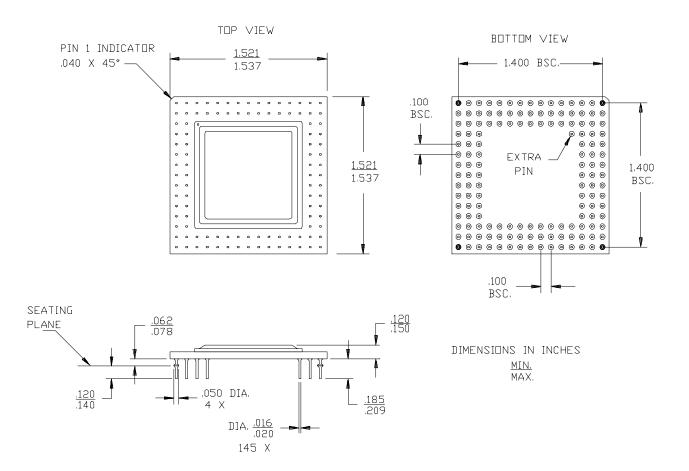

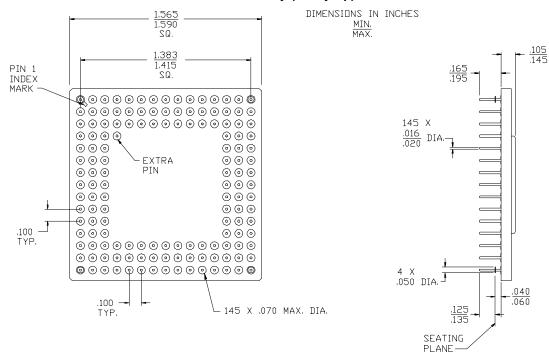

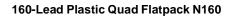

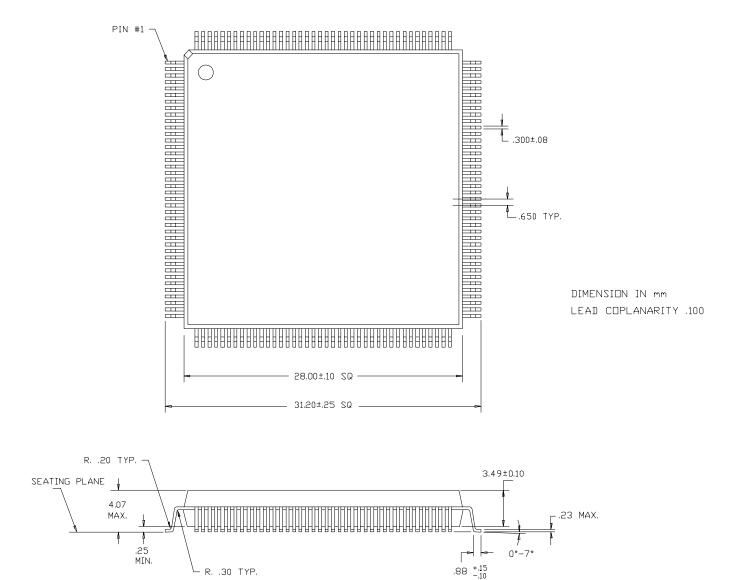

- <u>Chapter 1.17</u> Package Diagrams

#### Section 2. The VIC64 VMEbus Interface Controller

- Chapter 2.1 Introduction

- Chapter 2.2 Compatibility

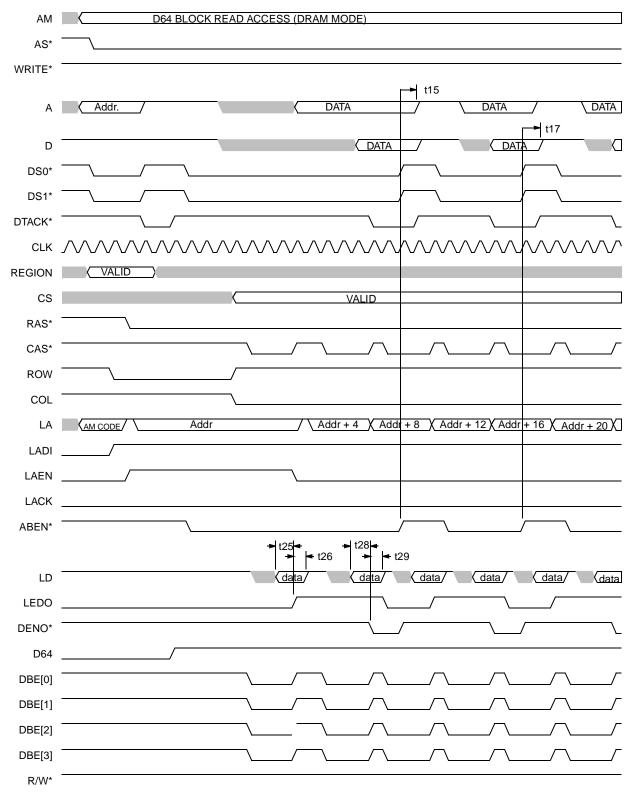

- Chapter 2.3 64-Bit Operations

- 2.3.1 VMEbus Specification

- 2.3.2 Address Modifier Codes

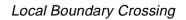

- 2.3.3 Boundary Crossing

- 2.3.4 External Circuit Complexity

- Chapter 2.4 VIC64: Additional Information

- 2.4.1 VIC64 Signal Description (Chapter 1.2)

- 2.4.2 System Controller Operations (Chapter 1.4)

- 2.4.3 VMEbus Master Operations (Chapter 1.5)

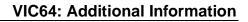

- 2.4.3.1 D64 Master Write Cycles

- 2.4.3.2 D64 Master Read Cycles

- 2.4.4 VMEbus Slave Operations (Chapter 1.6)

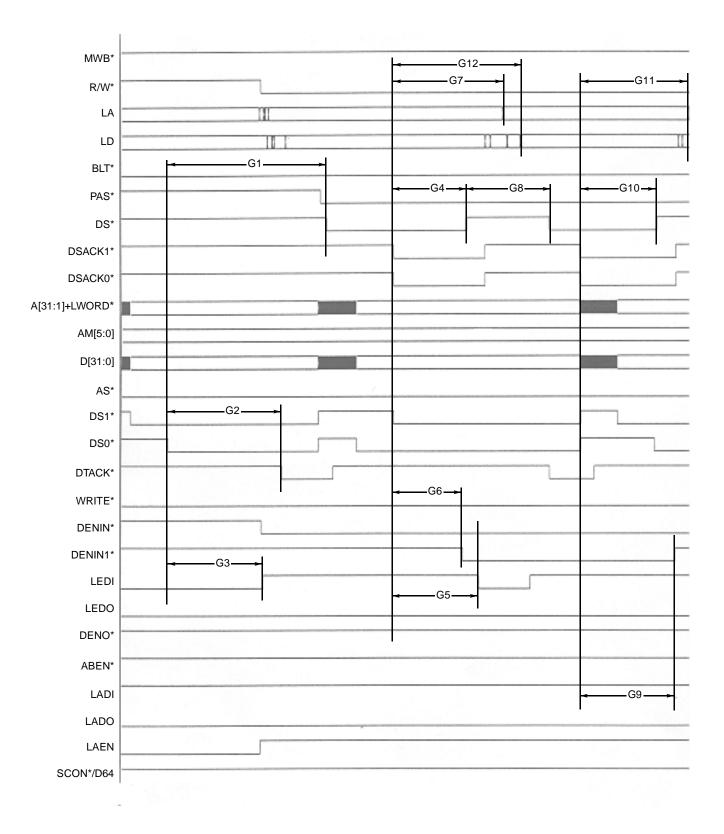

- 2.4.4.1 D64 Slave Read Cycles

- 2.4.4.2 D64 Slave Write Cycles

- 2.4.5 Interrupts (Chapter 1.9)

- 2.4.6 VIC64 Block Transfer Functions (Chapter 1.10)

- 2.4.6.1 D64 Transfers, VMEbus Boundary Crossing

- 2.4.7 Miscellaneous Features (Chapter 1.11)

- 2.4.7.1 Selection of System Controller Functionality

- 2.4.7.2 Enhanced Turbo Mode

- 2.4.8 Register Map and Descriptions (Chapter 1.12)

- 2.4.8.1 Interprocessor Communications Register 5

- 2.4.8.2 Block Transfer Definition Register

- 2.4.8.3 Release Control Register

- 2.4.8.4 Block Transfer Length Register 2

- 2.4.9 AC Performance Specifications (Chapter 1.13)

- Chapter 2.5 DC Performance Specifications

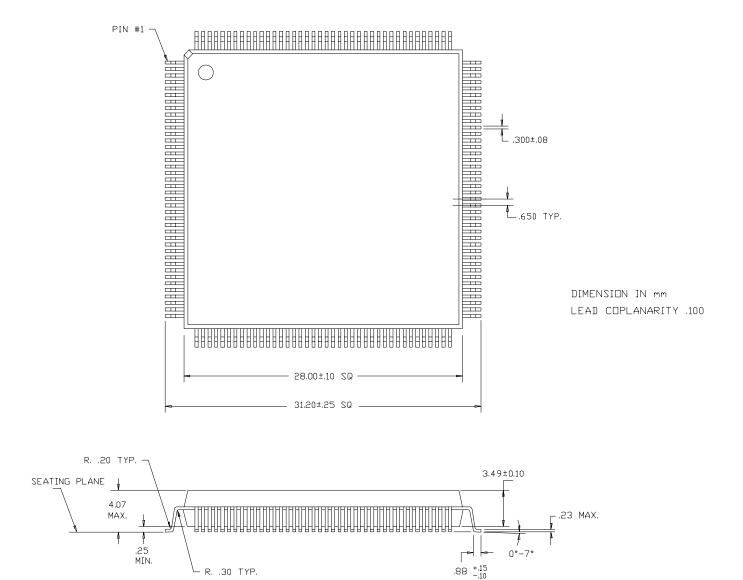

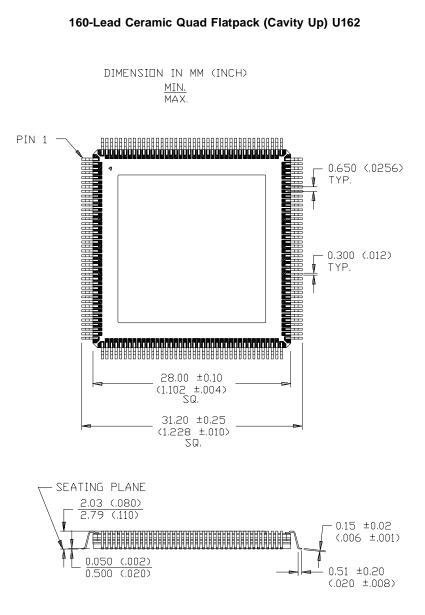

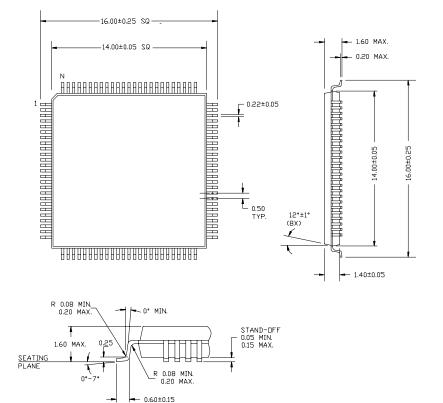

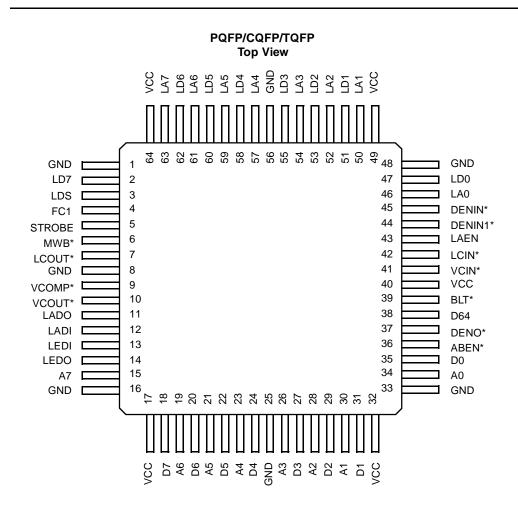

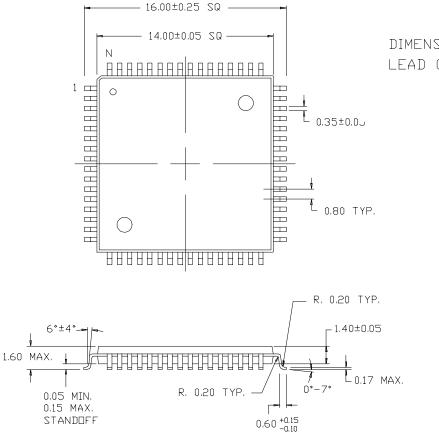

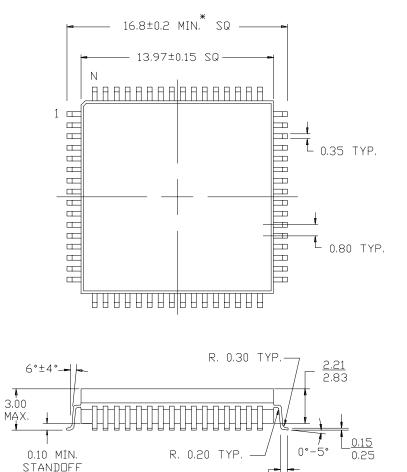

- <u>Chapter 2.6</u> Pin Configurations

- <u>Chapter 2.7</u> Package Diagrams

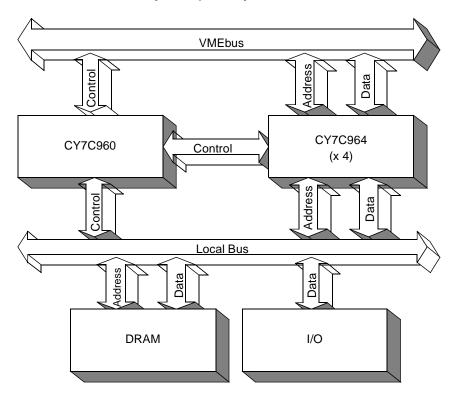

#### Section 3. The CY7C960/961 Slave VMEbus Interface Controllers

- Chapter 3.1 Introduction

- 3.1.1 Feature List

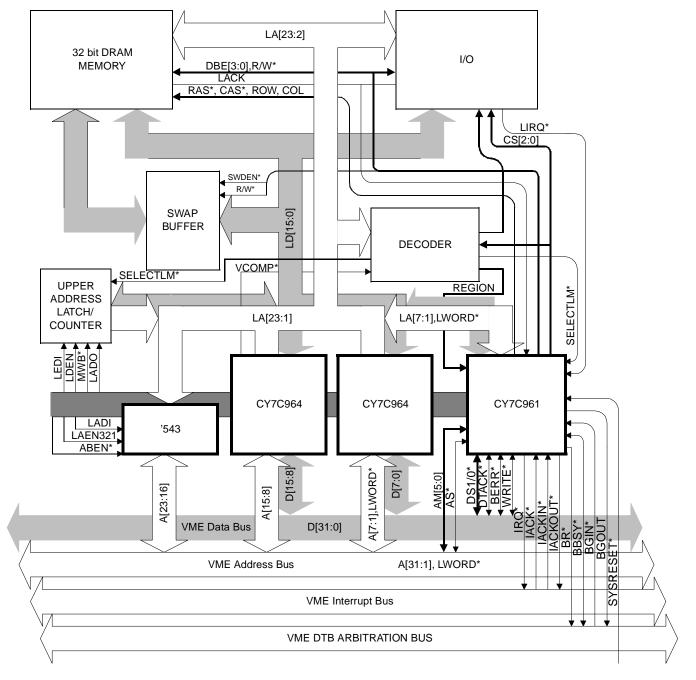

- 3.1.2 Family Overview

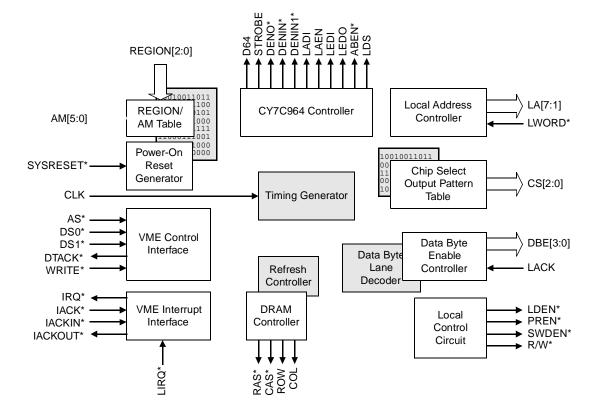

- 3.1.3 CY7C960 Architectural Overview

- 3.1.4 Key Concepts

- 3.1.4.1 Local Bus Concepts

- 3.1.4.2 VMEbus Concepts

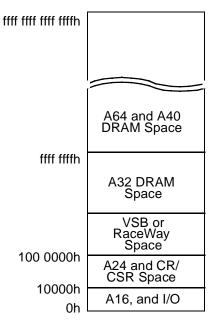

- 3.1.5 Address Mapping

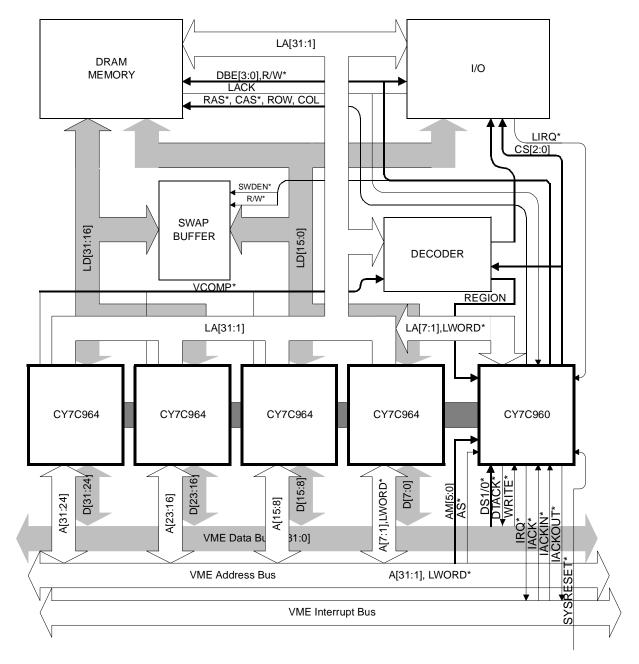

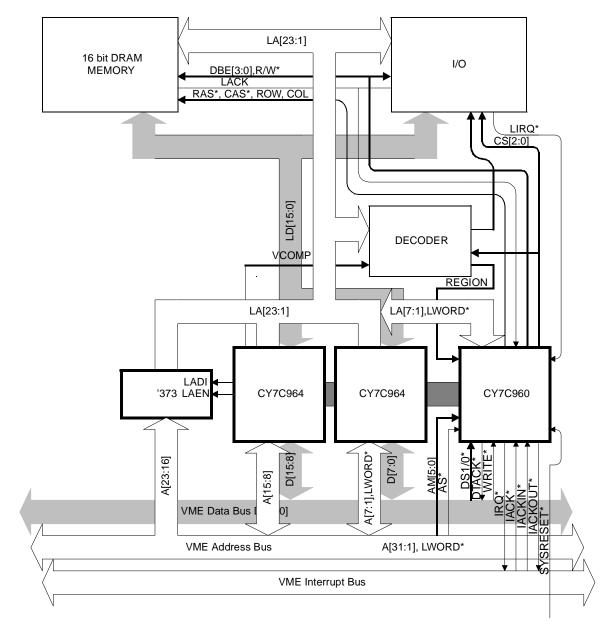

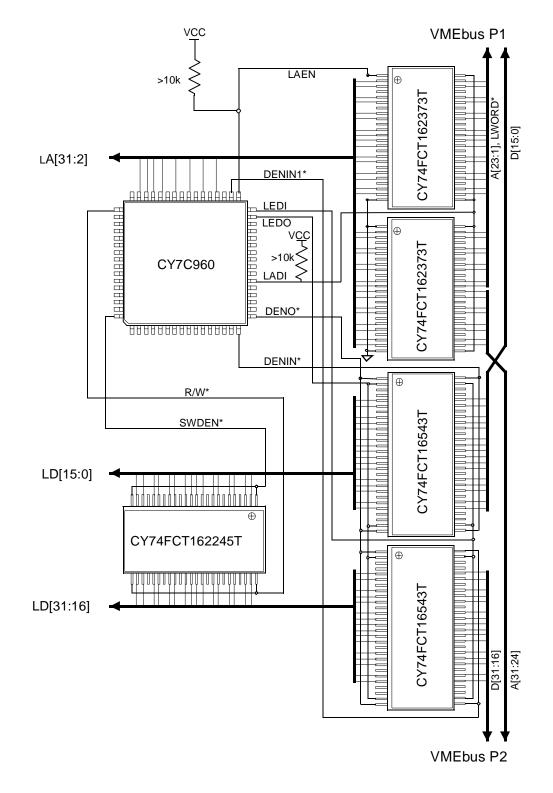

- Chapter 3.2 System Block Diagrams

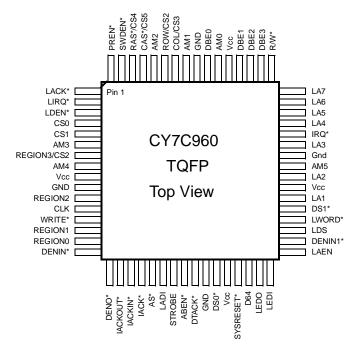

- Chapter 3.3 Pin Description

- 3.3.1 VMEbus Signals

- 3.3.2 Local Signals

- 3.3.3 Local Buffer Control Signals

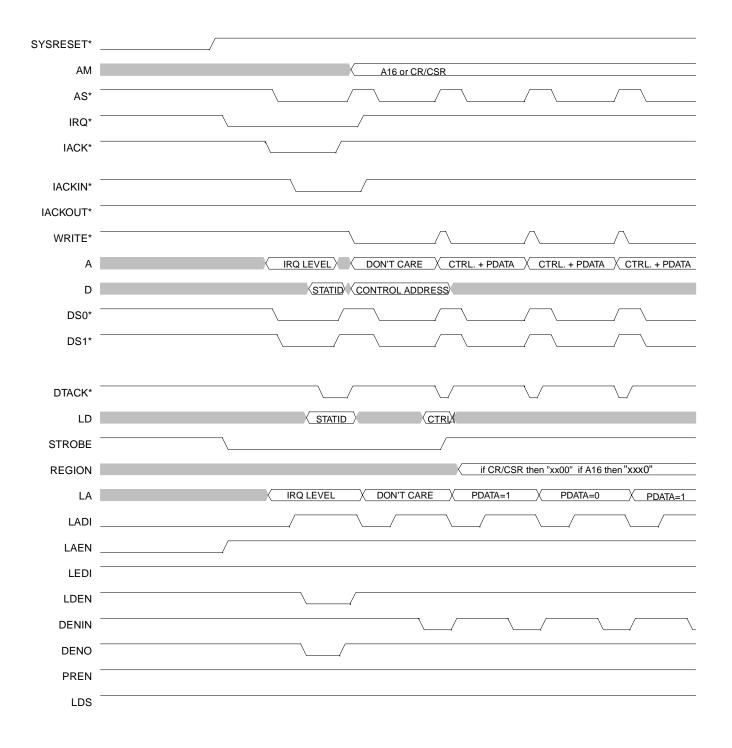

- <u>Chapter 3.4</u> Programming the CY7C960

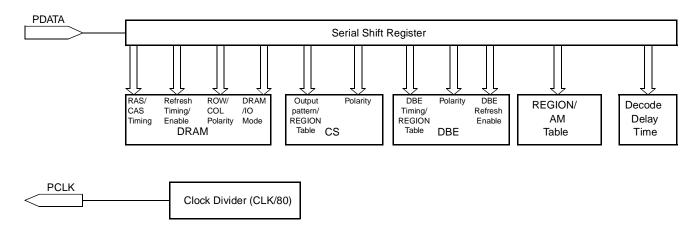

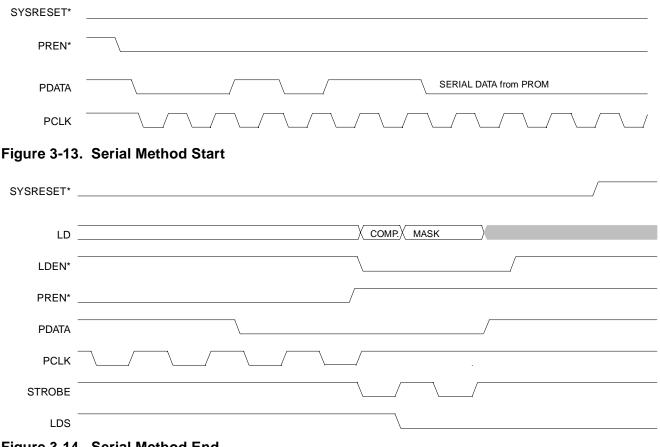

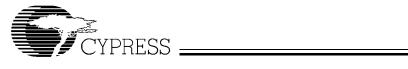

- 3.4.1 Configuration Bit Stream

- 3.4.2 Operation at Power-On or Reset

- 3.4.3 VMEbus Method

- 3.4.4 Serial PROM Method

- 3.4.5 Combination Method

- 3.4.6 Configuration Software

- 3.4.7 Programmable Features

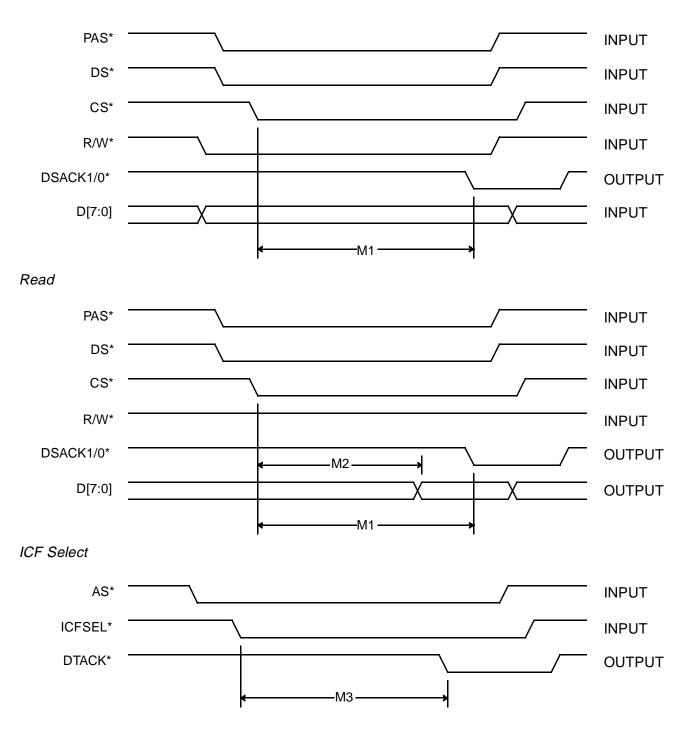

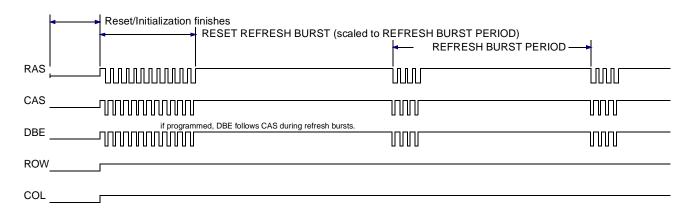

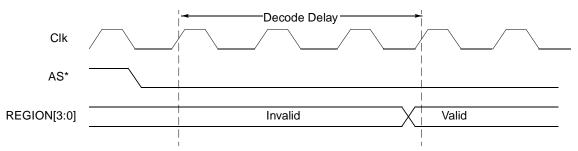

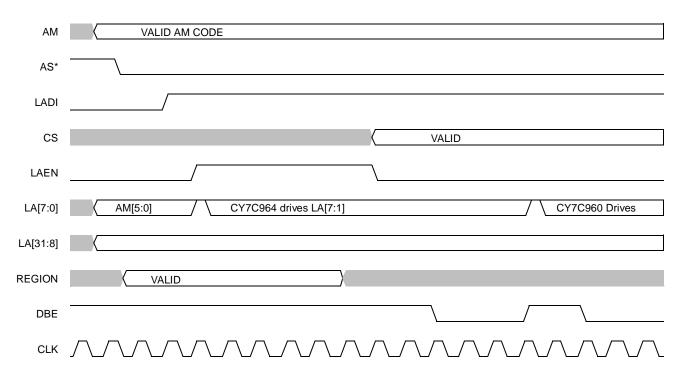

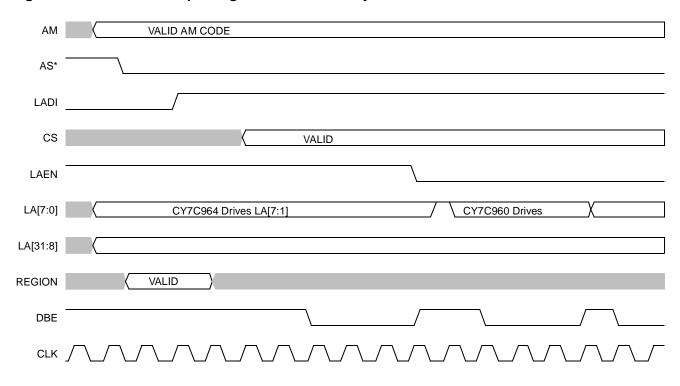

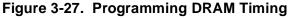

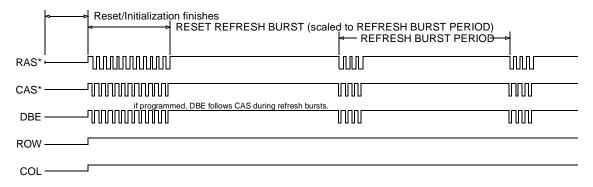

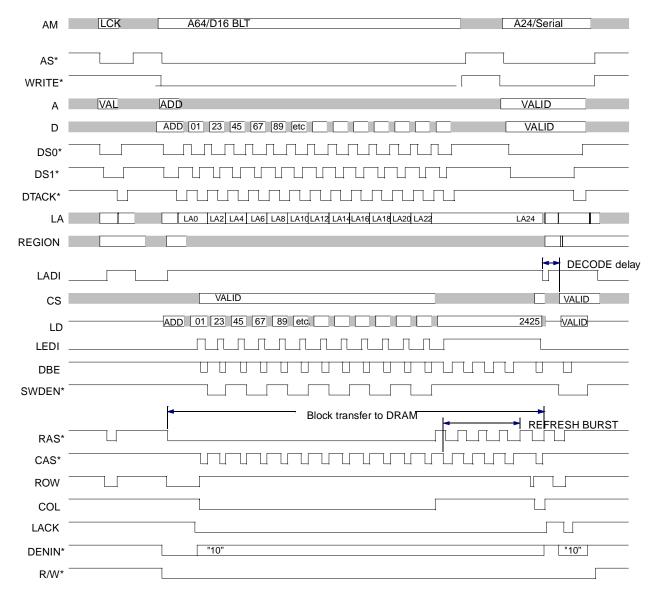

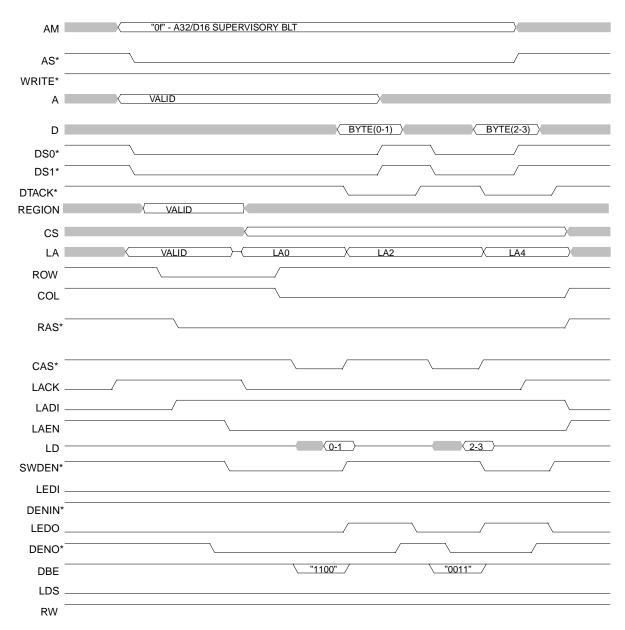

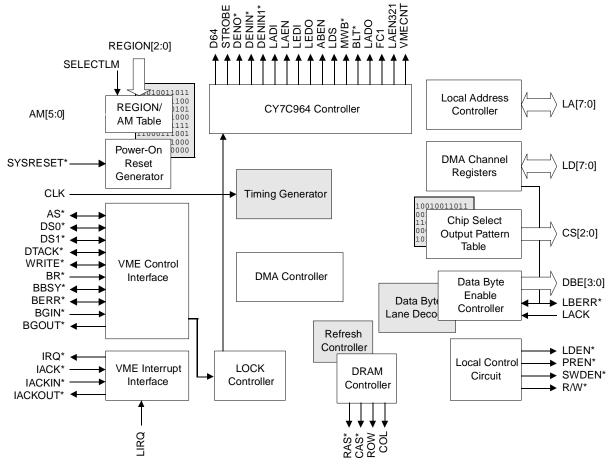

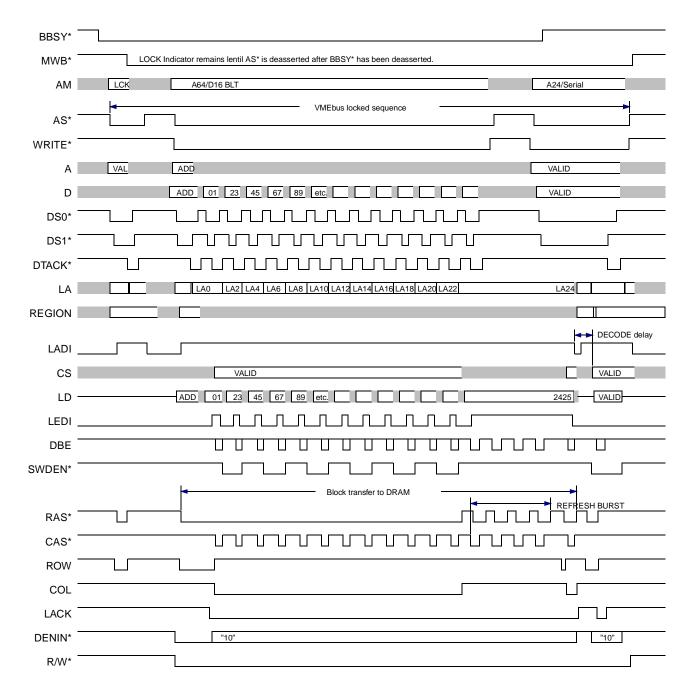

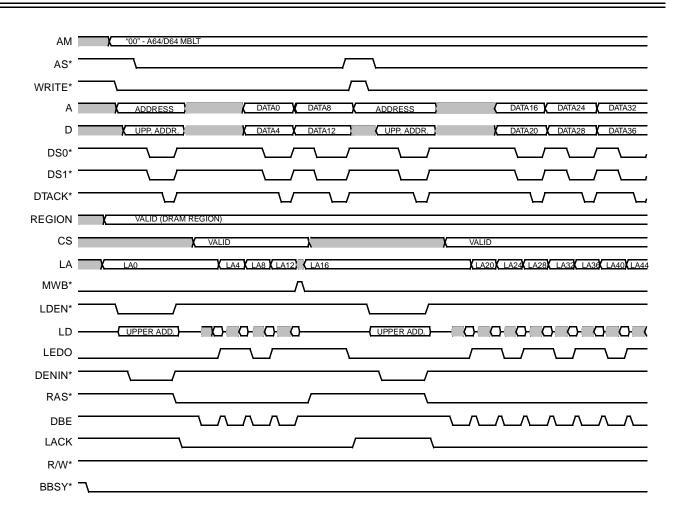

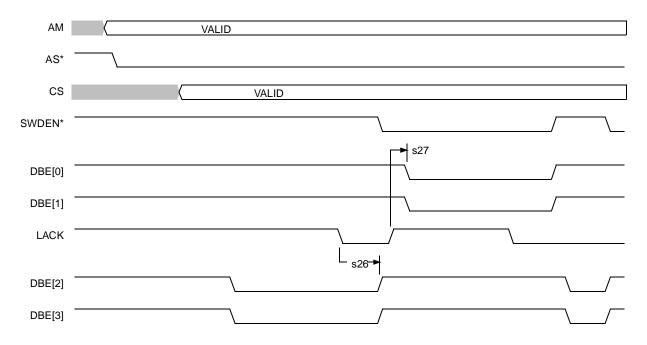

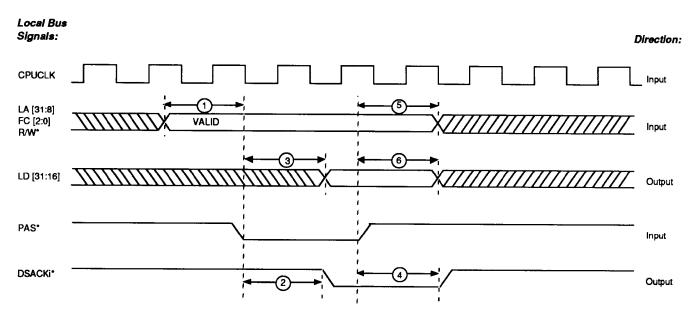

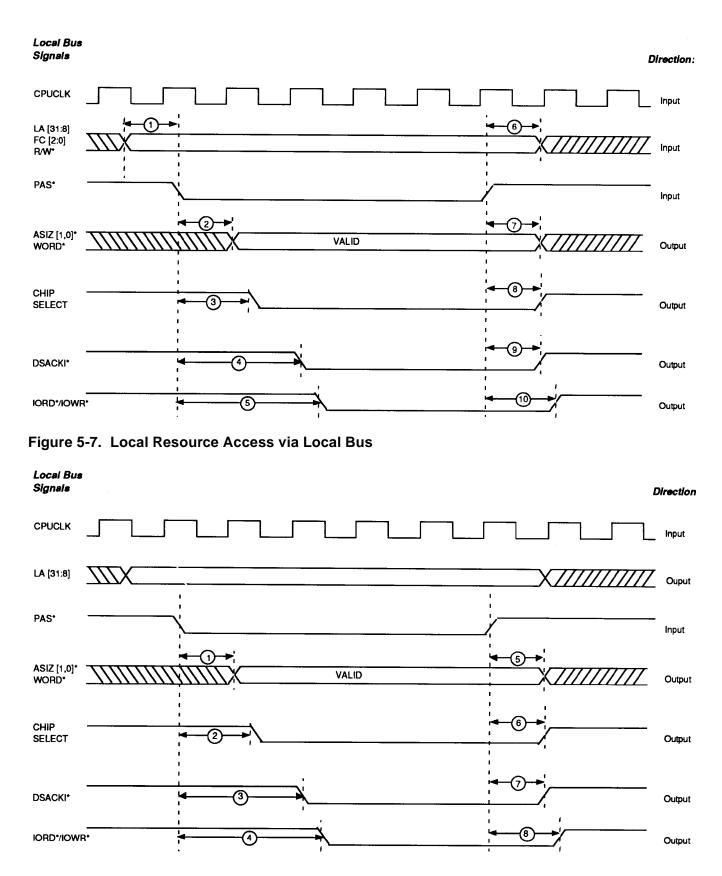

Chapter 3.5 VMEbus Interface Description 3.5.1 Definition of Terms 3.5.2 Overview 3.5.3 Region Mapping 3.5.3.1 AM/LA Multiplexing 3.5.4 Bus Holdoff 3.5.4.1 Transaction Type Detection 3.5.5 Decode Delay Timing 3.5.6 Slave Addressing Before Initialization 3.5.7 Address and Data Strobe Event Processing 3.5.8 Slave Data Transfer Acknowledgmen 3.5.9 Slave Write Posting 3.5.10 Slave Read-Ahead Cycles 3.5.11 Interrupt Cycle Support 3.5.12 Interrupt Handshake Support Chapter 3.6 CY7C964 Interface 3.6.1 CY7C964 Overview 3.6.2 CY7C964 Connections 3.6.3 Swap Buffer Control Chapter 3.7 Interfacing without CY7C964 3.7.1 Reduced Cost, Fewer Features Chapter 3.8 DRAM Control Description 3.8.1 Overview 3.8.2 Types of DRAM 3.8.3 VMEbus Implications 3.8.4 Refresh Cycles 3.8.5 Refresh Timing 3.8.6 DBE Refresh Enable Feature 3.8.7 Refresh and Reset 3.8.8 Local Acknowledge Behavior 3.8.9 DBE Signal Behavior 3.8.10 Formal Signal Description 3.8.10.1 RAS\*, CAS\*, ROW, COL 3.8.11 Programmable Features 3.8.11.1 Refresh Enable 3.8.11.2 Cycle Timing 3.8.11.3 Refresh Period 3.8.11.4 DBE Refresh 3.8.11.5 DBE Polarity 3.8.11.6 ROW, COL Polarity Chapter 3.9 I/O Control Description 3.9.1 Region Mapping 3.9.2 Chip Select Output Control 3.9.3 Chip Select Output Timing 3.9.3.1 Overview

- 3.9.3.2 Read-Aheads

- 3.9.3.3 Local Acknowledge Timing

- 3.9.4 Data Byte Enable Usage

- 3.9.5 Using I/O In DRAM Mode

- <u>Chapter 3.10</u> Design Considerations

- 3.10.1 Design Philosophy

- 3.10.2 CY7C964 Interface

- 3.10.3 Local Bus Philosophy

- 3.10.4 Read-Ahead Cycles

- 3.10.5 Write Posting

- 3.10.6 VMEbus Error Considerations

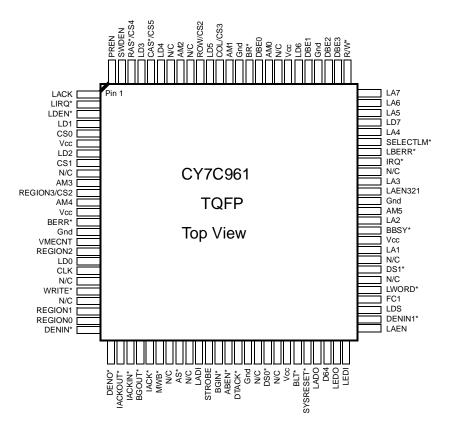

- Chapter 3.11 CY7C961 Description

- 3.11.1 Introduction

- 3.11.2 CY7C961 Lock Cycle Support

- 3.11.2.1 Overview

- 3.11.2.2 Description

- 3.11.3 CY7C961 Master Block Facility

- 3.11.3.1 Overview

- 3.11.3.2 Master Block Transfer Control from VMEbus

- 3.11.3.3 Master Block Transfer Control from Local Side of Interface

- 3.11.3.4 Programming the Master Block Facility

- 3.11.3.5 Register Definitions

- 3.11.4 Pin Description Addendum

- 3.11.4.1 VMEbus Signals

- 3.11.4.2 Local Buffer Control Signals

- 3.11.4.3 Local Signals

- 3.11.4.4 Master Block Transfer Performance

- 3.11.5 Examples of Block Transfers

- <u>Chapter 3.12</u> AC Parameters

- <u>Chapter 3.13</u> DC Performance Specifications

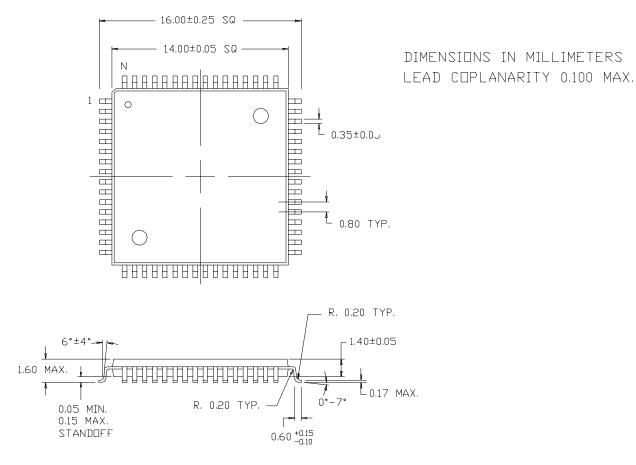

- <u>Chapter 3.14</u> Package Diagrams

#### Section 4. The CY7C964 Bus Interface Logic Circuit

- Chapter 4.1 Introduction

- Chapter 4.2 Features

- <u>Chapter 4.3</u> Interfacing to Cypress VMEbus Interface Controllers

- 4.3.1 VMEbus Signal Group

- 4.3.2 Buffer Control Signal Group

- 4.3.3 CY7C964 Local Signal Group

- 4.3.4 CY7C964 Address Comparison and Local Signal Group

- 4.3.5 Local Data Swap Buffer Logic

- <u>Chapter 4.4</u> Signal Descriptions

- 4.4.1 VMEbus Signals

- 4.4.2 Local Signals

#### <u>Chapter 4.5</u> CY7C964 Operation

- 4.5.1 Overview

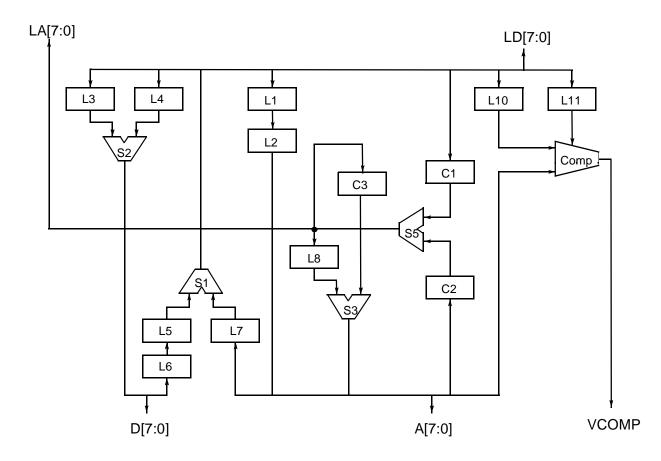

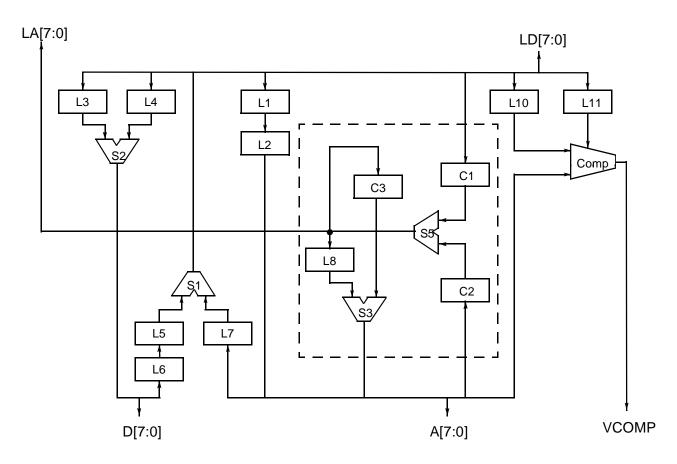

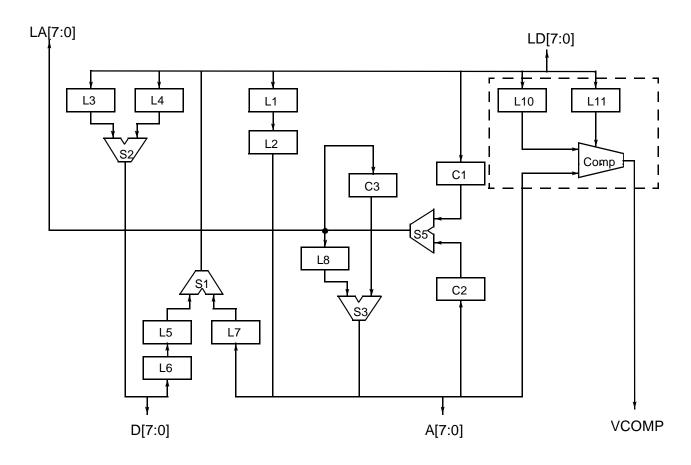

- 4.5.2 Master Block Transfer Local Address Counter (C1)

- 4.5.3 Local Address Multiplexer (S5)

- 4.5.4 Slave Block Transfer Local Address Counter/Latch (C2)

- 4.5.5 Master Block Transfer VMEbus Address Counter (C3)

- 4.5.6 VMEbus Address Latch (L8) and Multiplexer (S3)

- 4.5.7 VMEbus Address Comparator

- 4.5.8 VMEbus D64 Block Transfer Data Pipeline and Multiplexer

- 4.5.9 VMEbus D64 Block Transfer Data Demultiplexer

- Chapter 4.6 CY7C964 Alternate BLT Initiation Operation for VIC068A and VIC64

- <u>Chapter 4.7</u> DC Performance Specifications

- Chapter 4.8 AC Performance Specifications

- Chapter 4.9 Pin Description

- 4.9.1 Pin Definitions

- 4.9.2 Pin Configurations

- <u>Chapter 4.10</u> Package Diagrams

#### Section 5. The VAC068A VMEbus Address Controller

- Chapter 5.1 Introduction to the VAC068A

- 5.1.1 Features Summary

- 5.1.2 General Description

- Chapter 5.2 VAC068A Signal Descriptions

- 5.2.1 VMEbus Signals

- 5.2.2 CPU/Local Interface Signals

- 5.2.3 Parallel I/O-Shared Function Signals

- 5.2.4 Data Flow Control Signals

- Chapter 5.3 VAC068A Overview

- 5.3.1 Applications

- 5.3.2 VMEbus Address Decoding

- 5.3.2.1 Master Access

- 5.3.2.2 Programmable VMEbus Space

- 5.3.2.3 A24 VMEbus Space

- 5.3.2.4 A16 VMEbus Space

- 5.3.3 VMEbus Slave Access

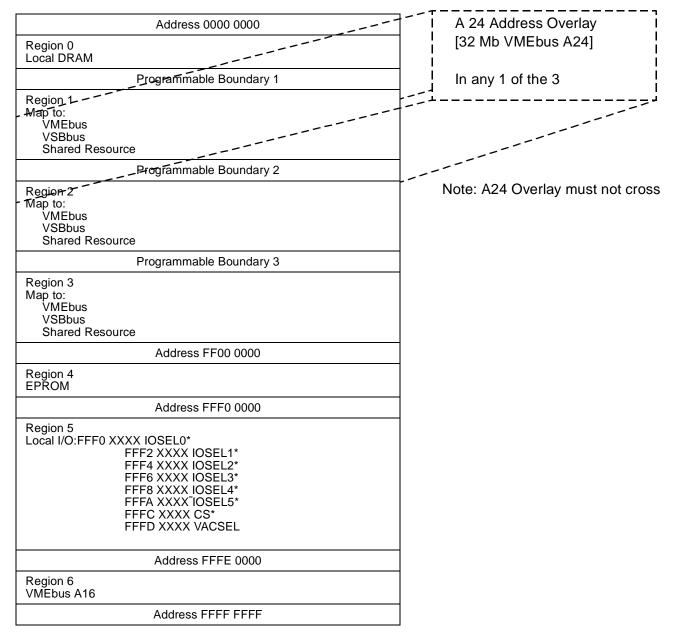

- 5.3.4 Local Memory Map Decoding

- 5.3.4.1 DRAM Decode

- 5.3.4.2 Programmable Decode

- 5.3.4.3 EPROM Decode

- 5.3.4.4 Local I/O Select Decode

- 5.3.5 Local Decode Control/Status

- 5.3.5.1 Function Code Decode

- 5.3.6 Programmable Input/Output

- 5.3.6.1 Serial I/O

- 5.3.6.2 I/O Select

- 5.3.7 Interrupt Support

- 5.3.7.1 Interrupt Status Register

- 5.3.7.2 PIO Interrupt

- 5.3.8 Miscellaneous Features

- 5.3.8.1 PIO9 Debounce

- 5.3.8.2 Isolated Data Bus

- 5.3.8.3 Programmable DSACKi\* Timing

- 5.3.8.4 VIC068A/VAC068A DMA Support

- 5.3.8.5 IORD\* and IOWR\*

- 5.3.8.6 I/O Recovery Timer

- 5.3.8.7 IACK Cycle Emulation for Non-680X0 Processors

- 5.3.8.8 Cache Inhibit Output

- Chapter 5.4 VAC068A Operation

- 5.4.1 Resetting the VAC068A

- 5.4.1.1 Global Reset

- 5.4.1.2 Soft Reset

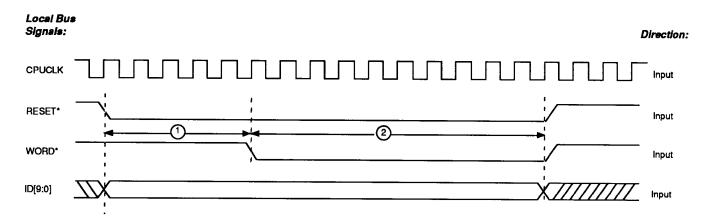

- 5.4.1.3 RESET\* Termination

- 5.4.2 System Initialization

- 5.4.3 Configuring the Local Memory Map

- 5.4.3.1 DRAM Size

- 5.4.3.2 VSB Space

- 5.4.3.3 VMEbus A32, D32 Access

- 5.4.3.4 Shared Resource Area

- 5.4.3.5 EPROM Space

- 5.4.4 Configuring the VMEbus Address Map

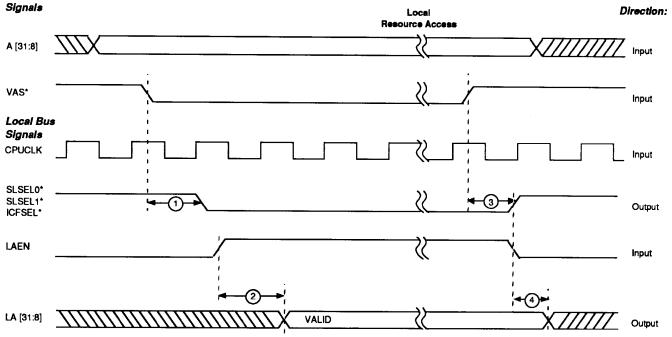

- 5.4.4.1 SLSEL0\* Access

- 5.4.4.2 SLSEL1\* Access

- 5.4.4.3 ICFSEL\* Access

- 5.4.4.4 VME A24 Master Cycle

- 5.4.4.5 VME A16 Master Cycle

- 5.4.4.6 Decode Control Register

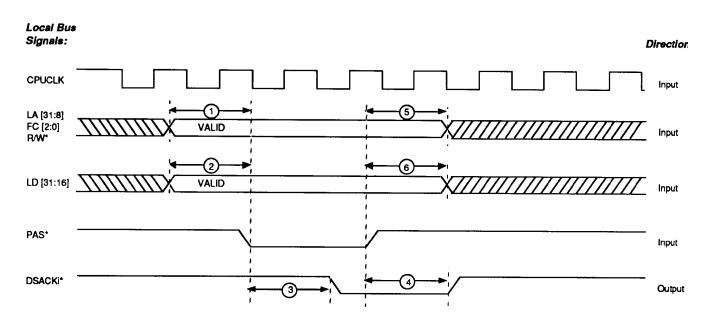

- 5.4.5 VME Master Access

- 5.4.6 VME Slave Operation

- 5.4.6.1 Slave Transfer Sequence

- 5.4.7 VME Master Block Transfer

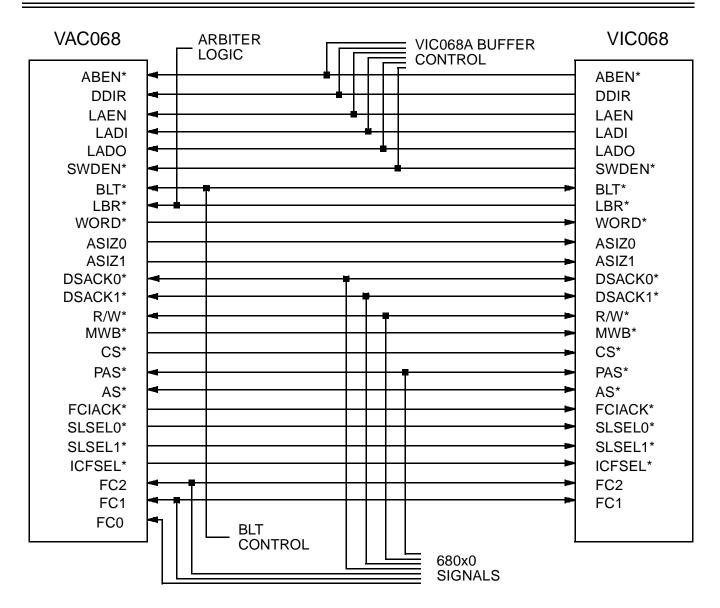

- 5.4.8 VIC068A/VAC068A Interconnect Diagram

- <u>Chapter 5.5</u> VAC068A Register Map and Descriptions

- Chapter 5.6 VAC068A AC Performance Specifications

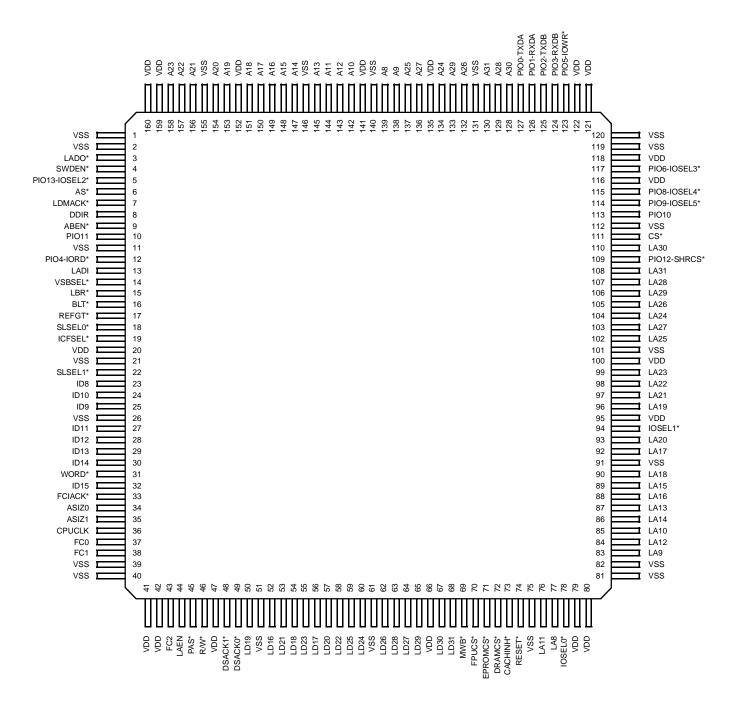

- Chapter 5.7 VAC068A Signal List and Pinout

- Chapter 5.8 DC Performance Specifications

- <u>Chapter 5.9</u> Package Diagrams

**Glossary**

# Introduction

Thank you for your interest in Cypress's line of VMEbus Interface Products! Cypress provides a wide range of solutions to help you design almost any VMEbus interface. This Handbook explains the use of each product individually. Diagrams and examples are shown where needed to help clarify the operation of each part. This book is broken into five sections as follows:

Section 1: The VIC068A VMEbus Interface Controller

Section 2: The VIC64 VMEbus Interface Controller

Section 3: The CY7C960/961 Slave VMEbus Interface Controllers

Section 4: The CY7C964 Bus Interface Logic Circuit

Section 5: The VAC068A VMEbus Address Controller

We also offer the *Cypress Applications Handbook*, which contains design examples using our VMEbus products. Although these examples may not show the exact solution you need, they can be used as building blocks to create an interface that fits your design.

Cypress also manufactures high speed SRAMs, Programmable Logic Devices (PLDs), Clock devices, and many Datacom devices as an aid for your design. Call (800)858-1810 to obtain a copy of one of our data books or the *Cypress Applications Handbook*.

For further help using any Cypress device, to download datasheets or application notes, or for general information about Cypress Semiconductor, check out our web page at www.cy-press.com. Datasheets or applications notes can be sent directly to your fax machine by calling (800)213-5120. For direct technical assistance call (408)943-2821 to reach our applications hotline or email us at cyapps@cypress.com.

# How to Use This Book

This guide provides the hardware and software designer with detailed information on the Cypress Semiconductor VMEbus Interface Products. It may also be used to provide detailed information regarding existing off-the-shelf VMEbus modules that utilize the Cypress line of interface products.

This document is not intended to instruct the reader on VMEbus standards and protocol. Firsttime VMEbus designers and users requiring such information are encouraged to refer to the VMEbus specification (ANSI/VITA-1-1994).

Throughout this specification, specific conventions are used when referring to VMEbus signals, terms, and register bit and bit fields.

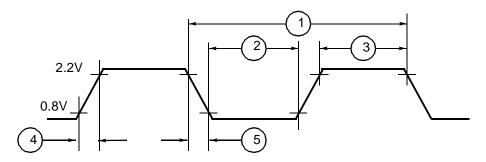

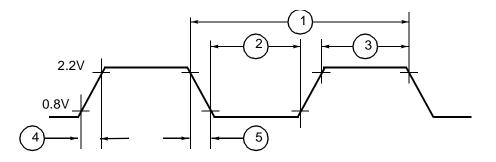

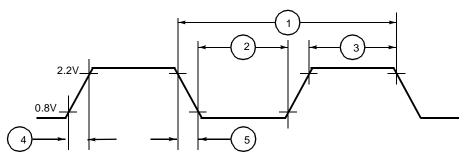

- The terms High or H are used to specify actual >V<sub>IH</sub> or >V<sub>OH</sub> levels. The terms Low or L are used to specify actual <V<sub>IL</sub> or <V<sub>OL</sub> levels.

- Active Low signals are followed by an asterisk (\*).

- Active High signals, clock signals, and address/data buses do not have an asterisk.

- The terms *assertion* and *deassertion* are used to indicate the forcing of a signal to a particular state. Assertion means forcing a signal to its TRUE or active state. Deassertion refers to forcing a signal to its FALSE or inactive state. These terms are used independent of the actual voltage levels represented.

- Address and data buses (or portions thereof) are referred to using a bus[MSB:LSB] format. For example, the entire VMEbus data bus is referred to as D[31:0].

- An individual bit of an address or data bus is referred to using a bus[bit] format. For example, bit 0 of the local address bus is referred to as LA[0] or, where space was restrictive, LA0.

- When referring to address and data buses with a user-specific limit, a "+" character is used to indicate the limit. For example, to refer to the range from LA bit 0 to some user-specified or unknown limit, the term LA[+:0] is used. LA bit 31 to a lower user-specified or unknown limit is referred to as LA[31:+].

- When referring to one or more related signals or registers containing numbers, the lowercase letter "i" is used to indicate the signal(s). For example, when referring to one or more of the VMEbus bus request signals (BR3\*, BR2\*, BR1\*, and/or BR0\*), the term BRi\* is used. When referring to the SS0CR0 and/or the SS1CR0 register, the term SSiCR0 is used.

- When referring to a specified group of signals ending in a number, a slash (/) is used to separate the signals. For example, when referring to the SIZ1 and SIZ0 signals, the term SIZ1/0 is used.

- Specific bits of a register are referred to in a register[bit] format. Ranges of bits are referred to in a register[upper:lower] format.

- Setting register bit or bits refers to writing a 1 (one) into the respective bits.

- Clearing register bit or bits refers to writing a 0 (zero) into the respective bits.

- The term *module* refers to a VMEbus circuit board. Depending on the context, module may or may not imply a VMEbus circuit board.

- The terms *local* or *local side* refer to CPU, memory, or other resources that connect to the non-VMEbus signals of the VMEbus interface device.

- The terms *master write* and *slave write* both imply a VMEbus write operation where data is transferred from a VMEbus master to a VMEbus slave. *Master read* and *slave read* both imply VMEbus read operations where data is transferred from a VMEbus slave to a VMEbus master.

- All hexadecimal values are preceded by a dollar sign (\$).

- The term *byte* is used to indicate 8 bits. The term *word* is used to indicate 16 bits. The terms *longword* and *lword* are used to indicate 32 bits.

- The term 68K is used to indicate a member of the Motorola CISC family of microprocessors (i.e., MC68000 through MC68040).

- The letter "T" is used to indicate the clock input period.

- The term *rescinding* is used to indicate a three-state output that is driven High before it is three-stated. See section 1.11.4.

- The letters "L" and "H" are used to indicate a High or Low value driven *by* the VMEbus interface device. The numbers "1" and "0" are used to indicate a High or Low value driven *to* the VMEbus interface device.

# Section 1

The VIC068A VMEbus Interface Controller

# Introduction to the VIC068A

1.1

### 1.1.1 Description

The Cypress Semiconductor VMEbus Interface Controller, VIC068A, is a single, integrated circuit designed to minimize the cost and board-area requirements of VMEbus boards, while at the same time maximizing their performance. The VIC068A was designed using Cypress's high-performance standard cells on a CMOS process. The VIC068A provides all VMEbus system controller functions plus many other features that simplify the development of VMEbus-based modules. The VIC068A utilizes Cypress's patented and military-approved high-drive CMOS drivers. These CMOS drivers connect directly to the VMEbus signal pins.

The VIC068A was developed through the joint efforts of Cypress Semiconductor and the VMEbus Technology Consortium under the auspices of the VMEbus International Trade Association (VITA). Because of this cooperation, the VIC068A offers an implementation that provides the broadest feature set and multi-vendor compatibility available on the market.

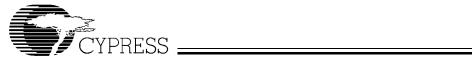

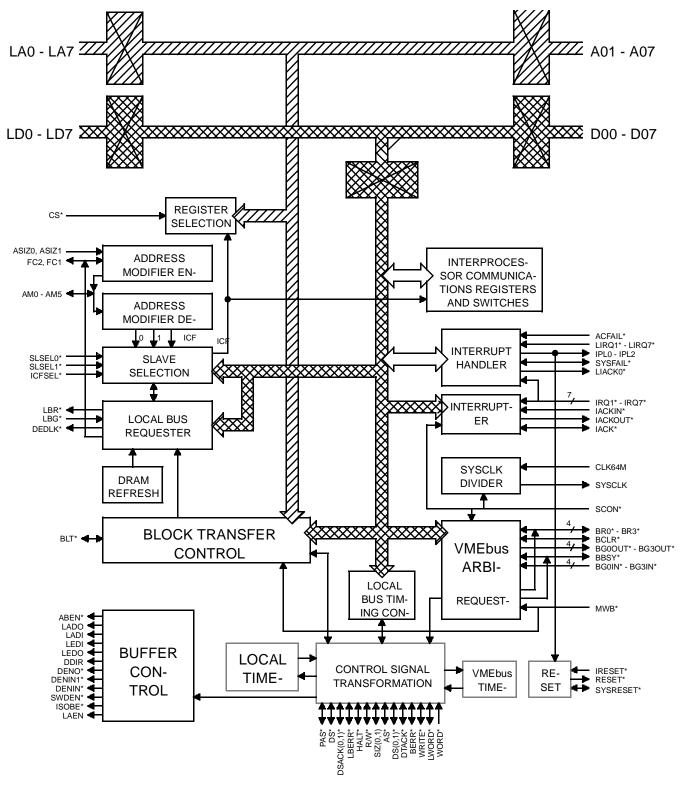

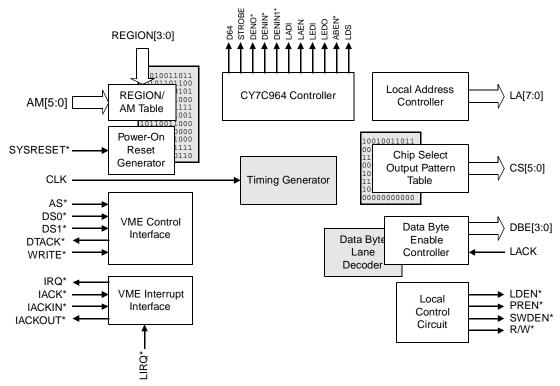

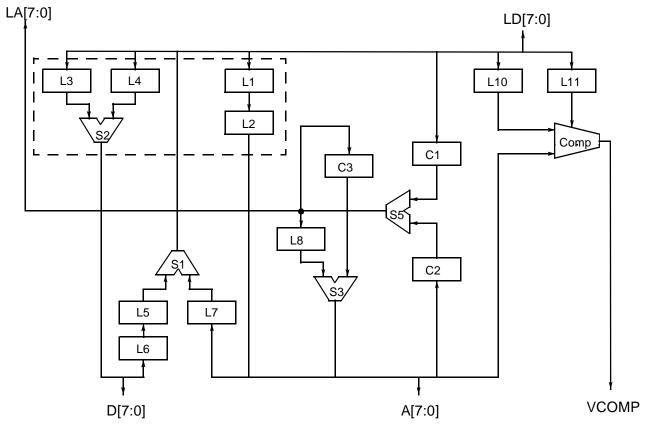

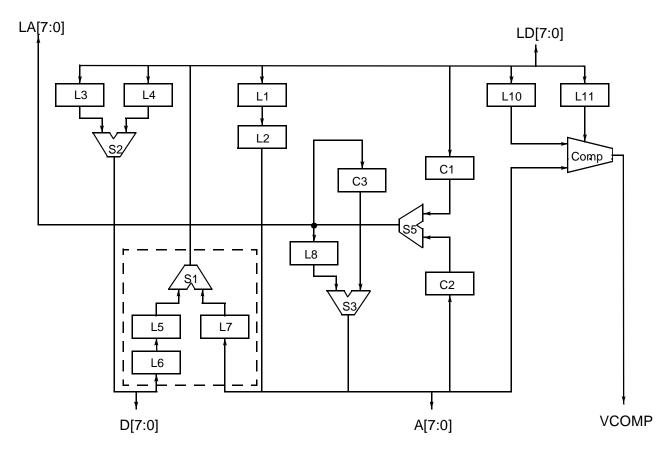

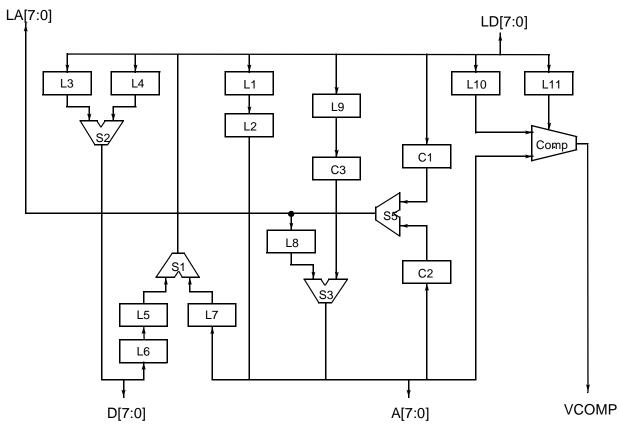

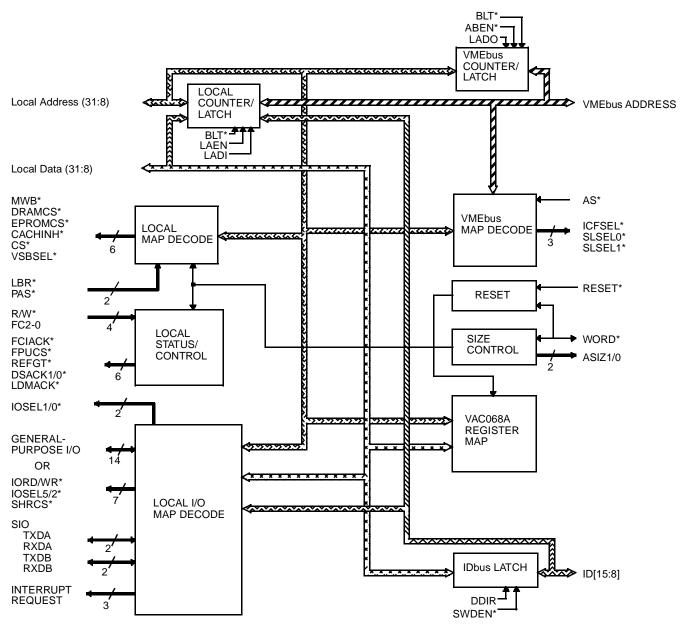

A block diagram of the VIC068A is shown in *Figure 1-1*. A typical 68030 application is shown in *Figure 1-2*.

### 1.1.2 Features Summary

The complete VMEbus Interface Controller and Arbiter includes

- PRI, SGL, and RRS arbitration

- the capability to drive arbitration signals directly

- arbitration timeout timer

- VMEbus timeout timer

- the capability to drive BGOUT\*, IACK\* daisy-chain

The complete VMEbus Master Interface includes

- five release modes

- write posting

- indivisible cycle support

- deadlock detection

- fair requesting

• user-defined AM code generation

The complete VMEbus Slave Interface includes

- write posting

- configurable local access timing

- slave block transfer support

Interleaved Block Transfer support includes

- block transfers with local DMA

- programmable transfer length, burst length, interleave period, and access timing

- "dual-path" option

The compete VMEbus, Local Interrupt Handler/Generator includes

- seven local interrupt signals

- seven VMEbus interrupt signals

- seven-level local encoding

- error/status interrupts

- periodic "heartbeat" interrupt

Interprocessor Communication Support includes

- four global mailbox interrupts

- four module mailbox interrupts

- five mailbox registers

Other features include

- local DRAM refresh control

- local timeout timer

- "turbo" mode

- programmable metastability delay

The VIC068A meets the IEEE VMEbus Specification 1014 Rev C.1.

Figure 1-1. VIC068A Block Diagram

Figure 1-2. VIC068A on 68030 Board

# VIC068A Signal Descriptions

1.2

# 1.2.1 VMEbus Signals

This chapter lists VMEbus-specified signals that are driven and received directly by the VIC068A. For complete definitions and descriptions of these signals, refer to the VMEbus specification (IEEE 1014).

#### SYSRESET\*

| Input:  | Yes                 |

|---------|---------------------|

| Output: | Yes, open collector |

| Drive:  | 48 mA               |

This is the VMEbus system reset signal. A Low level on this signal resets the internal logic of the VIC068A and asserts the signals HALT\* and RESET\*. These signals remain asserted for a minimum of 200 ms. If the VIC068A is configured as VMEbus system controller, a Low level on IRESET\* asserts SYSRESET\* for a minimum of 200 ms. See section 1.11.1.

#### ACFAIL\*

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

This is the VMEbus AC fail signal. This signal should be driven by the VMEbus power monitor (if installed), not the VIC068A. The VIC068A can be enabled to provide a local interrupt when this signal is asserted. See section 1.9.5.

#### SYSFAIL\*

| Input:  | Yes                 |

|---------|---------------------|

| Output: | Yes, open collector |

| Drive:  | 48 mA               |

As an output, the SYSFAIL\* signal is asserted when it detects that HALT\* has been asserted for more than 6  $\mu$ s by a source other than the VIC068A.

This signal is asserted by the VIC068A after a global reset. It may be masked by clearing ICR6[6] or by setting ICR7[7]. The VIC068A can also be enabled to provide a local interrupt on the assertion of this signal. See section 1.9.5.

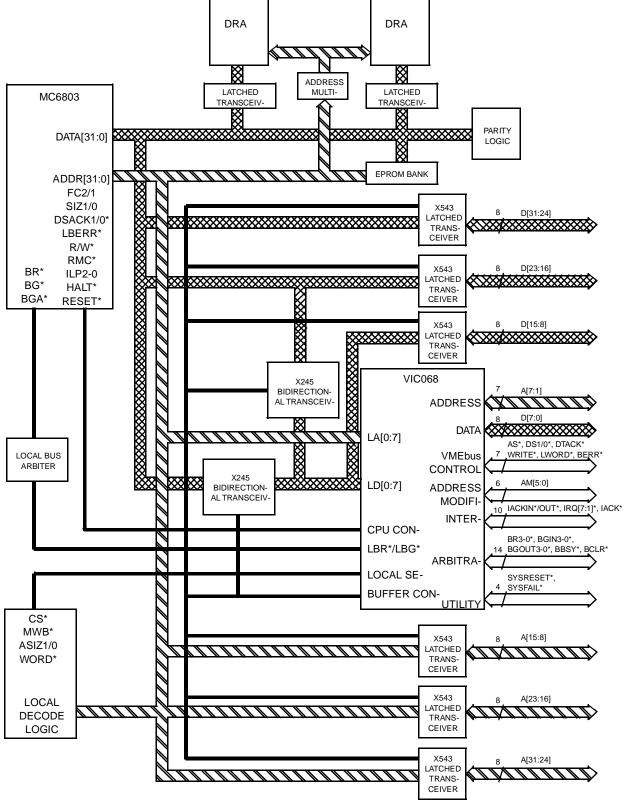

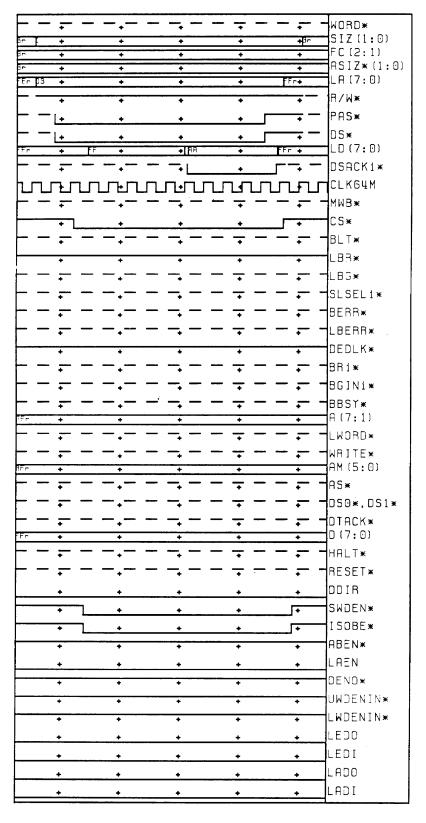

Figure 1-3. VIC068A Signal Diagram

#### SYSCLK

| Input:  | No               |

|---------|------------------|

| Output: | Yes, three-state |

| Drive:  | 64 mA            |

This is the VMEbus system clock signal. This signal is driven by the VIC068A when configured as system controller (SCON\* asserted). The output frequency is one-fourth the frequency delivered to the VIC068A CLK64M signal. To deliver the required 16 MHz on this signal, the VIC068A must run at 64 MHz. The VIC068A does not use this signal internally.

#### BR3\*-BR0\*

| Input:  | Yes                 |

|---------|---------------------|

| Output: | Yes, open collector |

| Drive:  | 48 mA               |

These are the VMEbus Bus Request signals.

#### BG3IN\*-BG0IN\*

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

These are the VMEbus daisy-chained Bus-Grant-In signals.

#### BG3OUT\*-BG0OUT\*

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

These are the VMEbus daisy-chained Bus-Grant-Out signals.

#### BBSY\*

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 48 mA           |

This is the VMEbus Bus-Busy signal.

#### BCLR\*

| Input:  | Yes              |

|---------|------------------|

| Output: | Yes, three-state |

| Drive:  | 64 mA            |

This is the VMEbus Bus-Clear signal.

#### D7-D0

| Input:  | Yes              |

|---------|------------------|

| Output: | Yes, three-state |

| Drive:  | 48 mA            |

These are the VMEbus low-order data lines.

#### A7-A1

| Input:  | Yes              |

|---------|------------------|

| Output: | Yes, three-state |

| Drive   | 48 mA            |

These are the VMEbus low-order address lines.

#### AS\*

| Input: | Yes             |

|--------|-----------------|

| Output | Yes, rescinding |

| Drive: | 64 mA           |

This is the VMEbus Address Strobe signal.

#### DS1\*-DS0\*

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 64 mA           |

These are the VMEbus Data Strobe signals.

#### DTACK\*

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 48 mA           |

This is the VMEbus Data-Transfer-Acknowledge signal.

#### BERR\*

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 48 mA           |

This is the VMEbus Bus-Error signal.

#### WRITE\*

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 48 mA           |

This is the VMEbus Data-Direction signal.

#### LWORD\*

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 48 mA           |

This is the VMEbus Longword signal.

#### AM5-AM0

| Input:  | Yes              |

|---------|------------------|

| Output: | Yes, three-state |

| Drive:  | 48 mA            |

These are the VMEbus Address-Modifier signals.

#### IACK\*

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 48 mA           |

This is the VMEbus Interrupt Acknowledge signal.

#### IACKIN\*

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

This is the VMEbus daisy-chained Interrupt-Acknowledge-In signal.

#### IACKOUT\*

| No   |

|------|

| Yes  |

| 8 mA |

|      |

This is the VMEbus daisy-chained Interrupt-Acknowledge-Out signal.

#### IRQ7\* - IRQ1\*

| Input:  | Yes                 |

|---------|---------------------|

| Output: | Yes, open collector |

| Drive:  | 48 mA               |

These are the VMEbus Interrupt request signals.

# 1.2.2 Local Signals

These signals define the local bus structure of the VIC068A. They are modeled after Motorola 68K signals.

#### LD7-LD0

| Input:  | Yes              |

|---------|------------------|

| Output: | Yes, three-state |

| Drive:  | 8 mA             |

These are the Local Data 7–0 signals. These signals are typically connected to the local processor data lines D[7:0] through an isolation buffer. VIC068A register accesses are also made through these data signals.

#### LA7–LA0

| Input:  | Yes              |

|---------|------------------|

| Output: | Yes, three-state |

| Drive:  | 8 mA             |

These are the Local Address 7–0 signals. These signals are typically connected to the local processor address lines. VIC068A registers are also addressed through these signals. When acting as the local bus master, the VIC068A drives these lines with the LAEN (active High) signal to supply the local address.

#### CS\*

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

This is the VIC068A chip select signal. This signal should be asserted whenever access to the VIC068A internal registers is required. See section 1.7.2.

#### PAS\*

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 8 mA            |

This is the physical/processor address strobe. This signal is used to qualify an incoming address when performing VMEbus master operations or register operations. This signal is driven when performing slave transfers, DRAM refresh, slave block transfers and block transfers with local DMA. When acting as an output, the minimum assertion and negation timing for this signal is configured by the Local Bus Timing register (LBTR).

#### DS\*

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 8 mA            |

This is the local data strobe. This signal is used to qualify incoming data when performing VMEbus master operations or register operations. This signal is driven when performing slave transfers, DRAM refresh, slave block transfers, and block transfers with local DMA. When

acting as an output, the minimum assertion and negation timing for this signal is directed by the Local Bus Timing register (LBTR).

#### DSACK1\*, DSACK0\*

| Input:  | Yes              |

|---------|------------------|

| Output: | Yes, three-state |

| Drive:  | 8 mA             |

These are the local data-size-acknowledge signals. One or both of these signals should be asserted to the VIC068A whenever the VIC068A is local bus master to acknowledge the successful completion of each cycle of a slave transfer, slave block transfer, or block transfers with local DMA. The VIC068A asserts one or both of these signals to acknowledge the successful completion of a VMEbus master operation (after receiving the VMEbus DTACK\* signal). The following should be noted about the DSACK1/0\* signals:

- The VIC068A asserts a 16-bit DSACKi\* code when the WORD\* signal is asserted, indicating access to a D16 VMEbus resource is complete. See section 1.5.3.

- The VIC068A treats the assertion of any DSACK1/0\* signal as a 32-bit acknowledge for slave accesses.

- The VIC068A does not directly support 16- or 8-bit local bus sizes.

- The VIC068A always asserts both DSACK\*s for register accesses as well as for interrupt acknowledge cycles.

#### LBERR\*

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 8 mA            |

This is the local bus-error signal. This signal should be asserted to the VIC068A whenever the VIC068A is local bus master to acknowledge the unsuccessful completion of a slave transfer, slave block transfer, and block transfers with local DMA, in which case the VIC068A asserts the VMEbus BERR\* signal. The VIC068A asserts this signal to acknowledge the unsuccessful completion of a VMEbus master operation (after receiving the VMEbus BERR\* signal).

During deadlocks, LBERR\* may also be configured to assert with the HALT\* signal to initiate a Motorola 68K retry sequence. LBERR\* may also be configured to assert without HALT\* for RMC cycle deadlocks. See section 1.5.7.

#### **RESET\***

| Input:  | No               |

|---------|------------------|

| Output: | Yes, three-state |

| Drive:  | 8 mA             |

This is the local reset indication signal. This signal is asserted whenever the VIC068A is in a reset state. An internal, global, or system reset causes the VIC068A to start its 200-ms reset timer and to assert RESET\* for a minimum of one reset timer period. If a reset condition is

present at the end of the reset timer period (200 ms), the reset timer is retriggered for an additional 200-ms period and continues to assert RESET\*. This reset timer retrigger operation repeats until the reset condition is not present when the reset timer period ends. Once the VIC068A stops driving RESET\* Low, this pin is three-stated. Since the VIC068A does not actively drive RESET\* to its inactive state, a pull-up resistor should be used on this signal to ensure that any device monitoring the RESET\* signal will see its removal. See section 12.1.

#### HALT\*

| Input:  | Yes              |

|---------|------------------|

| Output: | Yes, three-state |

| Drive:  | 8 mA             |

This is the "halted" condition indication signal. This signal, along with RESET\*, is asserted during reset conditions. An internal, global, or system reset causes the VIC068A to assert HALT\* for a minimum of 200 ms. If the reset condition continues for longer than 200 ms, HALT\* begins additional 200-ms timeouts until all reset conditions are cleared. Assertion of HALT\* for more than 6  $\mu$ s by anything other than the VIC068A causes the VIC068A to assert SYSFAIL\*.

HALT\* may be configured to assert during deadlock conditions along with LBERR\* to initiate a retry sequence for Motorola 68K processors. See section 1.5.7.

#### R/W\*

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 8 mA            |

This is the local data direction signal. This signal is driven while the VIC068A is a local bus master to indicate local data direction. As an input, R/W\* indicates data direction for VMEbus master cycles. In this case, the VMEbus signal WRITE\* reflects the value of R/W\*. A Low condition indicates a write operation.

#### FC2, FC1

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 8 mA            |

These are the local function code signals. These signals identify the type of local cycle in progress. As inputs, they should reflect the type of operations in terms of User/Supervisory Code/Data. They may be connected directly to the Motorola FC2/1 outputs for 68000-30 processors. For the 68040, the FC2/1 inputs may be connected to the TM2/1 outputs, respectively. Additional qualification may be required for 68040 applications because the 68040 uses previously reserved/unused function codes.

| FC2 | FC1 | Description        |

|-----|-----|--------------------|

| 0   | 0   | User Data          |

| 0   | 1   | User Program       |

| 1   | 0   | Supervisor Data    |

| 1   | 1   | Supervisor Program |

|     |     |                    |

As outputs, the VIC068A drives these signals whenever it is local bus master to indicate the type of local cycle the VIC068A is performing. See section 1.6.3.

| FC2 | FC1 | Description          |

|-----|-----|----------------------|

| 0   | 0   | Slave Block Transfer |

| 0   | 1   | Local DMA            |

| 1   | 0   | Slave Access         |

| 1   | 1   | DRAM Refresh         |

#### SIZ1, SIZ0

| Input:  | Yes             |

|---------|-----------------|

| Output: | Yes, rescinding |

| Drive:  | 8 mA            |

These are the local data size signals. As inputs, these signals identify the width of the VMEbus data to be transferred. The SIZi signals should not be used to indicate the physical port size of the slave device (D16, or D32). This is done with the WORD\* signal. As outputs, they are driven by the VIC068A as local bus master to identify the width of the incoming data. See sections 1.5.9, 1.6.5, and 1.6.8.

| SIZ1 | SIZ0 | Data Width |

|------|------|------------|

| 0    | 0    | Longword   |

| 0    | 1    | Byte       |

| 1    | 0    | Word       |

| 1    | 1    | 3-Byte     |

#### LBR\*

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the local bus request signal. This signal is asserted whenever the VIC068A desires mastership of the local bus. This signal remains asserted for the entire bus tenure.

Local bus mastership is requested when each of the following operations is desired:

- Standard slave accesses

- Slave block transactions

- Block transfers with local DMA

- DRAM refresh

#### LBG\*

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

This is the local bus grant signal. The signal is asserted by local resources in response to the LBR\* signal. The VIC068A does not incorporate a local-bus-grant-acknowledge protocol, so the LBG\* signal must remain asserted for the duration of LBR\*.

#### MWB\*

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

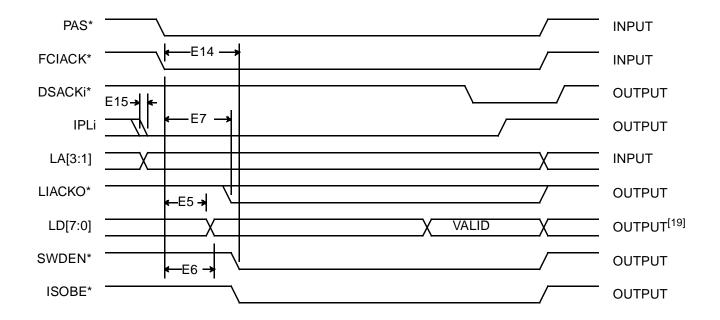

This is the "Module-Wants-Bus" signal. This signal is asserted by local resources to begin a VMEbus transaction. When qualified by the PAS\* signal, the VIC068A asserts the VMEbus BRi\* signal. This signal is usually asserted by local-to-VMEbus address decoders.

#### FCIACK\*

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

This is the local interrupt acknowledge signal. This signal is asserted (qualified by DS\*) to acknowledge all VIC068A-generated local interrupts. See Chapter 1.9.

#### SLSEL1\*, SLSEL0\*

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

These are the slave select signals. These signals indicate the VIC068A has been selected to perform a VMEbus slave operation. When qualified by AS\* and valid AM codes, the VIC068A requests the local bus to perform the slave cycle. These signals are usually asserted by VMEbus-to-local-address decoders.

The SLSEL1/0 signals may be used independently of each other to provide unique slave characteristics as defined by the Slave Select Control registers. See section 1.6.1.

#### ICFSEL\*

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

This is the Interprocessor Communication Facility (ICF) Select signal. This signal indicates that the ICF functions of the VIC068A have been selected. These include the ICF registers and the ICF switch interrupts. This signal is qualified with AS\* and A16 AM codes (A16/ Supervisory for global switches). See Chapter 1.8.

#### ASIZ1, ASIZ0

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

These are the VMEbus address size signals. These signals are driven to indicate the VMEbus address size of master VMEbus transfers. The address size information is issued on the VMEbus AM codes. User-defined address spaces may be accessed by asserting both ASIZ1/ 0 signals. In this case, the AM codes are issued according to the programming of the Address Modifier Source register.

| ASIZ1 | ASIZ0 | Address Size |

|-------|-------|--------------|

| 0     | 0     | User defined |

| 0     | 1     | A32          |

| 1     | 0     | A16          |

| 1     | 1     | A24          |

#### WORD\*

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

This is the VMEbus data width control signal. This signal, when asserted, indicates the requested VMEbus transaction should be treated as a D16 data path. When deasserted, the VMEbus data path is assumed to be D32. This signal should be used to configure VMEbus data width for master cycles only. Data width for slave cycles is configured in the Slave Select Control registers.

This signal is also used to configure the data width for block transfers with local DMA. When this signal is asserted during the block transfer initiation cycle, the block transfer is assumed to be a D16 block transfer.

This signal may be changed dynamically for individual transfers, or strapped Low at powerup for permanent D16 operation. If WORD\* is strapped Low at power-up, the VIC068A is configured as a D16 slave, independent of the slave configuration in the Slave Select Control registers.

WORD\* should not be used to indicate data size (i.e., byte, word, or longword) only VMEbus data port size (i.e., D16 or D32).

#### **BLT**\*

| Input:  | Yes                 |

|---------|---------------------|

| Output: | Yes, open collector |

| Drive:  | 8 mA                |

This is the block transfer with local DMA indication signal. This signal is used to indicate that a block transfer with local DMA is in progress. This signal remains asserted for the entire block transfer including interleave periods with the exception of local page boundary cross-

ings. BLT\* toggles during local boundary crossings to increment the external LA[+:8] counters. See section 1.10.1.1.

#### DEDLK\*

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the deadlock indication signal. This signal indicates that a deadlock condition has occurred. This signal should be used by local logic to remove its request for the VMEbus. DEDLK\* remains asserted until the slave transaction is complete.

DEDLK\* is also asserted to indicate that a VMEbus master cycle is being attempted during the interleave period of a block transfer with local DMA, without the dual-path feature enabled. In this case, DEDLK\* is asserted while MWB\* is asserted. If, during the interleave period, the MWB\* signal is asserted after the VMEbus has been re-obtained, the VIC068A will assert DEDLK\* for the duration of the burst. See section 1.5.7.

#### IPL2, IPL1, IPL0

| Inputs: | IPL0 only           |

|---------|---------------------|

| Output: | Yes, open collector |

| Drive:  | 8 mA                |

These are the local priority encoded interrupt request signals. These signals are asserted to interrupt the local processor. All local VIC068A interrupts are issued with these signals. These signals emulate the Motorola 68K interrupt mechanism. The assertion of one or more of these signals indicates a single interrupt with a priority given by the negative-logic value of the IPLi signals. Level 7 is the highest priority. These signals are open collector to allow the wire-ORing of multiple interrupt sources. See Chapter 1.9.

During the assertion of IRESET\*, IPL0 becomes an input. If IPL0 is asserted at this time, a global reset is performed. See section 1.11.1.2.

#### LIRQ7\*-LIRQ1\*

| Input:  | Yes                |

|---------|--------------------|

| Output: | LIRQ2* only        |

| Drive:  | 8 mA (LIRQ2* only) |

These are the local interrupt request signals. These signals serve as local interrupt request signals for the VIC068A. If enabled to handle the particular local interrupt, the VIC068A issues a processor interrupt with the IPLi signals at the assertion of a LIRQi<sup>\*</sup>. Configuration of local interrupts is allowed through the Local Interrupt Configuration registers. See section 1.9.3.

LIRQ2\* may also be configured to issue periodic "heartbeat" interrupts at user-defined intervals. See section 1.9.6.

#### LIACKO\*

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the "autovectoring" indication signal. This signal is asserted when the VIC068A is configured to allow the interrupting device to place its status/ID vector on the local data bus in response to a VIC068A-handled local interrupt acknowledge. This signal may be used to signal an autovectored interrupt acknowledge cycle for 68020/30/40 processors. This signal may be connected directly to the AVEC signal for these processors. See section 1.9.3.

#### **IRESET\***

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

This is the internal reset signal. This signal is used to issue both internal and global resets to the VIC068A. If asserted with IPL0\*, a global reset is performed. If asserted without IPL0\*, an internal reset is performed. All internal state machines and selected register bits are reset during the assertion of IRESET\*. HALT\* and RESET\* are both asserted during the assertion of IRESET\*. If configured as system controller, SYSRESET\* is also asserted during the assertion of IRESET\*. See Chapter 1.12.

#### SCON\*

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

This is the system controller enabling signal. This signal is used to configure the VIC068A as VMEbus system controller. This signal must be strapped Low at power-up and remain Low for VIC068A to reliably assume the role of VMEbus system controller, otherwise this signal should be tied High. See Chapter 1.4.

#### CLK64M

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

This is the VIC068A master clock input. This 64-MHz clock input is used to clock internal arbitration, timing, and delay functions within the VIC068A. Clock speeds as low as 1 MHz may be used, but all synchronous delays as well as VMEbus and local timing are affected.

#### RMC\*

| Input:  | Yes  |

|---------|------|

| Output: | No   |

| Drive:  | None |

This is the Read-Modify-Write control signal. This signal may be used to control indivisible cycles on the VMEbus. Its operation is controlled with the Interface Configuration register, bits 5–7. See section 1.5.6.

## 1.2.3 Buffer Control Signals

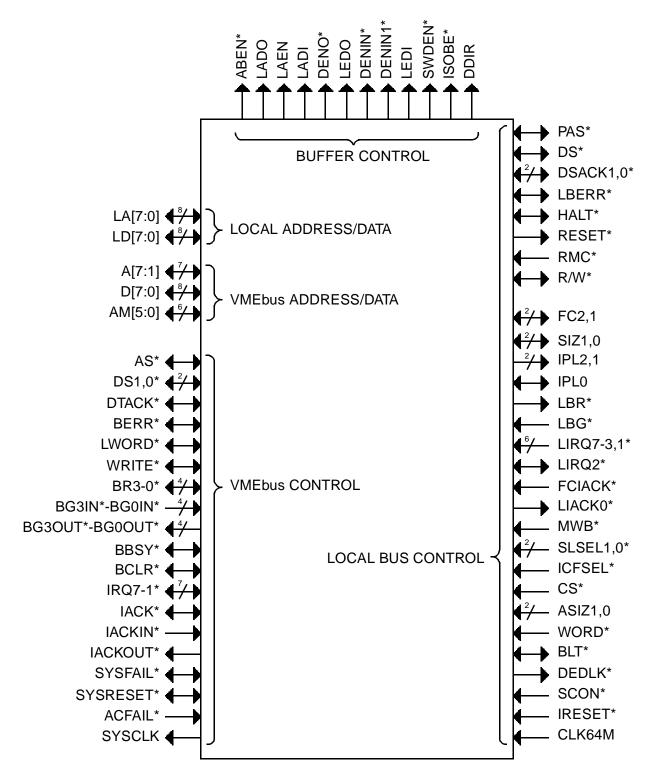

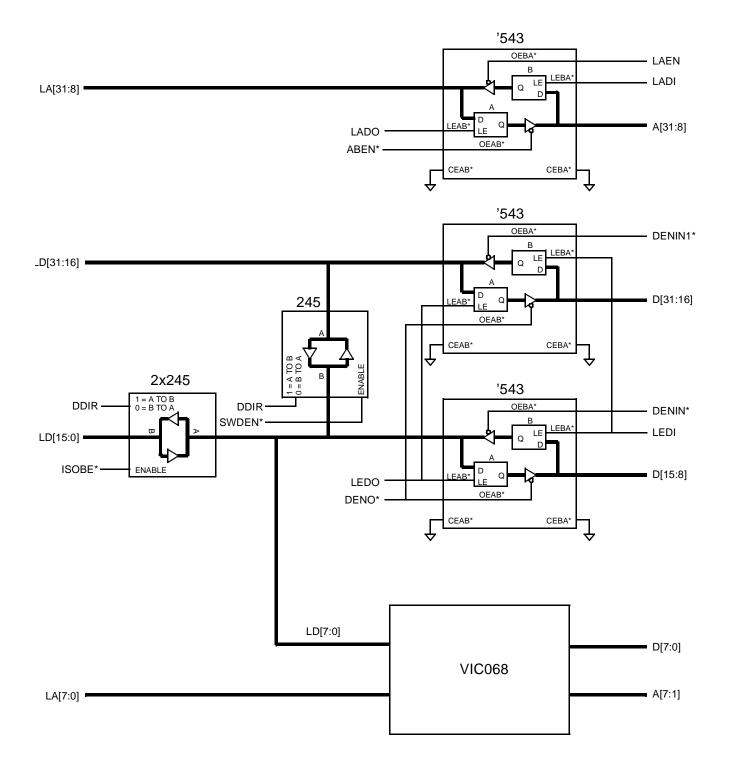

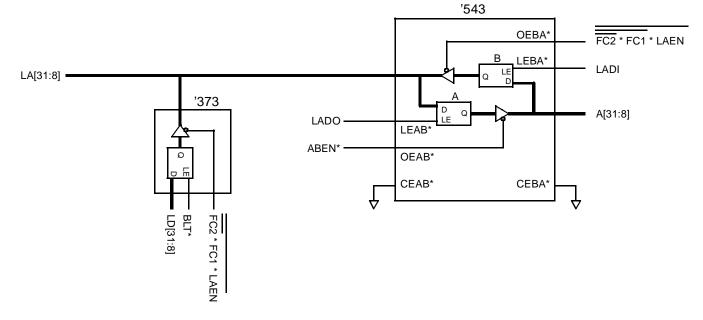

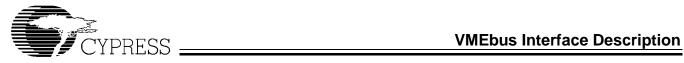

These signals control the latching and enabling of the external address and data latches and buffers. For block transfers with local DMA, some of these signals are used to control the counting and enabling of external counters required for page boundary crossing. These signals can be directly connected to Cypress CY7C964s which simplifies the VME interface by replacing 8 bit wide external latches, buffers and counters with one CY7C964. A complete 32 bit wide VME interface would consist of the VIC068A and three CY7C964s. See Section 4, The CY7C964 Bus Interface Logic Circuit, for more information.

For simple VME designs (i.e. single-cycle only) the VIC068A can directly drive the control lines of discrete buffers and latches (*Figure 1-4*).

*Figure 1-4* shows typical connections between the external latches/buffers and the buffer control signals.

#### ABEN\*

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the VMEbus Address Bus ENable signal. This signal is used to enable the external VMEbus address drivers for VMEbus master operations. It is typically connected to the OEAB input of a '543 address transceiver.

#### LAEN

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the Local Address ENable signal. This signal is used to enable the external local address drivers for slave accesses. It is typically connected to the OEBA input of a '543 address transceiver through an inverter.

Note that this signal is an active-High signal.

#### Figure 1-4. VIC068A Control Signals for Shared Memory Implementation

#### LADO

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

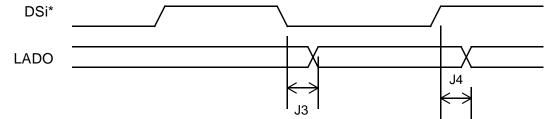

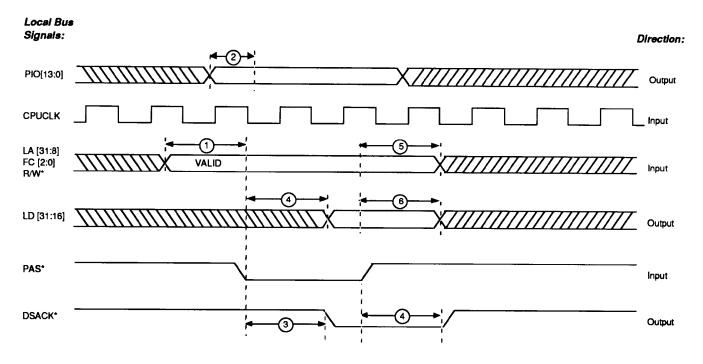

This is the Latch ADdress Out signal. This signal is used to latch the outgoing VMEbus address for VMEbus master operations. When this signal is asserted (High), it is assumed that the latches are in a latched state. When deasserted, the latches should be in a flow-through state. This allows direct connection to the '543 address driver LEAB input. LADO is very important for proper operation of master write posting and block transfers with interleave periods. For these operations, the VIC068A may use LADO in combination with LADI and ABEN\* to temporarily store the contents of a VMEbus address during intervening slave accesses.

#### LADI

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the Latch ADdress In signal. This signal is used to latch the incoming VMEbus address for slave accesses. When this signal is asserted (High), it is assumed that the latches are in a latched state. When deasserted, the latches should be in a flow-through state. This allows direct connection to the '543 address driver LEBA input. LADI is used in conjunction with LADO to temporarily store outgoing VMEbus master transaction addresses during intervening slave accesses.

#### DENO\*

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the Data ENable Out signal. This signal enables data onto the VMEbus data bus for master write and slave read cycles. This signal is typically connected to the OEAB input of the '543 data latches.

**DENIN\*** (formerly LWDENIN\*)

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the Lower Word Data ENable IN signal. This signal enables data onto the lower word of the local data bus LD[15:8] for master read and slave write cycles. This signal is typically connected to the OEBA input of the '543 lower data latch.

#### **DENIN1\*** (formerly UWDENIN\*)

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the Upper Word Data ENable IN signal. This signal enables data onto the upper word of the local data bus LD[31:16] for master read and slave write cycles. This signal is typically connected to the OEBA input of the upper '543 data latches.

#### LEDO

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

The Latch Enable Data Out signal. This signal latches the outgoing VMEbus data for master write and slave read cycles. When this signal is asserted (High), it is assumed that the latches are in a latched state. When deasserted, the latches should be in a flow-through state. This allows direct connection to the '543 address driver LEAB input. This signal may be used in conjunction with LEDI to temporarily store outgoing master write post data (data switchback).

#### LEDI

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the Latch Enable Data In signal. This signal latches the incoming VMEbus data for master read and slave write cycles. When this signal is asserted (High), it is assumed that the latches are in a latched state. When deasserted, the latches should be in a flow-through state. This allows direct connection to the '543 address driver LEBA input. This signal may be used in conjunction with LEDO to temporarily store outgoing master write post data.

#### **ISOBE\***

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the ISOlation Buffer Enable signal. This signal, along with the SWDEN\* signal, steers data from LD[31:16] to/from LD[15:0], which is referred to in this document as byte-lane switching. This signal is typically connected to the EN input of the '245 isolation buffer.

#### SWDEN\*

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the SWap Data ENable signal. This signal, along with the ISOBE\* signal, provides byte-lane switching. It provides for swapping LD[31:16] to LD[15:0]. This signal is typically connected to the EN input of the '245 swap buffer.

#### DDIR

| Input:  | No   |

|---------|------|

| Output: | Yes  |

| Drive:  | 8 mA |

This is the Data DIRection signal. This signal provides the data direction (i.e., read/write) information to the isolation and swap buffers. When asserted, buffers should be configured in the local-to-VMEbus (A-to-B) direction. This signal is typically connected to the DIR input of the '245 isolation/swap buffers.

# **1.3** Overview of the VIC068A

The VIC068A provides an economical and convenient means to interface between a local CPU bus and the VMEbus. The local bus interface of the VIC068A emulates Motorola's family of 32-bit CISC processor interfaces (68K). Other processors can easily be adapted to interface to the VIC068A with appropriate logic. All of the following items are discussed in further detail in later sections of this manual.

### 1.3.1 Resetting the VIC068A

The VIC068A can be reset by any of three distinct reset conditions.

- Internal Reset. This reset is the most common means of resetting the VIC068A. It resets most register values and all mechanisms within the device. This reset is usually issued as a push-button reset.

- System Reset. This reset provides a means of resetting the VIC068A through the VMEbus backplane. The VIC068A may also signal a SYSRESET\* by writing a configuration register.

- Global Reset. This is the most complete reset of the VIC068A. This resets all of the VIC068A's configuration registers. This reset should be used with caution since SY-SCLK is not driven and the BG\*/IACK\* daisy-chains are disabled while a global reset is in progress (while it is system controller). This is usually issued as a power-up reset.

All three reset options are implemented in a different manner and have different effects on the VIC068A configuration registers. See section 1.11.1.

# 1.3.2 The VIC068A VMEbus System Controller

The VIC068A is capable of operating as the VMEbus system controller. It provides VMEbus arbitration functions including:

- priority (PRI), round-robin (RRS), and single-level (SGL) arbitration schemes

- driving IACK\* daisy-chain

- driving BGiOUT\* daisy-chain (all four levels)

- driving SYSCLK output

- VMEbus arbitration timeout timer

- VMEbus transfer timeout timer

The system controller functions are enabled by the SCON\* pin of the VIC068A. When strapped Low, the VIC068A functions as the VMEbus system controller. See Chapter 1.4.

## 1.3.3 VIC068A VMEbus Master Cycles

The VIC068A is capable of becoming the VMEbus master in response to a request from local resources. In this situation, the local resource requests that a VMEbus transfer is desired. The VIC068A then makes a request for the VMEbus. When the VMEbus is granted to the VIC068A, it then performs the transfer, acknowledges the local resource, and the cycle is complete. The VIC068A is capable of all four VMEbus request levels (see section 1.5.1). The following release modes are supported (see section 1.5.2):

- Release On Request (ROR)

- Release When Done (RWD)

- Release On Clear (ROC)

- Release under RMC\* control

- Bus Capture And Hold (BCAP).

The VIC068A supports A32, A24, and A16 as well as user-defined address spaces.

#### 1.3.3.1 Master Write-Posting

The VIC068A is capable of performing master write-posting (bus-decoupling) during both block and single-cycle transactions. In this situation, the VIC068A acknowledges the local resource immediately after the request to the VIC068A is made, thus freeing the local bus. The VIC068A latches the local data to be written and performs the VMEbus transfer without the local resource having to wait for the VMEbus. See section 1.5.5.

#### 1.3.3.2 Indivisible Cycles

Read-modify-write cycles and Indivisible Multiple-Address Cycles (IMACs) are easily performed using the VIC068A. Significant control is allowed to:

- request the VMEbus on the assertion of RMC\* independent of MWB\* (this prevents any slave access from interrupting local indivisible cycles)

- stretch the VMEbus AS\*

- make the above behaviors dependent on the local SIZi signals

See section 1.5.6.

#### 1.3.3.3 Deadlock

If a master operation is attempted when a slave operation to the same module is in progress, a deadlock has occurred. The VIC068A signals a deadlock condition by asserting the DEDLK\* signal. This should be used by the local resource requesting the VMEbus to try the transfer after the slave access has completed. See section 1.5.7.

#### 1.3.3.4 Self-Access

If the VIC068A is selected as the slave while it is VMEbus master, a self-access has occurred. The VIC068A asserts both BERR\* and LBERR\* in this situation.

BESR[2,1] also indicates when a self-access has occurred.

### 1.3.4 VIC068A VMEbus Slave Cycles

The VIC068A is capable of receiving slave accesses (see Chapter 1.6). The VIC068A contains a highly programmable environment to allow for a wide variety of slave configurations. The VIC068A allows for:

- D32 or D16 configuration

- A32, A24, A16, or user-defined address spaces

- programmable block transfer support including:

- accelerated block transfer (PAS\* held asserted)

- non-accelerated-type block transfer (toggle PAS\*)

- no support for block transfer

- programmable data acquisition delays

- programmable PAS\* and DS\* timing

- restricted slave accesses (supervisory accesses only)

When a slave access is required, the VIC068A requests the local bus. When local bus mastership is obtained, the VIC068A reads or writes the data to/from the local resource and asserts the DTACK\* signal to complete the transfer.

#### **1.3.4.1 Slave Write-Posting**

The VIC068A is capable of performing a slave write-post operation (bus-decoupling) during single cycle transactions. When enabled, the VIC068A latches the data to be written and acknowledges the VMEbus (by asserting DTACK\*) immediately thereafter. This prevents the VMEbus from having to wait for local bus access. See section 1.6.7.

### **1.3.5 Address Modifier (AM) Codes**

The VIC068A encodes and decodes the VMEbus address modifier codes. For VMEbus master accesses, the VIC068A encodes the appropriate AM codes through FCi status, ASIZi status, and the block transfer status. For slave accesses, the VIC068A decodes the AM Codes and checks the Slave Select Control registers to determine if the slave request is to be supported with regard to address spaces, supervisory accesses, and block transfers. The VIC068A also supports user-defined AM codes. That is, the VIC068A can be configured to assert and respond to user-defined AM codes. See section 1.6.1.

## 1.3.6 VIC068A VMEbus Block Transfers

The VIC068A is capable of both performing (as master) and receiving (as slave) block transfers. The master VIC068A performs a block transfer in one of two modes:

- MOVEM-type block transfer

- master block transfer with local DMA

The VMEbus specification restricts block transfers from crossing 256-byte boundaries. The VIC068A works around this problem by simply toggling the AS\* at VMEbus page boundaries. The VIC068A is also able to break the total transfer length into smaller bursts. The VIC068A allows for easy implementation of large block transfers by releasing the VMEbus and local bus between these bursts and, at the appropriate time, re-requesting the buses at a programmed time later. This in-between time is referred to as the interleave period. All of this is performed without processor/software intervention until the transfer is complete. See section 1.10.1.1.

The VIC068A contains two separate address counters for the VMEbus and the local address buses. In addition, a separate address counter is provided for slave block transfers. The VIC068A address counters are 8-bit up-counters that provide for transfers up to 256 bytes. For transfers that exceed the 256-byte limit, Cypress CY7C964s, Cypress VAC068A or external counters and latches are required.

The VIC068A allows slave accesses to occur during the interleave period. Master accesses are also allowed during interleave with programming and external logic. This is referred to as the dual-path option. See section 1.10.1.1.6.

The Cypress Semiconductor CY7C964s or VAC068A may be used in conjunction with the VIC068A to provide much of the external logic required for extended block transfer modes such as the 256-byte boundary crossing and dual path. Three CY7C964s extend the 8-bit counters in the VIC068A to support full 32-bit incrementing addresses on both the local bus and VMEbus. The CY7C964s also contain the latches required for extended address block transfers as well as those required for supporting the dual-path option. The CY7C964 enhances boards that support block transfers by greatly reducing the necessary support logic.

The Cypress Semiconductor VAC068A may also be used to provide the latching and counting of upper data and addresses also reducing necessary support logic.

#### 1.3.6.1 MOVEM Master Block Transfers

This mode of block transfer provides the simplest implementation of VMEbus block transfers. In this mode, the local resource configures the VIC068A for a MOVEM block transfer and proceeds with the consecutive-address cycles (such as a 68K MOVEM instruction). The local processor continues as the local bus master in this mode. See section 1.10.1.2.

#### **1.3.6.2 Master Block Transfers with Local DMA**

In this mode, the VIC068A becomes the local bus master and reads or writes the local data in a DMA-like fashion. This provides a much faster interface than the MOVEM block transfer, but with less control and error detection. See section 1.10.1.1.

#### 1.3.6.3 Slave Block Transfers

The process of receiving a block transfer is referred to as a slave block transfer. The VIC068A is capable of decoding the address modifier codes to determine if a slave block transfer is desired. In this mode, the VIC068A captures the VMEbus address, and latches it into internal counters. For subsequent cycles, the VIC068A increments this counter for each transfer. The local protocol for slave block transfers can be configured in a full handshake mode by toggling both PAS\* and DS\* and expecting DSACKi\* to toggle, or in an accelerated mode in which only DS\* toggles and PAS\* is asserted throughout the cycle.

The VIC068A is capable of acting as a DMA controller between two local resources. This mode is similar to that of master block transfers with local DMA except that a local I/O acts as the second source or destination.

### 1.3.7 VIC068A Interrupt Generation and Handling Facilities

The VIC068A is capable of generating and handling a seven-level prioritized interrupt scheme similar to that used by the Motorola 68K processors. These interrupts may be the result of the seven VMEbus interrupts, seven local interrupts, five VIC068A error/status interrupts, and eight interprocessor communication interrupts.

The VIC068A can be configured as an interrupt handler for any of the seven VMEbus interrupts. The VIC068A can generate the seven VMEbus interrupts as well as supplying a user-defined status/ID vector. The local priority level (IPL) for VMEbus interrupts is programmable. When configured as the system controller, the VIC068A drives the VME-bus IACK daisy-chain.

The following characteristics of local interrupts may be configured in VIC068A registers:

- user-defined local Interrupt Priority Level (IPL)

- option for VIC068A to provide the status/ID vector

- edge or level sensitivity

- polarity (rising/falling edge, active High/Low)

The VIC068A is also capable of generating local interrupts on certain error or status conditions. These include:

- ACFAIL\* asserted

- SYSFAIL\* asserted

- failed master write-post (BERR\* asserted)

- local DMA completion for block transfers

- arbitration timeout

- VMEbus interrupter interrupt

The VIC068A can also issue interrupts by setting a module or global switch in the interprocessor communication facilities (mailbox interrupts).

# **1.3.8 Interprocessor Communication Facilities**

The VIC068A includes interprocessor registers and switches that can be written and read through VMEbus accesses. These are the only registers that are directly accessible from the VMEbus. Included in the interprocessor communication facilities are:

- four general-purpose 8-bit registers

- four module switches

- four global switches

- VIC068A version/revision register (read-only)

- VIC068A Reset/Halt condition (read-only)

- VIC068A interprocessor communication register semaphores

When set through a VMEbus access, the switches can interrupt a local resource. The VIC068A includes module switches that are intended for a single module, and global switches that are intended to be used as a broadcast.

# 1.4 System Controller Operations

The VIC068A is able to assume the system controller functions (also known as slot 1 functions) by strapping the SCON\* signal Low. For reliable operation, the SCON\* signal must remain asserted for the duration of operation. As the system controller, the VIC068A performs the following functions:

- priority, round robin, or single-level arbitration

- driving IACK\* daisy-chain

- driving BGiOUT\* daisy-chain (all four levels)

- driving SYSCLK output

- driving SYSRESET\* output

- driving BCLR\*

- VMEbus arbitration timeout timer

The following VIC068A registers are used as the system controller:

- Transfer Timeout Register (TTR), bits 5-7

- Arbiter/Requestor Control Register (ARCR), bit 7

- Error Group Interrupt Control Register (EGICR), bit 5

# 1.4.1 VMEbus Arbitration

The arbitration scheme is programmed by writing ARCR[7]. In PRI (priority) mode, BR3<sup>\*</sup> has the highest priority and BR0<sup>\*</sup> has the lowest. Higher priority bus requests will be handled before lower priority bus requests when in PRI mode. In the RRS (round robin) scheme, arbitration priority is assigned on a rotating basis. When the bus is granted to a requester on bus request line BR[n]<sup>\*</sup>, then the highest priority for the next arbitration is assigned to bus request line BR[n–1]<sup>\*</sup> (or BR3<sup>\*</sup> if previous level was BR0<sup>\*</sup>). Single-level arbitration is obtained by programming the VIC068A for PRI and setting all requestors to the same level.

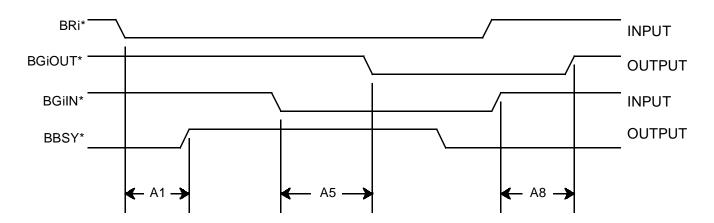

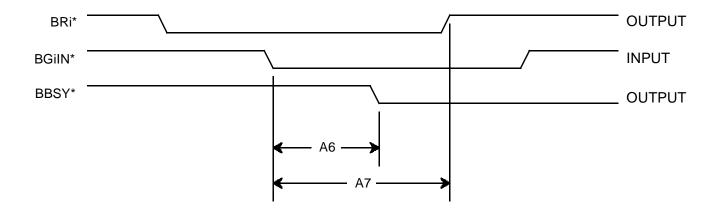

When the VIC068A is system controller, it senses the state of the BRi\* inputs. One of the four BGiOUT\* signals is asserted, corresponding to the highest pending request level during that arbitration cycle. If the VIC068A, as system controller, has a BRi\* pending along with another potential master at the same request level, the VIC068A does not assert the BGiOUT\* for itself.

An arbitration cycle begins with the deassertion of the BBSY\* signal. The VIC068A waits a minimum of 3T after the deassertion of BBSY\* before asserting the BGiOUT\* signal. The VIC068A deasserts the BGiOUT\* signal when the BBSY\* is again reasserted.

The VIC068A asserts the BCLR\* signal as part of its arbiter function when it senses a request at a higher priority than the level of the current VMEbus master. This may occur when the VIC068A is enabled for both PRI and RRS arbitration schemes. In either case, the VIC068A deasserts BCLR\* when BBSY\* is deasserted.

In systems containing many contending VMEbus masters, the use of RRS arbitration and fair requests is strongly recommended to prevent excessive bus latency to some of the VMEbus masters. To allocate an unequal share of bus bandwidth to a particular master, assign that master to a BR\* level shared with fewer masters.

### **1.4.2 The VMEbus Arbitration Timeout Timer**

After the VIC068A has asserted the BGiOUT\* signal, the VIC068A system controller monitors how long the grant is active. Failure to assert BBSY\* within 8 ms causes the VIC068A to issue its own BBSY\* for the VMEbus-required 90 ns. The EGICR can be used to generate an interrupt for a VMEbus arbitration timeout condition. This timeout feature may not be disabled. See section 1.9.5.

### **1.4.3 The VMEbus Transfer Timeout Timer**

The VIC068A contains a VMEbus transfer timeout timer. When the VIC068A is configured as the system controller, and the transfer timeout timer is enabled, the VIC068A starts this timer at the assertion of a DSi<sup>\*</sup>. If the timer expires before the assertion of DTACK<sup>\*</sup> or BERR<sup>\*</sup>, BERR<sup>\*</sup> is asserted by the system controller. BERR<sup>\*</sup> remains asserted until the DSi<sup>\*</sup>s are removed. The timer is configured in the TTR[7:5]. BESR[4] is set when this timeout condition occurs.

### 1.4.4 The BGi Daisy-Chain Driver

The VIC068A, as system controller, drives the BGiOUT\* daisy-chain in response to VMEbus requests. When the VIC068A is the system controller, the BGiIN\* lines are inactive, but need to be pulled High externally at the VIC068A (4.7–10K $\Omega$ ).

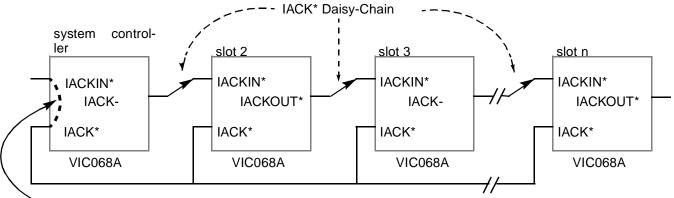

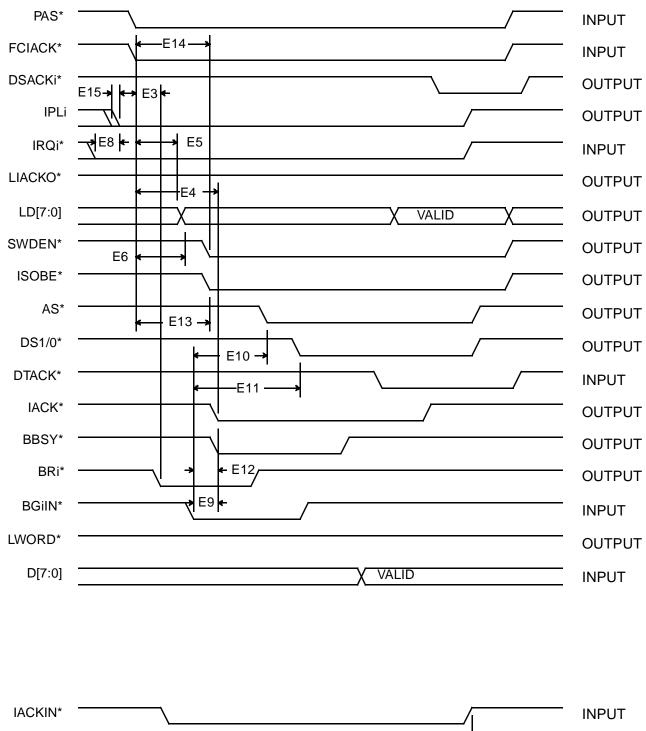

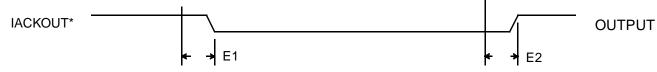

# 1.4.5 The IACK\* Daisy-Chain Driver

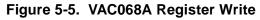

The VIC068A, as system controller, is the first device to drive the IACK\* daisy chain (*Figure 1-5*). When the VIC068A is performing duties as the system controller, the IACK\* input is internally tied to the IACKIN\* input. When a VMEbus interrupt handler drives IACK\* Low

on the VMEbus, the system controller VIC068A will see this as a Low on its IACK\* input and will react just like a VIC068A located elsewhere on the VMEbus would when its IACKIN\* is driven Low. See section 1.9.2.

logically tied together internally

Figure 1-5. IACK\* Daisy-Chain

# **1.5** VIC068A VMEbus Master Operations

The transfer of data is initiated by a VMEbus master module. The master module controls the type of transfer (read, write, interrupt acknowledge, etc.) and provides the address and address modifiers for the transfer. The timing of the start of the transfer is also controlled by the master.

The following VIC068A registers are used for master operations (block transfer registers not included):

- Transfer Timeout Register (TTR), bits 1, 2-4

- Interface Configuration Register (ICR), bits 1–7

- Arbiter/Requester Configuration Register (ARCR), bits 0–3, 5, 6

- Address Modifier Source Register (AMSR)

- Bus Error Status Register (BESR), bits 0–3

- Slave Select 1 Control Register 0 (SS1CR0), bit 6

- Release Control Register (RCR), bits 6–7

See Chapter 1.12 for descriptions of these registers.

### 1.5.1 VMEbus Requests

There are many types of cycles in which the VIC068A requests the VMEbus. These include:

- SINGLE-cycle data transfer requests (SINGLE)

- status/ID fetches for Interrupt ACKnowledge cycles (IACK)

- Indivisible Single-Address Cycles (ISAC) such as read-modify-write cycles

- Indivisible Multiple-Address Cycles (IMAC)

- Block Transfer Requests (BLT)

- VMEBus Capture And Hold (BCAP) requests

The actual assertion of the BRi\* signals are made in response to the following signals:

- assertion of MWB\* qualified by PAS\* for single-cycle and block-transfer accesses

- assertion of FCIACK\* qualified by PAS\* for VMEbus interrupt acknowledge cycles

- assertion of RMC\* qualified by PAS\* (when the ICR is appropriately programmed) for ISAC and IMAC cycles

- setting the BCAP bits in the ICR for BCAP and IMAC cycles

The request level is set in ARCR[6:5]. The default level is BR3\*.

## 1.5.2 Release Modes

The VIC068A supports the four VMEbus release modes:

- Release On Request (ROR)

- Release When Done (RWD)

- Release On Clear (ROC)

- VMEbus Capture And Hold (BCAP)

In addition to these, the VIC068A also allows an extension of the above items to provide for the use of the RMC\* signal. This is referred to as Release Under RMC\* Control. These modes are selected by writing RCR[7:6]. The Release Under RMC\* Control mode is programmed by setting ICR[5].

#### 1.5.2.1 Release On Request (ROR)

In this release mode, the VIC068A deasserts BBSY\* when a BRi\* is asserted by another VMEbus module and the VIC068A has no need for the VMEbus. The VIC068A does not assert the ABEN\* signal if there is no data transfer in progress and the VIC068A is currently the VMEbus master.

#### 1.5.2.2 Release When Done (RWD)

In this mode, the VIC068A deasserts the BBSY\* signal as soon as the following conditions occur:

- 1. BBSY\* has been asserted by the VIC068A for a minimum of 90 ns

- 2. AS\* has been deasserted by the VIC068A

- 3. The VIC068A has no further need for the VMEbus (the VIC068A has not asserted BRi\* for the last 2T)

- 4. BGiIN\* is not asserted to the VIC068A

#### 1.5.2.3 Release On Clear (ROC)

In this mode, the VIC068A continues to assert BBSY\* until the BCLR\* signal is asserted by the system controller.

#### 1.5.2.4 VMEbus Capture and Hold (BCAP)

In this mode, the VIC068A asserts BBSY\* continuously for as long as the BCAP mode is selected. The release of BBSY\* occurs by programming the release control bits to another release mode. If RWD is selected, BBSY\* is released immediately. If ROR is selected, BBSY\* is released at a pending VMEbus request. The VIC068A deasserts BBSY\* on the assertion

of BCLR\* if ROC is selected. Do not enter the BCAP mode if the VIC068A is currently the VMEbus master.

#### 1.5.2.5 Release Under RMC\* Control

In this mode, the VIC068A both requests and holds the VMEbus under control of the RMC\* signal. When appropriately programmed by setting ICR[5], the assertion of RMC\* and PAS\* causes the VIC068A to request the VMEbus, accept the BGiIN\*, and assert BBSY\*. The deassertion of RMC\* allows the deassertion of BBSY\* based upon the release mode programmed.

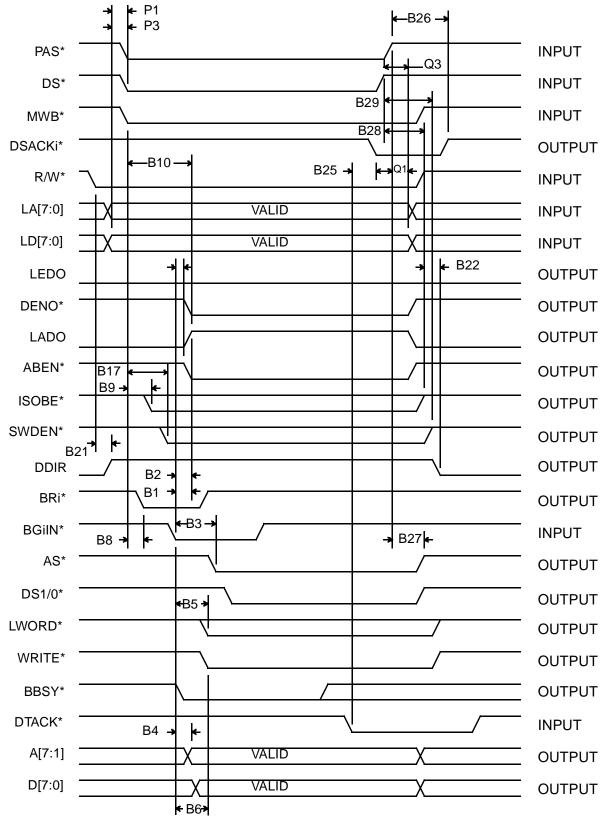

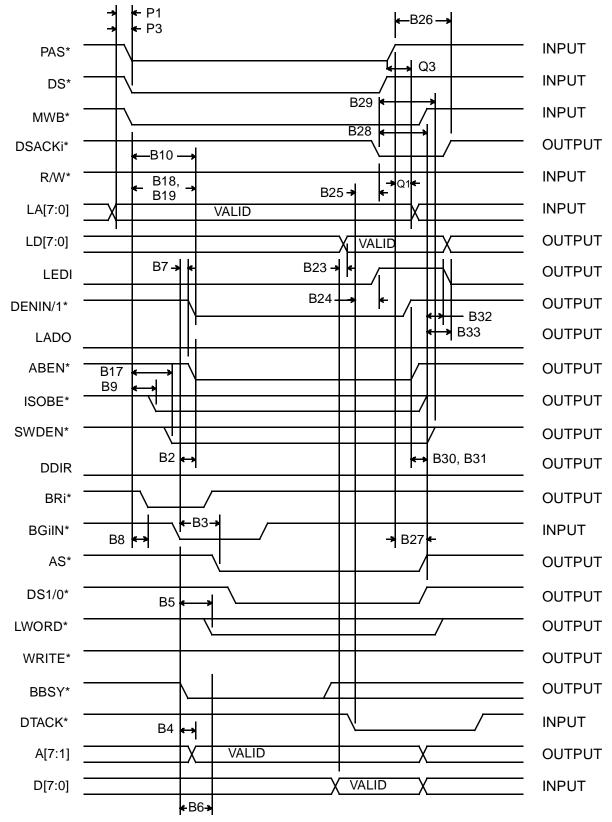

### 1.5.3 VIC068A VMEbus Master Write Cycle

If the VIC068A is not the current VMEbus master, the VIC068A bids for access to the VMEbus when it receives the MWB\* and PAS\* signals asserted. When all of the following conditions occur:

- 1. AS\* is deasserted from the previous cycle

- 2. DTACK\* and BERR\* are deasserted

- 3. the BGilN\* has been received

- 4. all appropriate metastability settling delays have elapsed

the VIC068A drives the D[7:0] data buffers onto the VMEbus and asserts DENO\*, which should be used to enable the remaining data buffers. At the same time, the VIC068A enables the A[7:0] address lines onto the VMEbus in addition to asserting the ABEN\* signal to drive the remaining VMEbus address lines. The VIC068A also drives AM[5:0], WRITE\*, and LWORD\* as required. At this time, the VIC068A initiates an internal delay to insure appropriate address set-up time before the assertion of the AS\*. After AS\* is asserted, the VIC068A latches the LA[7:0] and asserts the LADO signal, which should be used to latch the remaining local address lines.

After the AS\* signal has been asserted, the VIC068A initiates an internal delay to assert the data strobes (DSi\*). When this delay has elapsed, the VIC068A asserts the appropriate data strobes as determined by the size and alignment of the transfer. The DSi\* signals remain asserted until either DTACK\* or BERR\* have been asserted to the VIC068A. If DTACK\* is asserted, the VIC068A asserts the DSACKi\* signals according to the port size. That is, if the WORD\* signal was deasserted, the VIC068A acknowledges this D32 operation by asserting both the DSACK0\* and DSACK1\* signals. If the WORD\* signal was asserted, the VIC068A acknowledges this D16 transfer by asserting only the DSACK1\* signal. For example, when performing a longword transfer to a D16 device, asserting only DSACK1\* would notify the processor that the additional word of data needs to be transferred. This is consistent with the Motorola 68K dynamic bus sizing capabilities using DSACKi\*.

When turbo mode is enabled by setting ICR[1], the VMEbus address and data set-up times are decreased by 1T.

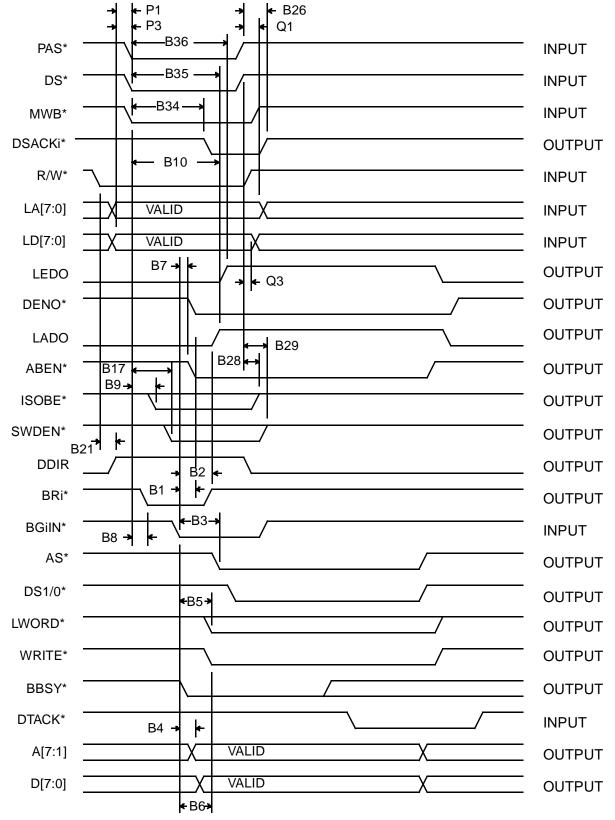

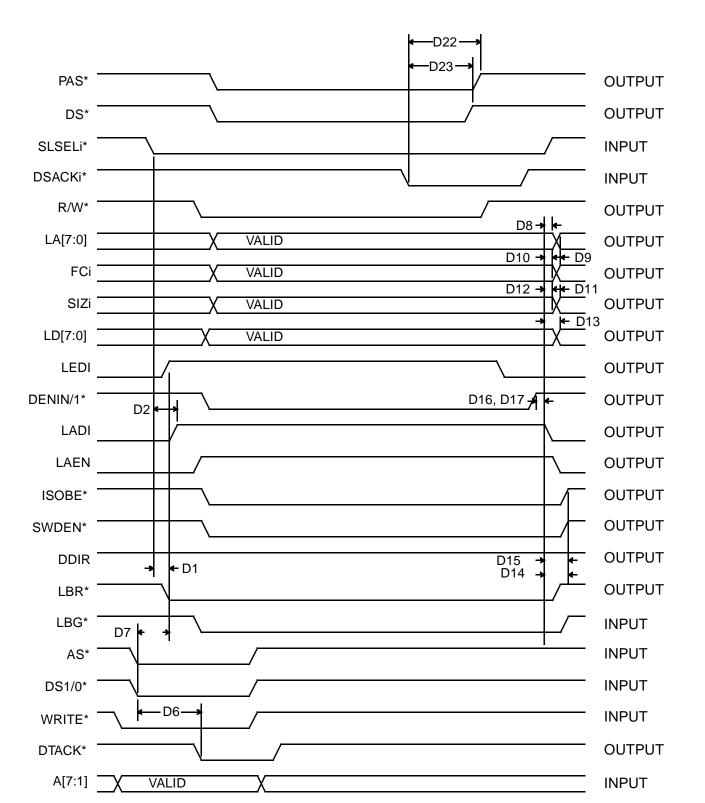

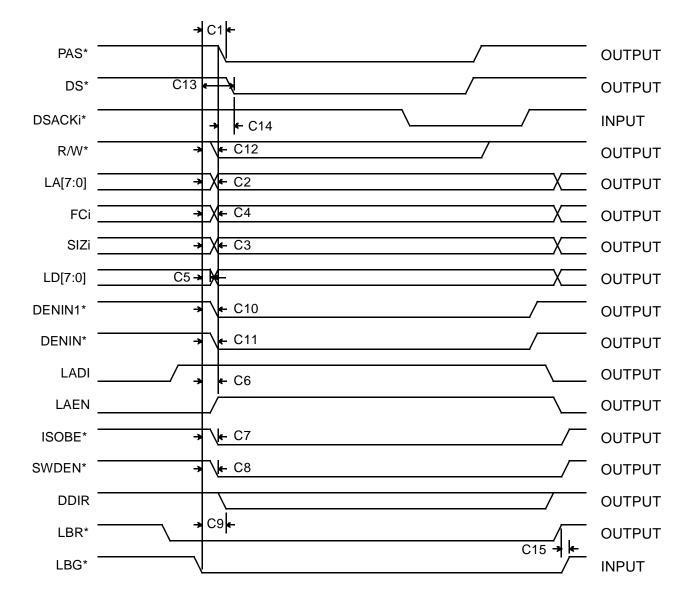

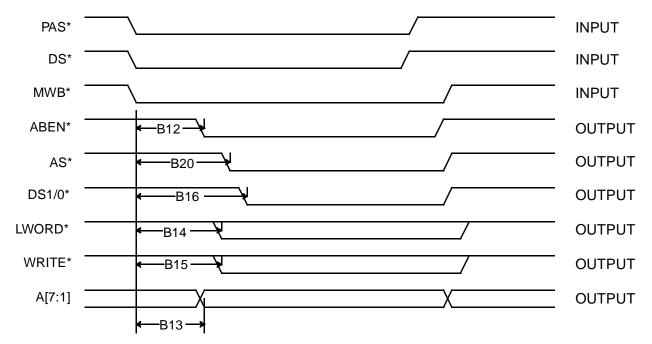

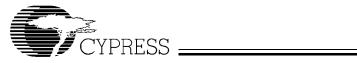

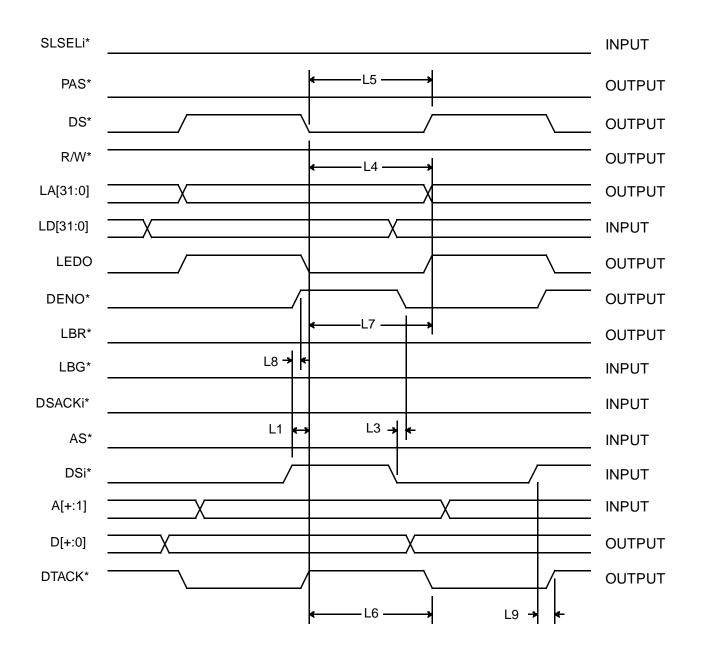

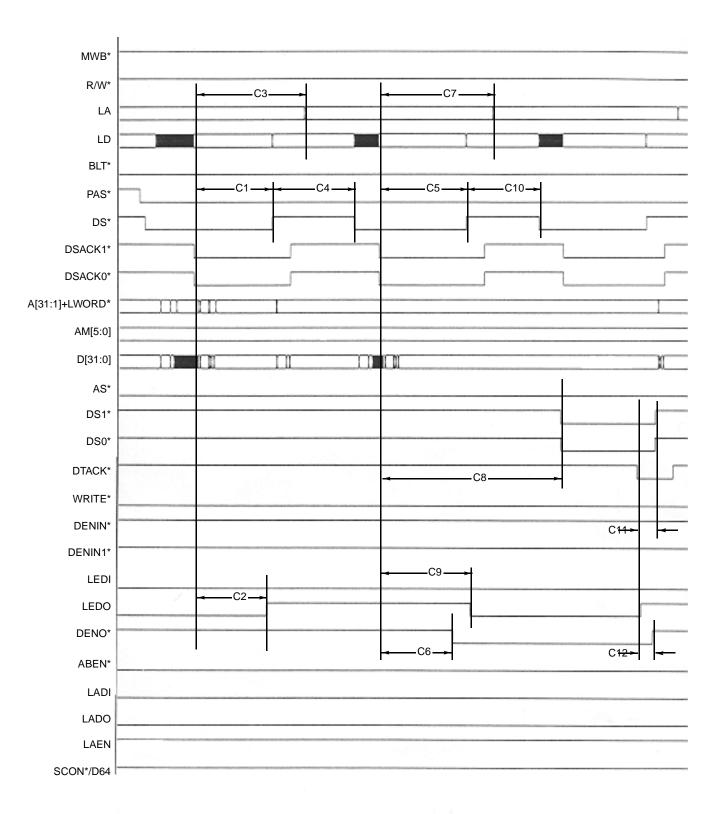

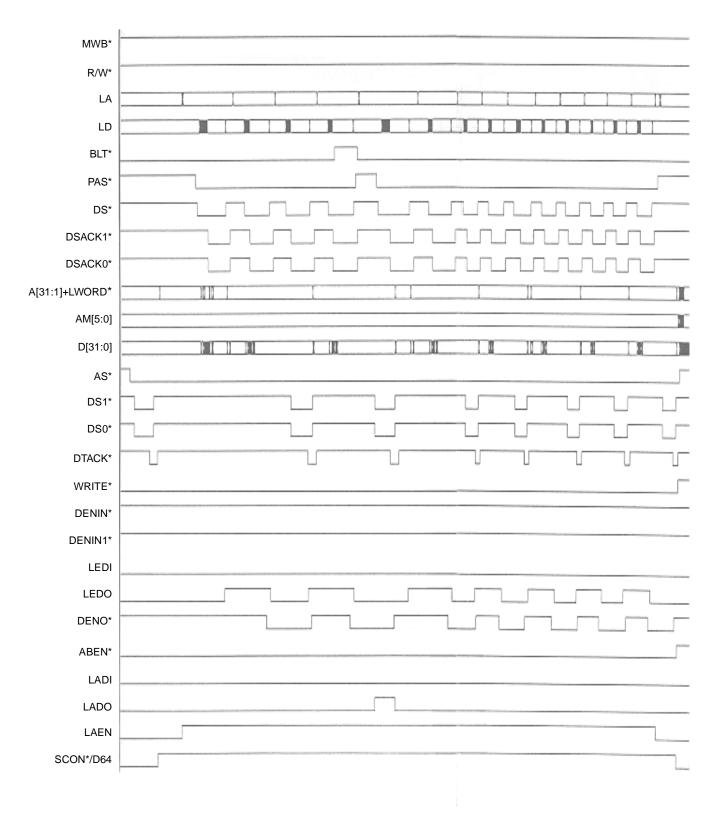

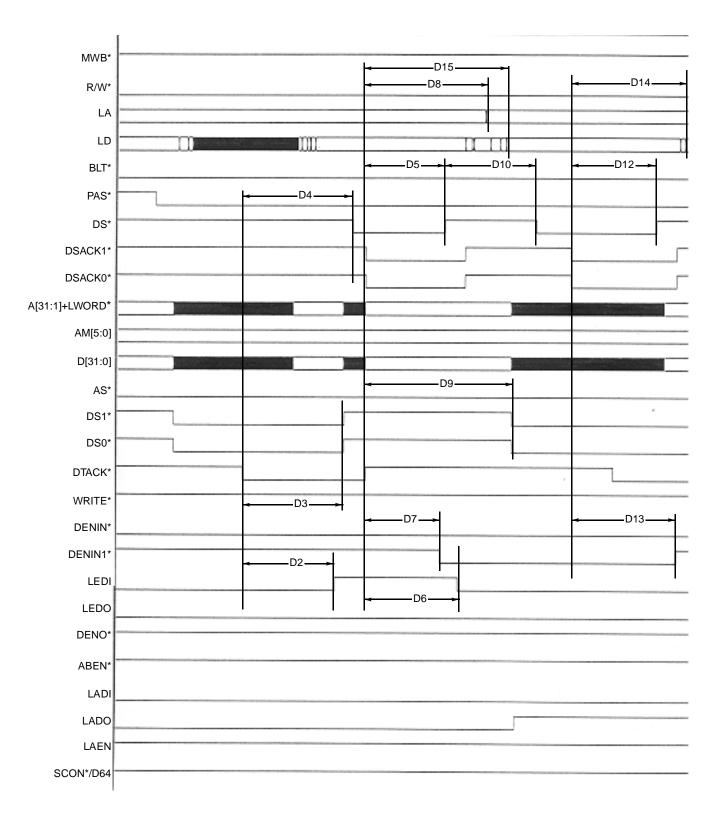

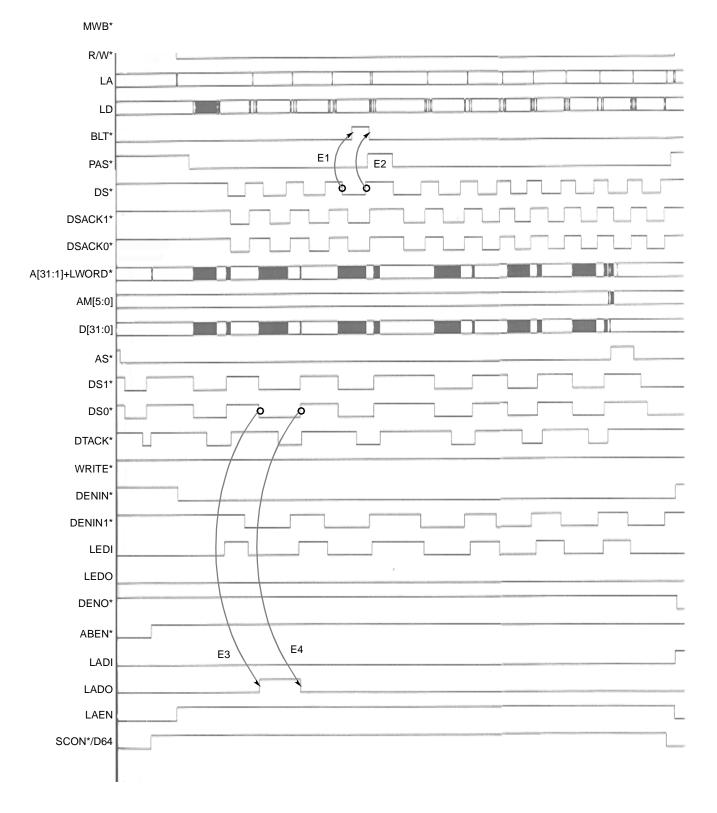

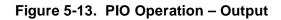

*Tables 1-1* through *1-4* show the buffer control signals for various master cycles.

| Data Path<br>Size |                  |                                 | al Bus<br>nulus          | ;                    |                      | lEbu<br>spon     |                  |             | ddre<br>ontr |                                  |             | Data<br>ontr |             |                  | Swa              | p Co             | ontro            | )       |

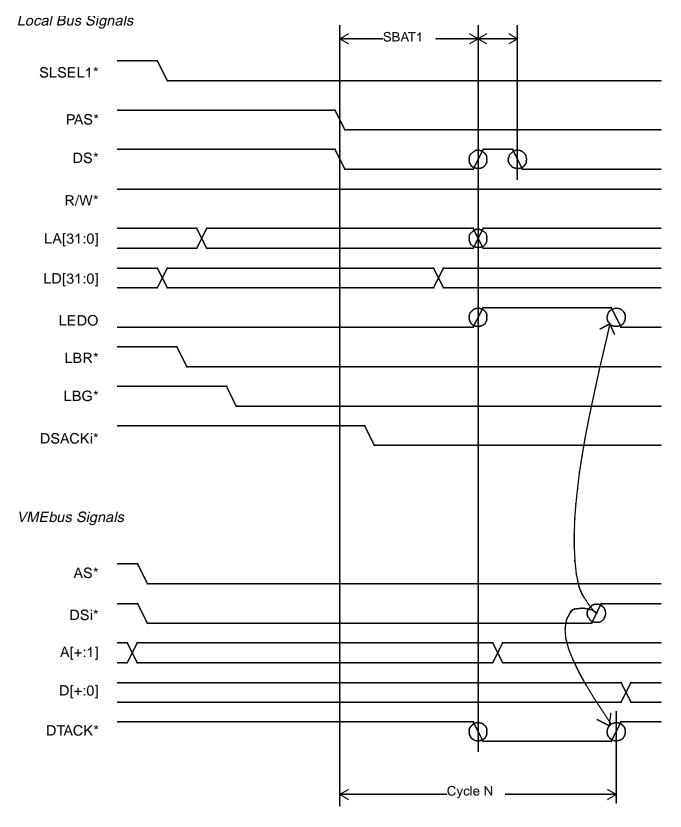

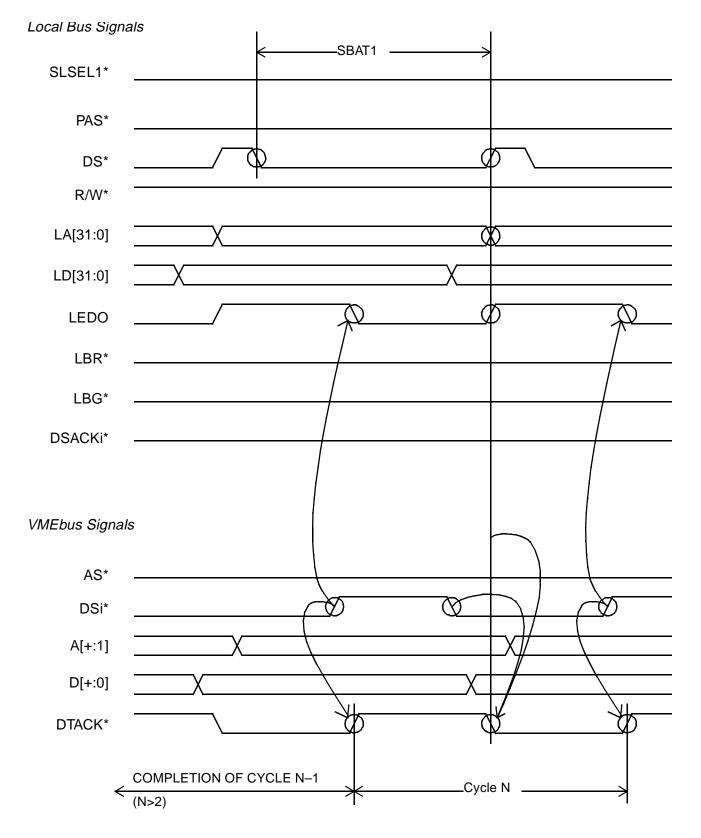

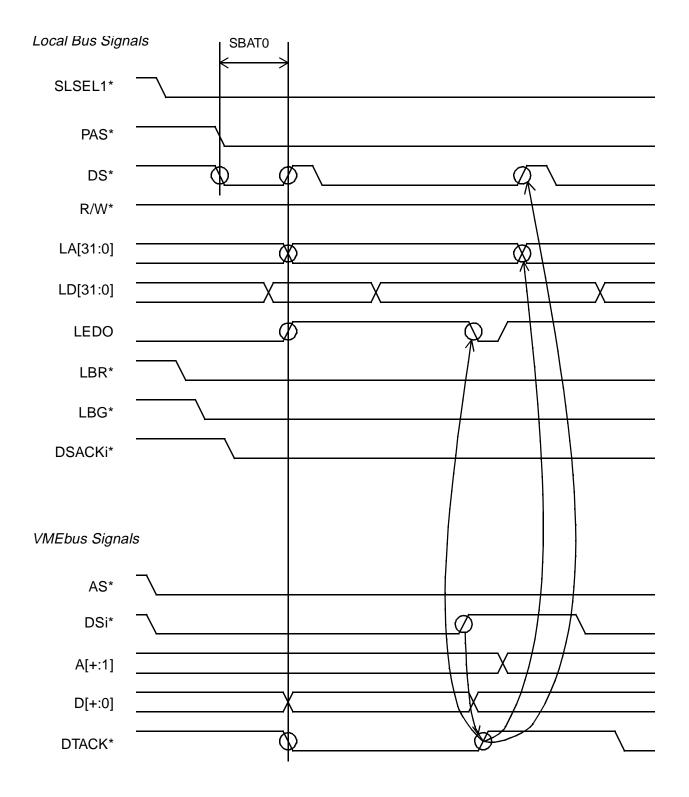

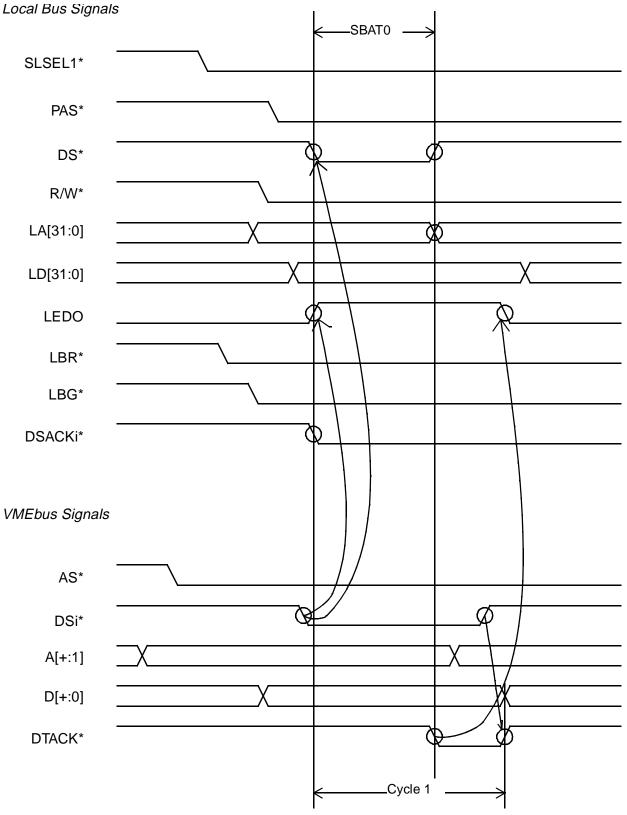

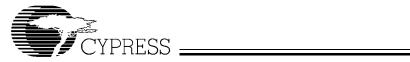

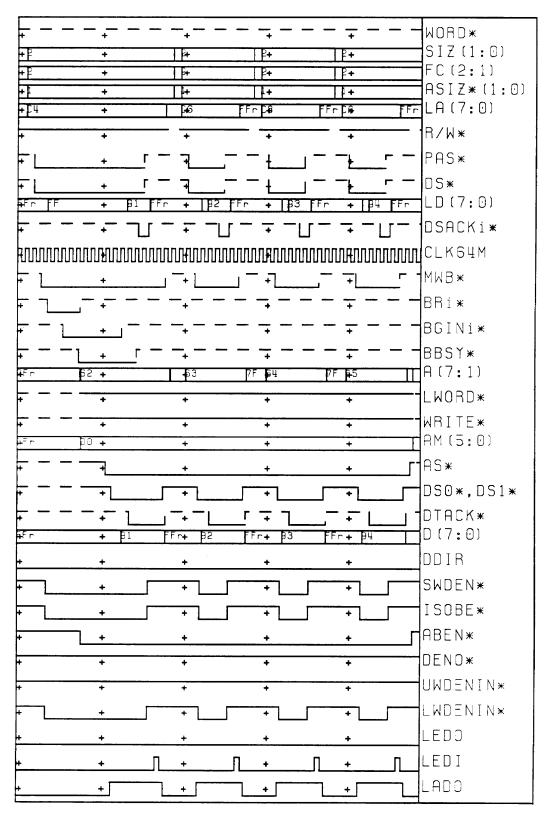

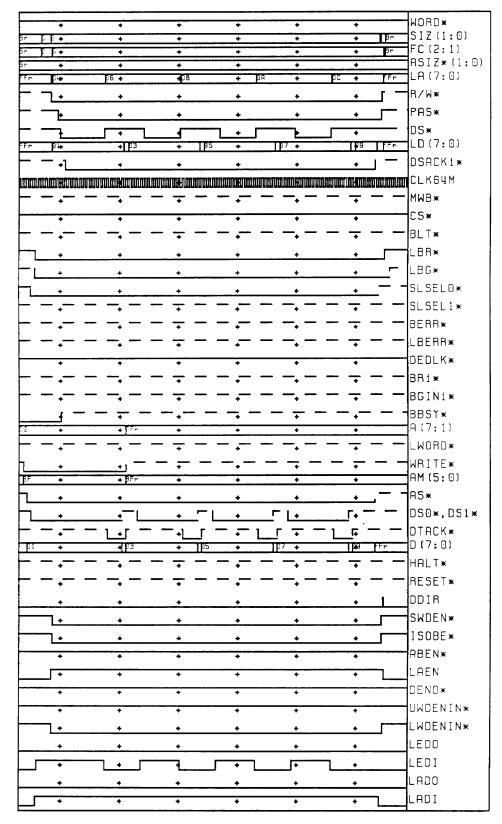

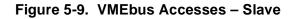

|-------------------|------------------|---------------------------------|--------------------------|----------------------|----------------------|------------------|------------------|-------------|--------------|----------------------------------|-------------|--------------|-------------|------------------|------------------|------------------|------------------|---------|