in**mos**®

# IMS B016 VMEbus master card

Incorporating the IMS F008A support software.

# SGS-THOMSON

# Contents

| 1                     | Intro                                                                                                                                                                                                                                                                | duction                                                                                                                                                                       | 1                                                                                                                                               |  |  |  |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                       | 1.1How to use this manual1.2BackgroundA tour of the IMS B016 hardware2.1IMS T801 and private SRAM2.1.1Dual–Access DRAM2.1.2MAP–RAM2.1.3Byte multiplexor2.1.4VMEbus master operation2.1.5VMEbus block transfer (BLT)2.1.6Events and Interrupts2.1.7VMEbus interrupter |                                                                                                                                                                               |                                                                                                                                                 |  |  |  |  |  |

|                       | 1.2                                                                                                                                                                                                                                                                  | Background                                                                                                                                                                    | 1                                                                                                                                               |  |  |  |  |  |

| 2                     | A to                                                                                                                                                                                                                                                                 | ur of the IMS B016 hardware                                                                                                                                                   | 3                                                                                                                                               |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      |                                                                                                                                                                               |                                                                                                                                                 |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      |                                                                                                                                                                               | 3<br>4                                                                                                                                          |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      |                                                                                                                                                                               | 4                                                                                                                                               |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      |                                                                                                                                                                               | 6                                                                                                                                               |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      |                                                                                                                                                                               | 8                                                                                                                                               |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      |                                                                                                                                                                               | 12                                                                                                                                              |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      |                                                                                                                                                                               | 12                                                                                                                                              |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      |                                                                                                                                                                               | 13                                                                                                                                              |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      | 2.1.8 Control of the local bus                                                                                                                                                | 13                                                                                                                                              |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      | 2.1.9 F–ROM                                                                                                                                                                   | 14                                                                                                                                              |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      | 2.1.10 Serial ports                                                                                                                                                           | 14                                                                                                                                              |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      | . 2.1.11 Resets and transputer system services                                                                                                                                | 14                                                                                                                                              |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      | 2.1.12 The front panel                                                                                                                                                        | 15                                                                                                                                              |  |  |  |  |  |

| 3                     | Insta                                                                                                                                                                                                                                                                | alling the IMS B016                                                                                                                                                           | 17                                                                                                                                              |  |  |  |  |  |

|                       | 3.1                                                                                                                                                                                                                                                                  | Configuring prior to installation                                                                                                                                             | 17                                                                                                                                              |  |  |  |  |  |

|                       | 3.2                                                                                                                                                                                                                                                                  |                                                                                                                                                                               | 19                                                                                                                                              |  |  |  |  |  |

|                       | 3.3                                                                                                                                                                                                                                                                  | 2.1.11 Resets and transputer system services<br>2.1.12 The front panel                                                                                                        |                                                                                                                                                 |  |  |  |  |  |

|                       | 31                                                                                                                                                                                                                                                                   |                                                                                                                                                                               | 20                                                                                                                                              |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                      |                                                                                                                                                                               | 20                                                                                                                                              |  |  |  |  |  |

| <b>4</b> <sup>′</sup> | The I                                                                                                                                                                                                                                                                | 3.3Installing the IMS B016 for use with IMS S514C in a<br>workstation203.4Installing the IMS B016 in a VMEbus card-cage20The IMS F008A support library214.1Package features21 |                                                                                                                                                 |  |  |  |  |  |

|                       | 4.1                                                                                                                                                                                                                                                                  | Package features                                                                                                                                                              | 21                                                                                                                                              |  |  |  |  |  |

|                       | 4.2                                                                                                                                                                                                                                                                  |                                                                                                                                                                               |                                                                                                                                                 |  |  |  |  |  |

|                       | 4.3                                                                                                                                                                                                                                                                  | Package features    Installing and using IMS F008A      Monitor code    Installing and using IMS F008A                                                                        |                                                                                                                                                 |  |  |  |  |  |

|                       | 4.4                                                                                                                                                                                                                                                                  | Examples and BSP code                                                                                                                                                         | 27                                                                                                                                              |  |  |  |  |  |

|                       | 4.5                                                                                                                                                                                                                                                                  |                                                                                                                                                                               | ge features       21         ng and using IMS F008A       22         r code       24         bles and BSP code       27         ibrary       28 |  |  |  |  |  |

|                       | 4.6                                                                                                                                                                                                                                                                  |                                                                                                                                                                               | 32                                                                                                                                              |  |  |  |  |  |

|                       | 4.7                                                                                                                                                                                                                                                                  | RTC library                                                                                                                                                                   | 36                                                                                                                                              |  |  |  |  |  |

|                       | 4.8                                                                                                                                                                                                                                                                  |                                                                                                                                                                               | 37                                                                                                                                              |  |  |  |  |  |

|                       | 4.9                                                                                                                                                                                                                                                                  |                                                                                                                                                                               | 39                                                                                                                                              |  |  |  |  |  |

|                       | 4.10                                                                                                                                                                                                                                                                 |                                                                                                                                                                               | 42                                                                                                                                              |  |  |  |  |  |

|                       | 4.11                                                                                                                                                                                                                                                                 |                                                                                                                                                                               | 44                                                                                                                                              |  |  |  |  |  |

|                       | 7.11                                                                                                                                                                                                                                                                 |                                                                                                                                                                               |                                                                                                                                                 |  |  |  |  |  |

| 5  | Deta                          | iled hardware description                                                                                      | 49             |  |  |  |

|----|-------------------------------|----------------------------------------------------------------------------------------------------------------|----------------|--|--|--|

| ۰. | 5.1                           | Using the IMS B016                                                                                             | 49             |  |  |  |

|    | 5.2 Primary control registers |                                                                                                                |                |  |  |  |

|    | 5.3                           | VMEbus MASTER configuring                                                                                      | 50             |  |  |  |

|    | •<br>•                        | 5.3.1MAP-RAM5.3.2Configuring the byte-multiplexor5.3.3Bus Error                                                | 50<br>53<br>55 |  |  |  |

|    | 5.4                           | 5.3.3 Bus Error                                                                                                | 55             |  |  |  |

| •  |                               | <ul> <li>5.4.1 Configuring the VMEbus slave decoder</li> <li>5.4.2 VIC programming for slave access</li> </ul> | 55<br>56       |  |  |  |

|    | 5.5                           | System controller functions                                                                                    | 56             |  |  |  |

|    | 5.6                           | VMEbus Interrupter                                                                                             | 57             |  |  |  |

|    | 5.7                           | Interprocessor communications registers                                                                        |                |  |  |  |

|    | EQ                            | <ul> <li>5.7.1 Interrupts</li></ul>                                                                            |                |  |  |  |

|    | 5.8<br>5.9                    |                                                                                                                | 61             |  |  |  |

|    | 5.9                           | 5.9.1 F-ROM                                                                                                    | 63             |  |  |  |

|    | 5.10                          | PEX Boards                                                                                                     | 64             |  |  |  |

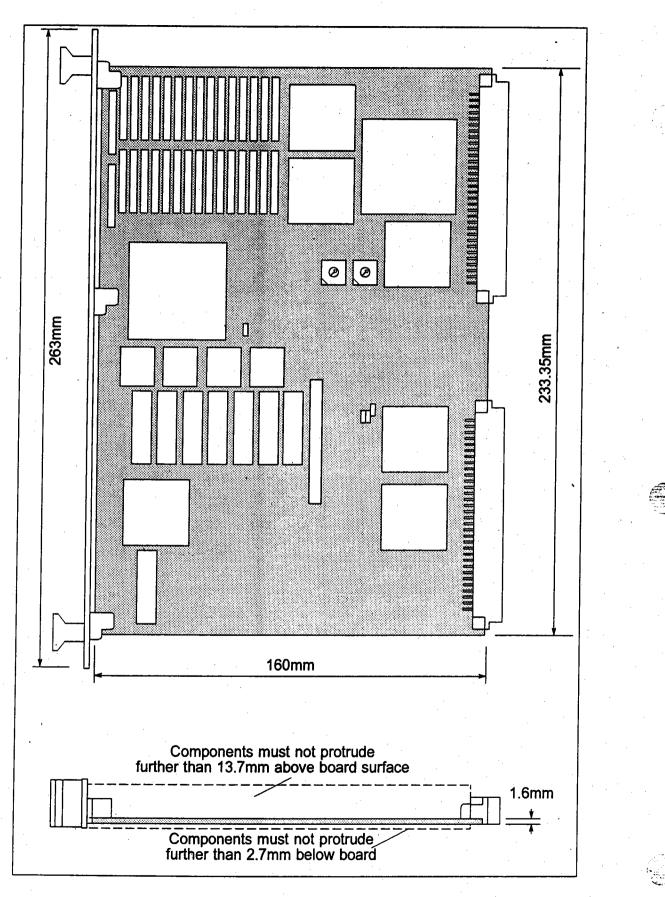

|    | 5.11                          | Mechanical and thermal details                                                                                 | 64             |  |  |  |

|    |                               | 5.11.1Mating connectors5.11.2Environmental details                                                             | 65<br>65       |  |  |  |

| 6  | Refe                          | rences                                                                                                         | 67             |  |  |  |

| Ар | pendic                        | ces                                                                                                            |                |  |  |  |

| A  | Mem                           | ory map of IMS B016                                                                                            | 71             |  |  |  |

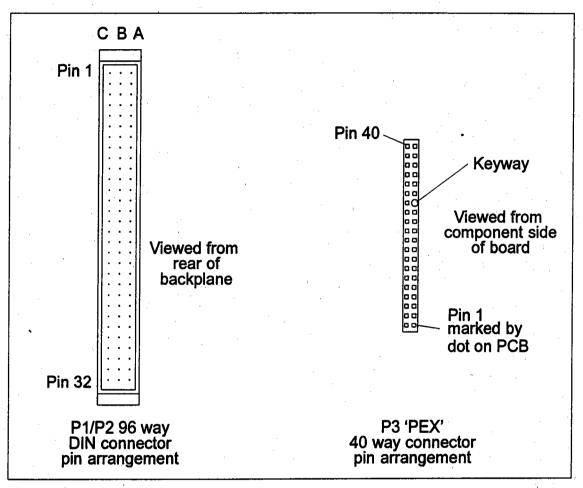

| B  | Connector diagrams and cables |                                                                                                                |                |  |  |  |

|    | B.1                           | Connector pin assignments                                                                                      | 75             |  |  |  |

|    | B.2                           | Cables                                                                                                         | 78             |  |  |  |

| С  | Electrical specifications     |                                                                                                                |                |  |  |  |

|    | C.1                           |                                                                                                                | 79             |  |  |  |

|    |                               | C.1.1 Power supply                                                                                             | 79             |  |  |  |

| ·  |                               | C.1.2 Board-to-board link connections<br>C.1.3 Non-local link connections                                      | 79<br>79       |  |  |  |

ii

# Contents

(

| D Monitor command language |                                                |                                                                                                                                                                                                                                                            |                                                                                                          |  |

|----------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|

| <b>D</b>                   | <b>Moni</b><br>D.1<br>D.2<br>D.3<br>D.4<br>D.5 | tor command languageLanguage basicsD.1.1ComponentsD.1.2DelimitersAbbreviationsD.2.1DefaultingD.2.2Error reportingVariables and expressionsD.3.1NumbersD.3.2Numeric expressionsD.3.3Numeric symbolsD.3.4AssignmentsD.3.5String assignmentIntrinsic commands | 81<br>81<br>81<br>82<br>82<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83<br>83 |  |

|                            |                                                | D.5.1Formal and actual parametersD.5.2Returning resultsD.5.3Control flow                                                                                                                                                                                   | 88<br>89<br>90                                                                                           |  |

| Ε                          | IMS E                                          | 3016 design revisions                                                                                                                                                                                                                                      | 92                                                                                                       |  |

| F                          | Comp                                           | patibility with the IMS B011                                                                                                                                                                                                                               | 95                                                                                                       |  |

|                            | F.1                                            | General compatibility issuesF.1.1VMEbus interfaceF.1.2Memory mapF.1.3Byte multiplexorF.1.4TRAM slotsF.1.5Serial ports                                                                                                                                      | 95<br>95<br>95<br>96<br>96<br>96                                                                         |  |

| G                          | VME                                            | bus performance                                                                                                                                                                                                                                            | 97                                                                                                       |  |

9

<u>iv</u>

# Introduction

## 1.1 How to use this manual

The manual is organised into roughly three sections:

- A general overview of the IMS B016 hardware functions and the access to those functions via the IMS F008A procedure library. This section also covers jumper configuration and installation details. Refer to chapters 2 and 3.

- A detailed description of the IMS F008A support library and example applications. This section also covers software installation, configuration and loading of the sample applications. Refer to chapter 4.

- An in-depth discussion of IMS B016 hardware functionality and the detailed procedures for setting up and using all the board level features. Refer to chapter 5.

The appendices contain memory map and connector information and also an overview of the monitor command language used in the example code.

## 1.2 Background

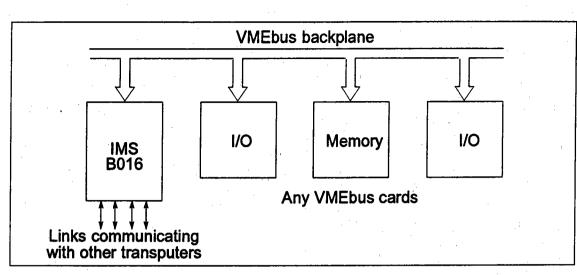

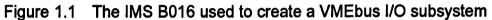

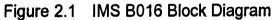

The IMS B016 is a VMEbus board incorporating a 32-bit transputer processor, local RAM, peripherals, and interface circuitry to allow efficient communication between the transputer and other VMEbus boards. See figures 1.1 and 1.2

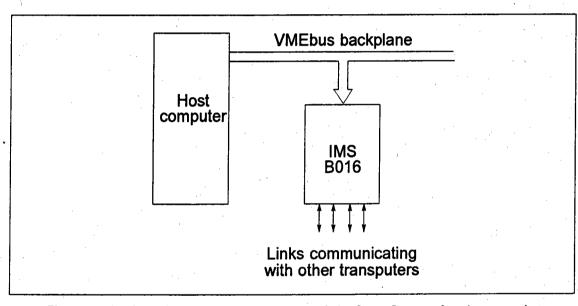

Sustained transfer rates in excess of 12Mbytes/s are achievable, given a fast VMEbus system. The IMS T801 on-board is capable of 12.5 MIPS and has its own private fast SRAM for speed-critical code and data. Some memory on the board can be accessed by both the transputer and other VMEbus Masters. This is called the *Dual-Access Memory*. The transputer, an IMS T801, can perform Master accesses to other VMEbus slaves. It can also interrupt other VMEbus Interrupt Handlers and itself handle VMEbus interrupts.

The IMS B016 can be used as the gateway hardware in a SUN workstation hosted transputer development system. A board support software product, the IMS S514C is available to support this use of the card. S514C users need not read this manual in detail as the User Guide supplied with the software contains specific installation and configuration details for the IMS B016.

Users wishing to proceed directly to install the IMS B016 in their equipment should read section 3.1.

Figure 1.2 The IMS B016 used as an interface from a host computer

# 2 A tour of the IMS B016 hardware

INMOS provides a set of software libraries, written in the C language and compatible with transputer toolset development systems. These libraries (IMS F008A) provide the easiest way to program the card for the majority of users. This section explains the card's features and operation from the perspective of a code which makes calls to IMS F008A libraries. Users who would like to perform functions which are not catered for in the IMS F008A libraries should read section 5.1 and refer to the IMS F008A source code.

#### 2.1 IMS T801 and private SRAM

The card's processor, an IMS T801 floating point processor, has four INMOS serial links. These links allow connections to be made to other transputer devices on other boards via the P2 connector. 256Kbytes of fast memory (the *private SRAM*) is directly connected to the IMS T801. This cycles in 80ns and is only accessible by the transputer. Typically this memory would be used to store transputer code and data which does not need to be accessed from the VMEbus. The SRAM is about twice as fast as the next fastest available memory, as seen from the transputer, so its use is recommended whenever possible. The SRAM occupies the first 256Kbytes of the transputer's address space, minus the IMS T801's 4Kbyte internal RAM which overlays it (#80001000–#8003FFFF).

Figure 2.2 IMS T801 and private SRAM

Note that most transputer compilers have storage allocation strategies which attempt to put frequently used data at a low memory address. This strategy will work well with the private SRAM as it is located just above the transputer's internal memory. However, in seeking ultimate performance, the user may wish to perform his own analysis of where code and data are placed. Refer to memory maps in Appendix A.

#### 2.1.1 Dual-access DRAM

A large memory, using fast DRAM devices, is accessible from both the IMS T801 and (with appropriate programming) from the VMEbus as slave memory. This kind of dual-access is sometimes called "dual-port memory" but since this is not strictly true (true dual-port memory is very expensive and about 100 times less dense than the devices used on the IMS B016) the term "dual-access" will be used here.

Two variants of the IMS B016 are available. The IMS B016–1 has four megabytes of dual-access DRAM. The IMS B016–4 has sixteen megabytes of dual-access DRAM. Otherwise the variants are identical. Without any special configuring, the dual-access DRAM appears as the first four or sixteen megabytes of the transputer's address space, minus the internal RAM and private SRAM which overlay it (#80040000–#803FFFFF or #80040000–#80FFFFFF) and cycles in 160ns (four CPU cycles).

When accessed from the VMEbus as slave memory, the dual-access DRAM can occupy any VMEbus address in any address space (except A16). Programmable decode circuitry on the card allows the card's memory to appear in one or more 64Kbyte blocks of VMEbus address space. This means that one can arrange for less than the full amount of card memory to be accessible on the VMEbus. This feature is useful both when implementing a system which uses the A24 address space (which is only 16 megabytes). It also permits decoding at multiple different locations which may be an advantage in a multi-master application. The correspondence between VMEbus addresses and IMS T801 addresses can appear slightly confusing. For a 4 Megabyte board, a VMEbus address can be represented as follows:

| 31 | 22 2 | 1 16 | 15 | · · · | - <u>.</u> | 0 |

|----|------|------|----|-------|------------|---|

| Α  |      | В    |    | С     |            |   |

|    |      |      |    |       |            |   |

Bitfields "A" and "B" together form a 16-bit value which is used in a table look-up to determine if the card should respond to the VMEbus transfer. Bitfields "B" and "C" together form the 22-bit index into the card's DRAM.

5

To determine what address is being accessed in dual-access DRAM, write the VMEbus address in the form shown and verify that bitfields "A" and "B" do in fact match the values programmed by prog\_slave\_access(). Then take bitfields "B" and "C" and replace "A" with 100000000 to form the corresponding IMS T801 address.

Note that some "lost" memory which the IMS T801 can not see because it is overlaid by the private SRAM will be accessible from the VMEbus. The first location in dual-access DRAM which is available to the IMS T801 is at offset #040000 so applications sharing data between other VMEbus masters and the cards IMS T801 should not use locations below this.

When the card is first switched on or reset, VMEbus slave accesses to the dual-access DRAM are disabled. The VMEbus address decoded and the type of address modifier recognised must first be programmed by the IMST801. VMEbus slave access would then be enabled. All these configuration functions are performed by writing control registers on the card from a program running on the IMS T801.

Using the IMS F008A libraries, VMEbus slave configuration of the dual-access DRAM is achieved using the routine prog\_slave\_access().

prog\_slave\_access(decode\_address, decode\_window, address type, writepost)

decode\_address is the base of the VMEbus address space to be decoded. decode\_window is the number of bytes of address space to decode (routine rounds this up to the nearest 64 Kbytes block). address\_type signifies whether the card should decode A32 or A24 cycles — value is either 32 or 24. Writepost controls whether the card buffers one outstanding write from the VMEbus — value 1 to enable writeposting. After configuring the routing enables VMEbus slave accesses.

```

#include "vme.h"

#include "basic.h"

```

```

int main()

{

basic_board_init();

prog_slave_access((void*)0x10000000,0x00400000,32,0);

}

```

This complete program first initialises the card and then sets up for decoding the dual-access DRAM as a four megabyte region from VMEbus address #10000000

in the A32 address space. Writeposting is not enabled. So after running this program, the IMS B016 card will function like a four Mbyte D32 VMEbus memory card in the A32 address space, decoded at address #10000000. The card will respond to both "user" and "supervisor" address modifier codes.

#### 2.1.2 MAP-RAM

6

The MAP-RAM is a look-up table, connected directly to the top 12 bits of the IMS T801's address bus. For every IMS T801 memory cycle, the MAP-RAM produces a set of control information which is used to determine how the various parts of the board's circuitry behave. For instance the MAP-RAM determines what kind of VMEbus cycle will be performed when the transputer attempts to perform a VMEbus master cycle.

Since there is one MAP-RAM location per megabyte of IMS T801 address space, different functions may not be programmed for two addresses within the same megabyte page.

The writing of MAP-RAM locations and the generation of the control bit-patterns which need to be written has been automated by routines in the IMS F008A support library. For most applications it should not be necessary to write MAP-RAM contents directly.

Users wishing to perform low-level MAP-RAM programming are directed to section 5.1.

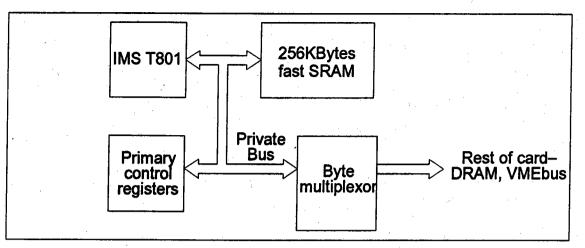

#### 2.1.3 Byte multiplexor

There are two main databuses on the board. One is private to the IMS T801 and its SRAM (and some control registers). The other connects everything else including the dual-access DRAM and the VMEbus. Between these two 32-bit busses is a transceiver which has the ability to re-order bytes (see figure 2.2). This feature allows data to be moved at high-speed between little-endian processors (the IMS T801) and big-endian processors and peripherals (most VMEbus cards). The byte multiplexor can perform any byte reordering operation, the particular operation is programmable on a megabyte-by-megabyte basis using the MAP RAM. Up to eight reordering functions can be active at any time.

In order that the board behaves in a sane fashion at system start-up, the operation of the Byte Multiplexor is disabled on reset and must be explicitly enabled via a control register. When disabled, the Byte Multiplexor functions as a simple 32-bit transceiver.

The eight re-ordering functions can be re-programmed at any time by writing the relevant registers. Note however that chaos is likely if the Byte Multiplexor is instructed to re-order memory where the currently executing program (or its data) resides. Note also that transputer byte-writes do not function correctly for regions of memory where byte multipexing is in operation. Control over the byte multiplexor is provided via various low-level IMS F008A routines. program\_byte\_mux() sets up a swap function, turnon/off\_byte\_mux() enable and disable the multiplexor. basic\_board\_init() clears the swap function code for all memory and programs swap function zero to "transparent". Thus memory areas which have not been explicitly configured for byte-multiplexing will retain a default transparent swap function when the byte-mux is enabled for a region of memory.

Since the majority of byte-multiplexing applications are associated with master VMEbus access, the routine prog\_master\_access() allows swap functions to be specified along with other VMEbus access parameters.

#### 2.1.4 VMEbus master operation

The IMS T801 can perform VMEbus master cycles simply by making memory accesses to certain regions of its address space. However, regions of address space must be programmed in advance for the appropriate VMEbus options.

The VMEbus supports various address spaces, including three different address sizes, 16-bit which is termed "A16", 24-bit (A24) and 32-bit (A32). Generally, simple I/O cards use the A16 space, complex I/O cards use A24, while CPU and memory cards use A32. The VMEbus also supports various data size options, including 32-bit (D32), 16-bit (D16) and 8-bit (D08). D32 tends to be used for CPU to memory transactions and for high-speed I/O, D16 for medium speed I/O and older cards and D08 for slow I/O such as serial ports.

The IMS B016 can generate many combinations of different address and data transfer VMEbus master cycles. The particular kind of transfer to be performed is determined by a look—up table, indexed on the IMS T801 address bus called the "MAP-RAM". Since the MAP-RAM has a separate entry for each and every megabyte of IMS T801 address space, the VMEbus master characteristics may be programmed on megabyte blocks. The IMS F008A routine prog\_master\_ac-cess() provides the mechanism for setting up such regions.

The VMEbus uses a byte-addressed scheme which is big-endian. That is, byte 0 corresponds to the upper byte of a 32-bit (D32) word, byte 1 to the upper middle byte and so on. Cards which support D32 transfers must also support D16 and D08 transfers to the same locations. However, all VMEbus memory spaces are conceptually 32-bit words, each composed of four bytes (called BYTE 0, BYTE 1, BYTE 2 and BYTE 3). Because the IMS T801 only performs 32-bit external memory cycles, it presents a 30-bit address to the rest of the card. This is sufficient to identify an individual VMEbus D32 longword, but lacks sufficient bits to address the words and bytes within D16 and D08 transfers. The IMS B016 works around this lack of address bits 0 and 1 by storing these bits within the MAP-RAM entry.

This means that one region of IMS T801 memory can be programmed to generate, for example a D16(BYTE3–2) transfer, while another can generate a D16(BYTE1–0) transfer. Working within the A16 or A24 address spaces, the upper 16 and 8 address bits respectively from the IMS T801 are not relevant to the VMEbus. These can be used to create multiple different regions in IMS T801 memory space which in fact generate the same A24 (or A16) VMEbus address. The effect is that all combinations of different D16 and D08 BYTEs can be addressed by the card.

In the A32 address space, this feature is not available since there are no redundant address bits. This means that practically it is not possible to use any data transfer size other than D32. Usually this would not be a limitation since the smaller data sizes are associated with I/O cards which are usually placed in the A16 and A24 address spaces.

The following example program, using IMS F008A library routines, programs the card such that for VMEbus A24 address region #100000-#1FFFFFFF , various regions in IMS T801 address space generate VMEbus master transfers with all the different sizes and byte selections.

#include "vme.h"

#include "basic.h"

#define MEGABYTE 0x00100000

```

int main()

```

1

int i=0; unsigned int

\*d32,\*d16b01,\*d16b23,\*d08b0,\*d08b1,\*d08b2,\*d08b3; unsigned int t1,t2;

| d32 =  |   |           |     | *)0x00100000; |

|--------|---|-----------|-----|---------------|

| d16b01 | = | (unsigned | int | *)0x04100000; |

| d16b23 | = |           |     | *)0x05100000; |

| d08b0  | = |           |     | *)0x06100000; |

| d08b1  | = |           |     | *)0x07100000; |

| d08b2  | = | (unsigned | int | *)0x08100000; |

| d08b3  | = | (unsigned | int | *)0x09100000; |

```

basic board init();

```

```

i=init_vme_master(3,RELMODE_ROR,TRUE);

i=prog_master_access(d32,MEGABYTE,32,24,0,0);

i=prog_master_access(d16b01,MEGABYTE,16,24,0,1);

i=prog_master_access(d16b23,MEGABYTE,16,24,0,2);

i=prog_master_access(d08b0,MEGABYTE,8,24,0,3);

i=prog_master_access(d08b1,MEGABYTE,8,24,0,4);

i=prog_master_access(d08b2,MEGABYTE,8,24,0,5);

i=prog_master_access(d08b3,MEGABYTE,8,24,0,6);

i=turnon_vme_master();

```

Example number 3 in the IMS F008A contains a more comprehensive version of this program, including byte-multiplexor and a second IMS B016 used as the slave card.

#### IMS T801 byte writes

}

Unlike many other microprocessors, the IMS T801 can *only* perform 32-bit and 8-bit write operations and only 32-bit reads. The VMEbus supports many more data transfer options and usually these are supported by using the IMS T801 performing only 32-bit reads and writes and using the card's capability to map those accesses into whatever VMEbus cycle is required. However, should the IMST801 perform an 8-bit write operation on a memory region programmed for VMEbus D32 transfers, the card will in fact generate the appropriate D08 VMEbus cycle.

That is, D08(BYTE0) for an upper byte write, D08(BYTE1) for an upper-middle byte write and so on. This feature means that for a region programmed to be VMEbus D32, the IMS T801's view of memory-including byte-write-will be identical to on-card memory. Thus such regions of VMEbus memory can be used for program code and data storage.

#### VMEbus error

Should a VMEbus transfer cycle, where the IMS B016 is master, receive a bus error, circuitry on the card causes an *event* to be signaled to the IMS T801. The IMS T801 has no feature corresponding to the M68000 the bus error pin and this mechanism (where an event is raised) is the only way to inform the CPU asynchronously of a bus error. The IMS T801 memory cycle which resulted in the bus error'ed VMEbus transfer will complete but with meaningless data if it is a read. The actions taken on bus error depend upon the application program. IMS F008A provides a very simple interrupt handler for bus error which sets a global variable—this can be checked every so often. More sophisticated schemes using channels to signal the error can be implemented by modifying the F008A code.

IMS F008A provides an event handler, complete with an event service routine for bus error interrupts. User's application code can make use of these library routines to detect bus error and take appropriate action.

```

#include "vme.h"

#include "event.h"

#include "basic.h"

int main()

{

basic_board_init();

start_event_handler();

install_berr_handler(standard_berr_handler);

my_vmebus_master_setup();

for (;;) {

my_vmebus_master_activity();

if (berr_happened == 1)

exit(1);

}

```

#### VMEbus request modes

IMS F008A routine init\_vme\_master() should be called before attempting to perform any master operations. It configures the VMEbus request level which the card will use, the request mode and whether the card will perform master writeposting.

Request modes allowed:

- ROR for "release on request". Meaning that the card captures the VMEbus on a master transfer and retains bus ownership until it sees another card requesting the bus.

- **RWD** for "release when done". Meaning that the card captures the VMEbus on a master transaction and then releases the bus immediately.

- ROC for "release on bus clear". Meaning that the card captures the VMEbus on a master transaction and then releases the bus when it sees a bus clear signal.

- BCAP for "bus capture and hold". Meaning that once the VMEbus has been captured by the card, it is never released.

Users who are in doubt about which bus request mode to use should probably be using ROR. Bus request level 3 should always work. Some system controllers only support this level.

#### VMEbus write posting

The VIC chip, and consequently the IMS B016, is capable of performing *posted* VMEbus write cycles. When a write cycle is initiated—either by the T801 as a VMEbus master or by another VMEbus master as a slave cycle to the IMS B016s dualaccess DRAM, the card's circuitry can store the data to be written and immediately acknowledge the writing device. The writing device can then proceed to perform other cycles and the write cycle completes some time later. This is termed "write posting". Write posting can greatly speed up many applications. However, it has the disadvantage that if the posted cycle actually never completes, then the writing device will have assumed that the write cycle did complete. Master and slave write posting are separately enabled. It is not possible to select writeposting on an address-basis.

#### System controller options

Certain VMEbus backplane housekeeping functions, such as system clock generation and bus arbitration, must be undertaken by the card installed in slot 1 (leftmost). Any VMEbus system *must* have a system controller and it must be in logical slot 1. In workstations which have a VMEbus the system controller function is usually performed by the mothercard.

The IMS B016 can perform system controller functions, when enabled by fitting jumper K3. Users who are not installing the card in slot 1 of their backplane need not read this section.

IMS F008A routine init\_slot\_one() configures both the backplane arbitration style and the bus timeout delay.

Arbitration style can be either *priority* or *round-robin* meaning that the next master granted the bus is either the one with the highest request level, or one requesting on the level given access least recently.

Bus timeout delay is the time after which the system controller signals bus error on a transaction which has not completed. A timeout delay of  $32\mu$ s is normal.

#### 2.1.5 VMEbus block transfer (BLT)

The IMS B016 does not support master BLT operation. Slave BLT transfers are handled.

#### 2.1.6 Events and interrupts

The IMS B016 provides the capability to handle VMEbus interrupts. It also provides several local on-card interrupt sources such as the Serial Ports, Bus Error detection and Interprocessor Communication Registers. All these interrupt conditions can be programmed to cause an IMS T801 *event*<sup>1</sup>.

The IMS T801 lacks any vectored interrupt system. In the IMS B016, extra circuitry is provided to allow VMEbus interrupt vectors (status/ID) to be read from a VIC status register. When this register is read, if a VMEbus interrupt is pending then the VIC requests the bus and fetches the Status/ID byte (vector). The value fetched is returned as the contents of the register to the IMS T801. In the case of a local interrupt, the vector is fetched from one of the vector registers within the VIC. Provided that the programmer has ensured that all interrupt sources have distinct vectors, an event process running on the transputer can distinguish between interrupts using the vector. IMS F008A provides an event handler library which allows interrupts, both VME and local, to be used from "C" programs. start\_event\_handler() is called, allowing handler routines to be installed via calls to routines such as install\_vme\_int\_handler()

```

#include "vme.h"

#include "event.h"

#include "basic.h"

void my_int_handler_1(void)

{

printf("Got Interrupt on irq 1\n");

}

int main()

{

basic_board_init();

start_event_handler();

vec=install_vme_int_handler(1,VECTOR_INT_1,my_int_handler_1

);

printf("\n Waiting for interrupts");

```

```

for (;;) ;

}

```

This example code programs a handler routine for VMEbus interrupt level 1. After initialising, the program loops forever, printing a message if an interrupt is received.

"Event" is the transputer terminology for "interrupt". Users should consult the Transputer Databook for details of event.

IMS F008A provides a header file containing suggested vector values for the local interrupt sources.

#### 2.1.7 VMEbus interrupter

VMEbus interrupts can be generated (as opposed to handled) by the card. The IMS F008A routine send vme\_interrupt(level) generates an interrupt on the level specified (1-7). This routine will not return until a VMEbus interrupt handler has acknowledged the interrupt. The routine prog\_vme\_interrupt\_vector(level,vector) programs the vector (status/ID byte) returned by the card during such an acknowledge cycle.

```

#include "vme.h"

#include "basic.h"

#include "event.h"

```

int main()

```

basic_board_init();

```

prog\_vme\_interrupt\_vector(1,VECTOR\_INT\_1);

}

2.

Ł

A separate handler can be installed to deal with interrupt acknowledge cycles install\_vme\_int ack handler.

#### 2.1.8 Control of the local bus

The local bus on the board (the bus to which the Dual-Access DRAM is connected) can be under the control of any of three entities:

- 1 The IMS T801.

- 2 The VMEbus control circuitry (VIC), when a VMEbus SLAVE cycle is in progress.

3 DRAM refresh circuitry.

Arbitration is performed at the end of each access. For the IMS T801 this means at the end of every memory cycle which requires the local bus (all memory cycles *except* those for private SRAM, primary registers and Byte-switch configuration registers). For the VIC this means the end of every VMEbus slave access to the IMS B016<sup>2</sup>. The arbiter reverts to an idle state after every refresh cycle. The design of the arbiter and the board is such that fair access is allowed to the Dual-Access DRAM for both the IMS T801 and VMEbus masters performing slave cycles. That is, if both the IMS T801 and a VMEbus master attempt to saturate the Dual-Access DRAM, then DRAM cycles will be given fairly to each requester.

On BLT (Block Transfer) slave cycles, the bus is secured for the the duration of the whole block transfer.

#### 2.1.9 F-ROM

The IMS T801 may boot from a link or from the on-board 256 Kbyte ROM. These ROM devices are electrically reprogrammable *Flash* devices which are reprogrammed in-situ. Reprogramming is achieved using the IMS T801, booted via a link with programming software.

For programming and erasing to function, jumper K4 must be fitted correctly for F-ROM.

The devices are soldered to the board for extra reliability. F-ROMs can be erased and reprogrammed in excess of 10000 times.

IMS F008A supports F-ROM programming and erasing from a host development system. Library routines which erase and program individual ROMs and ROM locations are also provided. These can provide a useful basis for writing custom F-ROM applications.

The IMS F008A monitor can be programmed into the F–ROMS and the card will then boot stand-alone–communicating via the serial port. The makefile used to operate the ROM version of the monitor provides an example which can be followed by users building stand-alone ROM applications.

#### 2.1.10 Serial ports

The card provides two independent asynchronous serial ports, buffered to EIA-RS232 levels on connector P2. IMS F008A provides a library of functions which drive the serial ports, including support for Xon/Xoff flow control and buffering using interrupts.

Baud rates up to 19.2K are supported and the IMS F008A monitor program can be configured to talk to a terminal via the serial ports.

#### 2.1.11 Resets and transputer system services

The card circuitry is reset at power-on and following a VMEbus reset and someone pushing the front panel reset button. All these actions create a *board reset*. In addition, the IMS T801 is reset at this time. However, the IMS T801 can also be reset from the "ServicesUp" port on connector P2. This reset will not affect any other circuitry apart from the transputer and allows the transputer to be re-booted without disturbing the rest of the card's circuitry. Note that this means that after a *board reset*, all the configuration for VMEbus access and suchlike will be lost. However following an IMS T801 reboot this configuration will not be lost.

It is possible to stop the operation of the CPU completely by performing a memory access to an address which does not correspond to either an on-board resource like DRAM or F-ROM or to a region programmed for VMEbus master access. In this event it is necessary to perform a *board reset* in order to recover correct operation.

Note that transputers do not typically clear their error signals on reset, a program which explicitly clears the error signal must be run. Transputer programs usually have this code included automatically. This means that users should not be surprised if the "error" LED remains lit after the card is reset.

The IMS T801 is provided with a 'subsystem" services port which is electrically compatible with other INMOS cards. In addition, three extra subsystem ports which are electrically compatible are provided for users who wish to control four independent sub-networks of transputers. These three extra ports are not software compatible with any other card and are dealt with in section 5.8.

The "traditional" subsystem port is addressed as two of the registers in the primary control registers (see figure 5.2). The reset register allows assertion of the notSubReset signal. Similarly the analyse register allows assertion of the notSubAnalyse register. Both these registers use only bit 0 and are not readable. In addition, the card's circuitry (including the IMS T801) can be reset when a VME-bus master writes the appropriate data into the VIC mailbox registers. This feature allows a F-ROM booted card to be re-booted under the control of another VMEbus master card (see section 5.7).

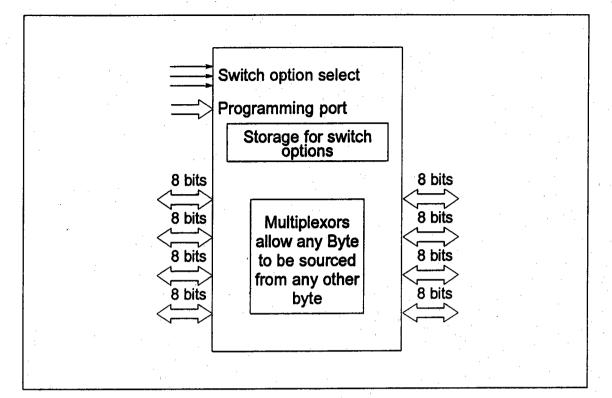

#### 2.1.12 The front panel

There is a push-button on the front panel (see figure 2.4). This resets all the card circuitry (including the IMS T801) and also produces a VMEbus reset if the card is configured as a slot 1 system controller.

The top LED (amber) lights when the IMS T801 error pin is asserted (please read section 2.1.11 about the error flag's behaviour).

The other three LED's light respectively when the IMS T801 makes a VMEbus master access; when another VMEbus master makes a slave access to the IMS B016's dual-access DRAM; and when the local bus is accessed by either the T801 or by the VMEbus. The brightness of the LED's indicates the density of cycles being performed. Note however, that the LED's are not intended to be balanced for brightness or calibrated with respect to each other.

Figure 2.4 Front panel showing LEDs

# 3 Installing the IMS B016

# 3.1 Configuring prior to installation

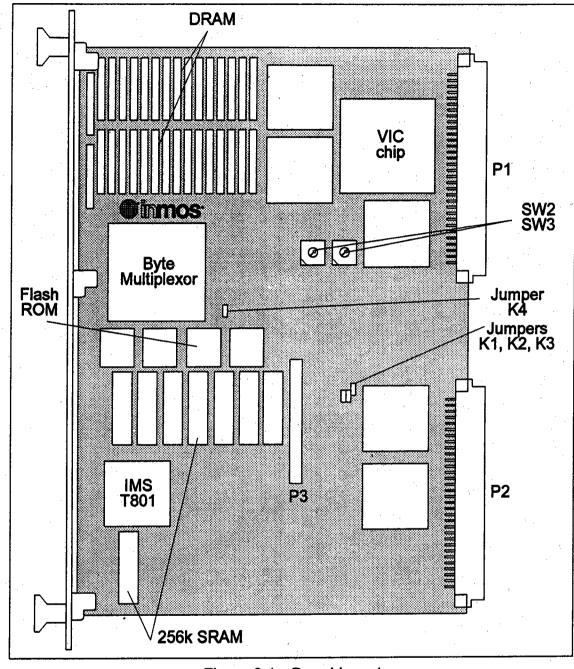

Since the IMS B016 is based around a VLSI controller, there are far fewer configuration switches and jumpers than are usually found on VMEbus cards. However, some functions are controlled by switches and jumpers.

17

The VMEbus address of the VIC VMEbus slave registers (mailboxes and so on) is selected by two hex switchest see figure 3.1). In setting the VMEbus address, a unique 8-bit binary number is being selected which will be compared with the VMEbus addresses. The upper four bits of this number are set by SW2 while the lower four bits are set by SW3 as small screwdriver or trim-tool can be used to rotate the pointers on SW2, 3. The pointer must be rotated to the desired hex character Here is an example setting:

The desired addresses are #DB00-#DBFF. This means that the 8-bit number to be compared is #DB. Its upper four bits are #D, its lower four bits are #B. Accordingly we set SW2 to "D" and SW3 to "B".

Care should be taken not to select a VMEbus slave decode address which conflicts with addresses which may be generated by the IMS 801 performing VMEbus *master* accesses (self-accesses). Note also that users should ensure that they do not have a situation where the slave registers occupy the same address region as another A16 slave on the bus.

The IMS T801's serial links can be set to work at two different speeds. For a link on one device to talk successfully to another device, they must be set to the same speed. Current technology allows link speeds of 10 or 20Mbits/s. Jumper K2 sets the link speeds for all four of the IMS T801's links. When K2 is fitted, the links are set to 10Mbits/s, otherwise they are set to 20Mbits/s.

The IMS B016 can perform the VMEbus 'Slot 1' system controller functions. To enable this function, fit jumper K3. K3 should only be fitted if the board is installed in slot 1 of a VMEbus rack.

Jumper site K4 has three pins. The jumper can be fitted either over the center pin and the left jin or over the center pin and the right pin. When programming the on-board E-ROMSsine programming voltage sharite persuabled by fitting K4 to Wates ments developed under Romssite not to be programmed extra-security, of their continue can be achieved by fitting K4 towards the IMS 1801. Table 3.1 summarises the jumper functions.

| ID | Function                                                                                                                                        |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| K1 | IMS T801 boots from link when fitted, otherwise from F–ROM                                                                                      |

| K2 | IMS T801 links are 10MBits/s when fitted, 20 MBits/s otherwise.                                                                                 |

| КЗ | When fitted, IMS B016 performs VMEbus slot 1<br>functions.<br>Do not fit unless the IMS B016 is installed in slot<br>1 of the VMEbus card-cage. |

| K4 | When not fitted F–ROM programming cannot occur. It must be fitted for F–ROM programming to function.                                            |

Table 3.1 Jumper functions

# 3.2 Handling

The unpacking note in the shipping carton will give details on how to unpack the IMS B016. Standard anti-static precautions should be observed since the IMS B016 contains MOS devices which are liable to static-discharge damage.

Some VMEbus compatible card-cages, notably SUN workstations, make use of the user-defined pins on connector P2. It is extremely important that the IMS B016

is not plugged into such a card-cage because permanent destruction of the IMS B016 and/or SUN can result. This restriction only applies to some slots in some kinds of SUN (and probably other card-cages) but users should always be aware of the danger. The solution required for the SUN is to use a special holding frame which isolates the P2 user-defined pins from the backplane. Such a frame is available from INMOS, part number IMS CA12.

# 3.3 Installing the IMS B016 for use with IMS S514C in a workstation

If you are using the IMS B016 as the gateway hardware from a SUN workstation to your transputer development system, INMOS board support software product IMS S514C is required. The S514C User Guide contains installation information specific to this application and should be consulted in preference to the following sections.

### 3.4 Installing the IMS B016 in a VMEbus card-cage

Before installing any board, first make sure that the power is turned off.

Inspect the VMEbus connectors for bent pins. Next, align the corners of the board with the ends of the card-guides. The component side of the board should be to the right. Slide the card home. If resistance is encountered the board is probably not aligned properly with the card guides. Now push firmly on the handles until the board is fully home. The front panel will fit against the card-cage. Lastly screw in the retaining bolts at the top and bottom of the front panel.

Remember that if you are using interrupts, the interrupt daisy-chain jumpers on the VMEbus should be configured correctly. Please consult the documentation for your VMEbus system to find out how to do this.

# 4 The IMS F008A support library

The IMS F008A is a package of software components, in INMOS ANSI C source format, that acts to document and to demonstrate the features of the IMS B016 VMEbus master card. It is written as a series of library modules whose routines focus on programming the devices and control registers of each sub-set of the board's functions.

21

Included with the library functions is an interactive monitor program which has command line options for setting up and exercising the I/O features and memory configuration. The monitor program comes in two configurations, one which is used via a development host interface, and another which can be burnt into the board EPROM and controlled via the serial ports.

For those who would like to use a Real-Time operating system in their IMS B016 application, the IMS F008A includes the source of a board support package for the VRTX32/T executive from Ready Systems Inc.

## 4.1 Package features

- Basic board setup procedures control address mapped access to VMEbus address space and byte-order swapping functions.

- VMEbus interface procedures control bus master and slave access and VME interrupt handling.

- RTC interface allows setting and reading of autonomous clock registers.

- Event library controls vectored interrupt handling capability.

- DUART support functions allow interrupt driven serial I/O over two channels.

- ROM support allows programming and reading of Flash ROM devices

- Command Line Interface allows easy experimentation and example application.

- VRTX32/T board support combines device access with pre-emptive scheduler regime.

- Compatible with INMOS ANSI C toolkit.

The following sections will describe the software installation and fully document the functions within each category together with their interfaces.

## 4.2 Installing and using IMS F008A

The release of the IMS F008A software is delivered on DOS format diskettes in 1.2Mb 5 1/4" format and 720Kbyte 3 1/2" format. To install and use the release about 2.5 Mb of disk space will be required.

To install the software:

- Insert Disk 1 of the release into your floppy disk drive.

- Run the command file 'install' on this diskette giving as parameters the letters of the source diskette drive and the destination hard disk drive. For example, if the floppy disk drive was identified as drive A and you wish to install the software on drive C then use the command

#### a:install a c

During the installation process a new directory tree is created, containing the software and associated files, at the top level of the destination drive.

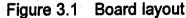

You will need an INMOS ANSI C toolkit (Dx214B or later) to use the IMS F008A software. Although it is delivered in DOS format, the code can be used in conjunction with a toolkit hosted on any machine. You will also need a transputer interface of some kind, either a card inserted in your host machine or a transputer development node accessible across the network. The subsystem and link connections that come from this interface must be connected to the appropriate connector pins of the IMS B016 card in order to boot programs onto the IMS B016 from a development system. It must be ensured that the card is configured to boot from a link as opposed to boot from ROM by fitting jumper K1. A typical development example is shown in figure 4.1.

#### Figure 4.1

The IMS B016 is cabled to the development system by connecting a link cable between one set of serial link pins on connector P2 and the link ouput from the devel-

opment system interface. Also connect a subsystem control cable between the services 'up' pins of connector P2 to the subsystem output from the development system interface. The nature of P2 connections varies on different VMEbus card cages but usually long wire-wrap tails are provided for pin rows A and C. Standard INMOS link connector cables can be plugged directly onto such pins provided the keyway is removed from the plug. As an example, using an IMS B008 interface installed into a PC development host, the link connection would typically appear on the 'pipetail' pins on the breakout board fitted to the IMS B008 rear connector. This should be connected to link 1 of a master IMS B016 (pins A5 through A9 of P2). Also connect the subsystem, labelled 'SS' on the breakout board, to pins C28 through C32 of P2. Ensure that the linkspeed selection of the interface board matches that of the IMS B016 configured using jumper K2.

With the equipment powered up, it should be possible to run a diagnostic tool such as 'ispy' on the transputer network and confirm the connections made. An example output is shown below:

| Using #200 ispy 2.33.1         |       |       |       |       |   |

|--------------------------------|-------|-------|-------|-------|---|

| <pre># Part rate Mb Bt [</pre> | Link0 | Link1 | Link2 | Link3 | ] |

| 0 T800c-20 0.05 0 [            | HOST  | 1:1   | 3:1   | • • • | ] |

| 1 T2 -17 0.88 1 [              | • • • | 0:1   | •••   | C004  | ] |

| 3 T801b-25 0.88 1 [            | • • • | 0:2   | • • • | • • • | ] |

If the diagnostic program does not report having found the processor on the IMS B016, re-check all the connections and linkspeed settings. Some of the example programs require two IMS B016 cards for operation. The link connections required between the cards are specified in the configuration files for those programs.

The rest of this discussion will assume access to a C toolkit and a connection to one or more IMS B016 cards. It will also assume familiarity with the transputer development tools and transputer terminology. It will also assume that the software is installed in a directory/drive called \$INSTALL.

To work with IMS F008A set your ISEARCH environment variable to include the paths \$INSTALL/include/, \$INSTALL/libs/ and \$INSTALL/clilib/. It should already contain references to the C toolkit include and library directories. Each directory of source should include one or more link control files and configuration source files which specify, in a host independent manner, the files required to build each target executable. There is also an existing makefile, but it may not be in a form suitable for your host environment. The toolkit utility program 'imakef' can be used to generate the appropriate makefile in all circumstances based on the search paths, link control files and configuration sources. It will also re-use the macro definitions and rules defined above the 'cut line' seen in the files. Once the the software installation is complete, 'imakef' should be run routinely to generate consistent makefiles for the local setup and environment.

23

## 4.3 Monitor code

Two monitor implementations are provided within the IMS F008A installation – one communicates via a host development system and the other is totally standalone, using the serial I/O facilities of the IMS B016. This second implementation can be programmed into the ROM of the IMS B016. In addition a number of examples of function usage are supplied that illustrate particular functions of VMEbus interface programming. The two sets of code can be combined if desired to give a comprehensive user experimentation interface across multiple boards.

The source code for the monitor implementations is in the files \$INSTALL/monitor/monitor.c and \$INSTALL/monitor/boardmon.c. See Appendix D for a description of the generic features of the monitor command language. The command set specific to the IMS B016 monitor is documented below:

To run a monitor program on the IMS B016, the following steps must be taken:

- Configure ISEARCH variable as previously described

- Change directory to \$INSTALL/F008/monitor.

- Make sure connections from development system to IMS B016 are known and correspond to the host link descriptions in the monitor.cfs configuration source file.

- On a PC development host run

imakef /d /c monitor.btl

which should complete without error or warning if the search paths have been set up correctly.

• Run a make utility referencing the makefile

make /x monitor.mak

All referenced code should compile and link to produce monitor.btl

- Use iserver to boot the executable code onto the IMS B016 iserver /ss /sb monitor.btl

- As the code runs, a prompt should appear

IMS B016 board monitor v1.0

B016>

A set of monitor commands can be run using the command statement source ``test.com''

If compiling the ROMable monitor code is desired, the code, link and configuration files are supplied as boardmon.c, boardmon.lnk, boardmon.cfs. Note that it will be necessary to delete the object file for the clilib module in order to

force a recompilation with a different compiler parameter. The binary file boardmon.bin that results from making this variant of the monitor code can be programmed into the ROM of the IMS B016 using the FLASH command of the hosted monitor.

The monitor CLI commands implemented for the IMS B016 are described below Note that commands that require host file system support are not included in the ROMable monitor implementation.

#### DISPLAY

#### DISPLAY <address><range>

Performs a formatted printout of memory words from the start address given for the specified number of bytes. Both Hex contents and an ASCII decode are shown. The address parameter defaults to the value of the BASEADDRESS variable and the range parameter defaults to the value of the RANGE variable. The command returns the value of the highest address reached.

#### SEARCH

#### SEARCH <address><range><value>

Searches for a given word value over a range of addresses. The range parameter specifies the length in bytes of the search area. All word values within this area are compared, including those that span word boundaries. The address parameter defaults to the value of the BASEADDRESS variable and the range parameter defaults to the value of the RANGE variable. The value parameter defaults to the value of the value of the RANGE variable.

FILL

#### FILL <address><range><value>

Fills a range of memory words with a specified value. The range parameter specifies the byte length of the filled area. The address parameter defaults to the value of the BASEADDRESS variable and the range parameter defaults to the value of the RANGE variable. The value parameter defaults to the value of the DATAVALUE variable.

#### COPY

#### COPY <address>range>rewaddress>

Copies memory contents from one address to another. The range parameter specifies the number of bytes to be copied. The copy is done in such as way as to avoid problems with overlapping areas of memory. The address parameter defaults to the value of the BASEADDRESS variable and the range parameter defaults to the value of the RANGE variable.

#### MAPRAM

#### MAPRAM <address>

Displays the IMS B016 mapram entry for a given address. The given address is truncated to the Megabyte boundary below the value given.

#### **MUXRAM**

#### MUXRAM <address>range>mapcode>rswop>wswop>