# IMS B431 Ethernet TRAM

Incorporating the IMS F006A support software.

INMOS is a member of the SGS-THOMSON Microelectronics Group

72 TRN 235 00

December 1991

Copyright INMOS Limited 1991. This document may not be copied, in whole or in part, without prior written consent of INMOS.

, Immos, IMS and OCCAM are trademarks of INMOS Limited.

\_\_\_\_\_

INMOS Limited is a member of the SGS-THOMSON Microelectronics Group.

72 TRN 235 00

December 1991

# Contents

| 1 | Introd | duction                                                                                      | 1 |

|---|--------|----------------------------------------------------------------------------------------------|---|

|   | 1.1    | Document structure                                                                           | 1 |

|   |        | 1.1.1 Conventions                                                                            | 1 |

|   | 1.2    | Background                                                                                   | 1 |

|   |        | 1.2.1 Prerequisites                                                                          | 2 |

| 2 | Instal | llation                                                                                      | 3 |

|   | 2.1    | IMS F006A software                                                                           | 3 |

|   | 2.2    |                                                                                              | 3 |

|   | 2.3    |                                                                                              | 4 |

|   |        | • • • •                                                                                      | 5 |

|   |        |                                                                                              | 6 |

| 3 | IMS F  | 006A overview                                                                                | 7 |

|   | 3.1    | Components                                                                                   | 7 |

|   | 3.2    |                                                                                              | 7 |

|   | 3.3    |                                                                                              | 8 |

|   | 3.4    |                                                                                              | 9 |

|   | 3.5    |                                                                                              | 9 |

|   | 0.0    |                                                                                              | 0 |

|   |        |                                                                                              | 0 |

| 4 | IMS F  | 006A libraries                                                                               | 3 |

|   | 4.1    | Interface procedures1                                                                        | 3 |

|   |        | • • • • • • • • • • • • • • • • • • • •                                                      | 4 |

|   |        |                                                                                              | 6 |

|   |        | 4.1.3 B431_Start_Ether() 1                                                                   | 8 |

|   |        | V                                                                                            | 9 |

|   |        | 4.1.5 B431_Tx_Packet2() 2                                                                    |   |

|   |        | 4.1.6 B431_Reset_Stats()                                                                     |   |

|   |        | 4.1.7         B431_Stop_Ether()         2           4.1.8         B431 Terminate()         2 |   |

|   |        | 4.1.9 B431_terninate()                                                                       |   |

|   |        | 4.1.10 B431_Waitfor_Event()                                                                  |   |

|   | 4.2    | Diagnostic procedures                                                                        |   |

|   |        | 4.2.1 B431 Internal Loopback() 2                                                             | 6 |

|   |        | 4.2.2 B431_External_Loopback() 2                                                             | 8 |

|   | 4.3    | IMS B431 Device Driver 2                                                                     | 9 |

|   |        | 4.3.1 Debugging support 3                                                                    |   |

|   | 4.4    | Using B431_Load_Driver() 3                                                                   | 3 |

| 5 | IEEE  | 802.3 C    | SMA/CD Ethernets                     | 35 |

|---|-------|------------|--------------------------------------|----|

|   | 5.1   | IEEE 80    | 02.3 CSMA/CD Ethernets               | 35 |

|   |       | 5.1.1      | Packet structure                     | 36 |

|   |       | 5.1.2      | CRC algorithm                        | 37 |

|   |       | 5.1.3      | Addressing                           | 38 |

|   |       | 5.1.4      | Retry algorithm                      | 38 |

|   |       | 5.1.5      | Ethernet statistics                  | 39 |

|   |       | 5.1.6      | Time domain reflectometer            | 40 |

|   |       | 5.1.7      | Heartbeat monitor                    | 41 |

|   |       | 5.1.8      | Performance                          | 41 |

| 6 | Detai | led hard   | dware description                    | 43 |

|   | 6.1   | Data str   | ructures                             | 43 |

|   |       | 6.1.1      | Buffer and descriptor ownership      | 45 |

|   |       | 6.1.2      | Data chaining                        | 45 |

|   | 6.2   | Softwar    | e structure                          | 45 |

|   | 6.3   | Initialisi | ng                                   | 47 |

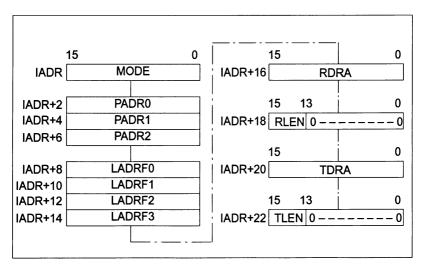

|   |       | 6.3.1      | The initialisation block             | 47 |

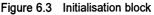

|   |       | 6.3.2      | CSR0–CSR3                            | 49 |

|   |       | 6.3.3      | Summary                              | 53 |

|   | 6.4   |            | ng                                   | 54 |

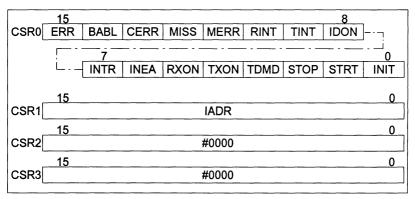

|   |       | 6.4.1      | The receive message descriptor       | 54 |

|   | 6.5   | Size and   | d number of receive buffers          | 57 |

|   | 6.6   | LANCE      | actions during packet reception      | 57 |

|   | 6.7   | Receive    | e driver actions                     | 58 |

|   |       | 6.7.1      | ERR is 0                             |    |

|   |       | 6.7.2      | ERR is 1                             |    |

|   |       | 6.7.3      | ENP is set (and ERR is clear)        | 59 |

|   | 6.8   |            | itting                               |    |

|   | 6.9   | The Tra    | nsmit message descriptor             | 60 |

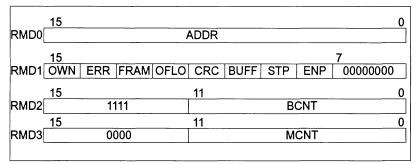

|   |       | 6.9.1      | Transmit message descriptor 0 (TMD0) | 60 |

|   |       | 6.9.2      | Transmit message descriptor 1 (TMD1) | 61 |

|   |       | 6.9.3      | Transmit message descriptor 2 (TMD2) | 61 |

|   |       | 6.9.4      | Transmit message descriptor 3 (TMD3) | 62 |

|   | 6.10  |            | actions during transmission          | 63 |

|   |       | 6.10.1     | Failure to transmit                  | 63 |

|   | 6.11  |            | I transmit driver                    | 64 |

|   |       | 6.11.1     | BUFF and ERR are clear               | 65 |

|   |       | 6.11.2     | BUFF is set                          |    |

|   |       | 6.11.3     | ERR is set                           | 65 |

|    | 6.12   | Interrupts, errors and error handling6 | 68 |

|----|--------|----------------------------------------|----|

|    |        | 6.12.1 Interrupt handling 6            | 68 |

|    |        | 6.12.2 Errors 6                        | 68 |

|    | 6.13   | Self Testing 7                         | 0  |

|    |        | 6.13.1 The MODE register 7             | 0  |

|    |        |                                        | 1  |

|    | 6.14   | IMS B431 TRAM engineering data 7       | '3 |

|    |        |                                        | '3 |

|    |        | ·····                                  | 3  |

|    |        |                                        | 6  |

|    |        | 6.14.4 Mechanical details 7            | 6  |

| 7  | Refer  | rences                                 | 7  |

| Ар | pendic | es                                     | 9  |

| A  | Direc  | tory structure                         | 1  |

| В  | Exam   | ple programs8                          | 3  |

|    | B.1    | IMS F006A example programs 8           | 3  |

|    |        | B.1.1 C Example                        | 3  |

|    |        |                                        | 7  |

\_\_\_\_\_

# Introduction

# 1.1 Document structure

This document is intended as a systems developers guide to using IMS F006A with the IMS B431 Ethernet TRAM. It is split into the following chapters.

Chapter 2 describes software and hardware installations.

Chapters 3 and 4 describe the software development environment and facilities provided by the IMS F006A. Use of the IMS B431 device driver in conjunction with the procedural interface libraries is discussed, and for each library procedure a full specification is given. ANSI C and OCCAM programmers should find that all the in-formation required to produce application software is contained entirely within this part of the manual.

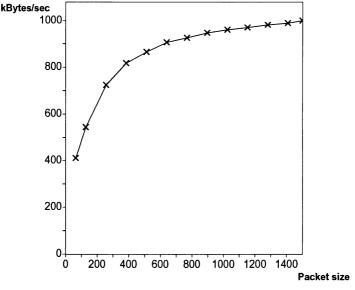

Chapter 5 provides background information on the IEEE 802.3 CSMA/CD networking standard (Ethernet). It describes packet format, addressing and the logical address and CRC algorithms. It also specifies the exact meaning and interpretation of the Ethernet statistics gathered by IMS F006A. Details of expected Ethernet performance levels are also provided.

Chapter 6 describes the IMS B431 Ethernet TRAM hardware in detail, it describes the Ethernet interface chip and how it is programmed. This section will only be of interest to programmers who wish to write their own device driver for the IMS B431 TRAM - where special requirements preclude the use of the IMS F006A software.

# 1.1.1 Conventions

Throughout this manual reference to software routines and constants provided in C and occam will be made using ANSI C syntax. Equivalent occam names may be derived by substituting occurrences of the '\_' (underscore) character with a '.' (period) character as appropriate.

# 1.2 Background

The IMS F006A is a software support package for the IMS B431 Ethernet TRAM. It is intended for those developers wanting to construct transputer systems incorporating IEEE 802.3 Ethernet attachment, but who are not interested in the low level programming details of the Ethernet interface hardware.

The IMS F006A software consists of a device driver for the IMS B431 Ethernet TRAM and procedural interface libraries for ANSI C and Occam which access the device driver via a transputer channel pair. This facilitates the creation of transputer programs to establish and engage in packet level communication on IEEE 802.3 Ethernet based local area networks (LANs).

IMS F006A is compatible with INMOS software development toolsets. Systems developers incorporate IMS F006A with their own application software using an appropriately selected toolset.

## 1.2.1 Prerequisites

In order to develop with IMS F006A the following (minimum) environment is required:-

#### Hardware

- IBM PC/AT or compatible personal computer

- IMS B008 IBM PC/AT TRAM Motherboard

- IMS B431 Ethernet TRAM (Size 2)

- A compute TRAM such as the IMS B404 (Size 2)

#### Software

IMS D7214 ANSI C Toolset for IBM PC/AT

#### or

IMS D7205 occam 2 Toolset for IBM PC/AT

# 2 Installation

# 2.1 IMS F006A software

The installation of IMS F006A requires at least 800 kBytes of free disk space be available on the host computer system hard disk.

To install IMS F006A from floppy disk drive  $\mathbf{A}$ : onto hard disk drive C: of an IBM PC/AT or compatible computer, proceed as follows:-

- 1 Insert the floppy disk into floppy disk drive A:.

- 2 Change the current working directory to C: \.

- 3 At the operating system command line, type a:install a c.

- 4 Respond as appropriate to prompts made by the install program.

# 2.2 IMS B431 Ethernet TRAM

Since the IMS B431 contains CMOS components, all normal precautions to prevent static damage should be taken.

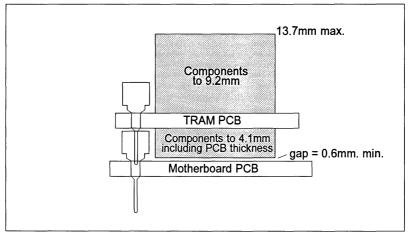

The IMS B431 may be supplied with spacer pin strips attached to the TRAM pins on the underside of the board. These spacers perform two functions. Firstlythey help to protect the TRAM pins during transit. Secondly, they can be used to space the TRAMs off the motherboard. If there are no components mounted on the motherboard TRAM slot, then the spacer strips should be removed before the TRAM is inserted.

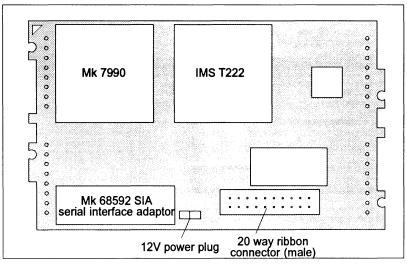

Plug the IMS B431 into the motherboard. Where the IMS B431 is being used with an INMOS motherboard, the yellow triangle marking pin 1 on the IMS B431 (see Figure 2.1) should be aligned with the silk screened triangle that appears in the corner of the appropriate TRAM slot.

Should it be necessary to unplug the IMS B431, it is advised that it is gently levered out while keeping it as flat as possible. As soon as the IMS B431 is removed, the spacer pin strips should be refitted to the TRAM to protect the pins.

Figure 2.1 IMS B431 board layout

# 2.3 Connecting to Ethernet (10BASE5)

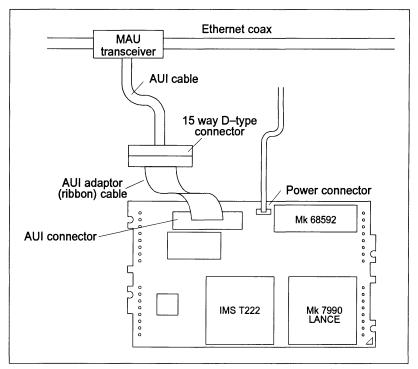

In an Ethernet (10BASE5) system, nodes are connected to the Ethernet coax by means of an *media access unit* (MAU) and an *attachment unit interface* (AUI) cable. The MAU is a specially designed housing incorporating a transceiver device. The MAU is clamped to the Ethernet coax; it penetrates the coax making contact with the signal conductor without interrupting traffic on the LAN. The node is connected to the MAU transceiver by means of an AUI cable. Ethernet supports a maximum cable length (without repeaters) of 500 metres.

When connecting the IMS B431 to an Ethernet system, the AUI connector on the IMS B431 is used to connect to a separate MAU. Figure 2.2 shows how the IMS B431 should be connected to an Ethernet system. It is intended that the 15-way D-type connector should be mounted in a suitable bulkhead or front panel on the equipment into which the IMS B431 is installed.

Figure 2.2 Connecting the IMS B431 to an Ethernet system

## 2.3.1 AUI connection

To reduce the overall height of the IMS B431, a 16-way male header is used instead of the standard 15-way D-type; the pinout of this connector is defined in table 2.1. A short length of adaptor cable is supplied for connection to a standard AUI cable. AUI cables should have a shielded, twisted pair for each signal or power pair; each pair should have a characteristic impedance of  $78 \pm 5\Omega$ .

The RX  $\pm$ , TX  $\pm$  and COLL  $\pm$  signals on the AUI connector are transformer isolated.

| Name  | Function       | Pin No. |

|-------|----------------|---------|

| COLL+ | collision pair | 4       |

| COLL- |                | 3       |

| TX+   | transmit pair  | 6       |

| ТХ–   |                | 5       |

| RX+   | receive pair   | ' 10    |

| RX–   |                | 9       |

| +12V  | power pair     | 11      |

| 0V    |                | 12      |

| GND   | shield         | 1,2     |

Table 2.1 AUI connector pinout

#### 2.3.2 AUI power

The Ethernet specification requires that the AUI cable must supply +12V at 0.5A to the MAU. Since there is no +12V supply on the IMS B431, this must come from an external power source. A +12V power source capable of supplying 0.5A should be connected to the power connector on the IMS B431. The IMS B431 routes power from this connector to the AUI connector. The pinout of the power connector is shown in table 2.2.

| Name    | Function       | Pin No. |

|---------|----------------|---------|

| +12V In | AUI power pair | 1       |

| 0V In   |                | 2       |

Table 2.2 Power connector pinout

Pins 1 and 2 connect directly to the AUI connector power pair pins.

# 3 IMS F006A overview

# 3.1 Components

IMS F006A consists of the following components:-

- IMS B431 device driver

- ANSI C and occam interface libraries

- Include files

- Example programs and configuration files

- Source code of interface libraries

# 3.2 IMS B431 device driver

The IMS B431 device driver runs on the IMS B431 Ethernet TRAM and is responsible for:-

- 1 Controlling the Ethernet interface hardware.

- 2 Performing diagnostic tests upon the Ethernet interface hardware and buffer memory areas.

- 3 Collecting and making available statistics concerning the operation and performance of the Ethernet interface.

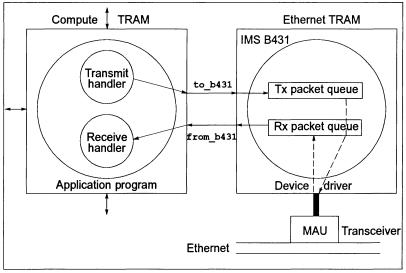

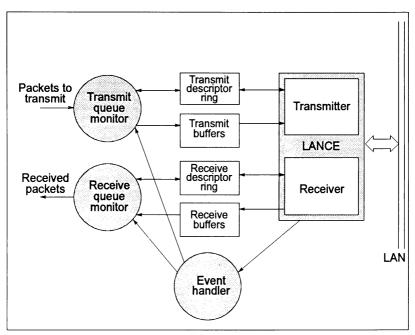

The device driver's primary role is to provide a buffered interface for transmitting and receiving IEEE 802.3 structured Ethernet packets. Packets sent to the device driver for transmission are buffered in a first in first out (fifo) queue where they wait to be transmitted. Similarly, packets received by the Ethernet interface are queued until read. Two transputer channels connect the device driver to application software running on an adjacent transputer. Packets are sent to the device driver by calling a procedure from the IMS F006A interface library with the channel to the device driver passed in as a parameter. In the other direction, packets are received by calling a different procedure to wait for their arrival.

Typically, application software will fork into two parallel processes to handle this concurrent activity. The arrangement is shown in the following diagram, one process is responsible for transmitting packets while the other handles their reception.

72 TRN 235 00

Figure 3.1 Software elements for active ethernet

Statistics concerning operation of the Ethernet interface are gathered by the device driver. They provide useful information relating to the performance and loading characteristics of the Ethernet network. See Section 5.1.5 for a description of these values. Application programs may request the current set of accumulated statistics, from the device driver, at any time.

In order to establish confidence in the correct operation of the Ethernet interface the device driver may be requested to perform diagnostic tests on the hardware it controls. Testing occurs by transmitting test packets which are looped backed either within the Ethernet interface hardware itself or via the attached network. An additional diagnostic feature, which may be enabled during Ethernet interface initialisation, tests for correct operation of the transmit and receive packet buffer memory.

# 3.3 IMS F006A interface libraries

The IMS F006A ANSI C and occam interface libraries contain an equivalent set of procedures. Procedures are provided to:-

- Initialise, start or stop the Ethernet interface

- Perform diagnostic loopback tests

- Transmit or receive IEEE 802.3 Ethernet packets

- Request or reset Ethernet statistics

- Download the IMS B431 device driver via an EDGE link

Details of the interaction between the IMS B431 device driver and client application programs are hidden by the use of these procedures. Application programs supply parameters which are packaged up and sent to the device driver for processing, data received in the opposite direction is unpacked and returned to the application program via a suitable procedure call.

The procedures for transmitting and receiving Ethernet packets are designed such that they may be called from two separate, parallel, processes. In ANSI C this is achieved by forking a new process with the ProcAlloc() and ProcRun() functions, while in occam the PAR construct achieves the same effect.

# 3.4 Example programs and source code

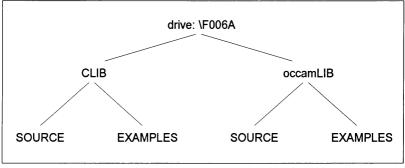

Example programs written in ANSI C and occam that demonstrate the use of the IMS F006A interface libraries are provided in the directories \F006A\CLIB\EXAMPLES and \F006A\OCCAMLIB\EXAMPLES. Configuration files are also included which describe a fairly typical transputer network consisting of a single IMS B431 Ethernet TRAM and a general purpose compute TRAM (which executes each example program). These can easily be modified to suite more specifc hardware if necessary.

Source code of both the ANSI C and occam interface libraries are provided in the directories \F006A\CLIB\SOURCE and \F006A\OCCAMLIB\SOURCE respectively. Most of the procedures are quite simple. The source code is supplied to demonstrate the low level interaction required to control the device driver from an adjacent transputer, this should allow similar interfaces to be produced for other, non-INMOS toolset, environments.

The files imsb431.h and imsb431.inc, also located in the source directories, contain ANSI C and occam definitions of a constant byte array. This is a bootable version of the IMS B431 device driver. Copying the contents of the array down a transputer link connected to a previously reset IMS B431 Ethernet TRAM will boot the TRAM with device driver software. This too allows alternative schemes to be developed for using the IMS B431 in other systems environments.

# 3.5 Environments

Transputer programs that incorporate the IMS F006A software and target a particular transputer network topology are constructed, using INMOS toolset utilities, in the conventional manner:- top level programs for each transputer in the target network are compiled, linked and configured into a single bootable file for the network. No software, other than the IMS B431 device driver, may execute on the IMS B431 TRAM. The device driver is supplied in linked unit format and should be placed on each IMS B431 TRAM in the network using the configurer tool. Because the device driver uses a single transputer link each IMS B431 TRAM will be physically connected to only one other transputer in the network. The remainder of the network is configured to run application software.

A minimal target transputer system will consist of at least an IMS B431 Ethernet TRAM and a compute TRAM. Larger systems may contain any number and combination of Ethernet and compute TRAMs, depending on the intended application. Embedded systems will probably also have a ROM TRAM to act as a bootstrap master, this will contain code to be booted into the transputer network at system startup time. IMS F006A, when used in conjunction with an INMOS toolset, permits the development of both embedded and hosted systems.

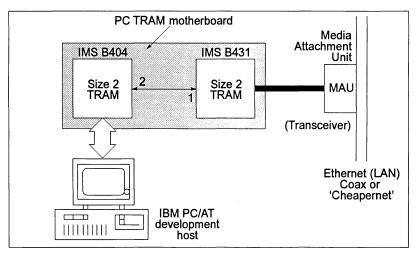

## 3.5.1 Development Environment

A typical hosted development environment is shown in the diagram below. It consists of an IBM PC/AT or compatible host computer installed with a TRAM motherboard, the motherboard is fitted with an IMS B431 Ethernet TRAM and a compute TRAM. The compute TRAM is used to run INMOS tools during development and the application program during test phases. The Ethernet TRAM executes the device driver. Interaction between the device driver and application program occurs over the hard link connecting both TRAMs.

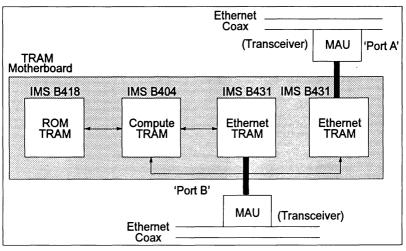

Figure 3.2 Example development environment

### 3.5.2 Target System Environment

The following diagram shows an example embedded system. The ROM TRAM contains configured application code including copies of the IMS B431 device driver which it boots into the transputer network. In this example the target transputer network consists of a single compute TRAM and two IMS B431 Ethernet TRAMs.

Figure 3.3 Example embedded system featuring IMS B431

# 4 IMS F006A libraries

To develop with the IMS F006A interface libraries:

## ANSI C programmers should:-

- 1 Add \F006A\; \F006A\CLIB\; to the ISEARCH environment variable.

- 2 #include the header file b431io.h. Also include b431test.h if using the diagnostic loopback functions provided with the ANSI C interface library.

- 3 Link against the library b431.1ib.

- 4 Configure the target transputer network:- place the IMS B431 device driver on the IMS B431 TRAM and application software on other TRAMs.

## occam programmers should:-

- 1 Add \F006A\;\F006A\OCCAMLIB\; to the ISEARCH environment variable.

- 2 **#INCLUDE** the header file b431io.inc. Also include b431test.inc if using the diagnostic loopback procedures provided with the occam interface library.

- 3 #USE and link against the library B431.LIB.

- 4 Configure the transputer network:- place the IMS B431 device driver on the IMS B431 TRAM and application software on other TRAMs.

# 4.1 Interface procedures

This section describes the procedures used to interact with the IMS B431 device driver. Interaction with the device driver occurs in one of two modes, which reflect the state of the Ethernet interface it controls, as follows:-

- The Ethernet interface is inactive (stopped), it ignores all activity on the Ethernet network. Procedures are provided to initialise and then start the interface. The device driver arranges for the Ethernet interface to be in this state at startup time.

- The Ethernet interface is active (started), packet I/O proceeds concurrently. Procedures are provided to transmit and receive packets, request Ethernet statistics or revert the interface to the inactive state.

The Ethernet interface must be initialised before it can be started. Once started, the application may fork into the separate parallel processes, described earlier, to handle packet I/O. The device driver will attempt to deliver packets it receives from

72 TRN 235 00

the Ethernet interface on the from b431 channel, B431\_Waitfor\_Event() should be called to wait for and receive them. B431\_Tx\_Packet1() or B431\_Tx\_Packet2() are used to transmit packets by sending them to the device driver along the to b431 channel. B431\_Waitfor\_Event() is also used to accept other events from the device driver such as notification of error conditions or Ethernet statistics. The Ethernet interface may be subsequently stopped, in order to alter initialisation parameters, or during software termination.

## 4.1.1 B431\_Init\_Normal()

## **Description:**

Initialise the Ethernet interface for normal operation (as opposed to diagnostic loopback operation).

This sets the physical address and logical address filter (multicast address group) for the Ethernet interface. Packets transmitted by the Ethernet interface will carry a source address equal to the physical address assigned by calling this procedure. Packets will be received if they carry a destination address equal to either the physical address or a multicast destination address matched by the logical address filter (or a broadcast address). Section 5.1.3 describes Ethernet addressing in detail.

Normal operation can be modified by enabling a number of optional mode flags.

Once initialised, the Ethernet interface can be started, see B431\_Start\_Ether().

C:

| int B431_Init_Normal( |                                                                 |  |

|-----------------------|-----------------------------------------------------------------|--|

| Channel               | *from_b431,                                                     |  |

| Channel               | *to_b431,                                                       |  |

| const unsigned char   | <pre>physical_address[PHYSICAL_ADDRESS_SIZE] ,</pre>            |  |

| const unsigned char   | <pre>logical_address_filter[LOGICAL_ADDRESS_FILTER_SIZE],</pre> |  |

| const long int        | <pre>mode_flags )</pre>                                         |  |

occam:

| PROC B431.Init.Normal(                |                         |

|---------------------------------------|-------------------------|

| CHAN OF ANY                           | from.b431,              |

|                                       | to.b431,                |

| VAL [PHYSICAL.ADDRESS.SIZE] BYTE      | physical.address,       |

| VAL [LOGICAL.ADDRESS.FILTER.SIZE]BYTE | logical.address.filter, |

| VAL INT                               | mode.flags,             |

| BYTE                                  | result )                |

|                                       |                         |

| Parameter              | Comments                                          |

|------------------------|---------------------------------------------------|

| from_b431              | Channel from the B431 device driver               |

| to_b431                | Channel to the B431 device driver                 |

| physical_address       | Physical address of the Ethernet interface        |

| logical_address_filter | Logical address filter for the Ethernet interface |

| mode_flags             | Mode flags bit mask                               |

#### Mode flags:

mode\_flags is a bit mask. Bits are set to enable optional Ethernet interface functions, or to modify the normal operating mode. The following bit masks are defined:-

| MEMORY_CHECK      | Enable execution of the packet buffer memory check                                                                                  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| PROMISCUOUS_RX    | Enable promiscuous mode packet reception. All packets will be received, regardless of their destination address, see Section 5.1.3. |

| MONITOR_HEARTBEAT | Enable heartbeat monitoring, see Section 5.1.7.                                                                                     |

| DISABLE_TX_CRC    | Disable automatic transmit packet CRC field generation, see Section 5.1.2.                                                          |

| DISABLE_TX_RETRY  | Disable transmitter retries, see Section 5.1.4.                                                                                     |

#### Return codes:

result contains the completion code for B431.Init.Normal(). It is returned by B431\_Init\_Normal().

A value of INIT\_SUCCESS indicates normal successful completion. Other result codes indicate a failure to initialise the Ethernet interface as follows:-

| INIT_NOT_STOPPED     | The Ethernet interface is active. It should be in the stopped state, see B431_Stop_Ether() |

|----------------------|--------------------------------------------------------------------------------------------|

| INIT_HARDWARE_FAILED | The Ethernet interface hardware failed to initialise correctly                             |

| INIT_MEMORY_FAULT    | A memory fault was discovered while executing the packet buffer memory check.              |

### Notes:

If automatic CRC field generation is disabled then packets supplied to the device driver for transmission should contain a user supplied CRC field. Section 5.1.2 describes the algorithm specified in the IEEE 802.3 CSMA/CD Ethernet standard for calculating the CRC value.

The heartbeat monitor function should only be enabled if the Media Attachment Unit (MAU) generates the heartbeat signal. This is usually a jumper configured option within the MAU (transceiver) box.

72 TRN 235 00

# 4.1.2 B431 Init Loopback()

### Description:

Initialise the Ethernet interface for loopback operation. When operating in loopback mode the Ethernet interface will return any self addressed transmit packets as received packets. This can occur within the Ethernet interface itself:internal loopback, or via the network:- external loopback.

Once initialised. the Ethernet interface can be started. see B431 Start Ether().

Loopback operation is intended for diagnostic purposes only. Application programs will normally use the supplied diagnostic procedures, described in Section 4.2, to perform diagnostic tests and will not call this procedure. It is provided in the interface library for users that wish to write their own diagnostic software.

C:

| int B431_Init_Loopback( |                                                     |  |

|-------------------------|-----------------------------------------------------|--|

| Channel                 | *from_b431,                                         |  |

| Channel                 | *to_b431,                                           |  |

| const unsigned char     | <pre>physical_address[PHYSICAL_ADDRESS_SIZE],</pre> |  |

| const long int          | mode_flags )                                        |  |

occam:

VAL INT

BYTE

PROC B431.Init.Loopback( CHAN OF ANY

from.b431, to.b431, VAL [PHYSICAL.ADDRESS.SIZE]BYTE physical.address, mode.flags,

result )

| Parameter        | Comments                                   |

|------------------|--------------------------------------------|

| from_b431        | Channel from the B431 device driver        |

| to_b431          | Channel to the B431 device driver          |

| physical_address | Physical address of the Ethernet interface |

| mode_flags       | Mode flags bit mask                        |

## Mode flags:

mode\_flags is a bit mask. Bits are set to enable optional Ethernet interface functions, or to modify the loopback operating mode. The following bit masks are defined:-

| MEMORY_CHECK      | Enable execution of the packet buffer memory<br>check                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| INTERNAL_LOOPBACK | Enable internal loopback mode, default is external mode                                                                                       |

| FORCE_COLLISION   | Enable transmit collisions, packets will be forced to collide. This tests the collision detection logic. Only valid in internal loopback mode |

| MONITOR_HEARTBEAT | Enable heartbeat monitoring, see Section 5.1.7.                                                                                               |

| DISABLE_TX_CRC    | Disable automatic transmit packet CRC field gener-<br>ation, see Section 5.1.2.                                                               |

| DISABLE_TX_RETRY  | Disable transmitter retries, see Section 5.1.4.                                                                                               |

#### Return codes:

result contains the completion code for B431.Init.loopback(). It is returned by B431\_Init\_loopback().

A value of INIT\_SUCCESS indicates normal successful completion. Other result codes indicate a failure to initialise the Ethernet interface as follows:-

| INIT_NOT_STOPPED     | The Ethernet interface is active. It should be in the stopped state, see B431_Stop_Ether() |

|----------------------|--------------------------------------------------------------------------------------------|

| INIT_HARDWARE_FAILED | The Ethernet interface hardware failed to initialise correctly                             |

| INIT_MEMORY_FAULT    | A memory fault was discovered while executing the packet buffer memory check               |

#### Notes

If automatic CRC field generation is disabled then packets supplied to the device driver for transmission should contain a user supplied CRC field. Section 5.1.2 describes the algorithm specified in the IEEE 802.3 CSMA/CD Ethernet standard for calculating the CRC value.

The heartbeat monitor function should only be enabled if the Media Attachment Unit (MAU) generates the heartbeat signal. This is usually a jumper configured option within the MAU (transceiver) box.

# 4.1.3 B431\_Start\_Ether()

## **Description:**

Start the Ethernet interface. Packet I/O will be enabled.

The Ethernet interface must be initialised before it is started, see B431\_Init\_Normal(). C: int B431\_Start\_Ether( Channel \*from\_b431 Channel \*to\_b431)

occam:

| PROC | B43 | 1.St | art.Ether( |

|------|-----|------|------------|

| CHAN | OF  | ANY  | from.b431, |

|      |     |      | to.b431,   |

| BYTE |     |      | result )   |

| Parameter | Description                         |

|-----------|-------------------------------------|

| from_b431 | Channel from the B431 device driver |

| to_b431   | Channel to the B431 device driver   |

### **Return codes:**

result contains the completion code for B431.Start.Ether(). It is returned by B431\_Start\_Ether().

A value of **START\_SUCCESS** indicates normal successful completion. Other result codes indicate a failure to start the Ethernet interface as follows:-

NO\_INIT\_DONE The Ethernet interface has not been initialised

### Notes:

Once the Ethernet interface has started, the channels connecting the application program to the B431 device driver (to\_b431 and from\_b431) become asynchronous. Commands to the device driver are issued by calling procedures with the to\_b431 channel only. Eg:- B431\_Tx\_Packet1() or B431\_Ether\_Stats(). The device driver will respond (if necessary) by sending results on from\_b431. B431\_Waitfor\_Event() is used to wait for and decode events generated by the device driver on this channel, three types of event can be expected:-

- 1 Received packets.

- 2 Report of an error condition.

- 3 A response to B431\_Stop\_Ether(), B431\_Ether\_Stats() or B431\_Terminate().

Application software should fork into two separate parallel processes after calling B431\_Start\_Ether(). One process will be responsible for transmitting packets

and sending commands to the device driver, the other will continuously loop calling B431\_Waitfor\_Event() to receive packets or command responses. Source code examples of this are described in section B.1.1 for ANSI C, and section B.1.2 for occam.

# 4.1.4 B431\_Tx\_Packet1()

**Description:**

Transmit an Ethernet packet. The packet is sent to the device driver where it is buffered and then transmitted on the Ethernet. Packets are buffered in a first in first out queue (fifo) where they wait to be transmitted. If the queue fills up then this procedure will block until there is sufficient space for the new packet. This behaviour does not affect the receive packet queue, which will continue to supply packets, if any are received. See B431\_Waitfor\_Event().

C:

| <pre>void B431_Tx_Packet1 (</pre> |                                     |

|-----------------------------------|-------------------------------------|

| Channel                           | *to_b431,                           |

| const unsigned char               | <pre>*ethernet_packet,</pre>        |

| const int                         | <pre>ethernet_packet_length )</pre> |

occam:

```

PROC B431.Tx.Packet1(

CHAN OF ANY to.b431,

VAL []BYTE ethernet.packet)

```

| Parameter             | Description                       |

|-----------------------|-----------------------------------|

| to_b431               | Channel to the B431 device driver |

| ethernet_packet       | Ethernet packet                   |

| ethernt_packet_length | Packet length                     |

Notes:

ethernet\_packet should contain a header (see Section 5.1.1). This will contain a destination address, source address and type length field. The source address should correspond to the address assigned to the Ethernet interface when initialised. If the Ethernet interface was initialised with transmit CRC field generation disabled then ethernet\_packet should also contain a user supplied CRC field.

In normal operation the minimum packet length is MIN\_PACKET\_LENGTH (64) bytes, and the maximum length is MAX\_PACKET\_LENGTH (1518) bytes. These values include the leading 14 byte packet header and trailing 4 byte CRC field. If automatic CRC field generation is disabled then the minimum and maximum packet lengths will be 4 bytes less. Packets containing less than the minimum number of bytes will be padded automatically to the minimum length.

# 4.1.5 B431\_Tx\_Packet2()

## Description:

Transmit an Ethernet packet. The packet header and data segments are sent to the device driver where they are assembled into a complete packet, buffered, and then transmitted on the Ethernet. The device driver will insert the source Ethernet address into the packet header automatically, this is the address assigned to the Ethernet interface during initialisation. Packets are buffered in a first in first out queue (fifo) where they wait to be transmitted. If the queue fills up then this procedure will block until there is sufficient space for the new packet. This behaviour does not affect the receive packet queue, which will continue to supply packets, if any are received. See B431\_Waitfor\_Event().

C:

| <pre>void B431_Tx_Packet2(<br/>Channel<br/>const unsigned char<br/>const short int<br/>const unsigned char<br/>const int</pre> | <pre>*to_b431,<br/>destination_address[PHYSICAL_ADDRESS_SIZE],<br/>type_length_field,<br/>*packet_data[],<br/>packet_data_length)</pre> |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| occam:                                                                                                                         |                                                                                                                                         |

| PROC B431.Tx.Packet2(                                                                                                          |                                                                                                                                         |

| CHAN OF ANY                                                                                                                    | to.b431,                                                                                                                                |

| VAL [PHYSICAL.ADDRESS                                                                                                          | S.SIZE]BYTE destination.address,                                                                                                        |

| VAL INT16                                                                                                                      | type.length.field,                                                                                                                      |

| VAL []BYTE                                                                                                                     | packet.data )                                                                                                                           |

|                                                                                                                                |                                                                                                                                         |

| Parameter           | Description                                                                                                        |

|---------------------|--------------------------------------------------------------------------------------------------------------------|

| to_b431             | Channel to the B431 device driver                                                                                  |

| destination_address | Destination Ethernet address                                                                                       |

| type_length_field   | Type or length value, the least significant byte corresponds to the most significant byte of the type length field |

| packet_data         | Packet data                                                                                                        |

| packet_data_length  | Data length                                                                                                        |

Notes:

If the Ethernet interface was initialised with transmit CRC field generation disabled then packet\_data should also contain a user supplied CRC field.

In normal operation the minimum packet length is MIN\_PACKET\_LENGTH (64) bytes, and the maximum length is MAX\_PACKET\_LENGTH (1518) bytes. These values include the leading 14 byte packet header and trailing 4 byte CRC field. If

automatic CRC field generation is disabled then the minimum and maximum packet lengths will be 4 bytes less. Packets containing less than the minimum number of bytes will be padded automatically to the minimum length.

## 4.1.6 B431\_Reset\_Stats()

#### **Description:**

Reset the Ethernet statistics. The device driver will clear (reset to 0) it's accumulated Ethernet statistics.

C:

```

void B431_Reset_Stats( Channel *to_b431 )

```

occam:

PROC B431.Reset.Stats (CHAN OF ANY to.b431 )

| Parameter | Description                       |

|-----------|-----------------------------------|

| to_b431   | Channel to the B431 device driver |

## 4.1.7 B431\_Stop\_Ether()

#### **Description:**

Stop the Ethernet interface. Packet transmission and reception will cease and the Ethernet interface will be disabled. Any queued transmit or receive packets will be discarded. When the Ethernet interface has stopped the device driver will send an acknowledge, B431\_Waitfor\_Event() should be called to receive the acknowledgement. Once stopped the Ethernet interface can be re-initialised or re-started.

C:

void B431\_Stop\_Ether( Channel \*to\_b431 )

occam:

PROC B431.Stop.Ether( CHAN OF ANY to.b431 )

| Parameter | Description                       |

|-----------|-----------------------------------|

| to_b431   | Channel to the B431 device driver |

# 4.1.8 B431\_Terminate()

## **Description:**

Terminate the B431 device driver. The device driver will acknowledge and then terminate. B431\_Waitfor\_Event() should be called to receive the acknowledgement. Once terminated no further interaction with the device driver is possible.

C:

void B431\_Terminate( Channel \*to\_b431 )

occam:

PROC B431.Terminate( CHAN OF ANY to.b431 )

| Parameter | Description                       |

|-----------|-----------------------------------|

| to_b431   | Channel to the B431 device driver |

## 4.1.9 B431\_Ether\_Stats()

#### **Description:**

Request the Ethernet statistics. The device driver will return it's current set of accumulated Ethernet statistics, B431\_Waitfor\_Event() should be called to receive them. Section 5.1.5 describes the statistics returned.

C:

void B431\_Ether\_Stats( Channel \*to\_b431 )

occam:

PROC B431.Ether.Stats (CHAN OF ANY to.b431 )

| Parameter | Description                       |

|-----------|-----------------------------------|

| to_b431   | Channel to the B431 device driver |

## 4.1.10 B431\_Waitfor\_Event()

### **Description:**

Wait for an Ethernet interface event. This procedure is called to wait for and decode events from the device driver when the Ethernet interface is active (see B431\_Start\_Ether()). The device driver will generate three types of event:-

- 1 Received packets

- 2 Report of an error condition

- 3 A response to B431\_Stop\_Ether(), B431\_Ether\_Stats() or B431\_Terminate().

**B431\_Waitfor\_Event()** is designed to be called from a process primarily responsible for handling the reception of Ethernet packets. Another, parallel process, will handle the transmission of packets independently of this.

C:

| int B431_Waitfor | Event (                             |

|------------------|-------------------------------------|

| Channel          | *from_b431,                         |

| Channel          | <pre>*cancel,</pre>                 |

| ETHER_STATS      | <pre>*ethernet_stats,</pre>         |

| unsigned char    | <pre>*ethernet_packet,</pre>        |

| int              | <pre>*ethernet_packet_length,</pre> |

| int              | *error_code,                        |

| unsigned char    | <pre>*failed_packet_data )</pre>    |

occam:

| PROC B431.Waitfor.Event(     |                                    |

|------------------------------|------------------------------------|

| CHAN OF ANY                  | from.b431,                         |

| CHAN OF BYTE                 | cancel,                            |

| [ETHER.STATS.SIZE] INT32     | ethernet.stats,                    |

| [MAX . PACKET . LENGTH] BYTE | ethernet.packet,                   |

| INT                          | <pre>ethernet.packet.length,</pre> |

|                              | error.code,                        |

| [FAILED.PACKET.LENGTH]BYT    | Efailed.packet.data,               |

| BYTE                         | result )                           |

|                              |                                    |

| Parameter              | Description                                                                                                                                                                     |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| from_b431              | Channel from the B431 device driver                                                                                                                                             |

| cancel                 | Cancel channel, used to force completion of the procedure call. Sending any byte value on this channel will cause the procedure to return immediately                           |

| ethernet_stats         | Ethernet statistics, an unsigned long integer<br>structure (INT32 array in occam) that contains<br>accumulated Ethernet statistics. Only valid if<br>result is B431_ETHER_STATS |

| ethernet_packet        | Received Ethernet packet, includes trailing<br>CRC field. Only valid if result is<br>B431_RX_PACKET                                                                             |

| ethernet_packet_length | Packet length                                                                                                                                                                   |

| error_code             | Error code, describes an error event. Only valid<br>if result is B431_ERROR_REPORT                                                                                              |

| failed_packet_data     | Failed packet data, contains the first<br>FAILED_PACKET_LENGTH bytes of a failed<br>transmit packet. Only valid if error_code is<br>ERROR_TX_PACKET_FAILED                      |

## **Return codes:**

result contains the completion code for B431.Waitfor.Event(). It is

returned by B431\_Waitfor\_Event().

The result value indicates the reason for completion, as follows:-

| Parameter           | Description                                                                                                                                                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B431_WAIT_CANCELLED | Indicates forced completion with the cancel channel                                                                                                                  |

| B431_TERMINATE      | Acknowledgement of device driver termination. See<br>B431_Terminate(), B431_Waitfor_Event()<br>should not be called again                                            |

| B431_STOP_ETHER     | Acknowledgement of an Ethernet interface stop re-<br>quest. See B431_Stop_Ether()                                                                                    |

| B431_ETHER_STATS    | Acknowledgement of a request for Ethernet statis-<br>tics. See B431_Ether_Stats(), ether-<br>net_stats will contain the current, accumulated,<br>Ethernet statistics |

| B431_RX_PACKET      | Indicates reception of an Ethernet packet. ether-<br>net_packet and ethernet_packet_length<br>will hold the packet and length of packet respectively                 |

| B431_ERROR_REPORT   | Indicates an occurence of an internal or Ethernet re-<br>lated error condition. error_code will contain a<br>reason code, see below for these                        |

error\_code will contain an error reason code (if result is set to B431\_ERROR\_REPORT), as follows:-

| Parameter                 | Description                                                                                                                                                                            |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ERROR_NO_ERROR            | No error                                                                                                                                                                               |

| ERROR_TX_PACKET_FAILED    | Device driver failed to transmit a packet after the<br>maximum number of transmit retries was at-<br>tempted. The first FAILED_PACKET_LENGTH<br>bytes of the failed packet is returned |

| ERROR_HEARTBEAT_STOPPED   | Indicates a failure to detect the heartbeat signal<br>from the Media Attachment Unit following pack-<br>et transmission. See Section 5.1.7.                                            |

| ERROR_TX_BABBLE_FAULT     | Indicates an attempt to transmit a packet longer<br>than the maximum allowed,<br>MAX_PACKET_LENGTH is 1518 bytes                                                                       |

| ERROR_DMA_REQUEST_LATE    | Fatal hardware fault, this should never occur                                                                                                                                          |

| ERROR_TX_BUFFER_INVALID   | Fatal internal condition, this should never occur                                                                                                                                      |

| ERROR_TX_BUFFER_UNDERFLOW | Fatal hardware fault, this should never occur                                                                                                                                          |

# 4.2 Diagnostic procedures

Two diagnostic procedures are provided for verifying correct operation of the Ethernet interface hardware. The tests performed by both procedures involve transmitting self addressed packets, waiting for them to return and then comparing the returned packet data with the original test data. This loopback is either confined to the bounds of the Ethernet interface hardware itself (internal) or may occur externally, via an attached network.

Internal loopback checks for correct operation of the Ethernet interface hardware and associated packet buffer memory while transmitting and receiving test packets. There is no interaction with the attached Ethernet network during the test. A failure to successfully perform internal loopback indicates a fatal fault within the Ethernet interface hardware. External loopback extends the scope of the tests performed by transmitting and receiving test packets via the live Ethernet. Failures during this test can be caused by problems with the Media Attachment Unit, associated cabling or a network fault.

Since both procedures initialise the Ethernet interface in diagnostic loopback mode, application software should re-initialise the interface after their use. The Ethernet interface will be left in the inactive (stopped) state.

## 4.2.1 B431\_Internal\_Loopback()

## **Description:**

Perform an internal loopback test of the Ethernet interface hardware.

```

C:

int B431 Internal Loopback(

Channel

*from b431.

Channel

*to b431,

const unsigned char

physical address[PHYSICAL ADDRESS SIZE],

int

*error code )

occam:

PROC B431. Internal. Loopback (

CHAN OF ANY

from.b431,

to.b431,

VAL [PHYSICAL.ADDRESS.SIZE]BYTE physical.address,

INT

result,

error.code )

```

| Parameter        | Description                                                          |

|------------------|----------------------------------------------------------------------|

| from_b431        | Channel from the B431 device driver                                  |

| to_b431          | Channel to the B431 device driver                                    |

| physical_address | Physical address of the Ethernet interface                           |

| error_code       | An Ethernet interface error code if result is<br>TEST_HARDWARE_ERROR |

### Return codes:

result contains the completion code for B431.Internal.Loopback(). It is returned by B431\_Internal\_Loopback().

A value of **TEST\_PASSED** indicates normal successful completion:- The Ethernet interface successfully passed the packet loopback test. Other result codes indicate a failure to perform the loopack test as follows:-

| TEST_INIT_FAILED     | The Ethernet interface hardware failed to in-<br>itialise correctly                                                                  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| TEST_MEMORY_FAULT    | A memory fault was discovered while execut-<br>ing the packet buffer memory check                                                    |

| TEST_LOOPBACK_FAILED | Test packets failed to return or were corrupt on reception                                                                           |

| TEST_HARDWARE_ERROR  | The device driver indicated a hardware fault,<br>error_code will be as described for<br>B431_Waitfor_Event(), see section<br>4.1.10. |

#### Notes:

Since no interaction with the external Ethernet network occurs during internal loopback the physical address assigned to the Ethernet interface may or may not be a valid address.

# 4.2.2 B431\_External\_Loopback()

## **Description:**

Perform an external loopback test of the Ethernet interface hardware.

```

C:

int B431 External Loopback(

Channel

*from b431.

Channel

*to b431,

physical address[PHYSICAL ADDRESS SIZE],

const unsigned char

*error code )

int

occam:

PROC B431.External.Loopback(

CHAN OF ANY

from.b431,

to.b431,

VAL [PHYSICAL.ADDRESS.SIZE]BYTE physical.address,

INT

result,

error.code )

```

| Parameter        | Description                                                          |

|------------------|----------------------------------------------------------------------|

| from_b431        | Channel from the B431 device driver                                  |

| to_b431          | Channel to the B431 device driver                                    |

| physical_address | Physical address of the Ethernet interface                           |

| error_code       | An Ethernet interface error code if result<br>is TEST_HARDWARE_ERROR |

#### Return codes:

result contains the completion code for B431.External.Loopback(). It is returned by B431\_External\_Loopback().

A value of **TEST\_PASSED** indicates normal successful completion:- The Ethernet interface successfully passed the packet loopback test. Other result codes indicate a failure to perform the loopack test as follows:-

| TEST_INIT_FAILED     | The Ethernet interface hardware failed to in-<br>itialise correctly                                                                  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| TEST_MEMORY_FAULT    | A memory fault was discovered while execut-<br>ing the packet buffer memory check                                                    |

| TEST_LOOPBACK_FAILED | Test packets failed to return or were corrupt on reception                                                                           |

| TEST_HARDWARE_ERROR  | The device driver indicated a hardware fault,<br>error_code will be as described for<br>B431_Waitfor_Event(), see section<br>4.1.10. |

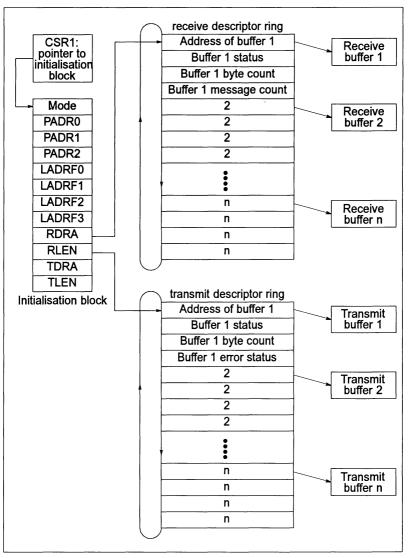

# 4.3 IMS B431 Device Driver

The IMS B431 device driver is supplied as a linked unit in the file:-\F006A\B431DRVR.LKU (which should be on the ISEARCH path). It is referenced by either a C (.cfs) or an occam (.pgm) configuration level program and should be placed on every IMS B431 Ethernet TRAM in the target transputer network. The configuration language syntax for achieving this is different for ANSI C and occam, the following configuration program source code fragments summarise this:-

```

occam .pgm file:

```

```

-- Hardware description

VAL K IS 1024 :

NODE b431 :

NETWORK simple.network

DO

--- IMS B431 has a T222 and 64 Kbytes memory

SET b431 (type, memsize := "T212", 64 * K)

CONNECT SomeOtherTram[link][2] TO b431[link][1]

- Can use an arbitrary link on IMS B431

-- Software description

#USE "b431drvr.lku" --- IMS B431 device driver

CONFIG

CHAN OF ANY SomeOtherTram.to.b431, b431.to.SomeOtherTram :

PLACED PAR

PROCESSOR b431

INMOS.B431.Driver( SomeOtherTram.to.b431, b431.to.SomeOtherTram )

:

ANSIC .cfs file:

/* Hardware description */

/* IMS B431 has a T222 and 64 Kbytes memory */

T212 (memory = 64K) b431;

connect SomeOtherTram.link[2] to b431.link[1];

/* Software description */

process (interface (input to b431, output from b431)) b431 driver;

connect SomeOtherTram.to b431 to b431 driver.to b431;

connect SomeOtherTram.from b431 to b431 driver.from b431;

```

```

/* Select linked units and place processes */

```

use "b431drvr.lku" for b431 driver;

/\* IMS B431 device driver \*7

place b431\_driver on b431;

72 TRN 235 00

## 4.3.1 Debugging support

To achieve maximum performance from the Ethernet interface the IMS B431 device driver linked unit b431drvr.lku is supplied with interactive debugging disabled. Note that it is not supplied with interactive debugging enabled, for the following reasons:-

- 1 The IMS B431 device driver will be used in real time communication system environments. Typically, it is not possible to interactively debug real time communication protocol software.

- 2 Because it would be slower, using a different and slower version of the device driver when debugging has the potential to alter the conditions under which bugs arise.

The consequence of this is that it is not possible to interactively debug transputer networks whose configuration descriptions include placement statements for the IMS B431 device driver. In particular, for ANSI C programmers, this means:-

- 1 When booted with ISERVER, configured programs will run normally.

- 2 Attempting to boot a configured program with the interactive debugger IDEBUG will fail, the debugger will generate a warning message.

- 3 Application debugging is possible with the post-mortem debugger.

and for occam programmers:-

- 1 Application software should be compiled and linked with interactive debugging disabled. Use the complier and linker **y** option.

- 2 The **y** option should also be used when configuring with occonf, it will fail to generate a bootable otherwise.

- 3 When booted with ISERVER, configured programs will run normally.

- 4 Application debugging is possible with the post-mortem debugger.

Interactive debugging is possible with the IMS F006A software, but this requires alteration to source code and network configuration descriptions. There will be occasions when interactive debug capability can be usefully applied to some parts of a target transputer network, while other parts continue to execute real time software. With care, it may even be possible to achieve this without affecting the real time nature of other transputers in the system. For this reason an alternative scheme for booting a target transputer network that allows both the interactive debugging of application software and the IMS B431 device driver to execute is supported by the IMS F006A software.

Every IMS B431 Ethernet TRAM, in a target network, is treated as a peripheral device and is not described in the corresponding network configuration file. The placed hard links and channels that previously connected application software to the device driver are instead placed onto an *EDGE* link. This separates application transputers from their attached IMS B431 Ethernet TRAMs. No bootable code will be generated for the IMS B431 TRAMs because they will not appear in the network description:— the network bootable file generated by configuring with the alternative description will not contain any code for any IMS B431 TRAMs. When the network is booted with this file it will run only application software, on application transputers. The IMS B431 TRAMs will be reset and not running any code.

The responsibility to boot each IMS B431 TRAM in this scheme is passed on to application software. The procedure B431\_Load\_Driver() does this, when passed a pair of transputer channels which are connected to an adjacent IMS B431 TRAM it will download the device driver into the TRAM and verify that the boot succeeded. The channels will be the same ones subsequently used to interact with the device driver, as previously described, and should be mapped onto an EDGE link known to be physically connected to the IMS B431 TRAM.

Booting the IMS B431 TRAM separately in this manner allows an application transputer network to be run with or without the interactive debugger present whilst maintaining constant behaviour on the Ethernet TRAM. It should be stressed, however, that the use of the interactive debugger does change the performance and therefore real time characteristics of the application being debugged. It is recommended that the post mortem debugger be used unless special circumstances require otherwise.

The following occam configuration source code fragment shows how to declare an EDGE link and how they are then attached to an application program:-

```

-- Hardware description.

VAL K IS 1024 :

VALMISK*K:

EDGE b431 :

ARC HostLink, B431Link :

NODE app :

NETWORK application

DO

-- Application code runs on an IMS B404 2Mbye TRAM

SET app (type, memsize := "T800", 2 * M)

CONNECT app[link] [1] TO HOST WITH HostLink

-- IMS B404 TRAM is known to be connected to the IMS B431

-- via it's link 2. It doesn't matter to which link on the

-- IMS B431 TRAM it is connected.

CONNECT app[link] [2] TO b431 WITH B431Link

:

```

-- Software description.

#INCLUDE "hostio.inc"

#USE "application.c8h" -- Application program

CONFIG

CHAN OF SP app.to.host, host.to.app :

CHAN OF ANY app.to.b431, b431.to.app :

PLACE app.to.host, host.to.app ON HostLink :

PLACE app.to.b431, b431.to.app ON B431Link :

PLACED PAR

PROCESSOR root

application( host.to.app, app.to.host, b431.to.app, app.to.b431)

;

# 4.4 Using B431\_Load\_Driver()

# **Description:**

Load the IMS B431 Ethernet TRAM with its device driver.

Applications, which do not include the IMS B431 Ethernet TRAM in their transputer network configuration, will use this procedure to download the device driver. The entire transputer network, with the exception of the Ethernet TRAM, will be loaded with application software at bootstrap time. This procedure allows the application to subsequently download the device driver into the Ethernet TRAM. Once loaded, the Ethernet TRAM will function exactly as it would as if booted with the device driver from the same configured bootable file as the application. This alternative (two stage) loading scheme is required when one part of the transputer network needs to be configured differently from another part. Section 4.3.1 describes this in more detail.

```

C:

#include <b431load.h>

int B431_Load_Driver(

Channel *from_b431

Channel *to_b431)

OCCAM:

#INCLUDE "b431load.inc"

PROC B431.Load.Driver(

CHAN OF ANY from.b431,

to.b431,

BYTE result)

```

| Parameter | Description                         |

|-----------|-------------------------------------|

| from_b431 | Channel from the B431 device driver |

| to_b431   | Channel to the B431 device driver   |

**Return codes:**

result contains the completion code for B431.Load.Driver(). It is returned by B431\_Load\_Driver().

A value of LOAD\_SUCCESS indicates normal successful completion:- the IMS B431 Ethernet TRAM will be running it's device driver. Other result codes indicate a failure to load and start the device driver as follows:-

| LOAD_BOOT_FAILED  | Could not download the device driver                       |

|-------------------|------------------------------------------------------------|

| LOAD_CHECK_FAILED | Loaded device driver but it failed to respond when checked |

## Notes:

from\_b431 and to\_b431 must be configured as EDGE channels, ie: they are placed onto an EDGE link by the configuration description for the application transputer network. The corresponding hard link should connect the EDGE to an IMS B431 Ethernet TRAM. This is discussed in the relevant toolset documentation for the configurer tools:-icconf (ANSI C) or occonf (occam).

If the EDGE link is physically unconnected, or connected to something other than an IMS B431 Ethernet TRAM, then this procedure will fail and interaction with the device driver will be impossible.

# 5 IEEE 802.3 CSMA/CD Ethernets

# 5.1 IEEE 802.3 CSMA/CD Ethernets

Ethernet is a Local Area Network (LAN) standard originally proposed by Xerox Corp, Digitial Equipment Corp and Intel Corp. It is now established as ANSI/IEEE Standard IEEE 802.3. Cheapernet is a variant of Ethernet using the same signalling conventions but a cheaper network medium.

Ethernet is a Carrier Sense, Multiple Access, with Collision Detection local area network (abbreviated to CSMA/CD). This term defines the way in which two or more nodes gain and share access to a common bus transmission medium:- the Ethernet coaxial cable.

Communication is by means of packets. A packet is a collection of octets (bytes). Packets are transmitted in byte serial order, and within each byte bit serial order, on the coaxial cable.

When a node wishes to send a packet to another node, it observes the network to see whether any other node is transmitting a packet (Carrier Sense). If it detects another transmission, it will not attempt to transmit and instead defers until the network is quite. If it does not detect another transmission it begins to transmit the packet.

Because it takes a finite time for a signal to travel across the network, two (or more) nodes may begin transmitting simultaneously because they all believe the network is free (Multiple Access). This results in packets colliding on the network.

All of the nodes detect the collision (Collision Detection). The nodes which were not attempting to transmit will then not attempt to transmit until the collision has been resolved and a packet transmitted. The nodes which were attempting to transmit wait for a random time then attempt to transmit again. Thus, one node should always gain possession of the network. If another collision occurs, the nodes wait again for a random time and try again. Up to 16 transmission attempts are allowed, if the packet has not been transmitted after this, the node does not try to transmit it again.

Because of the carrier sense function, there is only a short time at the beginning of transmission during which collisions can occur. This time is known as the slot time and is the time taken for a transmitted signal to travel to the farthest point on the network, collide, and return as a collision. The slot time is defined to be 64 byte times which at 10 Mbits/s is  $51.2\mu$ s. This definition of slot time limits the maximum path length on the network to 500 meters.

Once the slot time has elapsed without any collisions being detected, a node may assume that it has possession of the network. All other nodes will have detected it's transmission and will not attempt to transmit.

# 5.1.1 Packet structure

| IEEE 802.3 MAC frame format   |                                                                                   |                        |                   |          |                        |        |                   |         |

|-------------------------------|-----------------------------------------------------------------------------------|------------------------|-------------------|----------|------------------------|--------|-------------------|---------|

| IMS F<br>gener                |                                                                                   | User supplied User sup |                   | supplied | F006<br>gener-<br>ated |        |                   |         |

| Pre-<br>amble<br>1010<br>1010 |                                                                                   | Dest.<br>address       | Source<br>address | Length   | Data                   |        | (optional)<br>PAD | FCS     |

| 56 bits                       | 8 bits                                                                            | 6 bytes                | 6 bytes           | 2 bytes  | 46 – 1500 bytes        |        | 4 bytes           |         |

| IMS F                         | Ethernet frame format<br>IMS F006<br>generated User supplied User supplied gener- |                        |                   |          |                        |        |                   | F006    |

| Pre-<br>amble<br>1010<br>1010 | Sync<br>11                                                                        | Dest.<br>address       | Source<br>address | Туре     |                        | Data   |                   | FCS     |

| 62 bits                       | 2 bits                                                                            | 6 bytes                | 6 bytes           | 2 bytes  |                        | 46 – 1 | 500 bytes         | 4 bytes |

Ethernet packets have the following structure:-

Figure 5.1 Ethernet packet structure

The IEEE 802.3 preamble and start frame delimiter (SFD) bits are equivalent to the Ethernet preamble and sync bits. Thus the packet formats are essentially identical.

Bytes are transmitted from left to right, starting with the preamble bits and finishing with the frame check sequence (FCS) bytes. The IMS B431 hardware generates the preamble and SFD / sync bits automatically, it also computes the frame check sequence bytes unless explicitly disabled from doing so.

The packet is logically split into two parts:- the packet header and data segments. The header contains addressing and control information and the packet data segment contains data.

The destination and source address fields are both 6 bytes long. The source address will correspond to the address assigned to the Ethernet interface during initialisation, it identifies the packet's origin. The destination address identifies the intended recipient of the packet. Section 5.1.3 describes Ethernet addressing conventions.

The type or length field is two bytes long, it carries either a packet type code or a length value. Type codes are used to identify packets as members of a common

higher layer protocol family. When used as a length field the value corresponds to the number of bytes carried in the data part of the packet which may then be different from the actual number of bytes in the packet. This is used to distinguish data bytes from optional padding bytes. The length value should be expressed in big endian order, the most significant byte is transmitted before the least significant.

# **Packet lengths**

The minimum Ethernet packet length is 64 (MIN\_PACKET\_LENGTH) bytes. The maximum is 1518 (MAX\_PACKET\_LENGTH) bytes. These values include the 14 (PACKET\_HEADER\_SIZE) byte packet header and trailing frame check sequence bytes. Attempting to transmit a packet longer than the maximum allowed will result in a transmit babble fault. Packets smaller than the minimum value will padded to the minimum value with random data.

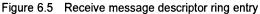

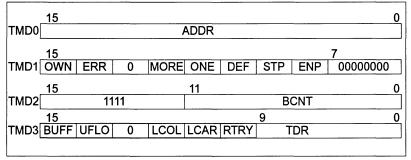

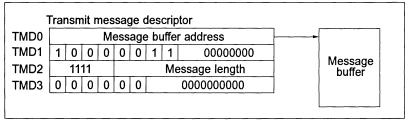

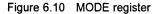

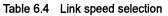

# 5.1.2 CRC algorithm