# Contents

| Preface                                                  |           |

|----------------------------------------------------------|-----------|

| Acknowledgments                                          |           |

| Introduction                                             |           |

| Chapter 1 Introduction to Parallel Processing and the Tr | ransputer |

| Chapter 2 Transputer Hardware Architecture               |           |

| Chapter 3 Transputer Instruction Set                     |           |

| Direct Instructions                                      |           |

| Indirect Instructions                                    |           |

| Floating Point Numbers                                   |           |

| Chapter 4 Programming the Transputer                     |           |

| Chapter 5 Newer Transputers                              |           |

| Chapter 6 Instruction Set Reference                      |           |

| Instructions ADC to FMUL                                 |           |

| Floating Point Instructions                              |           |

| Instructions GAJW to XWORD                               |           |

| Appendix A Transputer Instructions Sorted by Operation   | on Code   |

| Appendix B Sample Floating Point Number Representa       | tions     |

| Appendix C Special Workspace Locations                   |           |

| Appendix D Transputer Memory Map                         |           |

| Appendix E Instructions which can Set the Error Flag     |           |

| Appendix F Instructions Unique to the T414 and T800      |           |

| Appendix G Summary of different models of transputer     | S         |

| Suggested Readings                                       |           |

# Preface

It's not often that an engineer sits down to write a book out of frustration. However, after struggling with nonstandard and sometimes cryptic documentation from Inmos, I set out to do so, hoping at first only to crystalize the information in my own head, then later realizing that others may be facing the same problem.

For other conventional microprocessors on the market, documentation is plentiful, but the transputer is a strange bird. It is probably the most successful CPU chip conceived of, designed, and manufactured outside of the United States. Yet it has not attracted the following of technical writers that the latest chips from Motorola, Intel, or other American manufacturers have. Let the others follow the pack. The ability to multitask processes with assembly level instructions or to connect multiple transputers together like "electronic leggo" sets this CPU chip apart from the rest. Whether others will follow its lead remains to be seen, but I believe the transputer has had and will continue to have an important role to play in the area of computing known as "parallel processing."

Parallel processing essentially means more than one computing element working on the same problem. Hopefully, this means the problem can be solved faster (but not always). Usually, the type of problems that can be solved faster involve heavy number crunching, the kind of problems scientists sink their teeth into. In the never-ending search for more computer speed, scientists are rushing headlong into parallel processing and transputers are there waiting for them.

# Acknowledgments

This book would not have been possible without the assistance of important individuals. Will Burgett provided great assistance in editing early drafts and making them human-readable. Philip Goward also reviewed many copies and was mercilessly correct in pointing out technical errors or omissions. Colin Plumb provided the inspiration with his editorializing, but excellent technical note on the bizarre nature of transputer assembly language. Wayne Davison cleared the fog on the IEEE 754 Standard by patient answers to my naive questions. Tom Merrow let me apprentice with him on some important tasks involving operating system essentials. And Charles Vollum gave me an extraordinary opportunity to learn about transputers.

Thank you everybody!

# Introduction

Why the transputer? The overwhelming market share of microprocessors today are either members of the Intel 80x86 or Motorola 680x0 family. These traditional processors have the numbers behind them, but the transputer reflects an architecture we're going to see more of in the future. The on-chip floating point unit (in the T800 transputer) yields performance faster than microprocessors paired with their coprocessor cousins. Multitasking is the wave of the present as well as the future, and the transputer provides assembler-level support for multiple processes; in fact, the transputer has a process scheduler built into it.

The most important feature of the transputer, however, is its support for communication between processors. From a hardware perspective, the transputer has four bidirectional serial links that can be connected to other transputers; this hardware mechanism can be exploited for parallel processing. From a software perspective, communication to another transputer occurs in the same fashion that communication occurs between two processes on the same transputer, allowing for easier software design of parallel programs.

Parallel programming is where computers are going. Personal computers are still benefiting from the increase in single processor performance, but at the mainframe and minicomputer level, multiprocessor architectures are starting to dominate the scene. The problems encountered in single processor architectures will also eventually arise in personal computers, and parallelism will be used to increase their performance as well.

When Inmos first introduced the transputer, they decided to insulate programmers from the basic instruction set of the transputer. Instead of providing information about the native assembly language, they provided a language called Occam. Occam is a higher level than assember, but lower than most programming languages (such as Pascal or C). Occam allows a programmer to exploit the parallelism and special communication features of the transputer in a well-defined manner, yet it was a new and completely different programming language. Programmers want to program in the languages they are familar with. Inmos eventually relented and began providing information on the underlying instruction set of the transputer. Now, programming languages in C, C++, Fortran, Pascal, Modula-2, and Ada are all available for the transputer, and the list is growing.

Inmos originally designed the transputer for the embedded microcontroller market. There are some features of the transputer that reflect this influence. One example of this is that if certain flags are set in a certain order the transputer will shut down. This may be desirable for a coffee maker, but not a general purpose computer. As more users and designers saw the transputer, however, they began to realize its inherent power as a computing engine, since it was possible to cascade multiple transputers together to solve problems in significantly less time than it would take single processor systems.

So, due to the original product push and the lack of detailed information about the instruction set, transputer-based computers did not emerge at once. Instead, add-on accelerator boards consisting of multiple transputers that could be plugged into existing computers came forth. However, transputer-based computers are starting to enter the marketplace today.

There are three basic models of the transputer: the T212, the T414, and the T800. The T212 has a 16-bit wide register length and is not discussed in this book, although much of what is written about the T414 applies to it as well. By far the more popular models are the T414 and T800 (both with 32-bit wide registers), which are discussed in this book. The basic difference between the T414 and T800 is that the T800 has an on-chip floating point arithmetic engine. There are other minor differences that are noted in the pages that follow.

Most assembly language programmers have already mastered the basics of binary arithmetic and hexadecimal representation of binary numbers, so these subjects are not discussed. Hexadecimal numbers are indicated by the prefix "0x" as in the C programming language. For example, "0xA" means the hexadecimal value "A" (which is equivalent to the decimal value 10).

Inmos invented some new terminology when it produced the transputer, perhaps just to be different. For the sake of consistency, their terminology is used where it differs with conventional computerese. The most agregious terms are Inmos's use of "workspace" for "stack" and "instruction pointer" for "program counter". There is also the "workspace pointer," which everyone else in the computer industry would call the "stack pointer."

The basic organization of the book is as follows:

Chapter 1 Parallel processing Chapter 2 Transputer architecture Chapter 3 The instruction set Chapter 4 Programming the transputer Chapter 5 Newer Transputers Instruction Set Reference Detailed descriptions about each instruction Appendixes Miscellaneous useful information Suggested Readings List of useful references

This book is intended to be useful for reference even after it has been read thoroughly. The information does not depend on any one operating system or assembler. Programming examples have sufficient comments to make them easily portable. It is hoped that the dissemination of this information will generate further excitement and interest in the transputer.

# Introduction to Parallel Processing and the Transputer

What is parallel processing? Parallel processing is the ability to perform multiple computations simultaneously. In some multitasking operating environments, it may appear that you are computing two things at the same time, but in reality the computer is only doing one thing at a time, switching between tasks so quickly that it appears to be doing more than one thing at a time when it isn't. True parallel processing involves physically separate computing engines, each chewing on some computation.

Since microprocessors were first invented, engineers and hobbyists have been envisioning a computer system consisting of many processing elements. However, advances in the performance of single processor units has been so great in such a short time that many engineers and scientists believe that uniprocessor computers will always provide the best performance and that higher performing computers are only a generation away. Yet parallel processing is starting to emerge as a way of bringing more computing power to bear against problems that even the fastest computers have found intractable. Essentially, parallel processing is a mechanism to allow computers to calculate faster.

Although it may seem perfectly rational that two computers working together on a problem should be able to solve it faster than one, it's not always the case. Consider the following C program fragment, which multiplies each element of a 1000 element integer array (called a) by 100:

for (i = 0; i < 1000; i++)a[i] = a[i] \* 100;

Each element of this array could be multiplied in parallel, and if you had 1000 processors you could parallelize this to all 1000 of them like so:

```

processor 1 a[1] = a[1] * 100

processor 2 a[2] = a[2] * 100

processor 3 a[3] = a[3] * 100

...

```

However, suppose the program loop was:

for (i = 1; i < 1000; i++)a[i] = a[i] \* a[i - 1]

This is not so easy to parallelize, since the current computation depends on the result of the previous one. That is why it is important for programmers to structure their programs in a manner so it is possible to take advantage of parallelism.

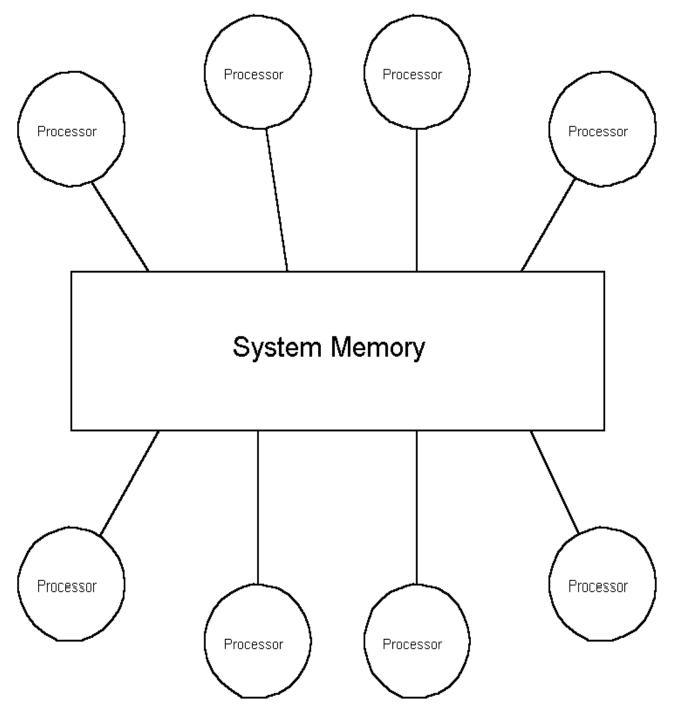

There are two basic models of parallel processing: shared memory and distributed memory. Shared memory processing is where multiple processors are connected to the same system memory. This scheme is used in many minicomputers and mainframes today. An advantage of shared memory is that multiple processors can use the shared system memory as a fast way to communicate and exchange data. The main problem of shared memory is that several processors can attempt to access the same memory location at the same time. When this happens, the requests have to be serialized, that is put into a sequential ordering. The contention that arises due to serializing is referred to as "memory contention." This slows down overall performance. Thus, shared memory systems tend to require faster memory so that processors will not have to wait too long before having a memory request satisfied. For shared memory in general, the more processors, the faster the memory required.

Figure 1-1 An example of a shared memory architecture.

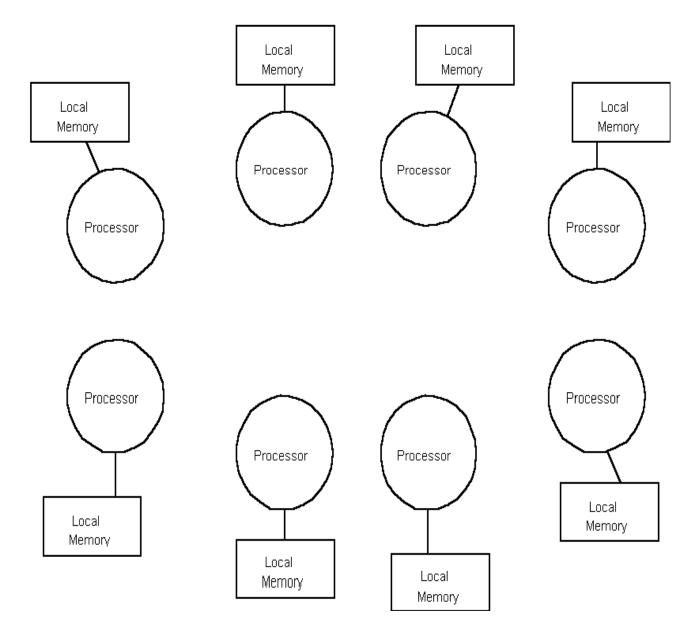

The alternate memory model, distributed memory, is where the transputer fits in. In a distributed memory model, each processor has its own local memory. The key question in a distributed memory model is What is the nature of the communication between processors? There is no common "memory pool" for communication in a distributed memory environment, so instead the processors must have some other method of communication. On the transputer, this method is to use serial "links," which act very much like serial ports on personal computers. Each transputer has four bidirectional links that can be connected to links on other transputers. Each link provides a flow of data from one processor in the system to another. Thus, like building blocks or leggo, one can connect many transputers together into various configurations. Such a mechanism is typical of a distributed processing system.

Figure 1-2 An example of distributed memory.

One popular software mechanism for using distributed memory as a kind of global shared memory is "Linda." Linda was developed by David Gelernter and Nicholas Carriero at Yale and is essentially a set of communication primitives that are added to an ordinary computer language. In a Linda program, a programmer places data into and reads or removes data from an abstract shared memory area called "tuple space." The data objects inside the tuple space are referred to as "tuples." A tuple space can exist in either shared or distributed memory. This abstraction has the advantage of portability. In particular, Linda programs can run on either shared or distributed memory machines. Underlying system libraries implement the machine-dependent communication functions upon which Linda relies. Linda programs ignore the underlying processor topology and aim at a higher level of abstraction for interprocess and interprocessor communication.

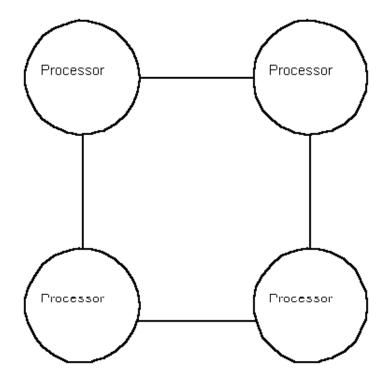

However, for most distributed memory environments, the processor topology is the main consideration. The next question to ask then is how to connect multiple transputers. With four links per transputer, there are various topologies, or network configurations, that are possible. It is possible to configure four transputers in a "ring," with each processor connected to two others, much like children holding hands to form a ring. Ring topologies are common in computer networks, since they only require an input line from one system and an output line to another.

Figure 1-3 Four processors configured in a ring.

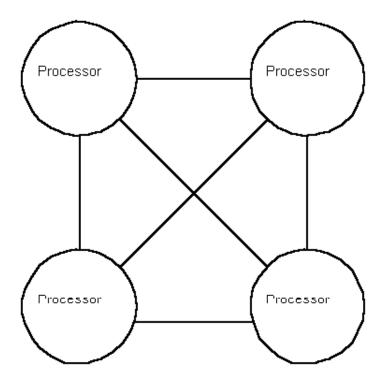

However, the transputer has four links, so it is possible to provide more interconnections between processing elements. If another link was used to connect each processor, another configuration would be possible. When each processing element in a network of processors is connected to all the other processors in the network, the network is said to be "fully-connected."

Figure 1-4 Four processors configured in a fully-connected ring.

Transputers are not limited to ring topologies. In general, the topology of a computer network is determined by the communication needs of the application program. These needs reflect the algorithmic solution for the problem it is

trying to solve. For some applications, it may be desirable to configure a series of transputers into a tree structure.

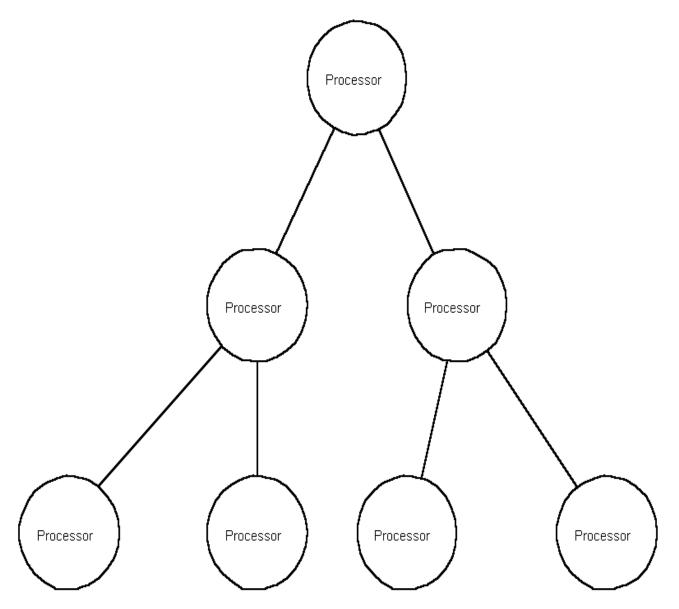

Figure 1-5 Seven processors configured into a binary tree.

Key questions surrounding processor topologies are: what is the nature of the problem to be solved, how can the problem be parallelized, and how will data migrate from processor to processor? The data migration issue is perhaps the easiest to focus on. For instance, consider a problem where each computing engine acts like a worker on an assembly line, performing some computation on the problem, then passing its result onto another worker on the line. The data drives the computation. This scenario is referred to as a "pipeline," where data is input at one end, then piped through multiple processors, each of which performs some intermediate step towards the final result. The last processor, presumably, achieves the final result and outputs it.

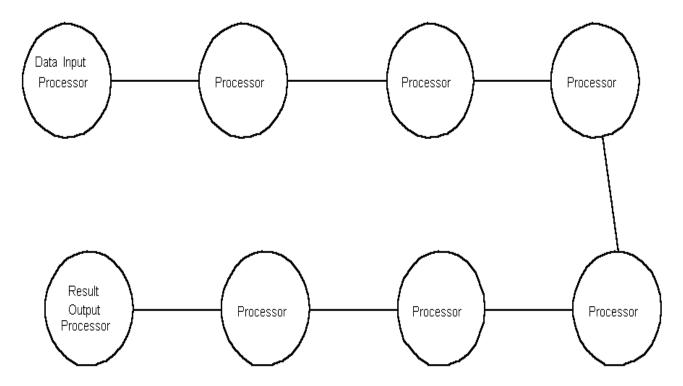

Figure 1-6 Eight processors configured in a pipeline.

In general, computers can be broken down into one of four categories:

SISD single instruction, single data stream MISD multiple instruction, single data stream SIMD single instruction, multiple data stream MIMD multiple instruction, multiple data stream

A single instruction, single data stream (SISD) computer is a traditional single central processing unit (CPU) computer with only one processor working on one set of data at a time. Ordinary personal computers fall into the SISD category. A multiple instruction, single data stream (MISD) computer has multiple processors, each of which executes instructions on a single stream of data. Fault-tolerant computers, which duplicate hardware functionality, are an example of this category, as a fault-tolerant system typically has at least two processors each performing the same computation on the same piece of data, then if the primary unit fails, the backup unit takes over. Single instruction, multiple data stream (SIMD) computers are typically "arrays" of processors that each execute the same instruction on a different set of data. A grid of processor performing a matrix multiplication (hence the term array) would be an example of SIMD computing; each processor performs the same multiplication instruction, but on different elements of the matrix. Multiple instruction, multiple data stream (MIMD) computers are where each processor executes a different sequence of instructions on a different set of data. A computer network can be thought of as an MIMD system (since it is usually composed of SISD computers all executing different instructions on different data).

The power of the transputer design is that it is flexible enough to be configured into any of these categories. A computer architectural design can now be fitted to the exact problem you are trying to solve. This provides a performance boost for programs previously constrained to run on a traditional single-processor computer architecture.

Each of the four serial links on a transputer can be connected to a serial link on another transputer. This allows you to construct a network of transputers just as you could connect a network of personal computers together. In the same way that computer network topologies vary, so too can transputer network topologies vary. Much of the analysis that applies to computer networks also applies to transputer networks. The main idea is to get additional computational power by using multiple processors together on a problem. The unique aspect of the transputer that makes this possible is its built-in ability to communicate with other transputers over its serial links. Since each transputer uses its own local memory, the memory is said to be "distributed" over the processor network.

Transputers, in short, are distributed memory processing engines that can be configured into a variety of architectures.

The architecture of the processor network can be tailored to the problem to be solved. Usually the network topology is fixed; however it is possible to construct transputer networks that can be reconfigured on the fly, that is as the processor is running a program. In addition to the serial links, there are assembly language level instructions designed for communication between transputers. The transputer is unique among popular microprocessors today in providing both hardware and software level support for parallel processing.

# **Transputer Hardware Architecture**

There are two strong influences in the transputer's design philosophy and one minor one: parallel processing and RISC (Reduced Instruction Set Computing) concepts have strongly shaped the transputer, while embedded microcontroller notions have also had an impact. The microcontroller influence is seen most strongly where the transputer can shut itself down if a computation produces an error. This may be necessary if a coffee pot starts to overflow, but no modern computer system really runs without allowing computation errors of some kind. Another influence that stems from embedded microcontrollers is that transputers are capable of servicing external interrupts quickly. This is primarily due to the small amount of state associated with each transputer "process" or thread of execution, thus changing the current process, also called "context switching," is relatively inexpensive.

Note: The term "thread" refers to a single sequence of instructions being executed. If you follow the consecutive instructions a program executes, then you are following the "thread of execution" for the program. Some operating systems, like MS-DOS, can only support a single thread of program execution. Other operation systems, like Unix, can support multiple threads of program execution, implying that more than one program can execute at the same time.

The major features of the chip, however, are inherent support for parallel processing and RISC. The parallel processing influence gave the transputer communication mechanisms that enable multiple transputers to behave as a single computing engine with each individual component transputer passing necessary messages (about a computation) to another. The RISC influence has made the instruction set sparse, but not small. This means that due to the relatively large number of special features on the transputer (built-in chip-to-chip communication channels called "links," on-chip timers, assembler level multiprocessing, etc.), the instruction set is not small, but each instruction exercises only a narrow aspect of a particular hardware feature. In this sense the transputer comes closest to the RISC concept. For instance, unlike many new 32-bit microprocessors the transputer does not provide support for indexed addressing in a single instruction. The same functionality exists, but instead of having the index in one register, the base address in another, and a single instruction to compute the effective address and fetch its contents, the transputer requires several instructions are less functional than conventional or CISC (Complex Instruction Set Computing) instructions. The advantage of the transputer's RISC approach is that the instructions themselves, while less powerful, execute much faster.

In addition to these software-oriented features, the transputer has built into it a programmable external memory interface and thus requires very little support circuitry. The most costly part of a transputer-based system is typically the RAM.

Inmos introduced the transputer in 1984. The INMOS transputer family is currently composed of three different processors:

- The 16-bit T212,

- The 32-bit T414, and

- The 32-bit T800.

The T212 is not discussed in this book, but much of what is said about the T414 applies to it. (Note that the T212 has 16-bit registers, thus a word length of 16 bits or 2 bytes, while the T414 and T800 have 32-bit registers, thus a word length of 32 bits or 4 bytes.) The T800 is essentially a T414 with an on-board floating point co-processor engine and is available in 20, 25 or 30 MHz versions. The T414 is currently available in a 15 or 20 MHz version.

The 20 MHz versions of the T414 and T800 can provide for about 15 MIPS (million instructions per second) performance. However, since transputer instructions are more primitive (i.e., less functional) than conventional microprocessor instructions, this translates to a relative performance of about 3 to 5 MIPS (when compared with other conventional microprocessors).

## **Register Set**

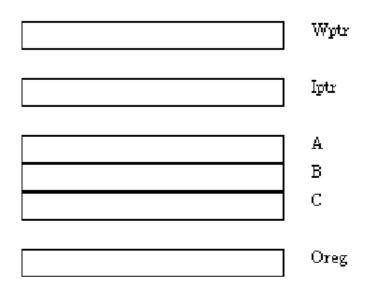

The transputer has three general purpose registers (forming a stack), a program counter (called the "instruction pointer" in Inmos parlance), a stack pointer (called "workspace pointer" by Inmos), and an operand register.

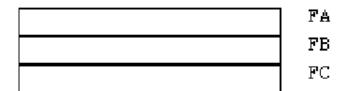

The general purpose registers on the transputer form a three deep stack (and operate in a similar fashion as RPN calculators, like those manufactured by Hewlett-Packard). Values are pushed onto the register stack and popped off it. These three integer registers are named A, B, and C. (Note: On the T800 there are three additional registers named FA, FB, and FC for floating point arithmetic.)

If you push a value into A, first B will be pushed into C and the contents of A will be pushed into B; then A is set to the new value. Similarly, if you pop the register stack, A receives the contents of B and then B receives the contents of C. After popping the register stack, C is undefined. (Although it has been observed that the value of C is replicated, that is, it retains its value after the register stack is popped. Some transputer compilers take advantage of this feature, but Inmos warns that it may be discontinued in the future and software should not rely on it.) The A, B, and C registers are 16 bits wide on the T212 and 32 bits wide on the T414 and T800.

# T800 Only

Figure 2-1 Transputer register set.

You always access the register stack through the A register. When you pop the value in register A, its contents will come off the stack (into memory), while those values of B and C move down (into A and B). Conversely, when you push a value onto the stack:

- 1. The C register receives the value in the B register.

- 2. The B register receives the value in the A register.

- **3.** The new value is placed in register A.

In addition to the register stack, the transputer has three other major registers:

- The instruction pointer (program counter),

- The operand register, and

- The workspace pointer (stack pointer).

The operand register serves as the focal point for instruction processing. All transputer instructions are one byte long and typically execute in one or two clock cycles. The four upper bits of a transputer instruction contain the operation to perform, the four lower bits contain an operand for that operation. There are special transputer instructions to form longer operands. These are called "prefix" instructions, since typically they prefix (or come just before) other instructions that use the operand register.

A prefix instruction loads its operand field into the four least significant bits of the operand register, and then shifts the operand register left four places. Consecutive prefix instructions can be used to fill the operand register with any value, one nibble at a time. By using the contents of the entire operand register as an operand along with the operand field of the current instruction (its lower four bits), any 32-bit value can be used as an instruction operand.

#### Register Notation and Summary

There are six registers on the transputer that are used in virtually all programs. They are Iptr, Wptr, the A-B-C stack, and Oreg.

Iptr - Instruction pointer. Normally referred to as a program counter, Inmos chose to call it the instruction pointer. This contains the address of the next instruction to execute.

Wptr - Workspace pointer. Again, this is normally called a stack pointer, but Inmos chose to call it a "workspace pointer." The transputer instruction set is strongly geared for using memory locations that are at small positive offsets from Wptr for the storage of variables. Note that loading from an absolute address requires two instructions, while loading from the workspace (stack) only requires one.

A, B, C - General purpose registers that form a three deep stack.

Oreg - Operand register. This register is used to assemble small operands from multiple instructions (e.g., prefix instructions) into one long operand.

## Flags

There are three flags in the transputer: Error, HaltOnError, and FP\_Error.

Error - The transputer has an error flag similar to an overflow flag in conventional microprocessors, except that its "sticky," that is once set it stays set until it's explicitly cleared. The Error flag value is also sent out over an external pin of the same name. This harkens back to the microcontroller influence in the transputer, so other transputers can detect that one has made a computation error and take some appropriate action. This is probably never used in reality.

HaltOnError - This flag, when set, halts the entire transputer if Error is set (provided Error was previously clear). It is probably wise to leave this flag clear, otherwise you could shut down the entire transputer if Error is set. Again, this is the microcontroller influence that says, if you're controlling some device and you make a mistake, shut everything down.

FP\_Error - This flag is the floating point error flag and behaves like the Error flag does, except that it is used for floating point errors. It is only present on the T800.

## **T800 Floating Point Unit**

There is a measure of support for IEEE floating point arithmetic in both the T414 and T800 transputer. The T414 has several instructions designed to assist single-length (32-bit) floating point arithmetic. These instructions are implemented in microcode on the chip.

The T800 does not have those instructions, instead it has something much more powerful, an on-chip floating point arithmetic engine. Most conventional CPUs, such as the Intel 80x86 and Motorola 680x0, have sister coprocessor chips for floating point arithmetic (the Intel 80x87 and Morotola 68881 and 68882). Inmos has done them one better and incorporated the floating point unit on the same chip in the T800. The floating point performance of the 20 MHz T800 is in the 1.5 to 2.0 Megaflop (million floating point operations per second) range. This is roughly 50 percent faster than a 16 MHz 80386/80387 combination.

The T800 floating point unit supports IEEE floating point arithmetic for both single length values (32-bit) and double length values (64-bit). The floating point registers are organized in a three deep stack, like the integer registers. The floating point engine and the integer unit can act autonomously to a degree, so while the integer unit is computing an address, the floating point unit can perform some numerical computation simultaneously. This "overlapped execution" is the one way to maximize transputer performance (and some compilers exploit this).

The floating point unit registers are called FA, FB, and FC. These registers are 64 bits long and can hold either single (32-bit) or double (64-bit) precision floating point values. There is no way to query the precision of the number that one of these registers contains (i.e., is it a 32-bit or 64-bit number?), so it is necessary for the programmer to be aware of this limitation when writing code.

## **Instruction Format**

Transputer instructions are a single byte in length, although one instruction is merely "execute the contents of the operand register as an instruction," which is the way around a one-byte instruction limitation. Instructions that are one byte in length are called "direct instructions." Instructions that use the "execute the contents of the operand register" trick and are more than one byte in length are called "indirect instructions." Indirect instructions are composed of prefix instructions that load a value into the operand register, followed by an operate instruction that triggers the actual execution.

The idea behind single-byte instructions is to improve the effectiveness of the instruction pre-fetch, which in turn improves processor performance. Since there is an extra word in the processor's pre-fetch buffer, the transputer rarely has to wait for an instruction fetch before proceeding to decode and execute the next instruction. Since transputer instructions are only one byte in length and one word is fetched from memory at a time, transputers are effectively equipped with a four-byte instruction cache.

The most commonly used instructions were chosen to be the direct instructions, since direct instructions are the most compact (one byte) and execute the fastest. However, it is obviously impossible to code all necessary instructions into a single byte. As a result, some operations in the transputer require more than one instruction.

As mentioned earlier, the upper four bits of a byte determine the instruction code, so this allows for 16 possible instructions. Only 13 of these are commonly used by assembly language programmers (for example, load, store, jump, and call). Each of these instructions requires an operand that is partially supplied by the four-bit operand field.

The other three instructions (not commonly used by assembler programmers) are the two prefix instructions, which are used to build operands longer than four bits, and the operate instruction, which says "execute the contents of the operand register as an instruction." Assemblers insulate programmers from having to build longer instructions out of these more primitive assembler instructions.

More often than not, four bits per operand is often insufficient, so the transputer has two special instructions called PFIX and NFIX that are used to load the operand register. When one of these instructions is executed, the operand register is shifted four bits to the left and then the instruction's operand (from the NFIX or PFIX) is placed in the four bits that were cleared by the shift (the lowest four bits or least significant nibble). Using these instructions, you can load the operand register with any 32-bit value (the word length of the transputer).

## **Data Organization in Memory**

The transputer architecture provides inherent support for 32-bit integer or long values, as well as byte or character values. It is more difficult to provide support for the short 16-bit values, such as in the C programming language. Most instructions are geared around word (32-bit) quantities; however, there are two instructions LB (load byte) and SB (store byte) that support character-sized (8-bit) data. Support for 16-bit quantities must be emulated by using the byte instructions and shifting; there is no instruction level support for short (16-bit) quantities. For example, to load a 16-bit quantity, first you load one byte, then shift left eight bits, and then add the next byte. (Note: These comments apply to the T414 and T800, which are 32-bit word length machines, not the T212, which is a 16-bit word length machine. On the T212, support for shorts is inherent, support for "longs" or long-types is not.)

The transputer is little endian in nature, meaning that the least significant bytes of data are stored first in the lower memory addresses. This is like the Intel 80x86 architecture and is the opposite of the Motorola 680x0 architecture.

#### Addresses

The addresses on the transputer are one word wide, yielding a continuous address space of four gigabytes for the 32-bit T414 and the T800. The address bus is multiplexed with the data bus. An interesting facet of the transputer is that addresses are "signed," that is, if the most significant bit of an address is set, the address is negative and actually precedes any positive address.

Transputers have two basic ways of addressing data in memory: (1) stack operations and (2) random access methods. Both techniques are valid, but stack operations are faster, whereas random access methods are more typically convenient for the programmer. In either case it is faster to access words in memory rather than bytes. Important: Many instructions dealing with memory require addresses on word boundaries (i.e., addresses that are multiples of four), otherwise unpredictable values can result from a memory access.

The transputer also has instructions geared for moving entire blocks of memory quickly, for copying arrays or to provide a graphics "bit blit" function.

#### **On-Chip Memory**

Transputers have fast on-chip memory, which is mapped into the low end of the transputer's address space. There are 2K bytes on the T212 and T414, and 4K bytes on the T800. This internal memory can be accessed by the transputer without wait states, whereas at least two processor cycles are added for external memory accesses. A program that fits into this on-chip memory will execute an instruction in the transputer's cycle time. In the case of the 30 MHz version of T800, this is a 33 nanosecond cycle.

The on-chip memory is considered to start at the bottom of the address space, which corresponds to the largest negative number, namely 0x80000000. A few values in the on-chip memory are used for link communication channels and process swap information.

A typical use of on-chip memory is for register variables (since the transputer has only three registers). An on-chip register variable can be accessed in a single cycle, while variables held in external RAM require extra cycles to be latched and read. Although code executing out of on-chip memory will experience a speedup, empirical evidence seems to indicate that placing the workspace into on-chip RAM provides the biggest performance boost to most programs by speeding up data references.

Each thread of execution on the transputer is called a "process." Every process has a stack (i.e., a workspace) associated with it. The workspace associated with the currently executing process lies above a base address (i.e., in higher, more positive, memory). The transputer's workspace pointer register points to the base address of the workspace for the process currently being executed.

Memory locations within a small offset from the workspaces are "local," and they can be accessed extremely fast by using the load local (LDL) and the store local (STL) instructions. If a memory location is within 16 words of the workspace pointer, it can be accessed with a one-byte instruction. When the workspace in a process resides in the transputer's internal, on-chip memory, workspace data can be accessed in one processor cycle (50 nanoseconds on a 20 MHz T414 or T800). In this case, the workspace acts like a large set of registers on a conventional microprocessor. In fact, some transputer compilers implement register variables by simply moving the variable to one of the first 16

locations on the workspace.

### **Microcode Scheduler**

Many operating systems allow you to "fork" or "spawn" or "exec" multiple processes (threads of execution) with a program; however, it is very rare to be able to do this in a native assembly language. The transputer has inherent support for multitasking via an on-chip microcoded scheduler. Certain instructions add new processes to the scheduler's queue of processes; other instructions cause a process to be removed from that queue. The task scheduler can schedule processes all on its own. Task switching in the transputer takes less than one microsecond. The scheduler executes processes from the queue in an endless loop, that is, once it reaches the end of the queue, it proceeds to the start of the queue for its next process to schedule. There are two separate queues the scheduler manages: one for high priority processes.

Processes running on a transputer can have any one of the following status conditions:

- Running,

- Waiting in a queue to be executed,

- Waiting for input,

- Waiting for output, and

- Waiting for a certain timer value.

If the status is "running" or "waiting in a queue to be executed," the process is active. If the status is any one of the remaining three conditions, the process is inactive.

Transputer processes can run in either low or high priority. A high priority process can interrupt a low priority process at any time. The high priority process will continue running:

- **1.** Until it is completely finished;

- 2. Until it has to wait for a communication; or

- **3.** Until it has to wait for a certain timer value.

A low priority process will always be preempted by any high priority process, for example if a high priority process is queued up for the scheduler, the running low priority process will be interrupted and the high priority process will begin executing. All high priority processes must terminate or be waiting for input or output before any low priority process will be scheduled.

Before it has to give way to a high priority process, a low priority process finishes executing its current instruction and then its process state (register values, flag values, etc.) is saved in reserved memory locations. Depending on what instruction was being performed at the time of interruption, the task switch time from high to low priority can take anywhere from 19 to 58 processor cycles (1 to 3 microseconds on a 20 MHz T414). When a process that has high priority must wait, the low priority process that was interrupted is rescheduled, but only if there are no other active high priority processes. This switching of processes from one to another is often referred to as a "context switch."

Typically, a high priority process is tied to the Event pin to handle external interrupts. This high priority process then "wakes up" when there is an external event it needs to service. If another interrupt occurs over the Event pin, another high priority process is spawned to service that event. This is how a transputer responds to external interrupts by creating a process to handle each interrupt.

Scheduling is done differently for processes of the same priority. Descheduling one process will only occur when a certain type of instruction has been executed. These instructions are also known as "descheduling points," since it is a point in a program where the current process can be descheduled and another can be scheduled to run. Furthermore, almost no process state is saved on a switch to another process of the same priority. In particular, the values in the A, B, C register stack are not preserved when another process of the same priority level is scheduled.

So you should be careful when programming a transputer that the register stack doesn't have any information that can be lost when you reach one of these special instructions that can cause the current process to be descheduled. This does

place an additional burden on the programmer or compiler writer, but while the transputer stores much less process information during a same priority to same priority context switch, this makes process switching much faster. Remember that when a process is descheduled by another process of the same priority, the integer stack values are "lost," however, the integer stack is saved when a high priority process interrupts a low priority process.

Also remember that only one process is ever running at any given instant of time. The scheduler is in an endless loop of saving the state of one process, transferring execution to another process (to run), waiting as the process runs, then interrupting it and saving its state so it can transfer execution to another process, and so on. The rapid switching of the CPU between processes produces the illusion that multiple programs are running at the same time.

#### Communication

An important concept for parallel programming is the ability to connect multiple transputers together to form a network of processors. Connections between processors allow transputers to communicate information and share data. This means that more than one CPU or "computing element" can work on a problem, and hopefully the problem can be solved faster than it would be with only one computing element. There are built-in hardware connections to allow transputers to communicate with each other.

Each transputer has four bidirectional one-bit wide serial ports called "links." A link on one transputer can be connected to a link on any other transputer. Inmos developed a general technique for one process to communicate to another process. Each such communicating process writes to and reads from memory addresses called "channels." Channels can be used for communication between processes inside a single transputer (in that case, the channels can reside almost anywhere in memory), or channels can be used to communicate over links to a process on another transputer (in which case certain fixed memory addresses in on-chip RAM must be used).

Typically, when a transputer runs several processes at the same time, these processes will want to communicate. To accommodate this need, the transputer offers use of internal channels for communication. These internal channels are used exactly the same way that external channels (i.e., links) are. The only difference is that any memory location will work in place of the reserved locations used by links.

Using internal channels gives you a sophisticated way to synchronize processes without semaphores or other fancy software tricks. For instance, examine the case where two processes need to share data. One process may be ready to send data to the other process, but the receiver process isn't ready to receive it yet. The sending process will execute an OUT instruction over a channel and be descheduled until the receiving process is ready (i.e., executes an IN instruction). When the receiving process executes the IN instruction, the sending process in this example is automatically rescheduled and the communication starts. This is a more efficient use of processor time, since the sending process hasn't had to continually poll (query) some status flag to check if the second (receiving) process is ready. This same trick can also be used to synchronize processes on different transputers.

Currently, links operate at a maximum speed of 20 MBits/sec, yielding an effective unidirectional data rate of 800 kilobytes/sec for the T212 and the T414, and 1.8 megabytes/sec for the T800. Transputer links use a handshake in which each byte that is sent must be acknowledged before the next byte can be sent. The T800 has an improved handshake mechanism, which is why it has a faster transfer rate.

Links have assigned locations in internal, on-chip memory. To send a message to another transputer, you must use one of these reserved locations. These locations correspond directly to pins on the transputer that will be electrically connected to either other transputers or to switching chips that will eventually connect to another transputer's link pin. Note that each input and output link channel is one word (four bytes) wide:

Link Address (hexadecimal)

Link 3 input 0x8000001C Link 2 input 0x80000018 Link 1 input 0x80000014 Link 0 input 0x80000010 Link 3 output 0x8000000C Link 2 output 0x80000008 Link 1 output 0x80000004 Link 0 output 0x80000000 (base address of memory)

So, for example, a process communicating across link three would read from address 0x8000001C and write to address 0x8000000C. Note that there are special instructions used for communication.

Programs communicate across a link by executing an input (IN) instruction or output (OUT) instruction. Parameters to these instructions are the memory-start address of the data and the length of the data block. When executed, the input or output instruction invokes the link engine. Once the instruction is started, the CPU is free to go ahead and do something else.

The link hardware acts autonomously, stealing cycles from the processor to get data from memory and pass it over the link channel. After every byte sent, the receiving transputer sends an acknowledgement signal and stores the data in the buffer of the receiving process. If there is no such receiving process, the receiving transputer doesn't acknowledge the byte. The sending transputer still waits for an acknowledgment, though. So a receiving process must be started to receive the byte, or the sender will block (i.e., wait) until there is one.

When the message has been transferred, the communicating processes are placed back on the process ready queues (maintained internally by the transputer's microcoded scheduler). As a result of the internal link engine stealing cycles from the CPU, there is some small CPU overhead once the communication begins.

Because the link engines don't do any buffering, communications can only take place when a sending process and a receiving process are both ready to communicate. This means that one side has executed an output instruction and the other side has executed an input instruction.

A process that wants to communicate through a hardware link will always be descheduled. The transputer will reschedule that process only after the message has been sent or received. Thus, transputer processes sleep as long as they're waiting for communication.

When a process is descheduled, the transputer puts information about it at the end of a "ready" queue. This is a queue of processes ready to run when the current process reaches a descheduling point. It can take some time before the process works its way back to the start of the queue and is able to run again. Because of this delay, for you to use the hardware links efficiently, you should use the largest possible message. By doing this a process will be descheduled a minimum number of times. In this case, you can see that it would make sense to calculate and pass 100 or even 1,000 pixels worth of data at a time, rather than just one pixel.

## **Event Channel**

In addition to the links, there is another hardware mechanism that acts as a channel. The external Event pin on the transputer uses location 0x80000020 as its "channel." Whenever the external event pin receives a signal, any process waiting on this channel is awakened. This is the transputer's equivalent of an interrupt. In this sense it is a one-way channel, since a process must continually wait on the channel (for input) by executing an IN instruction, but never sends data through it. The length of the expected message does not matter as no data is actually transferred through this channel; thus it makes the most sense to input a byte from it as this is the smallest unit. Caution: This pin is "edge-triggered," which means that the smallest glitch will latch it. Also note that the pin must be pulled low before it can be triggered again.

#### **On-chip Timers**

Another unique feature of the transputer are its on-chip timers that can be set or read by a program. There are several considerations that made it essential that the transputer have an on-chip timer. First, it is necessary to be able to "timeout" (i.e., abort after a certain amount of time has elapsed) on a link channel if communication is not taking place. This requires a clock to check the elapsed time during which no communication occurs. Second, the unusual multiprocessing ability of the transputer requires the microcode scheduler (which schedules processes to be run) to swap processes in a "fair" manner. This can prevent one process from "hogging" the CPU all the time. Normally, process scheduling is implemented at the software level in an operating system, but the transputer permits multiple processes to be run on the chip at the assembly code level. A scheduler is built into the microcode that gives each

process a timeslice. It tries to be fair and give each process a relatively equal slice of CPU time, although a programmer can defeat its "fairness" by not using instructions that can cause descheduling. In order to do this, the scheduler needs a clock. Programmers can take advantage of this clock to schedule processes themselves. A process can be programmed to sleep for a certain amount of time, then "wake up" and continue.

The transputer has two on-chip timers, one for high priority processes and one for low priority processes. Each timer is a 32-bit register. The high priority timer ticks once each microsecond for a period of about 71 minutes, while the low priority timer ticks once each 64 microseconds for a longer period of about 76 hours. A process can only access the timer that is associated with its own priority level.

Times between (now + one tick) and (now + 0x7FFFFFF ticks) are "in the future." If you attempt to wait for them, the process will deschedule and wait for the specified time to appear in the timer register. Times between (now + 0x80000000) and now are in the past. If you attempt to wait for them you won't wait at all, that is your process will not be descheduled. This mechanism can prevent a process from going to sleep for over three days (76 hours) in the case that it just wanted to pause for a brief millisecond, but a high priority process preempted it for two milliseconds before it could deschedule itself. Thus, what the process thought was the "future" became the "past" before the process could actually execute.

# **Transputer Instruction Set**

### The Basic Types of Transputer Instructions

Each transputer instruction consists of a single byte divided into two four-bit parts. The four most significant bits are a **function code**, and the four least significant bits are a **data value** (see Figure 3-1). This allows for 16 function codes or 16 instructions; however, one of the 16 instructions (operate) allows indirect access to many more instructions.

# Function Data Bits 7 to 4 3 to 0

Figure 3-1 Function Code and Data Value within a byte.

Based on this arrangement, transputer instructions can be divided into two categories: **direct** and **indirect** instructions. Inmos studied which instructions are most often executed and designed the transputer so that the most common instructions are encoded into a single byte and execute very rapidly. These are the direct instructions. The remaining instructions require multiple bytes of memory and are referred to as indirect instructions.

## **Direct Instructions**

The most common programming operations are the direct instructions. As a result, the direct instructions have been designed to be the fastest and most compact instructions on the transputer. Inmos claims that most programs on the transputer will typically spend 70 percent of their time executing direct instructions.

Direct instructions can be broken into three general groups:

ï Stack operations;ï Prefix functions; andï Flow control instructions.

The transputer's architecture consists of a three register stack that uses registers A, B, and C. Register A is at the top of the stack and register C is at the bottom. Table 3-1 is a full list of the direct instructions available for the INMOS transputer.

Table 3-1. Direct Instructions

Opcode Mnemonic Description 0X j jump 1X ldlp load local pointer 2X pfix prefix 3X ldnl load non-local 4X ldc load constant 5X ldnlp load non-local pointer 6X nfix negative prefix 7X ldl load local 8X adc add constant 9X call call subroutine AX cj conditional jump BX ajw adjust workspace CX eqc equals constant DX stl store local EX stnl store non-local FX opr operate

# **Stack Operations**

To load a constant value into a transputer register, use the LDC (load constant) instruction.

1. When the transputer executes *load constant*, the low order nibble of the instruction is placed in the lowest four bits of the operand register.

2. The contents of B are pushed into the C register, and the contents of A are pushed into B (the registers form a stack).

3. Finally, the contents of the operand register are placed into the A register.

# Example 3-1

#### **Register Contents:**

A 10 B 20 C 30

## **Instruction Executed**

ldc 5; This loads the value 5 into the A register.

# **Result:**

A 5 B 10 C 20

Comment: In this example, the contents of C are "lost" (i.e., pushed off the bottom of the stack).

## Example 3-2

For the same initial values of A, B, and C used in Example 3-1, the instruction sequence:

#### **Register Contents:**

A 10 B 20 C 30

# **Instructions Executed**

ldc 9 ldc 2

## **Result:**

A 2 B 9 C 10

**Comment:** When the ldc 9 is executed, the contents of B are pushed into C, and the contents of A are pushed into B. Next, 9 is placed into the A register. When the ldc 2 is executed, the stack is pushed again, B is pushed into C, and A is pushed into B before 2 is placed into register A.

The add constant instruction is used to add a constant value to a register and is represented in mnemonic form by ADC. An example using ADC follows:

1. The lower nibble of the *add constant* instruction is placed in the lower four bits of the operand register.

2. The contents of the operand register are then added to register A.

## Example 3-3

**Register Contents:** A 10

A 10 B 20 C 30

**Instructions Executed** ldc 6 adc 3

# **Result:**

A 9 B 10 C 20

**Comment:** First, 6 is loaded into register A. This pushes the old contents of A and B, while the old contents of C are pushed off the stack. Then, 3 is added to A (which contains 6 after the ldc 6) and 9 remains.

One of the important points to remember is that, if the addition **overflows** (i.e., causes the A register to wrap around from 0x7FFFFFF to 0x80000000 in either direction), the Error flag is set. This means that, if the most significant bit of A changes because of an add constant instruction, the Error flag is set.

## Workspaces

Besides the register stack, a program must also access the main memory to perform operations. The transputer extends the register stack model to address memory in a stack-based fashion. Inmos, however, chose not to use the word "stack" in their documentation for memory-based stacks. Instead Inmos calls them "workspaces"; however, they are simply stacks in memory. So if the word "workspace" seems foreign to you, just mentally substitute "stack" wherever you see it.

Workspaces are organized as "falling" or "decreasing" stacks, in that the top of the workspace grows towards low memory. (In other words, towards the most negative address 0x80000000. Recall that addresses are signed.) All workspace-based operations must be word-aligned. Whenever you are addressing memory you must do so on addresses that are multiples of four.

There is a special register that the transputer uses just to contain the address at the top of the workspace. It is called the *workspace pointer* and is abbreviated *Wptr*.

*Wptr* must always contain a word-aligned value; it must point to the beginning of a word (not a byte) in memory. Since the transputer has a 32-bit word length (or four bytes), the *Wptr* is always an even multiple of four.

To retrieve a value from a workspace, use the load local instruction.

The *load local* instruction:

1. Pushes B into C;

2. Pushes A into B; and

3. Loads the 32-bit value into A that is located at the address of four times the operand added to the workspace pointer.

## Example 3-4

This example uses the following values for the registers and memory:

#### Registers

A 10 B 20 C 30 Wptr 10004000

Memory 10004000 5 10004004 7 10004008 9

If the following instruction is executed: ldl 0

Then the value at 10004000 is loaded into A, resulting in: A 5 B 10 C 20

If instead, you execute: ldl 1

Then the value at 10004004 is loaded into A, resulting in: A 7 B 10 C 20

In a similar fashion, if you execute: ldl 2

It will then yield: A 9 B 10 C 20

**Comment:** In all of the cases shown in Example 3-4, the workspace remains unchanged, while the operands in the *load local* instructions refer to word-offsets (four bytes) from the workspace pointer.

Use the store local instruction to place values from the A register into a workspace.

Just as in the case with the *load local* instruction, *store local* :

1. Calculates the address of a memory location by adding four times its operand to the workspace pointer.

2. It then places a copy of the contents of the A register at that location.

# Example 3-5

Again, using the following values for the registers and memory:

## **Registers:**

A 10 B 20 C 30 Wptr 10004000 Memory: 10004000 5 10004004 7 10004008 9

If you execute a: stl 0

Then the value at 10004000 is replaced by A and thus: 10004000 10 10004004 7 10004008 9

If instead, you execute: stl 1

Then the value at 10004004 is replaced by A and thus:

10004000 5 10004004 10 10004008 9

And likewise (if instead you execute): stl 2

Yields: 10004000 5 10004004 7 10004008 10

Comment: In all of the above cases, the A, B, and C registers remain unchanged.

Use the load local pointer instruction to calculate addresses related to the workspace.

The load local pointer instruction:

1. Loads the workspace pointer plus four times the operand into the A register (after pushing B into C and A into B).

### Example 3-6

Using the same values as Example 3-5:

#### Registers

A 10 B 20 C 30 Wptr 10004000

Then: ldlp 0

Results in: A 10004000 B 10 C 20

If instead, you execute: ldlp 1

Then you have: A 10004004 B 10 C 20

And likewise (if instead you execute): ldlp 2

Yields: A 1004008 B 10 C 20

Comment: In all of the above cases, the workspace remains unchanged.

In the previous workspace-related instructions, the word "local" is key. All of the operations are local to the workspace in use. But suppose you want to randomly access some memory location that isn't in the current workspace? The transputer provides for non-local memory accessing.

The load non-local instruction allows you to access any address in memory.

Load non-local works in about the same way that load local does, except that:

1. Register A is used as a base address instead of the workspace pointer Wptr.

2. The B and C registers are unaffected by this operation. Also note that the address in A must be word-aligned (divisible by four).

## Example 3-7

Given the following:

## Registers

A 10004000 B 20 C 30

#### Memory

10004000 5 10004004 7 10004008 9

Then:

ldnl 0

Yields:

A 5 B 20 C 30

If instead, you execute: ldnl 1

Then you have: A 7 B 20 C 30

If instead you execute:

ldnl 2

It yields: A 9 B 20 C 30

**Comment:** A common technique is to:

1. First load register A with an address by way of the load constant instruction.

2. Then load the contents of the address using *load non-local* with an operand of zero: ldc address ldnl 0

# Example 3-8

The reverse operation, *store non-local*, places the contents of the B register to the word-aligned address pointed to by register A.

So given:

# Registers

A 10004000 B 20 C 30

#### Memory

10004000 5 10004004 7 10004008 9

Then: stnl 0

Yields: 10004000 20 10004004 7 10004008 9

If instead, you execute: stnl 1

Then you have:

10004000 5 10004004 20 10004008 9

If instead you execute: stnl 2

It yields:

10004000 5 10004004 7 10004008 20

There is an analagous load pointer instruction to the load local pointer called the load non-local pointer.

The load non-local pointer instruction:

1. Loads the contents of the A register plus four times the operand into the A register.

**2.** Registers B and C are unaffected.

#### Example 3-9

So if you have in this example:

A 10004000 B 20 C 30 Then: Idnlp 0 Yields: A 10004000 B 20 C 30 While:

ldnlp 1

Yields: A 10004004 B 20 C 30

And: ldnlp 2

Yields: A 10004008 B 20 C 30

Space on the Workspace

Space on the workspace is allocated and deallocated using an adjust instruction called *ajw* (for adjust workspace). Because the workspace grows towards the low memory addresses, you must allocate memory to the workspace by:

1. Decrementing the workspace pointer (by adjusting the workspace with a negative number); and

2. Deallocating space by incrementing the workspace pointer.

# Example 3-10

In this example, all the addresses are hexadecimal:

i This allocates two words (eight bytes) to the workspace:

; Wptr = 10004008 before the ajw

ajw -2

; Wptr = 10004000 after the ajw

i While the following deallocates two words from the workspace:

; Wptr = 10004008 before the ajw

ajw 2

; Wptr = 10004010 after the ajw

## **Prefix Functions**

With only four bits for data in an instruction byte, the maximum operand any instruction can have is 15. To allow values greater than 15 to be loaded into a register, other instructions are required to load the operand register. Two more instructions allow the operand of any instruction to be extended in length. These instructions load the data into the operand register that a future instruction can then use. These two instructions are *prefix* and *negative prefix*.

#### **Prefix Instruction.**

The *prefix* instruction:

1. Loads its four data bits into the operand register; and

2. Then shifts the operand register to the left by four places.

Consequently, operands of any length can be represented up to the length of the operand register (which is 32 bits).

## Example 3-11

To load the hexadecimal value 0x324 into the operand register, the code would be: pfix 3 pfix 2 ldc 4

After this sequence, register A would contain 324 (hexadecimal). The last instruction is a *load constant*, since the prefix instruction always shifts the operand register to the left by four places after placing its data bits in the lower four bits.

## **Negative Prefix**

Negative numbers are loaded in a similar fashion using the *negative prefix* instruction. The *negative prefix* instruction is similar to the *prefix instruction* except that it complements the operand register before shifting it to the left by four places.

#### Example 3-12

To load the value -31 (represented as FFFFFE1) into the operand register, the code would be:

nfix 1 ldc 1

After this sequence, A would contain -31 [hexadecimal FFFFFE1]. The nfix 1 instruction should be examined in detail:

ï First, 1 is loaded into the operand register.

ï Then all the bits are complemented, so the operand register now contains FFFFFFE.

ï The operand register is shifted to the left four places and contains FFFFFE0 at the end of the *nfix 1* instruction.

**Comment:** Normally, you will never have to deal with the prefix instructions because most assemblers take care of the prefix bytes for you and allow you to write code like: ldc 0x4321

Then the assembler automatically generates: pfix 4 pfix 3 pfix 2 ldc 1

# **Flow Control Instructions**

Most computer programs need to test a set of conditions. Then they decide what part of the program to execute, based on the results of the test. The transputer provides these necessary instructions for controlling the flow of execution.

The most obvious instruction for controlling the execution flow is the *jump* instruction. *Jump* causes the instruction pointer to be incremented by the amount of the operand. *Jump* is a *relative* instruction because the target address is computing by adding the operand to the current address (rather than loading some absolute address).

Most assemblers simply allow the name of a label to reference where to jump (see Example 3-13). The mnemonic for jump is "j."

#### Example 3-13

j THERE ldc 2 ldc 1 THERE: ldc 0

The *ldc 2 and ldc 1* will be skipped in the above program fragment because the *jump* instruction causes the flow of program execution to be transferred to the *ldc 0* instruction.

It has already been mentioned that the computation is relative. An equivalent way of expressing the program in Example 3-13 would be:

00004000 j 2 00004001 ldc 2 00004002 ldc 1

#### 00004003 ldc 0

Because all of the above instructions are direct, they are all one byte long. Suppose the numbers on the left are the instruction addresses in memory:

**1.** The "jump" with operand two (or the j 2 instruction) adds two to the instruction pointer.

**2.** The instruction pointer is incremented prior to executing the instruction, so when it starts executing j 2, it contains 00004001.

3. Then the j 2 instruction causes two to be added to the instruction pointer so that it will contain 00004003.

4. The instruction pointer continues executing instructions starting from 000040003.

Tip: Don't store information across a jump. The *jump* instruction can potentially trash the contents of the A, B and C registers.

*Jump* is actually a descheduling instruction: If another process is pending, the current process may be suspended and the pending process started (or resumed). The newly scheduled process may then use the registers as it will, thus invalidating any data in the registers before the "jump" in the first (and now sleeping) process.

There are times in a program when you might want to return to the point that is just after control was transferred. That way, a frequently used code fragment can be repeatedly used without having to contain multiple copies in the program. Such code fragments are known as *subroutines*, since they are part of the program but not inside the main routine. The main routine transfers executions to subroutines; eventually, the subroutine transfers executions back to the main routine. Subroutines are implemented through the traditional *call* instruction:

**1.** The *call* instruction pushes the C register, the B register, the A register, and the instruction pointer (in that order) onto the workspace.

**2.** Then it jumps to the "relative" address specifed by the instruction pointer that has been added to the operand of the call.

3. The workspace pointer is adjusted (decremented) by four to compensate for the information pushed onto it.

**Comment:** The corresponding *return* instruction, which returns control to the main line routine (mnemonic RET), is not a direct instruction and is two bytes long. When the *return* instruction is executed, any workspace claimed by the subroutine should be released by an *ajw* instruction) so that the *Wptr* has the same value it had prior to calling the subroutine.

The state of the workspace after the call instruction is:

## **Address Saved Values**

Wptr+4 (old Wptr pointed here) Wptr+3 C register Wptr+2 B register Wptr+1 A register Wptr+0 instruction pointer (Iptr)

You might recall that the workspaces grow towards low memory; after a call, the workspace pointer will contain four less than the old value. Like the *jump* instruction, *call* jumps to the "relative" address specified by the operand plus the instruction pointer.

#### Example 3-14

An example of a subroutine follows. This routine just decrements the single parameter it passes:

```

ldc 4

stl 0 ; place parameter on stack

call decrement

...

parameter = 5

locals = 0

decrement:

ajw -locals

ldl parameter

adc -1

stl parameter

ajw locals

ret

```

In Example 3-14, the first parameter to a routine is located at five words above the current workspace pointer because four items were pushed on the workspace as a result of the call instruction.

Also notice that to allocate local variable-space, you use ajw's at the start and end of the subroutine: The first allocates stack space by decrementing the *Wptr*; the second deallocates the stack space by incrementing the*Wptr*. In Example 3-14, the ajw's are not needed, since local variables were not used; they are there to help illustrate how a typical subroutine looks.

In Example 3-14, the first two lines above the decrement routine are directives to the assembler to replace the symbolic names *parameter* and *ws* with the constants on the right of the equals sign. This makes the code more readable because you're using symbolic names rather than numbers. Some assemblers use the "EQU" mnemonic for this directive, others use "#define" just like C.

In the code used in Example 3-14, the main routine:

1. First pushes the value it wants decremented on the stack, then it calls the decrement subroutine.

**2.** Next, the subroutine allocates stack space by adjusting the stack according to the number of local variables it needs (in this case, zero). This way, the local subroutine can use the stack for its own computations while preserving the data already put there by the main line routine.

The conditional jump (cj) instruction jumps if the value in the A register is false (zero), but not if its true (nonzero).

1. If the *conditional jump* is taken, the contents of A, B, and C are unaffected.

**2.** If the *conditional jump* is not taken, then the A register is popped and replaced by the contents of B and the contents of C are duplicated into the contents of B. To illustrate the usage of *cj*, let's modify the subroutine from Example 3-14 to decrement the parameter it has passed to zero, but not below zero. In Example 3-15, the routine will have to test if the parameter is zero, and if it is, return without decrementing the parameter.

#### Example 3-15

ldc 4

stl 0 ; parameter to pass call decr\_to\_zero ... parameter = 5 locals = 1 decr\_to\_zero: ajw -locals ldl parameter stl 0 ; save in a local cj return ; if zero, skip ldl 0 ; reload, cj popped A adc -1 stl parameter

return: ajw locals ret

In this program, the following sequence occurs:

1. The parameter is pushed on the workspace and then the subroutine is called.

2. First, the subroutine *decr\_to\_zero* adjusts the workspace for the number of local variables it will use (in this case, one).

3. Next, it retrieves the parameter that was passed and saves it in this local variable.

**4.** Then the *cj* instruction tests the A register for zero. If the paramater was zero, A will be zero and the jump will be taken. The workspace that was allocated for local variables will be deallocated, and the subroutine will return to the main routine. If on the other hand (as in this instance where parameter is four) the parameter is nonzero, then the *cj* will fail to take the jump and the A register will be popped.

**5.** The subroutine continues executing through the *ldl* 0 instruction. *ldl* 0 retrieves the value of the parameter, which is then decremented.

**6.** Finally, the local workspace is deallocated and the subroutine returns. Note that the local variable in this instance was used simply to temporarily hold a result, since *cj* pops the register stack. It is often necessary to compare two values in a program. The *equals constant* (eqc) instruction compares the contents of the A register with the operand and replaces the contents of A with zero if the operand and A were not equal, and with one if they were equal. The B and C registers are unaffected.

#### Example 3-16

Let's modify the subroutine in Example 3-15 so that it takes a parameter larger than one and decrements it to one, but not lower. The code could look like:

```

ldc 4

stl 0 ; parameter to pass

call decr_to_one

...

parameter = 5

locals = 1

decr_to_one:

ajw -locals

ldl parameter

stl 0 ; save in a local

eqc 1

```

```

cj continue ; if one, skip

```

j return

continue: ldl 0 ; reload the parameter adc -1 stl parameter

return: ajw locals ret

In Example 3-16, the parameter is tested to see if it is one by the eqc 1 instruction.

**1.** If it is one, the A register will contain 1 (true = 1). If it is zero, the result of the eqc 1 test was false (false = 0).

**2.** If the A register contains zero, it means that the test has failed. For instance, the parameter was not one, so the cj tests the A register for zero and jumps if A is zero. If the parameter is not one, the subroutine skips ahead to the where the continue label points (*ldl* 0).

**3.** If on the other hand the cj is not taken, then the A register contained something nonzero. Since the result of an eqc is only one or zero, this means that A contains one, which means the eqc 1 yielded true. In this case, the subroutine unconditionally jumps to the return point.

#### **Summary of Direct Instructions**

**J** *jump* transfers the flow of execution. Jumps are instruction-pointer relative (i.e., the operand is added to the instruction pointer to calculate the location of the next instruction to be executed). *Jump* is also a descheduling breakpoint.

**LDLP** *load local pointer* instruction loads the workspace pointer, plus four times the operand register, into A. This gives you the address of a value on the workspace.

**PFIX** *prefix* loads the lower nibble of its operation code into the operand register and then shifts the operand register to the left by four places.

**LDNL** *load non-local* loads the value pointed at by the address calculated by the workspace pointer, plus four times the operand register, into A.

**LDC** *load constant* loads the lower nibble of its operation code into the lower nibble of the operand register and then loads the operand register into A.

LDNLP load non-local pointer loads A plus four times the operand.

**NFIX** *negative prefix* loads the lower nibble of its operation code into the operand register and then inverts all the bits in the operand register and shifts the register to the left by four places.

LDL load local loads the value at the word-offset of the operand register into A.

**ADC** *add constant* loads the lower nibble of its operation code into the operand register, then adds the contents of the operand register and A.

**CALL** *call* pushes the C, B, and A registers, as well as the instruction pointer on the workspace. It then jumps to the relative address specified by the operand register.

CJ conditional jump jumps to the relative offset in the operand register if the value in A is zero (false).

AJW adjust workspace adds four times the operand register to the workspace pointer.

EQC equals constant tests the value in A against the operand register.