# **The Transputer Handbook**

Ian Graham and Tim King

Prentice Hall New York London Toronto Sydney Tokyo Singapore

First published 1990 by Prentice Hall International (UK) Ltd 66 Wood Lane End, Hemel Hempstead Hertfordshire HP2 4RG A division of Simon & Schuster International Group

© Prentice Hall International (UK) Ltd, 1990

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form, or by any means, electronic, mechanical, photocopying, recording or otherwise, without prior permission, in writing, from the publisher. For permission within the United States of America contact Prentice Hall Inc., Englewood Cliffs, NJ 07632.

Printed and bound in Great Britain at the University Press, Cambridge

Library of Congress Cataloging-in-Publication Data

Graham, Ian, 1947– The transputer handbook / Ian Graham and Tim King. p. cm. ISBN 0-13-929134-2 : \$33.95 1. Transputers. I. King,Tim, 1954–. II. Title. TK7895.T73G73 1990 004'.35–dc20 90-7072 CIP

British Library Cataloguing in Publication Data

Graham, Ian, 1947– The transputer handbook.

1. Computer systems. Parallel-processor systems

I. Title II. King, Tim 004.35

ISBN 0-13-929134-2

1 2 3 4 5 94 93 92 91 90

## Contents

| Preface |            |                              |    |

|---------|------------|------------------------------|----|

| No      | otatio     | nal Conventions              | x  |

| Tr      | adem       | arks                         | xi |

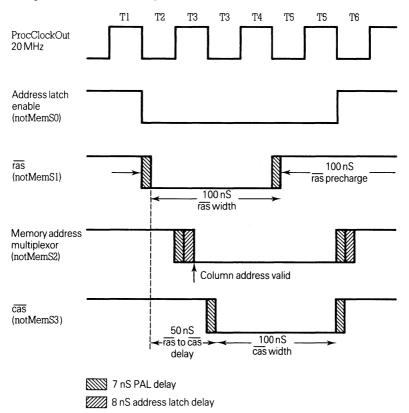

| 1       | Intr       | oduction                     | 1  |

|         | 1.1        | Why more power?              | 1  |

|         | 1.2        | How do we get more power?    | 3  |

|         | 1.3        | Types of parallel computer   | 4  |

|         | 1.4        | MIMD architectures           | 5  |

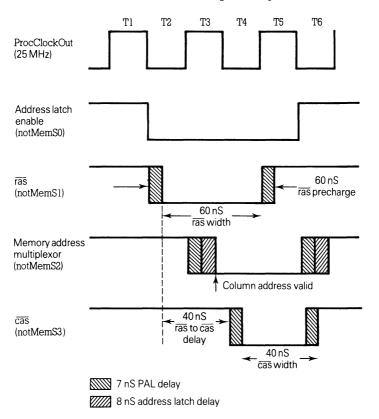

|         | 1.5        | The transputer               | 6  |

| 2       | The        | Transputer                   | 7  |

|         | 2.1        | Microprocessor architectures | 9  |

|         | 2.2        | Transputer architecture      | 11 |

|         | 2.3        | The transputer family        | 15 |

| 3       | The        | Instruction Set              | 18 |

|         | 3.1        | The evaluation stack         | 18 |

|         | 3.2        | Simple instructions          | 20 |

|         | 3.3        | Encoding                     | 22 |

|         | <b>3.4</b> | Further instructions         | 27 |

|         | <b>3.5</b> | Position-independent code    | 27 |

|         | 3.6        | Flow of control              | 28 |

|         | 3.7        | Process scheduling           | 29 |

|         | 3.8        | Channels                     | 31 |

|         | 3.9        | Timer                        | 33 |

|         |            |                              |    |

|   | 3.10 | Alternation                                  | 34  |

|---|------|----------------------------------------------|-----|

|   | 3.11 | Error handling                               | 36  |

|   | 3.12 | The extended instruction set                 | 37  |

|   | 3.13 | Graphics support                             | 38  |

|   | 3.14 | Floating-point support                       | 41  |

|   | 3.15 | Debugging instructions                       | 43  |

|   | 3.16 | Processor identification                     | 45  |

| 4 | Lov  | v-Level Programming                          | 47  |

|   | 4.1  | Linking code                                 | 47  |

|   | 4.2  | Code generation issues                       | 49  |

|   | 4.3  | Bootstrapping                                | 53  |

|   | 4.4  | Debugging                                    | 55  |

|   | 4.5  | A disassembler                               | 58  |

| 5 | Tra  | nsputer Languages                            | 63  |

|   | 5.1  | Occam                                        | 65  |

|   | 5.2  | Runtime library support for parallelism in C | 76  |

|   | 5.3  | Adding parallel syntax to C                  | 84  |

| 6 |      | tware Environments                           | 88  |

|   | 6.1  | Express                                      | 90  |

|   | 6.2  | Linda                                        | 91  |

|   | 6.3  | Trollius                                     | 93  |

|   | 6.4  | Mach                                         | 93  |

|   | 6.5  | Meikos                                       | 94  |

|   | 6.6  | Helios                                       | 95  |

|   | 6.7  | UNIX                                         | 97  |

| 7 |      | nsputer Family Hardware                      | 101 |

|   | 7.1  | Hardware architecture                        | 101 |

|   | 7.2  | The transputer processors                    | 109 |

|   | 7.3  | Transputer support devices                   | 112 |

| 8 |      | tem Integration                              | 120 |

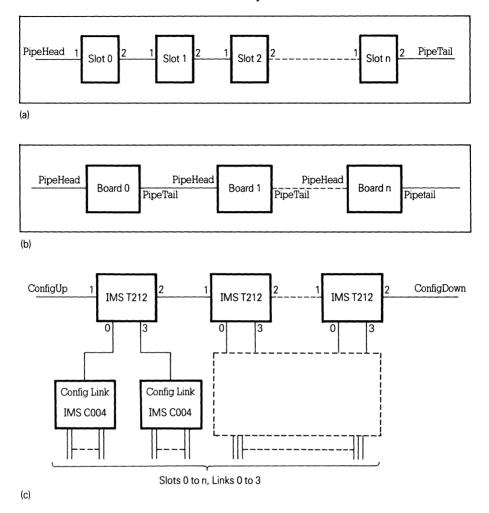

|   | 8.1  | Connecting transputer links                  | 120 |

|   | 8.2  | Reset, analyse and error schemes             | 126 |

|   | 8.3  | Transputer modules and motherboards          | 128 |

|   | 8.4  | PC and other boards                          | 135 |

|   | 8.5  | Workstations                                 | 137 |

|   | 8.6  | Large-scale transputer systems               | 137 |

| 9 | Tra  | nsputer Hardware Design                      | 143 |

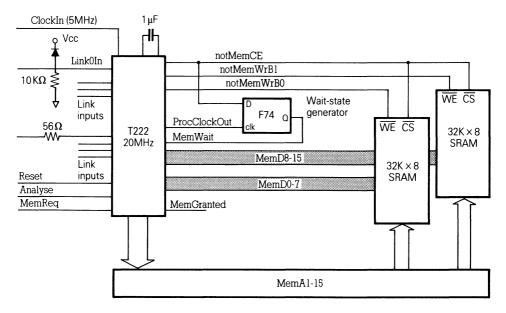

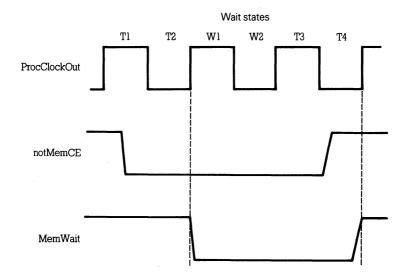

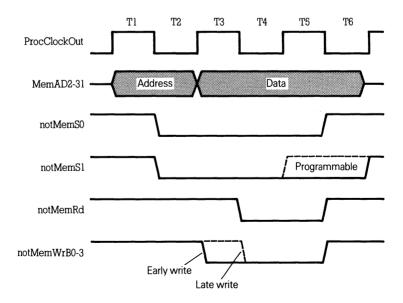

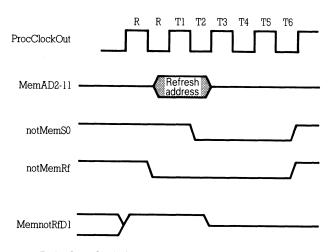

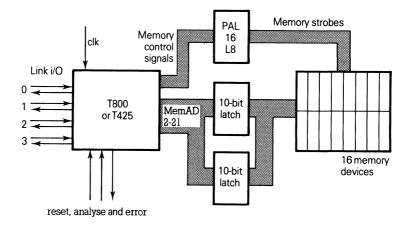

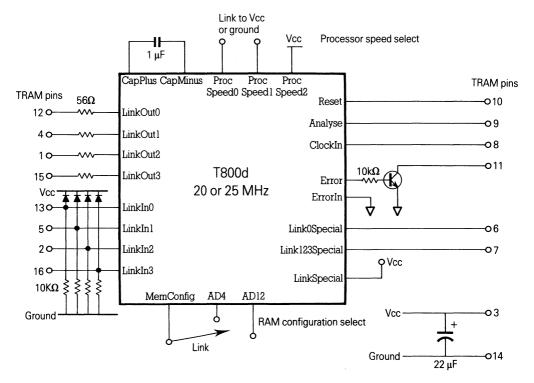

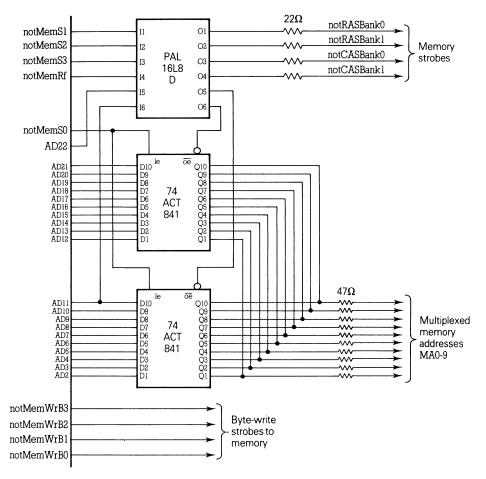

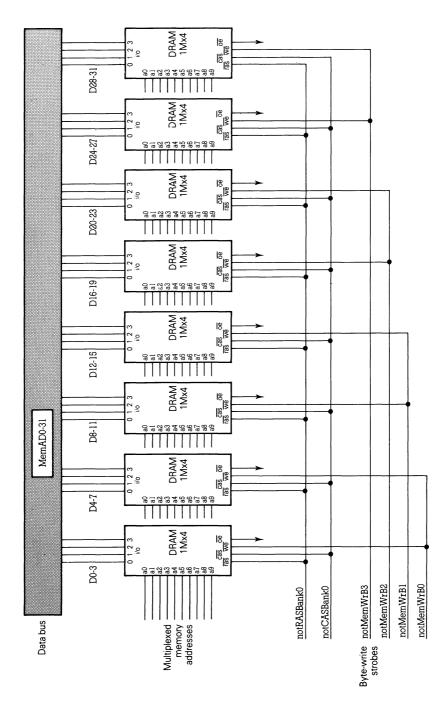

|   | 9.1  | Sixteen-bit transputer memory interface      | 143 |

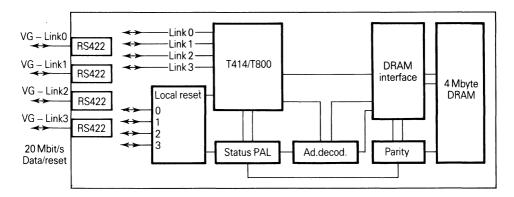

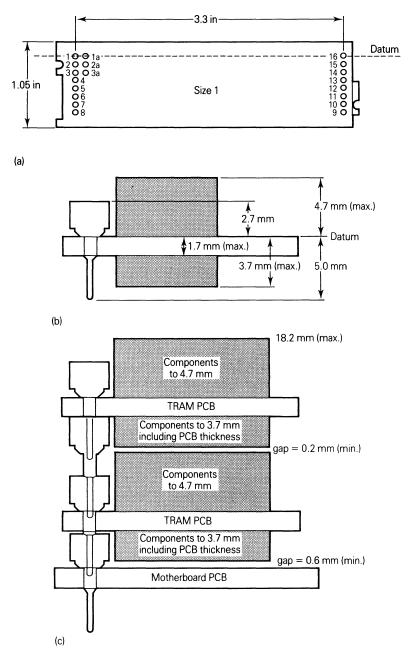

| <ul><li>9.2 Thirty-two bit programmable memory interface</li><li>9.3 Design example – a size 2 TRAM</li></ul> | 147<br>151        |

|---------------------------------------------------------------------------------------------------------------|-------------------|

| Appendix A: Instruction Set Reference<br>Appendix B: Memory Configuration Program<br>Appendix C: Product list | 160<br>176<br>181 |

| References and Bibliography                                                                                   | 193               |

| Index                                                                                                         | 195               |

## Preface

In this book we describe the software and hardware implementation of transputer parallel processing systems. We hope to bring together information from a multitude of sources in a more readily accessible form.

This book is not intended as a substitute for a study of engineering data when detailed design decisions are to be made, but should act as a guide to the capabilities of the transputer family and transputer-based systems. This should help the reader to choose the software and hardware solution that will best suit their problem.

Neither of us is an employee of INMOS Ltd, but we are both transputer users by choice, one in an academic environment, the other as head of a research-oriented software development company. Thus our opinions are our own, and do not always coincide with those of INMOS, and at times may be directly opposed. Despite this we would like to acknowledge the help provided by INMOS in the preparation of this book.

We would like to thank the following for permission to reproduce diagrams in the book: INMOS for Figures 2.1, 7.1–7.10, 8.1, 8.7–8.10 and 9.6; Meiko for Figure 8.11; and Parsytec GmbH for Figures 8.6 and 8.13–8.15.

The majority of our programming examples are in C, rather than occam, and we assume that the reader has a knowledge of C.

One of us (I.D.G.) thanks the University of Bath for a Visiting Fellowship, during the tenure of which this book was completed. We would also acknowledge the help provided by those transputer hardware and software manufacturers whose products are mentioned in the text.

| Shepton Mallet | I.D.G. |

|----------------|--------|

| 1990           | T.J.K. |

## **Notational Conventions**

Internal processor registers and flags are shown in italics:

A, B, C, Error, HaltOnError

Program examples and processor opcodes are shown in monospace typewriter font:

writeln("Hello World"); ldl 5

Signal and pin names are shown in the monospace font:

BootFromRom, notError

Hexadecimal numbers are preceded by 0x, and shown in the monospace font:

0xF (4 bits) 0xF0 (8 bits) 0xF0F1 (16 bits) 0xF0F1F2F3 (32 bits)

## Trademarks

UNIX is a trademark of AT&T.

VAX and PDP-11 are trademarks of Digital Equipment Corp.

IBM is a trademark of International Business Machines.

Computing Surface, In-Sun Computing Surface are trademarks of Meiko Ltd.

Helios is a trademark of Perihelion Software Ltd.

•, Immos, IMS and occam are trademarks of INMOS Limited. INMOS is a member of the SGS-THOMSON Microelectronics Group.

## Chapter 1 Introduction

The rush to provide faster and faster computer systems seems to have taken us headlong from the classic IBM mainframe of the 1960s through the departmental minicomputers, typified by the VAX of the 1970s into the massive flood of personal computers during the 1980s. It is a well known but instructive cliché that the amount of computing now available in a wristwatch would have taken huge boxes of air-conditioned power thirty years ago.

The focus of the development of fast, innovative processors has shifted from the computer manufacturers to a small, and shrinking, group of semiconductor manufacturers. These semiconductor manufacturers continue to promise bigger (or rather smaller) and better devices each year, and there seems to be no limit to the amount of computing power that will eventually be available on your desktop.

Two questions need to be asked at this point: why do we need all this computing power, and how are we going to be provided with it?

### 1.1 Why more power?

This first question is often forgotten; computers just get faster and faster all the time. For many users, computers are already fast enough. Consider someone using a word processor or spreadsheet on a personal computer; so long as the text is displayed or the spreadsheet updated within a second or so then getting a faster computer so that the update takes half a second hardly seems worthwhile. These users have no real need of more computer power, and are happy with their system.

Other users can clearly see room for improvement. If the word processor has been replaced with a desktop publishing package then the speed with which the system responds may well become more critical. Unlike the previous system a character is represented on the screen by a pixel pattern defined by a chosen font. The computer system has to perform a significant amount of extra work in this case. All the word-processor software had to do to display a character was to load its value into a hardware register; the character generator built into the display circuitry would then cause the correct pixels to be sent to the screen.

The modern flexible font system places a much greater burden on the software. A software routine must locate the correct bitmap for the character, size and font required, possibly generating it from a stored set of Bezier curves. The computer must then set each individual pixel on the screen to represent the required character. All of this work is needed just to display a single character. There is then considerable extra effort required in order to scale pictures, move columns of text around a screen, change the width and format of columns and so on. The amount of extra work to be performed ranges from 100 to 1000 times more.

It is hardly surprising that a computer capable of providing excellent performance when faced with simple tasks suddenly shows its limitations when asked to handle a much more complicated program. What is sometimes not appreciated is exactly how much more complex desktop publishing is than simple word processing. So far as the user is concerned it is a simple step up from limited fonts and poor quality to multiple proportional fonts and high quality.

Current software users are becoming more critical of the user interface provided. Originally it was perfectly acceptable for a software package to have obscure commands that had to be typed before it could be persuaded to do anything. Users were not to be trusted with anything as complicated as a computer, unless they were willing to spend hours reading the manuals and attending training courses. It was also considered a matter of honor that individual companies developed a certain house style, so that pressing a particular key on one package might have a devastatingly different effect from the same key in a package from a rival manufacturer.

Modern developments have shown that good software should be intuitive. If the user has learned one program package then the next package, albeit from a different software house, should behave in a similar fashion. Standard screens have been replaced by windows, overlaid on other windows. More than one program can be run at the same time. The screen itself is capable of displaying complex graphics and variable-sized fonts. A mouse is used to select from iconic images of programs, while pull-down menus are used to select the different options.

This general improvement in the user interface has had yet another major impact on the amount of computer power required behind it. Graphical systems have become the standard for every computer user, rather than being used occasionally by specialists in order to plot a diagram or draw a graph. Graphics resolution has improved dramatically from  $320 \times 200$  pixels on the screen to  $1024 \times 768$  or more. All of this uses more and more computer power.

On the general scale, more computer power enables us to produce better models of the real world. These might be higher quality graphical models, quicker statistical models or more accurate engineering models. As our requirements for these models increase then our appetite for computer power also increases. Consider areas such as computer simulation, where a full simulation of an intricate piece of engineering such as a power station must be performed in order to verify the design. Even on the largest of present computers such simulations can take years.

There are many areas of potential computer applications that are not currently being addressed because the technology is simply too slow. Good examples here are concerned with getting the computer to do anything that the human brain is good at, such as voice recognition, image analysis and pattern recognition, artificial vision, and natural language understanding. We are a very long way from the science fiction of having a robot come into the room, recognize us and understand our natural speech. Current research into the software solutions to these problems suggests that huge amounts of computer power will be required.

#### **1.2** How do we get more power?

The preceding section put forward some arguments as to why more computing power is required now, and why we see no saturation of this requirement in the future. This section describes some of the problems in making computers faster and faster.

The underlying and absolute physical limitation is the speed of light. Certain semiconductor manufacturers seem to be suggesting that their particular technology has a rosy and unencumbered future, with faster and totally compatible models coming out each year for ever. This is, of course, impossible. The technology wall presented by the speed of light is at the top of a technology hill. Not only is it impossible to scale the wall, it also gets extremely difficult even to get close to it.

Desktop personal computers used to be based on microprocessors with an 8 MHz clock speed, and recent developments have seen the introduction of 33 MHz chips. At first glance this can be seen as the gradual, but irresistible, onwards march of technology. A more detailed examination shows that even this change has led to more problems than might first have been assumed.

Consider the problem of attempting to design a memory interface. As anyone who has bought a personal computer will know, a microprocessor with a clock rate of 16 MHz will not run twice as fast as one with a clock speed of 8 MHz. A normal dynamic memory chip will have an access time of between 80 and 100 nsec, and the faster the chip the more expensive it gets. It is possible to use static RAM devices, which have a much shorter access time, but which are perhaps ten times as expensive, and are not available in such high density packages as dynamic memory. Thus the memory is unlikely to be able to keep up with the 16 MHz processor. A common solution is to provide a cache memory of fast RAM, but this is expensive, and relies on the locality of programs and data.

Bus structures become much less useful as processor speeds increase. Until recently it was common for a microprocessor system to consist of a CPU board and some memory boards connected by a high-speed bus. However, processors are now sufficiently fast that memory access is unacceptably slowed by the physical layout of the bus and its associated capacitances. Even high-speed peripheral interfaces can no longer reside on the bus.

Part of the approach to solving these problems has been to place more of the required circuitry on a single chip. On-chip devices, such as cache memory, memory management units and floating-point units, are preferable as no external buffers are required and the distances involved are very small. Complex single-chip devices have been made possible by the development of very large scale integration (VLSI), which in its turn is encouraged by the requirement for more and more complex devices. The recent Intel processor, the i860, may have a reduced instruction set architecture but with more than one million transistors it is hardly a simple device. These complex chips have their own problems. The chips are difficult to manufacture with high yields, and are therefore expensive. They dissipate a lot of heat, which has to be removed from the chip in some way, and they require fast memory and generate fast signals, which places strict limits on board design.

An analogy to this problem is that of trying to get a drink in a crowded bar. The bartender starts to get overwhelmed, and so a replacement with more experience is brought in. He works faster, but still cannot cope with the increasing demand, and so another replacement is found who has been training for the Olympics. Although she is now racing from one side of the bar to the other, she still cannot cope. Efficiency is lost, more drinks are spilled and glasses broken.

The solution, of course, is to replace the single bartender with five or six who share the work. If the amount of work increases yet again, more staff are brought in to continue the service.

In order to produce more and more powerful computers we must provide power through multiple processors, working together to achieve a solution to a large shared problem. The techniques of parallel computation are applicable to all scales of processor, from the smallest to the largest, and will not be made obsolete by new technology, as we will always require more power than can be provided by any single processor, whatever its technology.

## **1.3** Types of parallel computer

There are many ways in which to define a taxonomy of parallel computers. An early attempt by Flynn (1966, 1972) divided computer systems into four major categories based on the number of instruction and data streams that are processed simultaneously. Flynn's categories are as follows:

- Single instruction stream, single data stream machines (SISD).

- Single instruction stream, multiple data stream machines (SIMD).

- Multiple instruction stream, single data stream machines (MISD).

- Multiple instruction stream, multiple data stream machines (MIMD).

The SISD architecture still describes most of today's large and small computers, where a single program executes using a single set of data. SISD machines can potentially have multiple functional units, such as vector processors or pipelines, as is common in today's 'uniprocessor' supercomputers.

SIMD machines execute the same instruction stream simultaneously on many sets of data – examples are array processors such as the ICL Distributed Array Processor (Reddaway, 1984). Systems with this architecture are restricted in the problems that they can solve, but are particularly suited to operations on large matrices.

MISD machines potentially execute many instructions in multiple streams on a single data stream. However, no examples of this machine organization seem to exist.

We will be concerned here principally with the MIMD machines, where multiple sets of possibly different instructions are executed concurrently on multiple data sets. This is the most general model, as it is possible to make a MIMD machine behave as either a MISD or SIMD machine by suitable programming.

The Flynn taxonomy provides a crude separation of machine types. For a more sophisticated analysis and alternative taxonomies the reader is referred to Hockney and Jesshope (1988) and Krishnamurthy (1989).

## **1.4 MIMD architectures**

In this book we discuss the hardware implementation and programming of machines of the MIMD type. Such systems are already common, and two main architectures have emerged which differ in how the processors communicate to share data and control. It is clear that the processors should communicate, either with each other or with a controlling processor, in order that the computing task may be distributed over the parallel system and the results of the computation collated.

#### 1.4.1 Shared-memory machines

In shared-memory systems the processors use a common pool of memory, normally with some hardware constraints to avoid memory access conflicts. Tasks communicate through shared variables, and code and data may also be shared by tasks running on different processors. One clear disadvantage of the shared-memory architecture is that a limited memory bandwidth must be shared by all the processors in the system. Thus as each new processor is added, the system performance does not improve linearly, but follows the law of diminishing returns. The amount of degradation is clearly very dependent on the application, and on the details of the memory architecture. The memory contention problem thus limits the number of processors that can be added to the system, and the large memory bandwidth required in the main memory adds to its cost.

#### 1.4.2 Distributed-memory machines

Alternatively, each processor may have its own local memory, and communicate with the others over hardware channels or links. The total memory bandwidth and instruction execution rate thus increase linearly as more processors are added to the system. The principal limitation of this message-passing architecture lies in the communication links. If in a system of n processors each must communicate directly with all of the others then n(n-1)/2 bidirectional links would be required. This would result in an impossibly complex architecture with even a modest number of processors. Thus practical solutions limit the number of hardware links to each processor, and provide either software or hardware message switching so that data and control information can be transferred between processors as the application requires. If this communications system and the topology of interconnection are not well designed, then communications overheads can severely limit the overall performance of the parallel machine.

## 1.5 The transputer

The INMOS transputer is the first single-chip microprocessor that provides a highspeed processor, fast inter-processor communications, and explicit support for multiple processes and multiple processor systems. The design aims were for a device that would be used in multiple processor message-passing systems, where each processor had its own physical memory, but with support for multiple shared-memory processes on each transputer. What the transputer does not provide, therefore, is any memory management on chip, or any support for off-chip memory management devices.

The intended application areas range from process control, with 1-50 loosely coupled processors, workstations with 4-16 processors, to computing accelerators and supercomputers with over 256 processors. The transputer is a reasonably recent development and yet it has already had a profound impact on the way in which certain types of problems are solved.

## Chapter 2 The Transputer

This chapter describes the architecture of the transputer family. In fact there is a fairly wide range of transputer devices available, but the family resemblance is very strong, and they all follow the basic outline described here. The family members are described in summary at the end of this chapter; more detailed information on the properties of individual devices is given in later chapters.

The basic components of all microprocessors are the instruction execution and decoding unit, often called the central processing unit or CPU, and an external memory interface or EMI. The CPU reads instructions from memory via the EMI and executes them sequentially. These two components make up the complete internals of older chips such as the Z80 or the 68000. Many modern chip designs concentrate on making this standard processor and memory interface combination run as fast as possible. However, increasing sophistication in VLSI technology has allowed designers to increase the level of system integration, and to include onchip functions that previously required external coprocessors. The most important additions are memory management, floating-point arithmetic, and instruction and data caches. In each case the provision of these functions on chip provides a substantial performance improvement over the same function implemented in external hardware.

Memory management hardware provides a mapping between the large virtual address space of the processor and the relatively small amount of physical memory. Each process can have a separate virtual address space and a different mapping into physical memory, and thus the memory used by one process can be protected from access by other processes and can appear to grow beyond the physical memory limits. The address translation hardware can be made to run much faster when the memory management module is integrated on the same chip as the CPU and memory interface.

The same is true of floating-point coprocessors. The performance of an external coprocessor may be limited by the speed at which the main processor can load it with instructions and operands and store the results in memory. The external coprocessor interface also tends to share the same signal lines as the EMI, and to

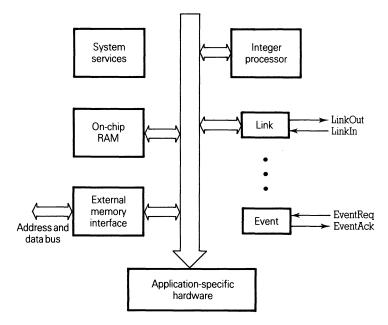

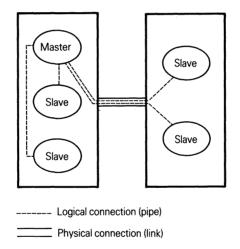

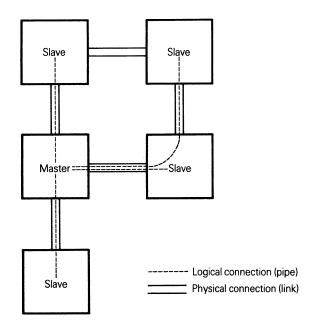

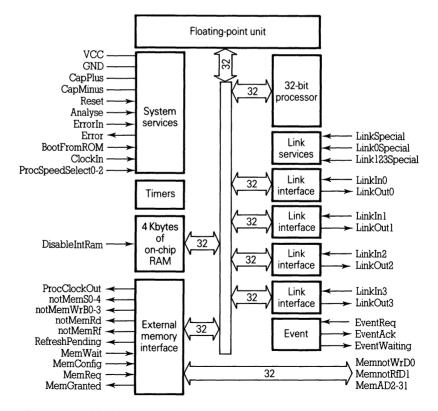

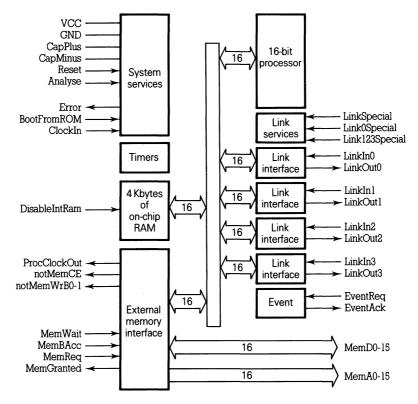

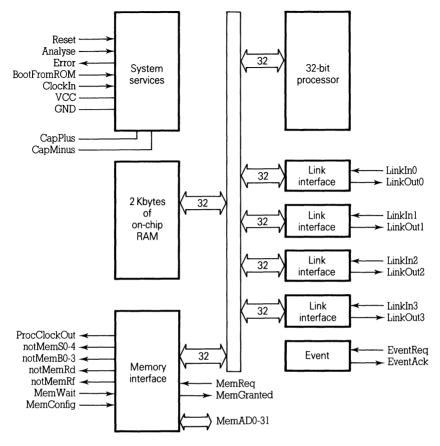

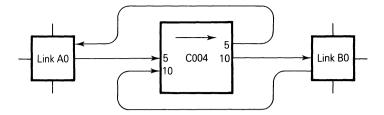

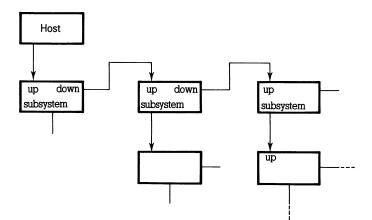

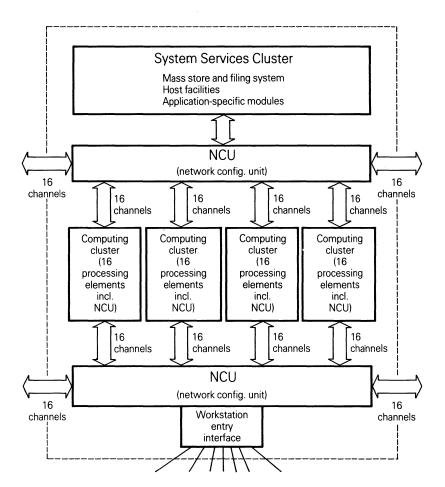

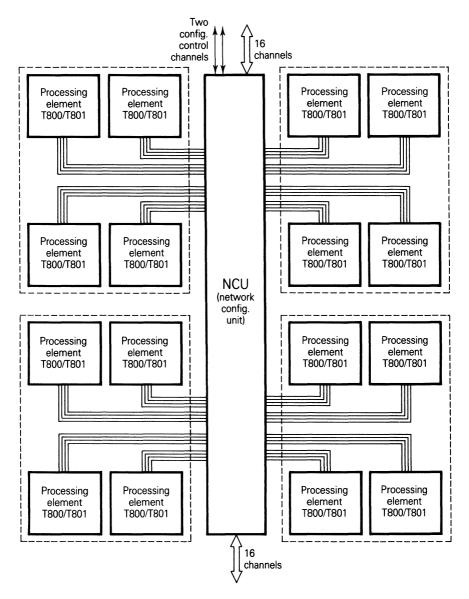

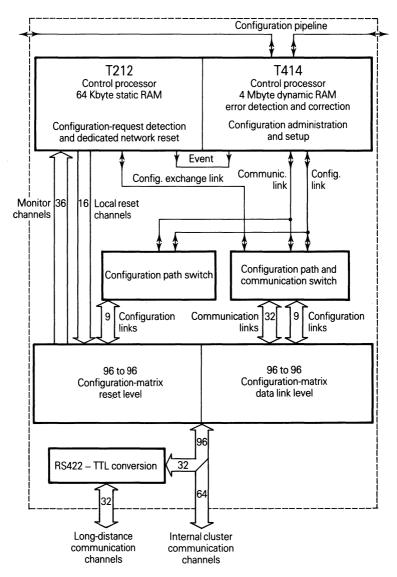

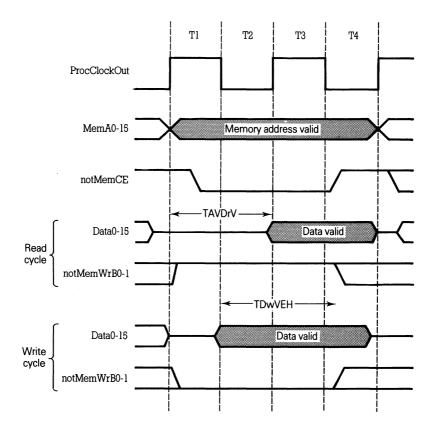

Figure 2.1 The generic transputer

reduce the memory bandwidth of the system. This has led the designers of some of the most recent high-performance microprocessors, such as the 80486 and i860, to include on-chip floating-point units.

Another common addition on chip is a cache of some kind, which allows frequently accessed data and code to be held on chip. Sometimes this cache is implemented for instructions only, as on the 68020; or with separate instruction and data caches as on the i860. The transputer family uses a rather different approach at present, having on-chip RAM that can be used in exactly the same manner as external memory, except that accesses to the internal memory are at least two to three times faster. Unlike a cache, this requires the programmer to make explicit use of the fast RAM, and to decide if it should contain code, or data, or a mixture of both.

The major extra function built in to every member of the transputer family is that of on-chip communications. It is this single item that makes the transputer unique, as every transputer comes equipped with the ability to communicate with other transputers. It is thus very easy to construct arrays of processors working together as a MIMD computer.

In summary, a transputer (Figure 2.1) is a single-chip VLSI device with processor, memory and communications links, which represents a slight deviation from current microprocessor technology. Along with various support devices it is manufactured by INMOS Ltd, part of the SGS-Thompson Microelectronics Group. The first transputer product, the IMS T414, was introduced in 1986, and by December 1989 there were ten processors in the family. The common features of all present transputers are as follows:

- High-speed integer processor with microcoded process scheduler.

- On-chip fast static memory.

- Up to four links for communication with other transputers.

- Internal timers.

- External memory interface.

However, the transputer lacks one feature that we have begun to expect in more conventional microprocessors: there is no support for memory management, or for virtual memory. This lack is a result of the design goals of the transputer. It is a device intended for the implementation of multiprocessor systems, where each processor has its own local memory and processors communicate by messagepassing along fast links. Thus protection of the address space of one process from the actions of another can be provided by putting the two processes on separate transputers, rather than by a memory management scheme.

The transputer family consists of a number of different processors that have been optimized for different tasks. However, the overall architecture of the transputer makes it easy to construct and to program systems containing a mix of these transputer types. The transputer links make hardware interconnection fairly easy, and the transputer instruction set is designed so that programs can be written that are independent of the word length of the processor, even at the binary level. Transputers will normally be used in multiprocessor systems and thus the performance of the individual processor is not so critical. If more processor power is required, more processors can be added with very little modification of the software.

## 2.1 Microprocessor architectures

Current microprocessors fall into two main groups. On the one hand lie the complex instruction set computers (CISC) where a rich instruction set is available to manipulate data both in memory and in registers. The alternative approach is based on the reduced instruction set (RISC) philosophy. Here a small number of instructions are available, most acting only on data in registers. The logic behind the RISC approach is that it is possible to construct a faster computer by keeping it simple.

The transputer CPU does not fall readily into either category. It has a simple instruction set which means that it tends to be viewed as a RISC processor. It is, however, much more than a RISC processor because of the extra functionality built into the chip to support high-level concepts such as processes, timers and inter-process communication.

It is useful to review some of the more familiar microprocessor families at this

stage in order to compare them with the transputer. The two major families of CISC processors started with the 8086 from Intel and the 68000 from Motorola. The Intel range has expanded to include the 80486, whereas Motorola have the 68040 at the top end of their range.

The Intel 80386 is a popular 32-bit chip providing integer-only operations. A floating-point coprocessor may be added externally. There is a set of registers of which many have special purposes in certain instructions. The chip provides a way of emulating the older 8086 processor with its segmented architecture, but in native mode a full 32-bit linear address space is available. There is a range of specific opcodes intended to speed up certain operations such as copying strings as well as the standard arithmetic and logical operations. Many operations may be performed directly to memory without loading the value into a register. The chip contains an integral memory management module.

The Motorola 68030 at first sight seems slightly more symmetric. There are sixteen general-purpose registers but these are divided into two types, called data and address registers, and many operations can only be performed in one type. Special addressing modes use the registers in different ways and can decrement or increment them as a side-effect of other instructions. The chip is integer only but an external floating-point coprocessor adds a separate set of floating-point registers. There are no special string instructions, instead an instruction cache is provided which ensures that any short loop becomes resident on chip. A data cache is also used to speed performance. The linear memory address space is handled by an integral memory management unit. Many standard operations, such as addition, can load one argument from memory but always leave the result in a register. The instruction set includes a number of special case operations to manipulate such things as program modules.

Both Intel and Motorola have recently announced their entry into the RISC camp in the shape of the Intel i860 and the Motorola 88000 microprocessors. The 88000 has thirty-two general-purpose 32-bit registers and two completely separate address buses for instructions and data. As with many RISC designs, all operations are handled in registers; two specific load and store operations are the only way of accessing memory. A floating-point unit is provided on the chip, whereas cache and memory management are handled externally by other members of the 88000 family.

Another RISC chip is the SPARC design from Sun Microsystems. This is a classic RISC design which has been used to extend a range of computers previously based on 68020 processors. The logic behind a RISC processor is that most programs are written in a high-level language and compilers are not very good at using special-purpose instructions. Most processors spend 90 percent of their time executing 10 percent of their instructions; the next step is to speed up those instructions and leave out the complicated ones, such as multiplication, which can be provided by software. The SPARC design provides a simple but fast processor based on three-address instructions so that each opcode is of the form 'add R1 to R2 and place the result in R3'. The result is that each instruction is 32 bits wide; the problem with

the RISC approach is the processor can spend a large amount of its time reading these simple instructions in order to execute them.

The SPARC design has one interesting design feature not generally found on other commercial RISC chips: the concept of a 'register window'. A compiler can make good use of a small number of registers and ensure that few redundant stores and loads from memory are made. However, as soon as a procedure is called the current register set is dumped because the compiler does not know what registers are used in the procedure; when the procedure returns the registers are restored from memory. The SPARC architecture provides a different set of registers for the new procedure which are allocated from a circular buffer. Only when the entire register set has been used up does the compiler need to save the previous contents.

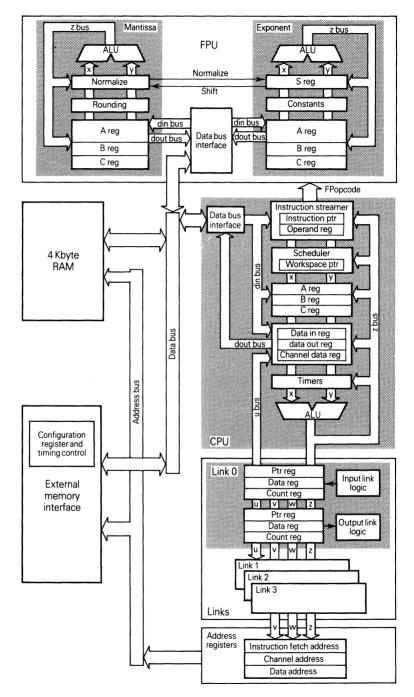

## 2.2 Transputer architecture

The internal design of the transputer is unlike that of any of the preceding processors. A central concept of the transputer is that of the process and this can be seen throughout the instruction set. A process represents an individual thread of control and the transputer switches between running processes to provide the illusion that they are all running simultaneously. This process switching is sometimes called multi-tasking and is normally handled by an operating system, but in the transputer it is implemented totally by the hardware and microcode of the processor.

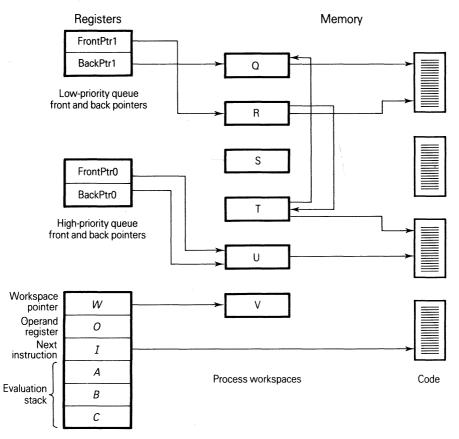

The register model of the transputer is shown in Figure 2.2. All registers are either 16 or 32 bits long, depending on the word length of the transputer. Registers A, B and C form an evaluation stack and transputer instructions are designed around the use of this stack rather than using general-purpose registers. A stack depth of three provides a good compromise between the ability to evaluate most expressions on the stack and having as little as possible to save when a context switch occurs.

Register W is the workspace pointer, a pointer into the local variables associated with the currently executing process. Many instructions refer to data by their offset from the workspace pointer. The instruction pointer register I points to the next instruction to be executed, and this corresponds to the program counter PC in more conventional processors. The operand register O is used in the construction of instruction operands.

#### 2.2.1 The process scheduler

A unique feature of transputer architecture is that it contains a microcoded scheduler which maintains two process queues, one at high and one at low priority. Processes in the high-priority queue are allowed to execute until they terminate, or

Figure 2.2 Transputer registers

require input or output. However, low-priority processes are automatically timesliced at about 1 msec intervals, and can also be interrupted by a high-priority process. These queues are implemented as linked lists through the workspaces of the active processes, the front and back of the queues are pointed to by two pairs of registers, one for each priority. The mechanics of process switching are discussed in detail in Section 3.7.

Associated with each priority level is a timer and a timer process queue. The high-priority timer ticks once every microsecond, the low-priority timer every  $64 \mu$ sec, or exactly 15,625 ticks per second. The number of bits in the timer registers depends on the processor model: for 16-bit processors the high-priority timer will cycle in about 65.5 msec, the low-priority timer in 4.2 sec; for 32-bit processors the high-priority timer cycles about every 4,295 sec (1.2 hours), the low-priority timer about every 76 hours. The timer registers can be read directly, or the scheduler can be instructed to queue a process for execution after the timer has reached a

certain value. The timer queues are again implemented as linked lists within the workspace of the waiting processes, but the entries are sorted into time order. The front pointers to the timer queues are stored in reserved locations.

Another important feature of the scheduler is its ability to select one of a group of processes for execution, depending on the occurrence of some event. These events may be the completion of a data input, the expiration of a timer period or an external interrupt.

#### 2.2.2 Communications

As the transputer has been designed for use in message-passing parallel computers it has strong support for inter-process communication. This has been designed so that there is almost no difference to the programmer whether the communication is between two processes executing on the same or on different transputers.

Data is transferred between two processes on the same transputer by copying data between their memory spaces. This transfer is synchronized by means of a channel control word, which is a single word anywhere in memory. Communication only takes place when both the inputting and outputting process are ready, and processes waiting for communication take up no processor time. Thus two transputer processes may synchronize by passing a message between them. Communication between two processes on different transputers uses just the same mechanism, synchronized by special channel control words that lie in reserved locations in low memory. The same instructions are used to set up the transfer, and the link engines in each transputer take care of the direct memory access (DMA) transfer between link and memory, with no processor intervention.

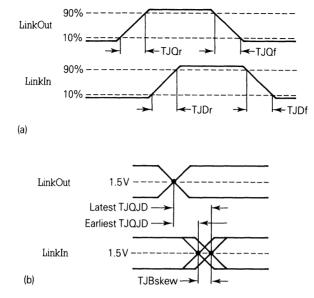

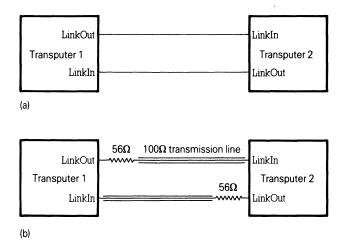

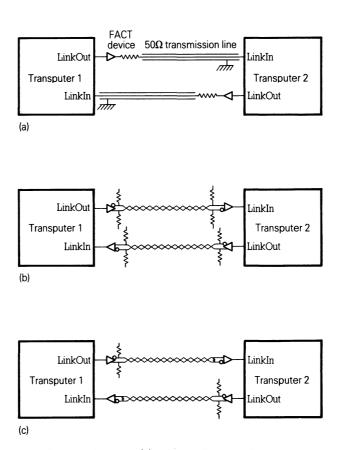

Each of the presently available transputers has either two or four external links. These are full duplex communications links that can exchange data with other transputers at 5, 10 or 20 million bits per second (Mbps), the speed being selected by voltages applied to three pins on the transputer package. The bidirectional data rate that can be achieved over the links depends on the types of processors exchanging data, and the link speed, but can be up to about 2.4 Mbytes per second for T800 transputers with 20 Mbps links.

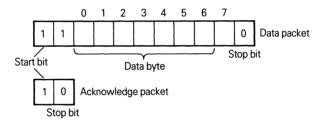

The link data are transferred as a serial byte stream, each byte being acknowledged by the receiving transputer. No attempt is made to detect errors on the link; it is assumed that the communications medium is error-free, or that higher levels of communications will detect and correct errors.

#### 2.2.3 Interrupts

The transputer has a single source of external interrupts, the EventReq input. The programming interface of this input is implemented so that it appears as another channel control word, located in low memory. A process instructed to wait on the

event channel will be descheduled until the EventReq input is taken high, when it will be rescheduled. When this occurs the event handshake output EventAck is driven high by the processor. In order to provide a rapid response to interrupts the process waiting for event input must have high priority, and be the only high-priority process running. If these conditions are met the worst case interrupt response time is about fifty processor cycles. This fast interrupt response is obtained by making long instructions interruptable.

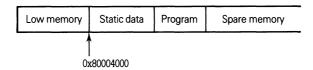

#### 2.2.4 Memory

The present members of the transputer family have 2 or 4 Kbytes of on-chip fast static RAM, which occupies the very bottom of the memory space. Some of this is reserved for processor microcode functions. This is an inadequate amount of memory for the majority of applications, and thus each transputer has an external memory interface. Reads or writes to internal memory are fast, requiring only a single cycle of the processor clock. External memory access is much slower, requiring at least two processor cycles and usually four or five in dynamic memory systems.

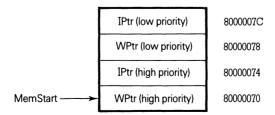

Memory addresses are signed, thus the memory of a transputer starts at the lowest possible negative number, MinInt, which is 0x8000 on a 16-bit and 0x80000000 on a 32-bit transputer. It runs through zero to the largest possible positive number, MaxInt, 0x7FFF or 0x7FFFFFFF. Several locations at the bottom of memory are reserved for processor functions, as shown in Table 2.1. In this table the addresses are shown as word offsets from MinInt, the actual byte address depending on the word length of the transputer. The lowest eight words contain the channel control words for the four external links, with the event control word in the ninth location. The next two locations contain the front pointers for the high-priority and low-priority timer process queues. Above these are the seven words that store the processor state when a low-priority process is interrupted by a high-priority process, the only occasion when the processor state has to be saved.

#### 2.2.5 System services

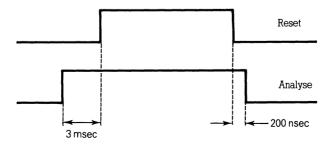

The system services interface includes signals necessary to reset and boot the transputer, to set the speed of its processor and its links, to signal errors and to respond to external events. The transputer can be reset into either of two modes, determined by the value of the Analyse signal when Reset is asserted. If reset with Analyse inactive the transputer will boot from memory if the signal BootFromRom is connected high. If BootFromRom is low the transputer will listen on its links, and can accept a bootstrap program or commands to write (poke) or read (peek) memory locations via the links. The Analyse input is used as a debugging aid. If Analyse is taken high while the transputer is running it will halt very shortly after, and the links will become inactive. Reset may then be asserted. When Reset

| Word address | Name             | Use                          |

|--------------|------------------|------------------------------|

| MinInt+28    | MemStart         | T805, T801, T800, T425, T225 |

|              |                  |                              |

|              |                  | reserved for extended        |

|              |                  | instructions                 |

|              |                  | (not T212, M212, T414)       |

|              |                  |                              |

| MinInt+18    | MemStart         | T414, T212, M212             |

| MinInt+17    | EregIntSaveLoc   |                              |

| MinInt+16    | STATUSIntSaveLoc |                              |

| MinInt+15    | CregIntSaveLoc   |                              |

| MinInt+14    | BregIntSaveLoc   | register save                |

| MinInt+13    | AregIntSaveLoc   | area                         |

| MinInt+12    | IptrIntSaveLoc   |                              |

| MinInt+11    | WdescIntSaveLoc  |                              |

| MinInt+10    | TptrLoc1         | low-priority timer           |

| MinInt+9     | TPtrLoc0         | high-priority timer          |

| MinInt+8     | Event            | event channel                |

| MinInt+7     | Link3Input       |                              |

| MinInt+6     | Link2Input       |                              |

| MinInt+5     | Link1Input       |                              |

| MinInt+4     | LinkOInput       | link control                 |

| MinInt+3     | Link3Output      | words                        |

| MinInt+2     | Link2Output      |                              |

| MinInt+1     | Link1Output      |                              |

| MinInt       | Link0Output      |                              |

Table 2.1 Reserved memory locations

comes low again the transputer will be in its reset state, but the registers will contain information on the state of the machine when it was halted by the assertion of Analyse.

### 2.3 The transputer family

The transputer family consists of three main groups: the 16-bit T2 series; the 32-bit integer-only T4 series; and the 32-bit T8 series, which have an on-chip 32/64-bit floating-point processor. Within these groups processors are distinguished by the amount of on-chip RAM, the number of links, details of the instruction set and the type of memory interface. However, all transputers conform to the general architecture model shown in Figure 2.1. Here we will introduce the present members of the transputer family, as summarized in Table 2.2; a more detailed description is given in Chapter 7.

|                        |      | 16-bit tr | ansputer  | s             |      |      |

|------------------------|------|-----------|-----------|---------------|------|------|

|                        | T212 | T222      | T225      | M212          |      |      |

| Word length            | 16   | 16        | 16        | 16            |      |      |

| Internal RAM           | 2K   | 4K        | 4K        | $2\mathrm{K}$ |      |      |

| Number of links        | 4    | 4         | 4         | 2             |      |      |

| Extended instructions  | n    | у         | у         | n             |      |      |

| Debugging instructions | n    | n         | У         | n             |      |      |

|                        |      |           |           |               |      |      |

|                        |      | 32-bit tr | an sputer | s             | -    |      |

|                        | T400 | T414      | T425      | T800          | T801 | T805 |

| Word length            | 32   | 32        | 32        | 32            | 32   | 32   |

| Internal RAM           | 2K   | 2K        | 4K        | 4K            | 4K   | 4K   |

| Number of links        | 2    | 4         | 4         | 4             | 4    | 4    |

| Hardware FPU           | n    | n         | n         | у             | у    | y    |

|  | Table 2.2 | The transputer | family | (December 1989) |

|--|-----------|----------------|--------|-----------------|

|--|-----------|----------------|--------|-----------------|

#### 2.3.1 Sixteen-bit transputers

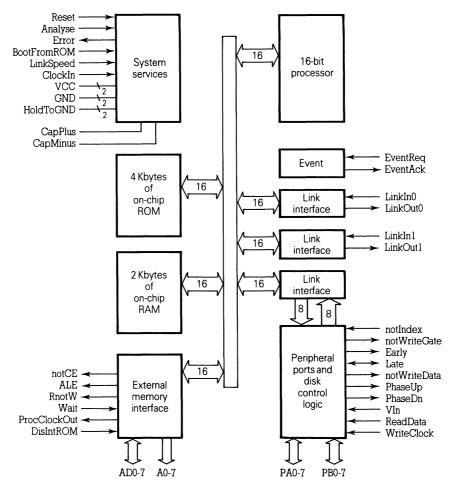

The T212 was the original 16-bit transputer, with 2 Kbytes of internal static memory; the T222 is a more recent device with 4 Kbytes of internal memory and an extended instruction set. The T225 is almost identical to the T222, but contains extra instructions to support debugging. The M212 is a derivative of the T212 with a built-in disk interface, 1 Kbyte of RAM and 4 Kbytes of internal ROM containing disk controller firmware. The M212 has only two external links, the other two are used as part of the disk interface.

#### 2.3.2 Thirty-two-bit transputers

The T414 is the original member of the transputer family. It has a 32-bit integer processor with 2 Kbytes of internal RAM. The T425 is an updated version of the T414, with block move instructions. This processor introduced instruction set extensions to support debugging, and is intended eventually to replace the T414. The recently announced T400 is a simplified and low-cost version of the T425, with only two links and 2 Kbytes of on-chip memory.

The first transputer specifically designed for numerical applications was the T800. This has 4 Kbytes of internal memory, and a floating-point unit (FPU) capable of operating to the IEEE-754 specification on 32- and 64-bit numbers. As the FPU is on chip the floating-point performance is excellent. The T805 is a development of the T800 with the same debugging support in its instruction set as the T225 and T425. The T801 is similar, but has a high-speed static RAM external memory interface, rather than the programmable interface of the other members of the T8 and T4 series. This makes it able to run faster, but requires more expensive and less compact memory devices. The 32-bit transputers are available in a range of clock speeds from 20 to 30 MHz.

#### 2.3.3 Future transputers

INMOS have recently announced their plans for the development of a much higher speed transputer, code-named the H1. This device is intended to have a processor roughly ten times the speed of present transputers, and links capable of an aggregate data rate of 80 Mbytes per second. The processor will have support for standard operating systems, presumably some form of memory management, and a simplified interface to dynamic RAM. It should be available in early 1991.

## Chapter 3

## The Instruction Set

This chapter describes the instruction set of the transputer. As previously noted, the transputer cannot be seen to lie in either the classic RISC or CISC camps. For programmers used to other microprocessors it can seem strange. It has a small number of registers, organized as a stack, and all instructions are stack, rather than register, oriented. It has little concept of condition codes, there are limited instructions for accessing memory and no sophisticated memory-addressing modes.

On the other hand, the concepts of processes, inter-process communication and process scheduling are handled directly by the device. Fundamentally, multiple processor architectures and inter-processor communications are designed into the transputer and its instruction set.

This chapter provides an overview of the instruction set and does not intend to be exhaustive. A full list of the transputer instruction set is provided in Appendix A.

#### 3.1 The evaluation stack

The instruction set of the transputer is designed around the idea of a stack as opposed to the idea of registers. Most other processors use these registers to manipulate values. Consider adding two numbers on a processor such as a 68000. The numbers would normally reside in memory and the result would eventually have to be stored back in memory. The 68000 is not capable of performing this directly even though it is a CISC processor. The sequence of operations would be as follows:

| MOVE.L | memX,DO |

|--------|---------|

| ADD.L  | memY,DO |

| MOVE.L | DO,memZ |

which loads value X into the register DO, adds the 'value Y to it, then stores it back. In a RISC processor the ADD instruction would only work on registers, so the

sequence could be described as follows (we continue to use 68000 style mnemonics for clarity):

| MOVE.L | memX,DO |

|--------|---------|

| MOVE.L | memY,D1 |

| ADD.L  | D1,D0   |

| MOVE.L | DO,memZ |

Inside the transputer the approach is similar, except that a stack is used. The actual operations to add the two numbers would be as follows:

| 1d1 | memX |

|-----|------|

| ldl | memY |

| add |      |

| stl | memZ |

Here the ldl instruction is used to transfer data from memory to a stack. The add instruction takes the top two values off the stack, adds them together and places the result on the top of the stack. The stl instruction is then used to store the top of the stack back into memory.

In a more conventional processor an assembly language programmer or compiler writer attempts to optimize performance by keeping suitable values in registers so that redundant access to memory is avoided. In the transputer the same approach is used to keep values within the evaluation stack as they are required. The stack is only three items deep and consists of the three registers A, B and C. The action of 1d1 can be described more formally as follows:

Copy the value of B into CCopy the value of A into BLoad from memory into A

Thus two consecutive ldl instructions place two values from memory into A and B. The add instruction can again be described more formally as:

Add B to ACopy the value of C into BLeave C undefined

or informally as popping two values off the stack, adding them together and pushing the result onto the stack. In the same way the stl instruction pops a value off the stack and stores it into memory, or:

Store A in memory Copy the value of B into ACopy the value of C into BLeave C undefined

In order to make effective use of this evaluation stack care must be taken in the order of evaluation of expressions, to ensure that wherever possible an intermediate expression is stored within the stack. The stack may seem limited in that it only holds three items but this is sufficient for most expressions.

Figure 3.1 Local variable access in Motorola 68000 processor

### 3.2 Simple instructions

The previous chapter gave an introduction to the transputer registers. Explicit reference to a transputer register is never made, as access to registers is always implicit in each instruction. The instruction pointer I is manipulated by instructions which specify transfer of control while the workspace pointer W may be thought of as a stack pointer for a falling stack.

In a high-level language we need a way to store local variables and this is traditionally done with respect to a stack pointer. Consider the following fragment of C code:

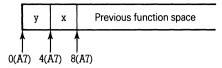

Here two variables local to the function f are declared and used later in a calculation. Again it is worth considering how this is done in other processors. On a CISC machine such as a 68000 the address register A7 is used as a falling stack. Space for local variables is allocated on this stack and can be addressed by positive offsets relative to A7. If we wish to store 32-bit values then these byte offsets must be multiples of 4, as shown in Figure 3.1.

Thus the code generated for the addition of x and y might look as follows:

| MOVE.L | 4(A7),D1 |

|--------|----------|

| ADD.L  | 0(A7),D1 |

| MOVE.L | D1,4(A7) |

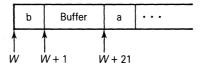

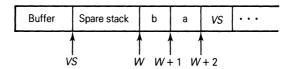

In the transputer, memory is allocated as offsets from the workspace pointer W (see Figure 3.2) in a very similar way, except that the offsets used are word offsets. The size of a word depends on the type of the transputer, being 16 bits for the T2 series and 32 bits for the others.

The instructions to load local data are always relative to W so it need not be specified. The only argument needs to be the offset from W, and so the same code fragment to add two local variables together would be generated as follows:

Figure 3.2 Local variable access in transputer

| ldl | 1 |

|-----|---|

| 1d1 | 0 |

| add |   |

| stl | 1 |

This scheme has the advantage that the same code will work on a T212, a T414 or a T800 with 16-bit values used on the T212 and 32-bit values on the other processors. It also shows why 16-bit integers should not be used on 32-bit transputers as the only size of local variable supported is the word. There are ways of accessing a byte from memory, which are described below, but the only way to use 16-bit integers is to shift and mask 32-bit numbers. For this reason many compilers give a warning message if a high-level language program declares values as 16-bit objects.

Besides local variables in the workspace, access is also required to other areas in memory, commonly into structures in languages such as C. This is where indirection is required, using the value of one memory location to refer to another. Consider the following C code fragment:

```

main(argc, argv)

int argc;

char *argv[];

{

char *arg;

...

arg = argv[3];

...

}

```

Here the value of **argv** is a pointer to an array of argument slots, each of which contains a further pointer to a string. The assignment to **arg** causes an indirection via **argv** and the value of the index. The code to generate this on a 68000 might look as follows:

MOVEA.L 8(A7),A0 MOVE.L 12(A0),4(A7)

In the first line we access the array pointer stored on the stack and save it in A0. In the second line we indirect through an offset of 12 on A0 to get the third array item, which is then stored as a local. Note that an offset of 8 is required because that is the byte offset of the third word in the array argy. On the transputer we perform indirection using the ldnl instruction. The same code fragment would translate to transputer code as follows:

| 1d1  | 2 |

|------|---|

| ldnl | 3 |

| stl  | 0 |

In the first line we access the pointer **argv** from the stack. The second line uses this plus the word given as argument as a pointer from which a memory location is loaded. The last line stores this back into memory again. Note that the transputer again uses a word rather than a byte offset for the argument to ldnl.

### 3.3 Encoding

The previous sections have given a very simple introduction to the transputer instruction set. We have seen how code fragments can be compiled on the transputer and have been able to compare this with a more familiar processor such as the 68000. This section describes the way in which the transputer encodes both instructions and data for greater code density.

Any computer architecture must choose a way in which numbers are stored. There are two differing requirements here. First, there is the maximum size of an integer which can be supported. On any 32-bit processor this is normally a 32-bit value. Secondly, there is the need to make the instruction set as compact as possible. For example, the 68000 series processors have an instruction to load an immediate value into a register. In the standard form this instruction is 6 bytes long: 2 bytes for the instruction code 'move immediate' plus 4 bytes for the value to be loaded. This is clearly wasteful when the number to be loaded is only small, and analysis of programs shows that loading small numbers such as 0, 1 or 4 is much more common than loading large numbers. The 68000 therefore has a special 'move quick' operation, which is only 2 bytes long and which can be used to load a number in the range -128 to +127.

There are several problems in having different instructions for the special case of small numbers. On the 68000 there are specific instructions for loading immediate values and adding or subtracting small numbers but the range is different for addition and subtraction, limiting these numbers to between 0 and 7. There are no special instructions for multiplication by small numbers or for any other immediate operations.

The transputer has a more elegant and flexible mechanism than this. A number within the transputer is represented by the number of bytes required and no more. The number is always represented in this way no matter where it is used within an instruction and no matter what the instruction. The approach is totally flexible giving no logical maximum integer size. A similar scheme is also used for encoding instructions, leading to a very dense and compact instruction set.

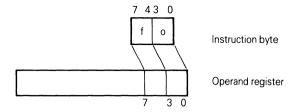

**Figure 3.3** Instruction byte and operand register (f=instruction byte function (4 bits); o=instruction byte operand (4 bits))

Transputer instructions are encoded in a stream of bytes. Each byte consists of two nibbles, the upper four bits containing a function code, the lower four bits an argument (Figure 3.3). Thus there are sixteen different function codes, consisting of thirteen 'direct functions' and three special functions. For the thirteen direct functions the function code is the opcode of the instruction to be performed. Before executing the instruction the argument part of the byte is loaded into the bottom four bits of the operand register O, where it acts as the operand of the instruction.

Consider the encoding for loading a constant value onto the top of the stack. This instruction is called ldc for 'load constant'. This is a direct function and is represented by 0x4. A number in the range 0-15 is represented by the argument nibble. Thus the complete instruction to load constant 8 onto the stack is represented by a single byte 0x48. After the instruction has been executed, the operand register is cleared.

But often we will want to load a constant that is greater than 15. Larger operands are generated by using special functions pfix (0x2) and nfix (0x6), which act as prefixes to the other functions. The pfix function loads its four argument bits into the operand register, and then shifts the register up four bits. The nfix instruction acts in exactly the same way, but complements the operand register before shifting it up. These functions are the only operations that do not clear the operand register after execution. For example, we can represent ldc 0x15 by two bytes 0x21 0x45, or pfix 1; ldc 5. The pfix instruction loads register O with the value 0x01 and then shifts it up four places, so that O contains 0x10. The ldc instruction then inserts the argument from its own instruction word into the lowest four bits of Oand uses the result 0x15 as the operand for the instruction. The register O is then zeroed ready for the next operation.

This mechanism is highly extensible and is limited only by the size of the internal registers. Table 3.1 shows the contents of the O register during the evaluation of the sequence of bytes required to represent the instruction ldc 0x892, which is 0x28 0x29 0x42. In the same way nfix (0x6) may be used to construct a negative number. For example, the instruction ldc -3 is represented by the byte sequence nfix 0; ldc -3 or 0x60 0x43.

Notice that it is also possible to encode numbers in a way that uses a fixed

Table 3.1 Execution of 1dc 0x892

| O before | Opcode | O during | O after |

|----------|--------|----------|---------|

| 0        | 28     | 8        | 80      |

| 80       | 29     | 89       | 890     |

| 890      | 42     | 892      | 0       |

amount of memory simply by using pfix instructions with a zero argument. Hence 0x20 can sometimes be used as a no-op within the transputer, and it is useful to pad short numbers to a standard length with this code. This technique is sometimes employed when a linker is to be used to pad values after a compilation has taken place. A later section of this chapter discusses this problem in more detail.

The 'operate' function opr is used to extend the instruction set. The operand of opr is taken as the opcode to be performed. Thus:

opr

5

instructs the transputer to perform the opcode 0x5, which is in fact add. The encoding for opr is 0xF so the complete add instruction is encoded as 0xF5. This scheme allows a further sixteen instructions to be encoded as a byte along with the thirteen encoded as a nibble. Again, these sixteen 1-byte instructions have been chosen to be the most commonly used after the direct functions. As the opcode of the instruction executed by the opr function is contained in the operand register, this register clearly cannot be used as the operand of the instruction. Thus instructions executed by opr take their operands from the evaluation stack or from memory.

Further instructions are available using larger operands to the opr instruction. For example:

opr 0x41

executes opcode 0x41, which is a shift left instruction. This is encoded as pfix 4; opr 1 or 0x24 0xF1, using the pfix instruction to extend the number range of the opcode.

This may sound rather complicated but the entire mechanism can be encapsulated in a few lines of code. The following C routine is used to encode a number in the most efficient manner:

```

#define f_pfix 0x20

#define f_nfix 0x60

#define TRUE 1

#define FALSE 0

void encodestep();

void encode( op, arg)

int op, arg;

```

```

£

if (arg < 0)

encodestep((~arg) >> 4, TRUE);

else

if (arg > 15) encodestep(arg>>4, FALSE);

printf("%2x\n", op | (arg & 0xf));

}

void encodestep(arg, negative)

int arg, negative;

ſ

if (arg > 15)

ſ

encodestep((arg>>4), negative);

printf("%2x", f_pfix |

((negative ? ~arg : arg) & 0xf));

}

else

printf("%2x", (negative ? f_nfix : f_pfix)

| (arg & 0xf));

}

```

Here are some encodings of various numbers:

| ldc | 12   | 0x4c     |

|-----|------|----------|

| ldc | 40   | 0x2248   |

| ldc | 257  | 0x212041 |

| ldc | -12  | 0x6044   |

| ldc | -40  | 0x6248   |

| ldc | -257 | 0x612F4F |

Clearly the encoding scheme can result in a very compact instruction stream. Reverting back to the sample segment of C code to add together two local variables, we can compare the size of the instruction set on the CISC processor and the transputer. The 68000 version is as follows:

| MOVE.L | 4(A7),DO | 0x202F0004 |

|--------|----------|------------|

| ADD.L  | 0(A7),D1 | 0xD2AF0000 |

| MOVE.L | D1,4(A7) | 0x2F410004 |

Compare the size of the code with the transputer version, which is as follows:

| 1d1 | 1 | 0x71 |

|-----|---|------|

| 1d1 | 0 | 0x70 |

| add |   | 0xF5 |

| stl | 1 | 0xD1 |

#### 26 The Instruction Set

The thirteen instructions allocated to single nibbles have been carefully chosen to be those used most commonly and are shown in Table 3.2. These include loading a constant, a local variable, a non-local variable, a local pointer and a non-local pointer. It is also possible to store local and non-local variables, adjust the Wpointer register, add and compare constants, make conditional and non-conditional jumps and call procedures using a single nibble. Sixteen more of the commonly used instructions are encoded as single bytes (Table 3.3). The 'Cycles' column shows the number of processor clock cycles taken to execute each instruction when its non-register operands are in internal RAM. Many of these simple instructions execute in a single clock cycle.

| Function code | Mnemonic | Cycles   | Instruction                        |

|---------------|----------|----------|------------------------------------|

| 0x0           | j        | 3        | jump                               |

| 0x1           | ldlp     | 1        | load local pointer                 |

| 0x2           | pfix     | 1        | prefix                             |

| 0x3           | ldnl     | 2        | load non-local                     |

| 0x4           | ldc      | 1        | load constant                      |

| 0x5           | ldnlp    | 1        | load non-local pointer             |

| 0x6           | nfix     | 1        | negative prefix                    |

| 0x7           | ldl      | <b>2</b> | load local                         |

| 0x8           | adc      | 1        | add constant                       |

| 0x9           | call     | 7        | call                               |

| OxA           | cj       | 2/4      | conditional jump (taken/not taken) |

| 0xB           | ajw      | 1        | adjust workspace                   |

| 0xC           | eqc      | <b>2</b> | equals constant                    |

| 0xD           | stl      | 1        | store local                        |

| 0xE           | stnl     | <b>2</b> | store non-local                    |

| 0xF           | opr      | -        | operate                            |

Table 3.2 Direct functions

| Table 3.3 | Single-l | byte operations |

|-----------|----------|-----------------|

|-----------|----------|-----------------|

| Byte | Mnemonic | Cycles | Instruction    |

|------|----------|--------|----------------|

| 0xF0 | rev      | 1      | reverse        |

| 0xF1 | 1b       | 5      | load byte      |

| 0xF2 | bsub     | 1      | byte subscript |

| 0xF3 | endp     | 13     | end process    |

| 0xF4 | diff     | 1      | difference     |

| 0xF5 | add      | 1      | add            |

| 0xF6 | gcall    | 4      | general call   |

| 0xF7 | in       | 2w+19  | input message  |

| 0xF8 | prod     | x      | product        |

| 0xF9 | gt       | 2      | greater than   |

| 0xFA | wsub     | 2      | word subscript |

| 0xFB | out      | 2w+19  | output message |

| 0xFC | sub      | 1      | subtract       |

| 0xFD | startp   | 12     | start process  |

| 0xFE | outbyte  | 23     | output byte    |

| 0xFF | outword  | 23     | output word    |

|      |          |        |                |

w= number of words transferred.

### **3.4 Further instructions**

Many of the instructions in the transputer are easily recognizable in other processors and are not worth an explicit mention here. A full list of the transputer instruction set is given in Appendix A.

These instructions include standard operations, such as signed and unsigned arithmetic operations; logic operations such as AND, OR, EXCLUSIVE-OR; and shifts. Unlike many other microprocessors, the transputer does not contain a special piece of hardware called a barrel shifter which is used to implement shifting of data. This means that shifting data is slow compared to some other processors; in particular, the unchecked multiply instruction called **prod** should be used in preference to shifts when multiplying by a constant power of two.

The transputer also contains explicit support for operations on values longer than a word; these are especially useful on the 16-bit series. Versions of the signed and unsigned arithmetic operations are provided, as well as extended shift instructions to shift double-sized objects. The normalize instruction norm may be used to shift left a double-sized object until its most significant bit is one, keeping track of the number of shifts needed.

As mentioned earlier, the transputer normally works entirely in words, which are either 16 or 32 bits depending on the type of transputer. It is possible to access individual bytes through instructions that allow loading and storing bytes. There is also provision for handling byte-sized structures, so that the same code could work on transputers with different word sizes. The bsub instruction is used to return the address of an offset within a byte structure. In the same way the wsub instruction returns the address of an offset within a word-sized structure, avoiding the need for explicit multiplication by two or four. The bcnt instruction can be used to multiply the A register by the number of bytes in a word, whatever that is. A complementary instruction wcnt decomposes an address into a word offset and a byte selector.

Structures can be copied efficiently using the move instruction, which takes its arguments from the evaluation stack. This instruction will copy A bytes of data from the address in C to the destination address in B. This is an efficient onedimensional copy and the more recent transputer variants, such as the T800 and T425, also have two-dimensional copy instructions. The move instruction does not allow overlapping source and destinations.

### 3.5 Position-independent code

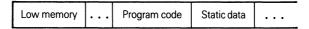

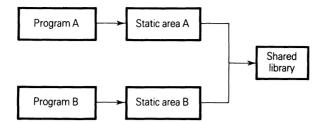

An important feature of many modern microprocessors is that code produced for them can be 'position independent' in that the code contains no absolute addresses. The instructions may be loaded anywhere in memory without the need for any changes to the code. This is normally good programming practice as it is also a prerequisite for producing 'pure code', which can be shared by many different processes. It also allows for code to be moved once it is loaded into memory.

On the transputer the use of pure code is highly important. As the transputer supports multiple processes in the instruction set it is important that standard libraries be shared by all the processes. Position-independent code may also be passed between interconnected processors, being loaded into different memory locations in different processors. The production of position-independent code is made possible by the 1dpi instruction, which loads a pointer to an instruction. Consider attempting to load the address of a string, ready to print it out with printf or some such similar routine. This string will normally be located somewhere within the program code. The following code would be used to perform the required action:

ldc (L1-L2) ldpi L1: ... L2: byte "Hello World"

Here the A register is loaded with the offset of the string from the instruction following the ldpi, which is used to add in the current value of the instruction pointer or I register. The sequence ldc 0; ldpi may be used to access the address of the next instruction.

## 3.6 Flow of control

The transputer supports the normal range of instructions to alter the flow of control and these are listed in Table 3.4. The call instruction is used to call a procedure; the instruction pointer I is pushed onto the stack, followed by the three registers A, B and C. The argument to call is then added to I to transfer control. The new

| Code            | Mnemonic | Cycles | Description                   |

|-----------------|----------|--------|-------------------------------|

| Jumps           |          |        |                               |

| 0x0             | j        | 3      | jump – direction function     |

| 0xA             | cj       | 4      | conditional jump (taken)      |

|                 |          | 2      | (not taken) - direct function |

| 0x21            | lend     | 10/5   | loop end (loop back/exit)     |

| Call and return |          |        |                               |

| 0x9             | call     | 7      | call – direct function        |

| 0x06            | gcall    | 4      | general call                  |

| 0x20            | ret      | 5      | return                        |

Table 3.4 Flow of control instructions

function will then commonly allocate some workspace by using the ajw instruction to decrement W. At the end of the routine the workspace used is deallocated with another ajw; the ret instruction is then used to deallocate the four slots of workspace used by call and to jump back to the place indicated by the saved I. This mechanism allows up to three arguments to be passed in the registers; extra arguments would normally be pushed onto the workspace stack before the call.

The call instruction is normally useful for calling routines where the offset is known in advance. This is not the case when calling a routine where the address is to be computed at run time. The instruction gcall is provided which simply swaps I and A, thus enabling the address to be computed into A and then jumped to. Another gcall could be used to return.

It is also often useful to be able to write a routine in such a way that it can be called from either call or gcall. The easiest way to do this is to assume that all routines are going to be accessed via call instructions. If a gcall must be used, a 'stub' procedure is generated and a call is made to this instead, passing the address of the procedure as an extra argument. The call to the stub will set up the workspace correctly and the stub needs only to pick up the extra argument at the end and jump to this using gcall.

Transfer of control can also be made using unconditional and conditional jumps j and cj while for-loop control is handled with lend. The transputer programmer should note that the instructions j and lend both have a curious side-effect – they may destroy the contents of all the evaluation stack registers A, B and C. This can be very confusing because at first it seems slightly odd that the registers are trashed at these points, and secondly because they are not always altered. So an assembler routine might work at some times and not at others.

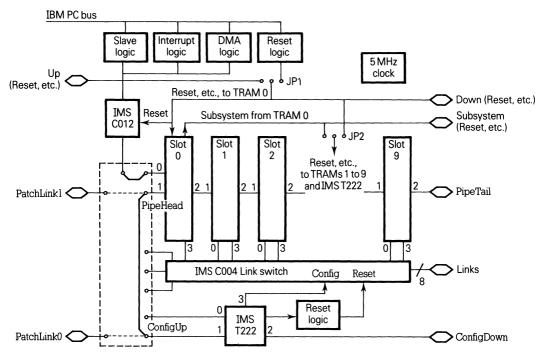

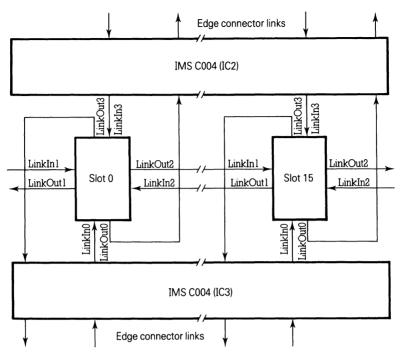

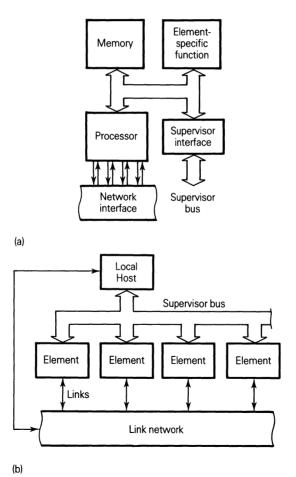

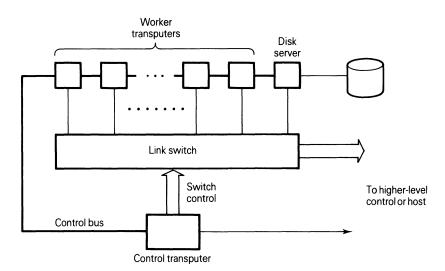

## 3.7 Process scheduling