# **IMS T9000**

# 32 BIT MICROPROCESSOR

#### **FEATURES**

- H Pipelined superscalar micro-architecture

- H Workspace cache

- H Programmable memory interface

- H 4 Gbyte physical address space

- H 16 Kbyte instruction and data cache

- H 120 MIPS peak

- H >80 MIPS sustained

- H >7 MFLOPs sustained

- H Sub-microsecond interrupt response

- H Per process error handling

- H Enhanced support for pre-emptive schedulers

- H Memory protection and address translation

- H 64 K virtual communication links

- H Support for message routing

- H Unidirectional peak bandwidth of 10 Mbytes/s per link

- H Separate control system

- H Single 5 MHz clock input

- H 20 MHz clock speed

- H 208 pin CLCC package

- H Single 5 V 5% power supply

The information in this datasheet is subject to change

# Contents

| 1  | MS T9000 introduction                                                                                                                                                                                                                                                                                  | . 7                                          |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2  | Pin designations                                                                                                                                                                                                                                                                                       | 10                                           |

| 3  | Programmable memory interface         3.1       External bus cycles         3.2       External DMA         3.3       Memory refresh         3.4       Memory wait         3.5       Booting from ROM                                                                                                   | <b>12</b><br>. 12<br>. 19<br>. 22<br>. 23    |

| 4  | Events                                                                                                                                                                                                                                                                                                 | . 27                                         |

| 5  | Data/Strobe links         5.1       Link format and protocol         5.2       Link functional description         5.3       Link speed select         5.4       Link configuration registers         5.5       Initialization         5.6       Link connections         5.7       DS-Link parameters | . 29<br>. 31<br>. 31<br>. 32<br>. 34<br>. 36 |

| 6  | Clocking phase locked loops         6.1       PLL decoupling         6.2       Clock input         6.3       ClockIn timings         6.4       Processor speed selection         6.5       Processor clock output         6.6       ProcClockOut timings         6.7       ProcClockOut stability      | . 39<br>. 39<br>. 40<br>. 40<br>. 41<br>. 41 |

| 7  | Static signals                                                                                                                                                                                                                                                                                         |                                              |

| 8  | <ul> <li>7.1 Timing for static signals</li> <li>Electrical specifications</li> <li>8.1 Absolute maximum ratings</li> <li>8.2 Operating conditions</li> <li>8.3 DC characteristics</li> <li>8.4 Equivalent circuits</li> <li>8.5 Power rating</li> </ul>                                                | <b>43</b><br>43<br>43<br>43<br>44            |

| 9  | Thermal data                                                                                                                                                                                                                                                                                           | 47                                           |

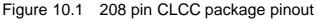

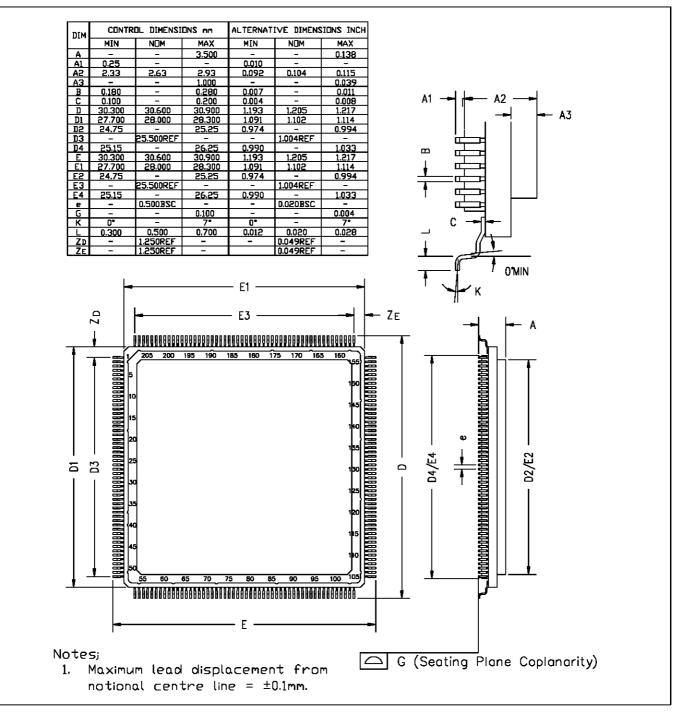

| 10 | Package specifications                                                                                                                                                                                                                                                                                 | 48                                           |

| 11 | Ordering                                                                                                                                                                                                                                                                                               | 51                                           |

# Errata sheet

# **Instruction Set**

# **FP** instructions

The following floating point instructions are not fully supported: *fpi32tor32*, *fpchki32*, *fpchki64*, *fpint*, *fprtoi32*, *fpstnli32*, *fprem*, *fprange*, *fpeq*, *fplg*, *fple*, *fpgt*, *icl*, *fdcl*, *ica*, *fdca*, *eqc* 0. Workarounds are present in all SGS-THOMSON T9000 compilers which make this transparent to users.

References: INSdi03119 INSdi03047 INSdi03021 INSdi03171

## causeerror and syscall

The instructions *causeerror* and *syscall* save an incorrect **lptr** when executed in a process with a null trap handler.

Reference: INSdi03817

#### devmove

The *devmove* instruction may malfunction where the source address is not aligned on a word boundary and the source and destination do not have the same alignment. In this situation, device load and store instructions must be used instead.

Reference: INSco00056

#### sttimer

An attempt to use the *sttimer* instruction to set the CPU Timer may set an incorrect value. If it is necessary to set a specific value, the value should be read back after writing, checked, and rewritten until it is correct.

Reference: INSco00057

# crcword, crcbyte

CRC instructions *crcword*, *crcbyte* require a software workaround to adjust the operands immediately before the relevant instruction is used.

Reference: INSco00058

# fpldall

*fpldall* requires that any single precision numbers are duplicated in both high and low words. This condition is met by *fpstall*.

Reference: INSco00060

#### fpdiv

In rare circumstances, the fpdiv instruction has been observed to return an incorrect result. If users experience a problem they are advised to avoid *fpdiv* or if not possible to contact support.

# Communications

# HdrAreaBase register after reset 2

After a reset 2 operation, the VCP HdrAreaBase register is reset rather than remaining unchanged, and so must be reprogrammed.

Reference: INSdi03508

# HeaderAreaBase read address

In order to read the HeaderAreaBase register, the config address #0801 should be used rather than #0901. Values should still be *written* to address #0901.

Reference: INSdi03468

# **Event channels in ALTs**

Event channels cannot be used as selecting inputs in ALT constructs.

Reference: INSdi03813

### sethdr instruction

The sethdr instruction will only program virtual channels with headers shorter than 4 bytes.

Reference: INSdi04058

### Reset 2

After reset 2 or a DS-Link reset, the VCP may fail to send the first outgoing packet, which may cause deadlock. Correct behavior is assured if the LocalizeError bit in each link is cleared before reset 2.

Reference: INSdi04165

# **DS-Link reset**

A DS-Link connection can fail to be reset correctly with a single ResetLink command. The workaround is to reset the link twice within 3.2 microseconds which requires the use of *stconf*, *resetch*, or *setchmode*.

Reference: INSco00052

# **DS-Link input**

The DS-Link input will ignore the first falling edges after reset. Therefore the link outputs of the other device should be reset low.

Reference: INSco00059

# Virtual resource channels

Virtual resource channels require a workaround: the server should guard the granting of the resource channel with an ALT.

# **Control Link return header**

The Control Link return header may be corrupted if RecoverError is used while Start is in progress.

Reference: INSco00066

# **Memory system**

## doallocate instruction

The *doallocate* instruction is not fully supported.

Reference: INSdi04166

### **Multiple error generation**

The EMI can generate four EmiErrors in response to a single error when *doallocate* is applied to an illegal address.

Reference: INSco00053

### Reset 2

After a reset 2, a read to an uncacheable location (i.e. a location not in device-only memory) should be made before sending a 'Run'.

Reference: INSco00051

#### **MemWait**

In the first cycle of MemWait being asserted, any configured transition on the Write strobes will nevertheless occur.

Reference: INSsy00063

# Databus active during BusReleaseTime

The T9000 may erroneously drive the databus during BusReleaseTime.

Reference: INSsy00100

#### MemWait incorrect in penultimate cycle

MemWait cannot be used in the penultimate cycle of an access to a bank configured to have a non zero precharge time. The workaround is to extend the memory access time by one cycle, so that MemWait is not asserted in the penultimate cycle.

Reference: INSco00055

#### **Illegal accesses**

The IMS T9000 may make speculative accesses to illegal locations. These may cause an error and therefore Bank 3 should be configured to cover all addresses. It is possible that the access made is to a device bank, see below.

# **Unprotected device banks**

The setting of device banks may not protect from non device accesses. This includes the possibility of speculative accesses being made to a device.

Reference: INSco00064

# **Miscellaneous**

# ajw, gajw instructions

P process address protection will not cause a trap when either of the instructions *ajw* or *gajw* accesses an illegal address. A trap will however occur on a subsequent illegal access.

Reference: INSdi03022

### **IEEE values**

IEEE denormalized and NaN values are not supported (truncated to zero). Rounding mode is always set to round to nearest.

Reference: INSdi03119

# Write locking of configuration registers

Write locking of the configuration registers is not implemented.

Reference: INSdi04167

# Reset 3

Reset 3 may fail to place the CPU in a runnable state if a CPU error or other global error has occurred, despite returning a handshake indicating success. Reset 2 should be used in this case.

Reference: INSco00018

# Jump 0

Jump 0 breakpoints may be reported as memory semantics errors.

# 1 IMS T9000 introduction

The IMS T9000 transputer is a 32-bit CMOS microprocessor designed to be used in applications which require high performance combined with high integration and simplicity of use. Software support for the IMS T9000 transputer includes ANSI C compilers and occam toolsets developed and supported by SGS-THOMSON.

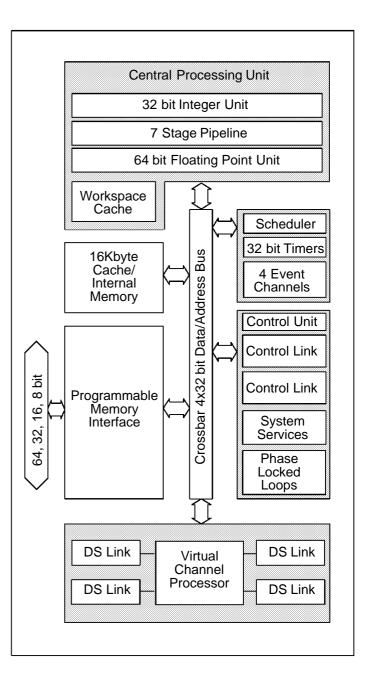

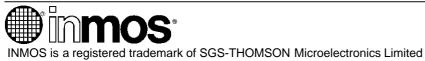

Figure 1.1 shows the major operational units of the IMS T9000 transputer.

The IMS T9000 has a pipelined superscalar architecture, which allows multiple instructions to be executed every processor cycle. Compilers can generate code without considering any details of the pipeline as the hardware organizes the incoming instruction stream into optimum groups of instructions. Other features which contribute to performance are a 16 Kbyte instruction and data cache, a 64-bit floating point unit, and a high bandwidth programmable memory interface. A separate work-space cache stores 32 locations relative to the workspace pointer to provide zero latency access to local variables. The IMS T9000 has four communication links for fast inter-processor communications.

The FPU provides single and double length arithmetic. The IMS T9000 running at a processor speed of 20 MHz is able to perform floating point operations at a rate of 7 Mflops sustained.

The 16 Kbyte cache provides a peak bandwidth of 400 Mbytes/sec. It can also be programmed to function as 16 Kbyte of on-chip memory, or as 8 Kbyte of on-chip memory and 8 Kbyte of cache. This allows small applications to run with no external memory, and guarantees deterministic code behavior for applications where this is critical.

The highly integrated programmable memory interface has a 4 Gbyte physical address space, and provides a peak bandwidth of 100 Mbytes/sec. Four independent banks of external memory are supported, and this allows the implementation of mixed memory systems, with support for DRAM, SRAM, EPROM and VRAM. It has a 64-bit data bus, and each bank of memory can be configured to be 8, 16, 32 or 64 bits wide. The full performance of the IMS T9000 can be exploited using low-cost DRAM, and up to 8 Mbytes of DRAM can be connected with no external components.

Transputers provide hardware support for scheduling processes, and this can be used directly by applications written, for example, in C or OCCAM. It can also be used to simplify the software implementation of real-time kernels and operating systems. The process model of the IMS T9000 transputer provides per process error handling and debugging support, and allows programs to be run in a protected logical address space. To improve the efficiency of real-time kernels access to the state of the processor has been simplified, and full control over interrupts and timeslicing has been provided.

Communication between processes takes place over channels, and is implemented in hardware. The same machine instructions are used for communication between processes on the same processor as for communication between processes on different IMS T9000 processors. On the IMS T9000, communication between processes on different processors takes place over *virtual* channels. Virtual channels are multiplexed onto each physical link by the virtual channel processor. Communication between IMS T9000 transputers that are not directly connected is achieved by using a separate asynchronous packet switch, the STC104.

With virtual channels it is not necessary for the programmer to allocate channels to physical links, and the allocation of processes to processors is simplified. The programming of powerful multiprocessor systems is therefore flexible and elegant.

Figure 1.1 IMS T9000 block diagram

The IMS T9000 has four high-bandwidth serial communication links which support virtual channels and dynamic message switching and provide a high data bandwidth with high data integrity. Each physical link consists of four wires, two in each direction, one carrying data and one carrying a strobe. The links are therefore referred to as data-strobe (DS-Links). The four DS-Links support a total bidirectional data bandwidth of 40 Mbytes/sec.

Two separate control links are provided to enable networks of IMS T9000 processors to be controlled and monitored for errors, even during the presence of faults in the normal data communications network. The control links of IMS T9000s and STC104s can be daisy chained, and/or connected into a tree by connection to a STC104. Whatever the physical connectivity the controlling network forms a logical tree, and a control processor is connected at its root. For small systems (such as a single IMS T9000 transputer) there is no need to use the control links as all necessary functionality can be controlled from software.

The hardware scheduling mechanism enables the creation and execution of any number of high and low priority processes. It handles timeslicing and message passing, often eliminating the need for a software kernel. Context switch time is sub-microsecond. Two 32-bit clocks tick at 1ns and 64ns intervals. The scheduler provides each process with a timer, simplifying real-time programming.

Four Event I/O pins provide asynchronous handshake interfaces between external events and internal processes and can be used as interrupts or as control for external peripherals. Response time is sub-microsecond.

Two on-chip phase locked loops generate all the internal high frequency clocks from a single clock input, simplifying system design and avoiding problems of distributing high speed clocks externally. The nominal input clock frequency used by all transputer family components is 5 MHz, regardless of device type, transputer word length, or processor cycle time.

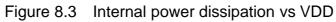

# 2 Pin designations

The following tables outline the function of each of the pins. Pinout details are given in Chapter 10, *Package specifications*.

Signal names are prefixed by **not** if they are active low, otherwise they are active high.

# Supplies

| Pin | In/Out | Function     |

|-----|--------|--------------|

| VDD |        | Power supply |

| GND |        | Ground       |

# Table 2.1 IMS T9000 supplies

# Phase locked loops

| Pin In/Out         |     | Function                                           |  |  |  |  |  |

|--------------------|-----|----------------------------------------------------|--|--|--|--|--|

| CapPlus, CapMinus  |     | External capacitor for internal clock power supply |  |  |  |  |  |

| <b>ClockIn</b> in  |     | Input clock                                        |  |  |  |  |  |

| ProcSpeedSelect0-2 | in  | Processor speed selectors                          |  |  |  |  |  |

| ProcClockOut       | out | Processor clock                                    |  |  |  |  |  |

## Table 2.2 IMS T9000 phase locked loops

# Programmable memory interface

| Pin            | In/Out | Function                            |  |  |  |

|----------------|--------|-------------------------------------|--|--|--|

| MemAddr2-31    | out    | Address bus                         |  |  |  |

| MemData0-63    | in/out | Data bus                            |  |  |  |

| notMemRAS0-3   | out    | RAS strobes – one per bank          |  |  |  |

| notMemCAS0-3   | out    | CAS strobes – one per bank          |  |  |  |

| notMemPS0-3    | out    | Programmable strobes – one per bank |  |  |  |

| notMemWrB0-3 { | out    | Byte-addressing write strobes       |  |  |  |

| MemWait        | in     | Memory cycle extender               |  |  |  |

| MemReqIn       | in     | Direct memory access request        |  |  |  |

| MemGranted     | out    | Direct memory access granted        |  |  |  |

| MemReqOut      | out    | Processor requires memory bus       |  |  |  |

| notMemBootCE   | out    | Bootstrap ROM chip enable           |  |  |  |

| notMemRf       | out    | Dynamic memory refresh indicator    |  |  |  |

{ these pins have different functions depending on the external port sizes

Table 2.3

IMS T9000 programmable memory interface

# **Control system**

| Pin In/Out          |     | Function                            |  |  |  |  |

|---------------------|-----|-------------------------------------|--|--|--|--|

| StartFromROM in     |     | Boot from external ROM or from link |  |  |  |  |

| Reset               | in  | System reset                        |  |  |  |  |

| CLinkInData0-1 in   |     | Control link input data channels    |  |  |  |  |

| CLinkInStrobe0-1 in |     | Control link input strobes          |  |  |  |  |

| CLinkOutData0-1 out |     | Control link output data channels   |  |  |  |  |

| CLinkOutStrobe0-1   | out | Control link output strobes         |  |  |  |  |

# Table 2.4 IMS T9000 control system

# **Communication links**

| Pin In/Out                                                |     | Function                  |

|-----------------------------------------------------------|-----|---------------------------|

| LinkInData0-3         in         Link input data channels |     | Link input data channels  |

| LinkInStrobe0-3 in                                        |     | Link input strobes        |

| LinkOutData0-3                                            | out | Link output data channels |

| LinkOutStrobe0-3                                          | out | Link output strobes       |

## Table 2.5 IMS T9000 communication links

# **Events**

| Pin         | In/Out | Function      |

|-------------|--------|---------------|

| EventIn0-3  | in     | Event inputs  |

| EventOut0-3 | out    | Event outputs |

#### Table 2.6 IMS T9000 event

# **Miscellaneous**

| Pin                                | In/Out | Function                 |

|------------------------------------|--------|--------------------------|

| HoldToGND Must be connected to GND |        | Must be connected to GND |

| HoldToVDD                          |        | Must be connected to VDD |

| DoNotWire                          |        | Must not be wired        |

Table 2.7 IMS T9000 miscellaneous pins

# 3 **Programmable memory interface**

The IMS T9000 programmable memory interface (PMI) can access a 4 Gbyte physical address space, and provides a peak bandwidth of 80 Mbytes/sec at 20MHz. It is designed to support memory subsystems with minimal external support logic. The interface has internal logic to provide decode and timing control functions and can be programmed through the configuration registers.

The external address space is partitioned into four banks (not to be confused with the four cache banks). This allows the implementation of mixed memory systems, with support for DRAM, SRAM, EPROM, VRAM and I/O. The timing of each of the four memory banks can be programmed separately, with a different device type being placed in each bank with no external hardware support. The PMI has a 64 bit data bus, and each bank of memory can be configured to be 8, 16, 32 or 64 bits wide. The PMI directly supports: 8, 16, 32 and 64 bit SRAM; 32 and 64 bit DRAM. All banks programmed to be 64 bit wide memory are defined as cacheable and always transfer a full 64 bit operand to and from external memory to the internal cache, providing fast cache refill. The full performance of the IMS T9000 transputer can be exploited using relatively low-cost DRAM, and up to 8 Mbytes of DRAM can be connected with no external components.

The IMS T9000 PMI has the following features:

- S multiplex addressing which replaces the need for an external address multiplexor in DRAM system design

- S separate RAS and CAS strobes for each bank

- S an extra programmable strobe for each bank

- S four write strobes which can be used to write part-words or bytes

- S support for DMA accesses.

In this chapter a *cycle* is one processor clock cycle and a *phase* is one quarter of the duration of one processor clock cycle.

# 3.1 External bus cycles

Transputer memory is byte addressed, with words aligned on eight-byte boundaries for 64 bit devices, four-byte boundaries for 32 bit devices and on two-byte boundaries for 16 bit devices.

During read cycles byte level addressing is performed internally by the IMS T9000. The PMI can read bytes, half-words, words or dual-words. It always reads the size of the bank.

During write cycles the IMS T9000 uses the **notMemWrB0-3** strobes to perform addressing of bytes. If a particular byte is not to be written then the corresponding data outputs are tristated. This allows writes to specified bytes within a word for 16 and 32 bit wide ports, but not for 64 bit wide ports which must always be cached.

The internally generated address is indicated on pins **MemAddr2-31**. However the two low order address bits, **A0-1**, are generated on pins **notMemWrB2-3** respectively as required for 8-bit and 16-bit external data buses.

The least significant bit of the data bus is always **MemData0**. The most significant bit can be adjusted dynamically to suit the required external bus size.

# 3.1.1 Generic memory cycle

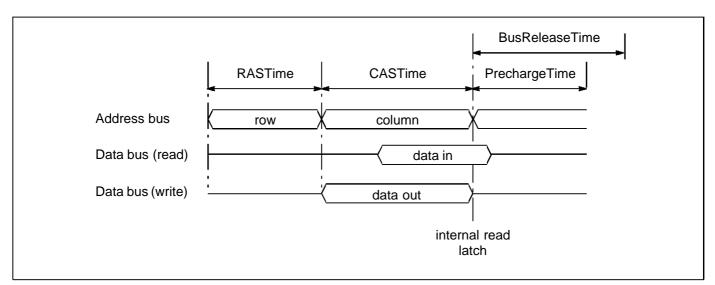

A generic memory interface cycle consists of a number of defined periods, or times, as shown in Figure 3.1. This generic memory cycle uses DRAM terminology to clarify the use of the interface in the most complex situations, but can be programmed to provide waveforms for a wide range of other device types. The timing of each of the four memory banks can be programmed separately, with a different device type being placed in each bank with no external hardware support.

Figure 3.1 Generic memory cycle

The **RASTime** and **CASTime** are consecutive. The **CASTime** can be followed by concurrent **Pre-charge** and **BusRelease** times. Thus, for DRAM, the times are used for RAS, CAS, and precharge respectively. For non-multiplexed addressed memory the **RASTime** can be programmed to be zero.

If the **RASTime** is programmed to be non-zero, and page-mode memory is programmed in a bank, the **RASTime** will only occur if consecutive accesses are not in the same page. The **RASTime** will not commence until the **PrechargeTime** for a previous access has completed. During this time the address is multiplexed by the amount specified in the format control register for the bank so as to output the row address on the address bus. During the **RASTime** a transition can be programmed on the RAS strobe, but not on any other strobe.

During the **CASTime**, all strobes are active. The address is output on the address bus without being shifted. Write data is valid during **CASTime**. The point at which read data is latched into the interface is referenced to the end of the **CASTime** cycle.

Parametrics are listed in section 3.1.2.

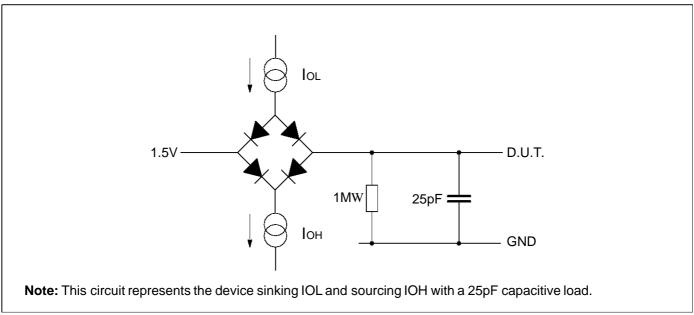

# 3.1.2 AC timing characteristics

The IMS T9000 PMI has three types of pins; address, data and strobe pins. The falling and rising edges of the strobe pins are programmable through the configuration registers. The following specification is given either as an absolute timing value or as a skew (Dtspec) from the nominal programmed number of phases (tn), where tn = (nominal programmed number of phases) / (4 \* internal clockSpeed). The overall spec value must also be adjusted to take into account the effect of clock variation (caused by the Phase Lock Loop). The amount of clock variation is expressed as

a percentage by the **tPCSTAB** parameter (see Table 6.4). The relationship between the parameter (tsPEC) as specified on the timing diagrams, the skew and the programmed value is as follows:

$$t_{SPEC} + t_n " \frac{t_n x t_{PCSTAB}}{100}) Dt_{SPEC}$$

(1)

The 'clock variation' component of **tspec** is assumed to be the very worst case that can happen, i.e. consecutive clock phases at their shortest or fastest for many clock cycles. This component should be added into the calculation of **tspec** to give the worst case value.

The following table gives the data setup and hold times for read, write and wait cycles. It also specifies the maximum skew from the nominal programmed values between the address and strobe pins.

Note, a minimum timing value with a negative value indicates that the transition of the second signal can occur before the first signal. For example the minimum timing specification for address setup to strobe valid is –9ns, i.e. the strobe can be valid 9ns before address setup.

# **Read cycle**

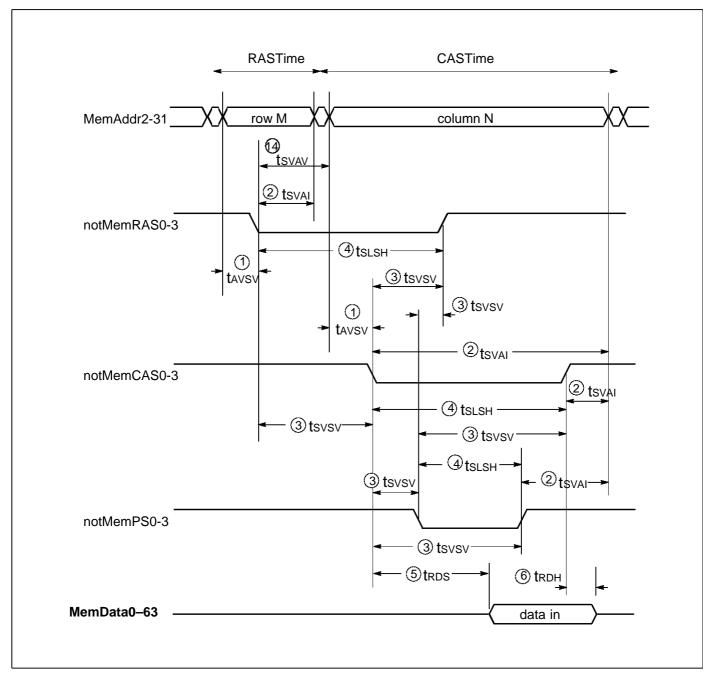

Figure 3.2 Read cycle timing

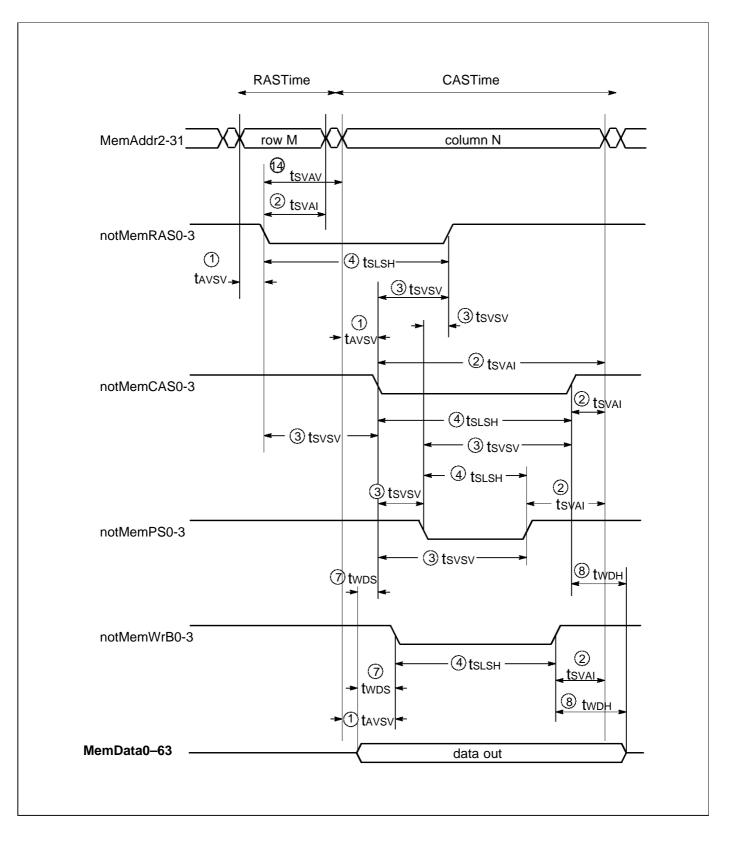

# Write cycle

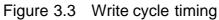

# **Consecutive cycles**

Figure 3.4 Cycle to cycle timing

| Symbol | No. | Parameter                                  | Parameter<br>type<br>(see note 1) | Min | Nominal                               | Max | Units  | Notes   |

|--------|-----|--------------------------------------------|-----------------------------------|-----|---------------------------------------|-----|--------|---------|

| DtAVSV | 1   | Address setup to strobe valid              | skew                              | -9  | -                                     | 0   | ns     | 2,3     |

| Dtsvai | 2   | Address hold after strobe valid            | skew                              | -3  | -                                     | +6  | ns     | 2,3     |

| Dtsvsv | 3   | Strobe valid to strobe valid               | skew                              | -7  | -                                     | +5  | ns     | 2,5     |

| DtSLSH | 4   | Strobe low to strobe high                  | skew                              | -4  | _                                     | +7  | ns     | 2,6     |

| DtSHSL | 9   | Strobe high to strobe low                  | skew                              | -7  | _                                     | +4  | ns     | 2,6     |

| DtSVAV | 14  | Strobe valid to next address valid         | skew                              | 0   | -                                     | +9  | ns     | 2,4     |

| tRDS   | 5   | Read data valid after <b>notMemCAS</b> low | nominal                           | -   | (CASTime*4)<br>-E1Time <sub>CAS</sub> | -   | phases | 7,8,14  |

| DtRDS  |     |                                            | skew                              | -   | _                                     | -19 | ns     |         |

| trdh   | 6   | Read data hold after <b>notMemCAS</b> high | nominal                           | -   | (CASTime*4)<br>–E2Time <sub>CAS</sub> | -   | phases | 9,10,14 |

| Dtrdh  |     |                                            | skew                              | -5  | -                                     | _   | ns     |         |

| tWDS   | 7   | Write data setup before related            | nominal                           | -   | ( <b>E1Time</b> -1)                   | -   | phases | 11      |

| Dtwds  |     | strobe low                                 | skew                              | -22 | _                                     | _   | ns     | 2,12    |

| twdh   | 8   | Write data hold after related strobe high  | nominal                           | _   | (CASTime*4)<br>–E2Time                | -   |        | 13      |

| Dtwdh  |     |                                            | skew                              | -4  | -                                     | -   | ns     | 2,12    |

Table 3.1 PMI AC specifications

#### Notes

- 1 *Parameter type*: refer to equation 1 in section 3.1.2 for an explanation of how tn (nominal programmed value) and DtsPEC (the skew) are related.

- 2 The timings are based on the following loading conditions: address pin loaded with 25 pF and strobe pins loaded with 25 pF. All parameters that reference strobe, apply to *all* memory strobes *eg* **notMemWrB0-3**, **notMemRAS0-3**, **notMemCAS0-3**, **notMemPS0-3**.

- 3 The value of this parameter is given by the programmed position of the falling edge (**RASEdgeTime** or **E1Time**) of the **RAS**, **CAS** or **PS** strobe.

- 4 The value of tsvav is given by the programmed length of the sub-cycle (**RASTime** or **CASTime**) minus the programmed position of the falling strobe edge (**RASEdgeTime** or **E1Time**).

- 5 The value of tsvsv is given by the absolute difference between any pair of falling edges (**RASEdgeTime** or **E1Time**) or any pair of rising edges (**E2Time**) or any falling to rising pair of strobes.

- 6 The nominal strobe pulse width (tSLSH or tSHSL) is given by the difference between the programmed falling (**RASEdgeTime** or **E1Time**) and the programmed rising edge (**E2Time**) of a **RAS**, **CAS** or **PS** strobe. This is applicable to a positive or negative pulse.

- 7 Where E1Time<sub>cas</sub> is the programmed falling edge position (E1Time) for notMemCAS expressed in clock phases.

- 8 The nominal value of tRDS could be extended by any wait cycles that are inserted after **notMemCAS** goes low. In this case, add 4 phases for every wait cycle.

- 9 Where E2Time<sub>CAS</sub> is the programmed rising edge position (E2Time) for notMemCAS expressed in clock phases.

- 10 The nominal value of tRDH could be extended by any wait cycles that are inserted after **notMemCAS** goes high again. In this case, add 4 phases for every wait cycle.

- 11 The nominal value of twos is given by the programmed E1Time for notMemCAS0-3 or notMemWrB0-3.

- 12 Timings are for all four byte write strobes notMemWrB0-3.

- 13 The nominal value of tWDH is given by the programmed **CASTime** *minus* the programmed position of the rising edge of **notMemCAS0-3** or **notMemWrB0-3**. Output data may be held indefinitely if there are no subsequent external cycles.

- 14 These figures are irrespective of the programmed strobe edges as the T9000 subsystems latch data internally and so are not directly related to the programmed strobe timings.

# 3.2 External DMA

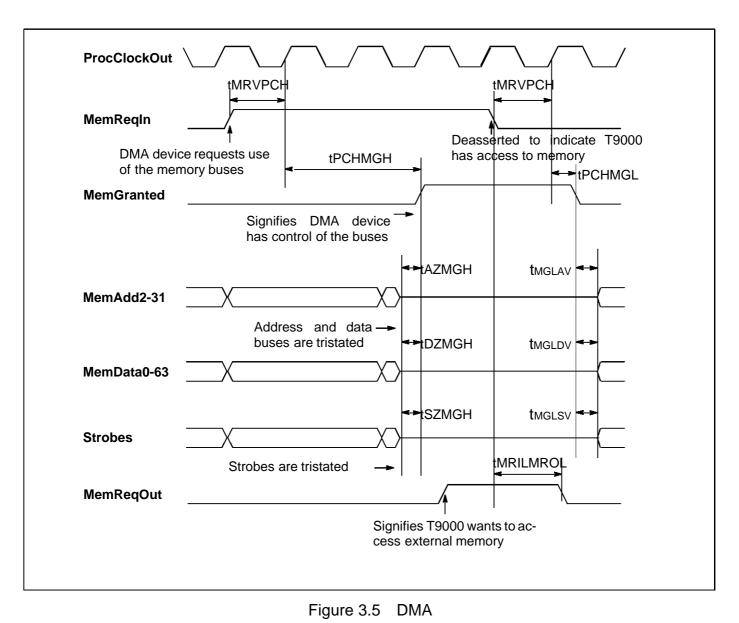

The **MemReqIn** pin high causes the IMS T9000 to tri-state its memory buses so that an external DMA can access memory. **MemReqIn** is sampled during each cycle of **ProcClockOut**, whilst the PMI is idle, or on the last cycle of any external access. If the current cycle is a four-word cache line refill then the four words of the line are read in before the PMI responds. If the cycle is a refresh cycle it is allowed to terminate before the PMI responds. If the current cycle is a word transfer to a smaller port then the interface completes the transfer of the sub-words before responding. **MemGranted** is asserted during the first clock cycle after the current cycle terminates. The address bus, data bus and the strobes are tristated during this clock cycle (see also Figure 3.5).

Deassertion of **MemReqIn** is sampled during each **ProcClockOut** and **MemGranted** is deasserted during the next clock period.

Strobes are tristated during the DMA transfer. If DMA is active for longer than one programmed refresh interval then external logic is responsible for providing refresh.

DMA allows a bootstrap program to be loaded into external memory for execution after reset. If **MemReqIn** is held high during reset, **MemGranted** will be asserted before bootstrapping from external memory begins. The bootstrap sequence will continue when **MemReqIn** is deasserted. This will not prevent bootstrapping from the control links taking place.

The IMS T9000 processor can continue to execute out of the cache until a request to external memory is required. If a DMA operation is in progress then execution will stall until the DMA is complete. The **MemReqOut** indicates to external logic that IMS T9000 external bus cycles are pending and execution has stalled. External logic can use this information to continue or interrupt the DMA transfer in progress.

Notes

1 In Figure 3.5 Strobes consist of the following signals: notMemRAS0–3, notMemCAS0–3, notMemPS0–3, notMemRf and notMemBootCE.

| Symbol     | Parameter                                             | Parameter<br>type | Min | Nominal | Max | Units  | Notes |

|------------|-------------------------------------------------------|-------------------|-----|---------|-----|--------|-------|

|            |                                                       | (see note 1)      |     |         |     |        |       |

| tMRVPCH    | MemReqIn setup before ProcClockOut rising             | absolute          | +20 | -       | -   | ns     | 2     |

| tPCHMGH    | MemReqIn response time                                | nominal           | -   | 2       | -   | cycles | 3     |

| DtPCHMGH   | MemReqIn response time                                | skew              | +9  | -       | +20 | ns     |       |

| tPCHMGL    | MemReqIn end response time                            | nominal           | -   | 1       | _   | cycles |       |

| DtPCHMGL   | MemReqIn end response time                            | skew              | +9  | -       | +20 | ns     |       |

| tAZMGH     | Address Bus tristate before <b>MemGranted</b> high    | absolute          | 0   | -       | _   | ns     |       |

| tDZMGH     | Data Bus tristate before MemGranted high              | absolute          | 0   | -       | _   | ns     |       |

| tSZMGH     | Strobes Bus tristate before <b>MemGranted</b> high    | absolute          | 0   | -       | _   | ns     |       |

| tMGLAV     | Address Bus active after end of <b>MemGranted</b> low | absolute          | -   | -       | 5   | ns     |       |

| tMGLDV     | Data Bus active after end of MemGranted low           | absolute          | -   | -       | 5   | ns     |       |

| tMGLSV     | Strobes Bus active after end of <b>MemGranted</b> low | absolute          | -   | -       | 5   | ns     |       |

| tMRILMROL  | MemReqOut                                             | nominal           | -   | 2       | _   | cycles |       |

| DtMRILMROL | MemReqOut                                             | skew              | 4   | -       | 4   | ns     |       |

#### Notes

- 1 *Parameter type*: refer to equation 1 in section 3.1.2 for an explanation of how tn (nominal programmed value) and DtsPEC (the skew) are related.

- 2 Setup time need only be met to guarantee sampling on the following rising edge of **ProcClockOut**.

- 3 If an external memory cycle is active, the maximum time could be the time taken to complete a (writeback cycle) + (refill cycle) + (refresh cycle), and for any bus release times to complete, where the refill and writeback may read or write up to 32 four bit words, taking the number of cycles determined by the width of the relevant memory bank.

| MemReqIn                            |                       |               |

|-------------------------------------|-----------------------|---------------|

| External memory<br>interface cycles | Read or write Refresh | Read or write |

| MemGranted                          |                       |               |

| Strobes                             | X                     |               |

| MemData0–63<br>MemAddr0–63          | X                     | <             |

Figure 3.6 IMS T9000 operation of **MemReqIn**, **MemGranted** with external, refresh memory cycles

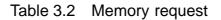

# 3.3 Memory refresh

The AC parameters of the strobe edges are equivalent to those defined for the strobes during a read/write cycle as shown in Table 3.1. Another access will not occur until the precharge time for that bank has expired.

**notMemRF** falls at the beginning of the refresh cycle and rises when the refresh is complete. Its AC parametrics are equivalent to those of the strobes.

Figure 3.7 Programming of the refresh control register

# 3.4 Memory wait

The PMI is designed to synthesize the required waveforms from the parameters in the **TimingControI0-3** registers. However, external control can be provided if required. If the **WaitEnable** bit is disabled (set to 0) then the external cycles are controlled exclusively by the **TimingControI0-3** registers. If the **WaitEnable** bit is enabled (set to 1) then **MemWait** is defined to operate as follows:

- S The **MemWait** pin is sampled during every clock cycle of the **RASTime** and the **CASTime** only. The sampling point is defined by tsvwv and tsvwi (see Table 3.3 and Figure 3.8).

- S The action of **MemWait** is to suspend the state of the cycle counters and the level of the strobes from the end of the cycle in which it is sampled high. This is maintained as long as **MemWait** is asserted.

- S When **MemWait** is deasserted counting continues as defined by the **TimingControl0-3** registers. Normal strobe behavior resumes from the end of the wait cycle during which **MemWait** is sampled low.

- Cycle 1 Cycle n Cycle m Tw Cycle Cycle m+1 m+2 MemAddr2-31 notMemCAS0-3 (ป) tsvwr νwv **MemWait** 12 twvcн ProcClockOut 3 tchw

- S If **MemWait** is asserted in the last cycle of a memory access then the results are undefined.

Figure 3.8 Memory wait timing

| Symbol        | No. | Parameter                | Parameter<br>type<br>(see note 1) | Min | Nominal              | Max | Units  | Notes |

|---------------|-----|--------------------------|-----------------------------------|-----|----------------------|-----|--------|-------|

| tsvwv         | 10  | Wait setup time          | nominal                           | -   | (m*4)- <b>E1Time</b> | -   | phases | 3,4   |

| Dtsvwv        |     |                          | skew                              | _   | _                    | –19 | ns     | 2     |

| ts∨wi         | 11  | Wait hold time           | nominal                           | -   | (m*4)-E1Time         | -   | phases | 3,4   |

| Dtsvwi        |     |                          | skew                              | +14 | _                    | _   | ns     | 2     |

| tw∨cн         | 12  | Wait valid before Clock  | nominal                           | +17 | -                    | -   | ns     | 2     |

| <b>t</b> CHWI | 13  | Wait invalid after Clock | nominal                           | -5  | _                    | -   | ns     | 2     |

#### Notes

### Table 3.3 Memory wait timings

- 1 *Parameter type*: refer to equation 1 in section 3.1.2 for an explanation of how tn (nominal programmed value) and DtsPEC (the skew) are related.

- 2 The timings are based on the following loading conditions: address pin loaded with 25 pF and strobe pins loaded with 25 pF. All parameters that reference strobe, apply to *all* memory strobes e.g. **notMemWrB0-3**, **notMemRAS0-3**, **notMemCAS0-3**, **notMemPS0-3**.

- 3 A wait state will be inserted between cycle **m** and cycle **m+1** in an **n** cycle access if the specified relationship is met.

- 4 In an **n** cycle access a wait cycle cannot be added after cycle **n–1**. Also, a wait cycle cannot be added before cycle 1.

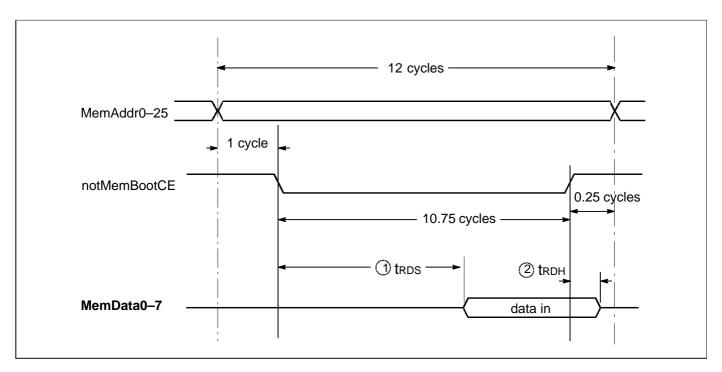

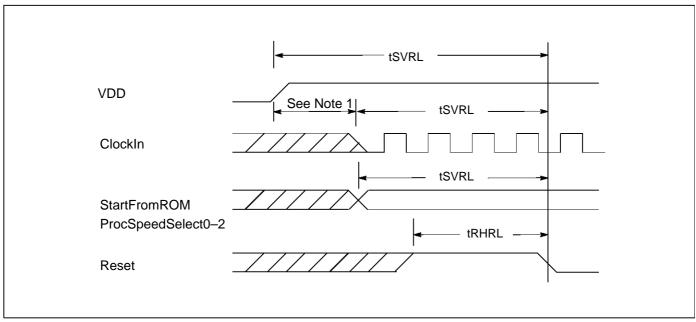

# 3.5 Booting from ROM

The IMS T9000 transputer can be bootstrapped from a ROM device, such as an EPROM or a Flash EPROM, or down control link (**CLink0**) from a host transputer or a computer with a link adaptor. In order to boot from ROM the **StartFromROM** pin must be held high.

# 3.5.1 Bootspace timing

The timing for accesses into the bootspace is not user programmable. The timing values used are defined in Figure 3.9. The timings have been deliberately relaxed to cover a wide range of ROM and T9000 speeds, typically 20 MHz to 30 MHz.

Figure 3.9 Boot cycle timing

| Symbol | No. | Parameter                                     | Parameter<br>type<br>(see note 1) | Min | Nominal | Мах | Units  | Notes |

|--------|-----|-----------------------------------------------|-----------------------------------|-----|---------|-----|--------|-------|

| tRDS   | 1   | Read data valid after <b>notMemBootCE</b> low | nominal                           | -   | 44      | -   | phases | 2     |

| Dtrds  |     |                                               | skew                              | -   | -       | -19 | ns     |       |

| trdh   | 2   | Read data hold after <b>notMemBootCE</b> high | nominal                           | -   | 1       | _   | phases | 2     |

| Dtrdh  |     |                                               | skew                              | -5  | _       | -   | ns     |       |

Table 3.4 Boot Cycle

#### Notes

- 1 *Parameter type*: refer to equation 1 in section 3.1.2 for an explanation of how tn (nominal programmed value) and DtsPEC (the skew) are related.

- 2 Read data must be valid as specified in Table 3.1. These figures are irrespective of the programmed strobe edges as the T9000 subsystems latch data internally and so are not directly related to the programmed strobe timings.

- 3 The AC parameters of the strobe edges are equivalent to those defined for the strobes during a read/write cycle as shown in Table 3.1.

- 4 The equivalent Bus Release Time for the next boot bank is 5 cycles.

# 4 Events

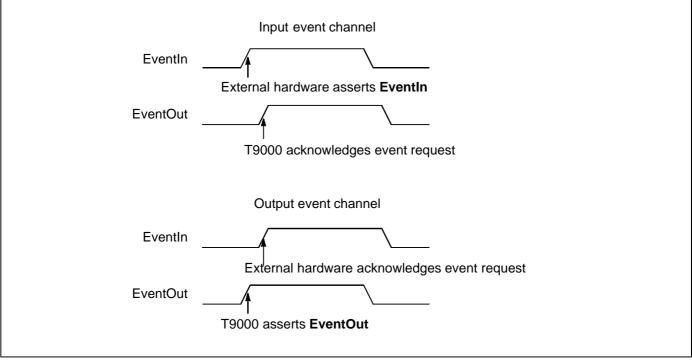

The **EventIn0-3** and **EventOut0-3** pins provide an asynchronous handshake interface between external events and internal processes. Event channels provide process synchronization but cannot transfer any data. Each pair of **EventIn** and **EventOut** pins can act either as an input or an output event channel, but not both simultaneously.

# Input event channel

When an external event takes an **EventIn** pin high the associated external event channel is made ready to communicate with a process. When both the event channel and the process are ready the processor takes the associated **EventOut** pin high and the process, if waiting, is scheduled. **EventOut** is removed after **EventIn** goes low. **EventIn** should not be taken low until **EventOut** has gone high.

# **Output event channel**

The IMS T9000 asserts the **EventOut** pin to instruct external hardware to perform an action. When both the event channel and the external hardware are ready the external hardware asserts the associated **EventIn** pin and responds to the instruction. **EventIn** should be removed after **EventOut** goes low.<sup>1</sup>

Only one process may use each event channel at any given time. If no process requires an event to occur **EventOut** will never be taken high. **EventOut** is taken low when **Reset** occurs or when a *resetch* instruction is executed on that channel.

Figure 4.1 Event

# Use of event channels with interrupts

An input event channel can be used for interrupts. Refer to *The T9000 Transputer Instruction Set Manual* for further information on how this can be achieved.

1 EventIn should not be set high until EventOut has been set high, and should not be removed until EventOut has gone low.

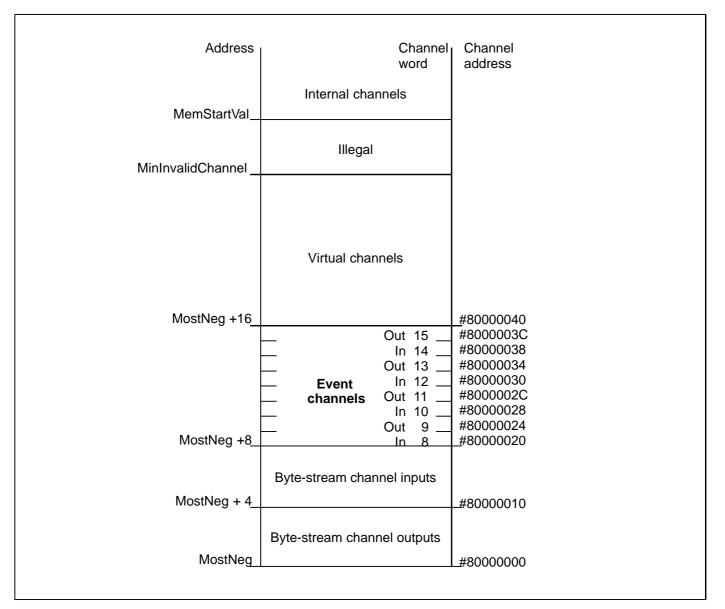

# 4.1 Event channel addresses

There are 8 words of memory reserved for event channels, from address #80000020 to #8000003C inclusive, see Figure 4.2. These addresses are also the channel addresses of the event channel. Each successive pair of words corresponds to one event channel. The lower address is used when the event is used for input, the higher address is used when the event is used for output. Thus the event channel address space is consistent with the virtual channel address space. In addition, provided the first event channel (**Event0**) is used for input, compatibility with the event channel address on the IMS T805 is achieved.

Each event channel must have a two word data structure to enable it to be used in resource mode. The (word-aligned) base of the block of memory for the resource mode words is pointed to by the **ExternalRCBase** configuration register. The two words for each of the four event channels are allocated at the bottom of the block.

Figure 4.2 IMS T9000 channel address space

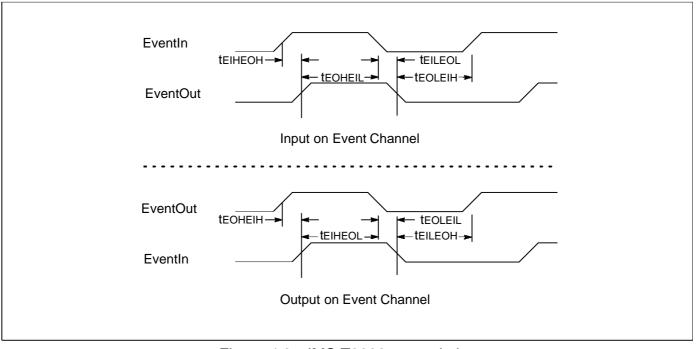

# 4.2 Event timing

| Symbol          | Parameter                             | Min            | Nominal | Max | Units | Notes |

|-----------------|---------------------------------------|----------------|---------|-----|-------|-------|

| <b>teiheoh</b>  | EventOut response to EventIn          | 0              | 1       |     | mS    |       |

| <b>tEOHEIL</b>  | Eventin hold                          | 0              |         |     | ns    |       |

| <b>tEILEOL</b>  | Delay before removal of EventOut      | 0              |         |     | ns    |       |

| <b>t</b> EOLEIH | Delay before re-assertion of EventIn  | 1 ProcClockOut |         |     | ns    |       |

| <b>teoheih</b>  | Delay before assertion of EventIn     | 0              |         |     | ns    |       |

| <b>tEIHEOL</b>  | EventOut response to EventIn          | 0              |         |     | ns    |       |

| <b>t</b> EOLEIL | Delay before removal of Eventin       | 0              |         |     | ns    |       |

| tEILEOH         | Delay before re-assertion of EventOut | 0              |         |     | ns    |       |

Table 4.1 Event timing parameters

Figure 4.3 IMS T9000 event timing

# 5 Data/Strobe links

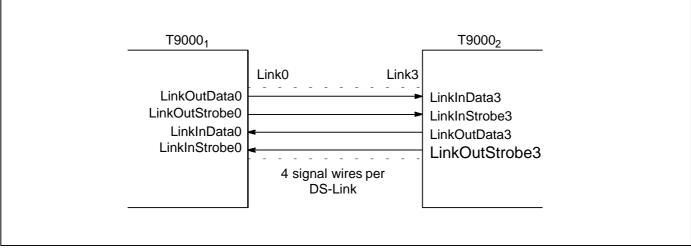

The IMS T9000 has four bidirectional links for normal inter-processor communications, and two additional links which can only be used for control purposes. All of these links use a protocol with two wires in each direction, one for data and one to carry a strobe signal, see Figure 5.1. These links are therefore referred to as data/strobe (DS-Links). The DS-Links are capable of:

- S Up to 100 Mbits/s

- S Unidirectional peak bandwidth of 10Mbytes/s per link

- S Support for virtual channels and through routing.

The links are TTL voltage compatible and are optimized for driving a 100 ohm transmission lines. The links can be directly connected with no external buffering or other glue logic.

Figure 5.1 shows two transputers connected via DS-Links. In this example Link0 of  $T9000_1$  is connected to Link3 of  $T9000_2$ .

Figure 5.1 DS-Links

# 5.1 Link format and protocol

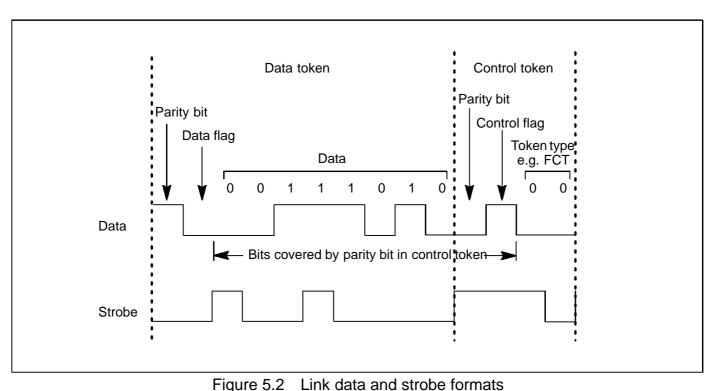

Each DS pair carries tokens and an encoded clock. The tokens can be data bytes or control tokens. Figure 5.2 shows the format of data and control tokens on the data and strobe wires. Data tokens are 10 bits long and contain a parity bit, a flag which is set to 0 to indicate a data token, and 8 bits of data. Control tokens are 4 bits long and contain a parity bit, a flag which is set to 1 to indicate a control token, and 2 bits to indicate the type of control token.

The DS-Link protocol ensures that only one of the two wires of the data strobe pair has an edge in each bit time. The levels on the data wire give the data bits transmitted. The strobe signal changes whenever the data signal does not. These two signals encode a clock together with the data bits,

permitting asynchronous detection of the data at the receiving end.

The data and control tokens are of different lengths, for this reason the parity bit in any token covers the parity of the data or control bits in the previous token, and the data/control flag in the same token, as shown in Figure 5.2. This allows single bit errors in the token type flag to be detected. **Odd** parity checking is used. Thus the parity bit is set/unset to ensure that the bits covered, inclusive of the parity bit (see Figure 5.2), always contain an odd number of 1's. The coding of the tokens is shown in Table 5.1.

| Token type         | Abbreviation | Coding    |

|--------------------|--------------|-----------|

| Data token         | -            | P0DDDDDDD |

| Flow control token | FCT          | P100      |

| End of packet      | EOP          | P101      |

| End of message     | EOM          | P110      |

| Escape token       | ESC          | P111      |

| Null token         | NUL          | ESC P100  |

P = parity bit

D = data bit

# Table 5.1 Token codings

One of the four control tokens is an escape token. The escape token is used to construct other 'composite' control tokens, see Table 5.1. One of these is the null token. Null tokens are sent in the absence of other tokens to ensure the immediate detection of parity errors and to enable link disconnection to be detected.

# 5.2 Link functional description

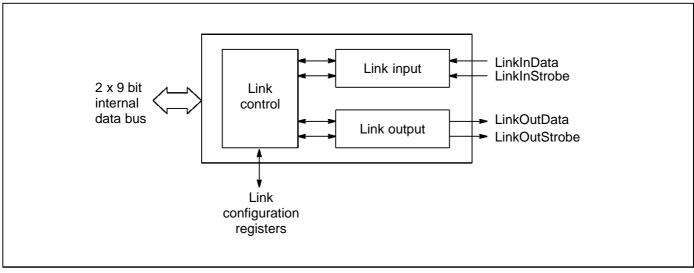

A link module consists of the units shown in Figure 5.3. The link control unit controls: link initialization, speed control, error reporting, etc. It connects to the link registers in the configuration space (refer to section 5.4). The link input unit interprets edge streams as tokens. The link output unit converts tokens to streams of edges.

Figure 5.3 Link module

# 5.3 Link speed select

The IMS T9000 DS-Links support a range of communication speeds. The speed of a DS-Link is programmed by writing to registers in the configuration space.

Only the transmission speed of a DS-Link is programmed as reception is asynchronous. This means that DS-Links transmitting at different speeds can be connected, provided that each device is capable of receiving at the speed of the connected transmitter.

The transmission speed of all four DS-Links on the IMS T9000 are related to the speed of the 10 MHz base clock. This 10 MHz clock is multiplied by a programmable value to provide the root clock for all the DS-Links. The multiplication factor is programmed by writing to the **SpeedMultiply** bit in the **DSLinkPLL** register. This root clock is then optionally divided (by programming the **SpeedDivide** bits) by 1, 2, 4 or 8 independently for each DS-Link, giving a range of speeds. This arrangement allows each DS-Link to be run at one of four transmission speeds, as shown in Table 5.2.

| SpeedMultiply | SpeedDivide1:0 |     |     |            | BaseSpeed |

|---------------|----------------|-----|-----|------------|-----------|

|               | 0:0            | 0:1 | 1:0 | 1:1        |           |

|               | @              | @2  | @4  | @ <b>8</b> |           |

| 8             | 80             | 40  | 20  | 10.0       | 10        |

| 10            | 100            | 50  | 25  | 12.5       | 10        |

| 12            | Reserved       | 60  | 30  | 15.0       | 10        |

| 14            | Reserved       | 70  | 35  | 17.5       | 10        |

| 16            | Reserved       | 80  | 40  | 20.0       | 10        |

| 18            | Reserved       | 90  | 45  | 22.5       | 10        |

| 20            | Reserved       | 100 | 50  | 25.0       | 10        |

Table 5.2DS-Link transmission speed in Mbits/sec

Note also that each DS-Link can be programmed to use a base rate clock of 10 MHz. At reset all DS-Links are configured to run at the **BaseSpeed** of 10 Mbits/sec. The **SpeedSelect** bit in the **Link0-3Mode** registers when set to 1 sets the respective DS-Link (**Link0-3**) to the speed selected by the **SpeedMultiply** and **SpeedDivide** bits, as opposed to the default base speed of 10 Mbits/s.

# 5.4 Link configuration registers

The DS-Links (in common with a number of other sub-systems of the IMS T9000) are controlled via a separate configuration address space. The registers in this address space are accessed via the *ldconf* and *stconf* instructions, or via *CPeek* and *CPoke* command messages received along **CLink0**.

Tables 5.3 to 5.7 describe the functionality of the DS-Links to be controlled, and the associated bit fields in the configuration registers. All SGS-THOMSON reserved bits should be set to 0.

Each DS-Link has four registers, the LinkMode register, LinkCommand register, LinkStatus register and LinkWriteLock register.

In addition the configuration space contains the **DSLinkPLL** register which contains the **SpeedMultiply** field. This determines the multiplication factor for the 10 MHz clock, to provide the root clock for all the DS-Links.

| DSLinkPLL #1005 |               | Read/Write                                                                                                                      |

|-----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------|

| Bit             | Bit field     | Function                                                                                                                        |

| 5:0             | SpeedMultiply | Sets DS-Link master clock to required value (see Table 5.2).<br>Note, 0 through to 7 are invalid values and should not be used. |

| 31:6            |               | SGS-THOMSON reserved.                                                                                                           |

| Table 5.3 | Bit fields in the <b>DSLinkPLL</b> register |

|-----------|---------------------------------------------|

|-----------|---------------------------------------------|

The Link0Mode, Link1Mode, Link2Mode, Link3Mode registers (one for each of the four DS-Links) power up into a default state and may be re-programmed before or after the DS-Link has been started.

Note also that each DS-Link can be programmed to use a base rate clock of 10 MHz. At reset all DS-Links are configured to run at the **BaseSpeed** of 10 Mbits/sec. The **SpeedSelect** bit in the **Link0-3Mode** registers when set to 1 sets the respective DS-Link (**Link0-3**) to the speed selected by the **SpeedMultiply** and **SpeedDivide** bits, as opposed to the default base speed of 10 Mbits/s.

| Link0 | -3Mode #8001  | , #8101, #8201, #8301 Read/Write                                                                                                                                                                                                                           |

|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Bit field     | Function                                                                                                                                                                                                                                                   |

| 1:0   | SpeedDivide   | The master link clock frequency is divided down by setting the <b>Speed-</b><br><b>Divide</b> bits to obtain the transmission frequency for each DS-Link.<br>Sets the transmit speed of the DS-Link (see Table 5.2).<br>00 = @1, 01 = @2, 10 = @4, 11 = @8 |

| 2     | SpeedSelect   | Sets the DS-Link to transmit at the speed determined by the <b>SpeedDi-</b><br>vide bits as opposed to the base speed of 10 Mbits/s.                                                                                                                       |

| 3     | LocalizeError | When set errors detected by the DS-Link are no longer reported to the control unit. Packets in transit at the time of an error will be discarded or truncated. (This bit is set by <b>Reset</b> to 1).                                                     |

| 4     | 1 (RESERVED)  | This bit should be written as 1.                                                                                                                                                                                                                           |

| 5,7   | 0 (RESERVED)  | These bits should be written as 0.                                                                                                                                                                                                                         |

| 6     | Mute Input    | When set to 1, all transitions on the link input are ignored.                                                                                                                                                                                              |

| 31:8  |               | SGS-THOMSON reserved.                                                                                                                                                                                                                                      |

Table 5.4Bit fields in the Link0-3Mode registers

The Link0Command, Link1Command, Link2Command, Link3Command registers are write only and contain four bits which when set cause a specific action to be taken by the DS-Link.

| Link0 | -3Command #8002 | , #8102, #8202, #8302 Write only                                                                                                                                                                                                           |

|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Bit field       | Function                                                                                                                                                                                                                                   |

| 0     | ResetLink       | Resets the link engine of the <b>Link0-3</b> . The token state is reset, the flow control credit is set to zero, the buffers are marked as empty, and the parity state is reset. It also resets the <b>LinkStatus</b> register error bits. |

| 1     | StartLink       | When a transition from 0 to 1 occurs <b>Link0-3</b> will be initialized and commence operation. It also resets the <b>LinkStatus</b> register error bits.                                                                                  |

| 2     | ResetOutput     | Sets both Data and Strobe outputs of Link0-3 low <sup>1</sup> .                                                                                                                                                                            |

| 3     | WrongParity     | The <b>Link0-3</b> output will generate incorrect parity. This may be used to force a parity error on the transputer at the other end of the <b>Link0-3</b> .                                                                              |

| 31:4  |                 | SGS-THOMSON reserved.                                                                                                                                                                                                                      |

Table 5.5 Bit fields in the Link0-3Command registers

1 Note that it is not necessary to do this in normal operation. This facility is provided in case the DS-Link is connected to non-transputer hardware which expects signals to be low after reset.

The Link0Status, Link1Status, Link2Status, Link3Status registers are read only and contain six bits which contain information about the state of the DS-Link.

| Link0 | Link0-3Status #8003, #8103, #8203, #8303 Read of |                                                                                                     |  |  |  |

|-------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|

| Bit   | Bit field                                        | Function                                                                                            |  |  |  |

| 0     | LinkError                                        | Flags that an error has occurred on the Link0-3.                                                    |  |  |  |

| 1     | LinkStarted                                      | Flags that the output <b>Link0-3</b> has been started and no errors have been detected.             |  |  |  |

| 2     | ResetOutputCom-<br>plete                         | Flags that <b>ResetOutput</b> has completed on the <b>Link0-3</b> .                                 |  |  |  |

| 3     | ParityError                                      | Flags that a parity error has occurred on the Link0-3.                                              |  |  |  |

| 4     | DiscError                                        | Flags that a disconnect error has occurred on the Link0-3.                                          |  |  |  |

| 5     | TokenReceived                                    | Flags that a token has been seen on the <b>Link0-3</b> since <b>ResetLink</b> or <b>LinkError</b> . |  |  |  |

| 31:6  |                                                  | SGS-THOMSON reserved.                                                                               |  |  |  |

Table 5.6Bit fields in the Link0-3Status registers

In addition to the above mentioned registers each DS-Link has an associated **LinkWriteLock** register. The write lock register provides protection from writes by the processor, so that the link is guaranteed to function regardless of program behavior.

Setting the write lock register inhibits all configuration writes to this link from the CPU. All control link reset commands clear all write locks.

Note that the CPU can start and reset the links by means of *resetch* and *setchmode* instructions even if the write lock is set.

| Link | )-3WriteLock #8004 | 4,#8104,#8204,#8304                                          | Read/Write |

|------|--------------------|--------------------------------------------------------------|------------|

| Bit  | Bit field          | Function                                                     |            |

| 0    | WriteLock          | When set to 1 it inhibits link configuration writes from the | e CPU.     |

| 31:1 |                    | SGS-THOMSON reserved.                                        |            |

# Table 5.7 Bit fields in the Link0-3WriteLock registers

# 5.5 Initialization

# 5.5.1 Link state on start up

After reset all **LinkData** and **LinkStrobe** signals are low, without clocks. Following reset an initialization sequence sets the speed of the link clock. The DS-Links are initially inactive, with a default configuration. They are configured and started by configuration writes. Their status can be determined by configuration reads. Each DS-Link (**Link0-3**) must be explicitly started by writing to the **Link0-3Command** registers respectively. When a DS-Link is started up it transmits NUL tokens unless and until it receives a token. Once it has been started and received a token it sends two FCT's.

Data may not be transferred over the link until the receiving link has sent a FCT to signify that it has enough free buffer space to receive the data.

The receiving link receives and correctly decodes the tokens. However, only when the receiving link has been explicitly started by writing across the (internal) configuration bus can it send tokens back. NUL tokens are then sent until data is required.

# 5.5.2 Link state following reset

Both **LinkData** and **LinkStrobe** are low following reset to level 0 or level 1. The DS-Links output pins are unchanged after a reset to level 2. Note that a particular DS-Link can be explicitly reset via the configuration bus.

The control logic is responsible for resetting the link input and output following an error, however it does not reset the configuration registers, or the Data and Strobe outputs. These may all be reset independently via the configuration registers.

Physical links can be reset in one of the following ways:

S A *resetch* (reset channel) instruction whose channel parameter designates a byte-stream channel.

This resets the queue registers for the link and resets and restarts the link.

S A *setchmode* (set channel mode) instruction with a parameter of 0, on a byte-stream channel, or by setting the **ResetLink** bit in the **Link0-3Command** configuration register via the configuration bus.

The token state is reset, the flow control credit is set to zero, the buffers are marked as empty, and the parity state is reset.

S VCP global reset.

This resets all four links.

The link automatically enforces a delay between reset and restart sufficient to guarantee that the other end will detect a disconnect error and complete its reset.

# 5.6 Link connections

DS-Links are not synchronized with **ClockIn** or **ProcClockOut** and are insensitive to their phases. Thus, links from independently clocked systems may communicate.

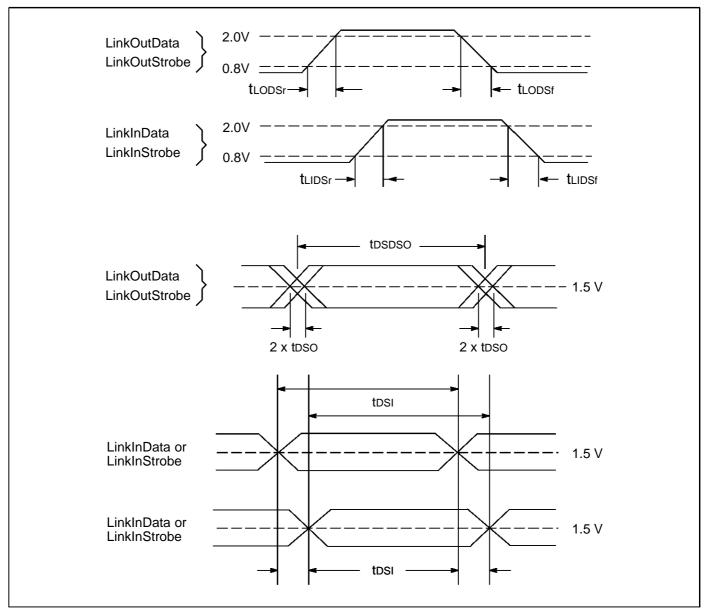

Figure 5.4 DS-Link timing

### 5.7 DS-Link parameters

| Symbol | Parameter                                 | Min | Nom | Max | Units | Notes |

|--------|-------------------------------------------|-----|-----|-----|-------|-------|

| CLIZ   | LinkIn capacitance                        |     | 7   |     | pF    |       |

| tDSDSI | Sustainable averaged input bit period     | 9   |     | 110 | ns    |       |

| tDSDSO | Output bit period                         | 10  |     | 100 | ns    |       |

| tDSI   | Data/strobe input edge minimum separation |     | 2.5 |     | ns    | 1,2,3 |

| tDSO   | Data/strobe output skew                   |     |     | 1   | ns    | 4     |

| tLIDSf | LinkIn fall time (2.0–0.8V)               |     |     | 100 | ns    | 6     |

| tLIDSr | LinkIn rise time (0.8–2.0V)               |     |     | 100 | ns    | 6     |

| tLODSf | LinkOut fall time (2.0–0.8V)              |     |     | 7   | ns    | 7     |

| tLODSr | LinkOut rise time (0.8–2.0V)              |     |     | 7   | ns    | 7     |

| ROH    | Output impedance (output driving high)    | 110 |     | 247 | W     | 8     |

| ROL    | Output impedance (output driving low)     | 63  |     | 104 | W     | 8     |

### Table 5.8 DS-Link timings

#### Notes

- 1 tDSDSO represents the minimum and maximum programmable bit periods.

- 2 tDSI is the shortest permissible spacing of 2 consecutive edges on the Data and Strobe wires (1 edge of either sense on each wire). If arriving Data and Strobe edges are skewed to the extent that this parameter is exceeded then the order of the edges becomes ambiguous and a parity error is likely to result.

- 3 Edge separation includes consecutive edges of a data input or a strobe input.

- 4 Based on a slew rate of 1.5 V/s, monotonic across the transition region. For other values of slew rate, use the following formula:

1.0 + (k \* slew rate) where k=1.0

- 5 tDSO is the maximum discrepancy between the time when a DS Output edge (either sense) starts a transition and the theoretical ideal (i.e. all consecutive DS edges spaced by tDSDSO).

- 6 Edges must be monotonic, hence faster edges are recommended unless the link is to be used in a noise free environment.

- 7 Measurement based on a loading of 25pF.

- 8 The link output drivers have been optimized for driving a 100W transmission line.

#### 5.7.1 Link Input and Output relative skews

For the skew parameters to be valid for a wide range of operating speeds (10 - 100 Mbits/s) certain parameters must be made relative to edge rates, as the interaction of edge rates and logic threshold have significant impact on the skew. Note that skew is measured relative to the edges crossing a nominal 1.5V logic threshold.

#### tDSI = Fixed skew + k \* (the larger of tLIDSr and tLIDSf)

Where *Fixed Skew* is related to the worst case DSDecoder input skew rejection and internal input path mismatches, and k is found by characterization and related to minimum variation in input threshold and input pad propagation delay.

#### toso = Fixed skew

where: *Fixed Skew* is related to the worst case Link Output PLL jitter and internal output path mismatch.

### 5.7.2 Skew budget

The concept here is that in order to eliminate the risk of DSLink parity errors due to the relative skew between Data and Strobe inputs a system designer must ensure that the sum of 2tbso and the relative skew between Data and Strobe induced by all system interconnect and buffering must be less than tbsbso – tbsl.

Note that an edge rate dependent calculation must be performed for external buffers with variable thresholds in order to calculate worst case tEXTSkew for both Data and Strobe, i.e. :

2tDSO + tEXTSkew < tDSDSO - tDSI

The parameter toso on the left hand side of the expression is multiplied by two to allow for the worst case situation of Data and Strobe undergoing maximum skew in opposite directions.

# 6 Clocking phase locked loops

Two on-chip phase locked loops (PLL) generate all the internal high frequency clocks from a single clock input, simplifying system design and avoiding problems of distributing high speed clocks externally. This chapter details the PLL input specifications, decoupling requirements and speed selections.

There is one PLL for the system clocks and one for the link clocks. Each PLL has six outputs, four quad phase signals and two bi-phase signals. The global system clocks use the four quad phase signals from the system clock PLL. The link clock is one of the bi-phase 100 MHz clocks from the link PLL.

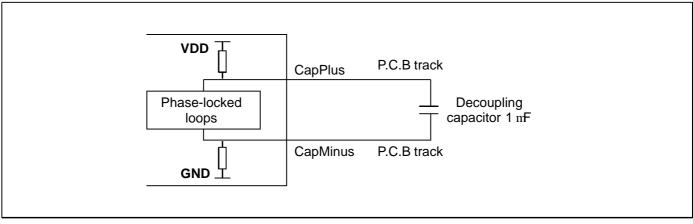

## 6.1 PLL decoupling

The PLL's require a decoupled power supply for satisfactory operation. The decoupling is performed externally by connecting a 1nF ceramic capacitor between the **CapPlus** and **CapMinus** pins on the chip. A surface mounted ceramic capacitor with an ESR (Equivalent Series Resistance) of less than 3 ohms should be used. In order to keep stray inductances low, the total PCB track length should be less than 20 mm, thus the capacitor should be no more than 10 mm from the chip. The connections must not touch power supplies or other noise sources.

Figure 6.1 Recommended PLL decoupling

## 6.2 Clock input

The high frequency internal clocks are derived from the clock frequency supplied by the user. The user supplies the clock frequency for input to the PLL's via the **ClockIn** input. The nominal frequency of this clock for all transputer family components is 5 MHz, regardless of device type, transputer word length or processor cycle time.

A number of transputer devices may be connected to a common clock, or may have individual clocks providing each one meets the specified stability criteria. In a multi-clock system the relative phasing of **ClockIn** clocks is not important, due to the asynchronous nature of the links. Mark/space ratio is unimportant provided the specified limits of **ClockIn** pulse widths are met.

Oscillator stability is important. **ClockIn** must be derived from a crystal oscillator; RC oscillators are not sufficiently stable. **ClockIn** must not be distributed through a long chain of buffers. Clock edges must be monotonic and remain within the specified voltage and time limits.

The timing requirements for **ClockIn** are given in section 6.3.

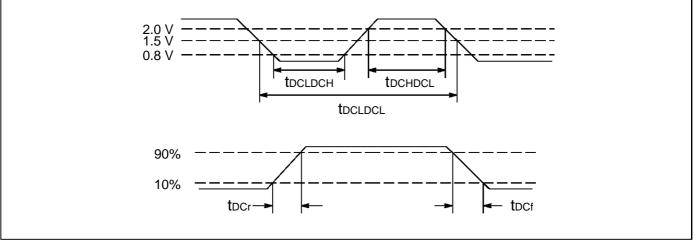

### 6.3 ClockIn timings

| Symbol          | Parameter                | Min | Nom | Max | Units | Notes |

|-----------------|--------------------------|-----|-----|-----|-------|-------|

| <b>t</b> DCLDCH | ClockIn pulse width low  | 40  |     |     | ns    |       |

| <b>tDCHDCL</b>  | ClockIn pulse width high | 40  |     |     | ns    |       |

| <b>tDCLDCL</b>  | Clockin period           |     | 200 |     | ns    | 1, 2  |

| tDCr            | ClockIn rise time        |     |     | 10  | ns    | 3     |

| tDCf            | ClockIn fall time        |     |     | 8   | ns    | 3     |

Table 6.1 **ClockIn** timings

#### Notes

- 1 Measured between corresponding points on consecutive falling edges.

- 2 This value allows the use of 200 ppm crystal oscillators for two devices connected together by a link.

- 3 Clock transitions must be monotonic within the range VIH to VIL (refer to Electrical specifications chapter).

Figure 6.2 ClockIn timing

## 6.4 Processor speed selection

The processor internal clock rate is variable in discrete steps. The clock rate at which the IMS T9000 runs at is determined by the logic levels applied on the three speed select lines **ProcSpeedSelect0-2** as detailed in Table 6.2. Note that the processor cycle time given in Table 6.2 is a nominal value; it can be calculated more accurately using the phase lock loop factor **PLLx** (see section 6.5 below).

| ProcSpeed<br>Select2 | ProcSpeed<br>Select1 | ProcSpeed<br>Select0 | Processor<br>clock speed<br>MHz | Processor<br>cycle time<br>ns | Phase lock<br>loop factor<br>(PLLx) |

|----------------------|----------------------|----------------------|---------------------------------|-------------------------------|-------------------------------------|

| 1                    | 1                    | 0                    | 20                              | 50.0                          | 4.0                                 |

| 1                    | 1                    | 1                    | 25                              | 40.0                          | 5.0                                 |

| 0                    | 0                    | 0                    | 30                              | 33.3                          | 6.0                                 |

Table 6.2 Processor speed selection

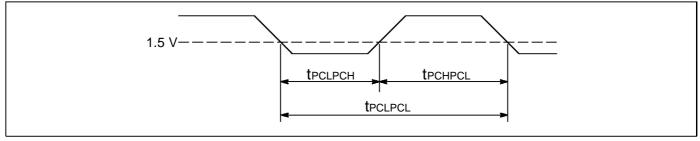

### 6.5 Processor clock output

The processor output clock (supplied on the **ProcClockOut** output) is derived from the internal processor clock, which is in turn derived from **ClockIn**. It provides an output timing signal at the rated clock frequency of the device. Its period is equal to one internal microcode cycle time, and can be derived from the formula:

#### tdcldcl = tdcldcl / PLLx

where: **tPCLPCL** is the **ProcClockOut Period**, **tDCLDCL** is the **ClockIn Period** and **PLLx** is the phase lock loop factor for the relevant speed part.

### 6.6 **ProcClockOut timings**

| Symbol         | Parameter                     | Min  | Nom          | Max  | Units | Notes |

|----------------|-------------------------------|------|--------------|------|-------|-------|

| <b>tPCLPCL</b> | ProcClockOut period           |      | _            |      | ns    | 1     |

| <b>tPCHPCL</b> | ProcClockOut pulse width high |      | tPCLPCL<br>2 |      | ns    |       |

| DtPCHPCL       | ProcClockOut pulse width high | -2.5 | -            | +2.5 | ns    |       |

| <b>tPCLPCH</b> | ProcClockOut pulse width low  |      | tPCLPCL<br>2 |      | ns    |       |

| DtPCLPCH       | ProcClockOut pulse width low  | -2.5 | _            | +2.5 | ns    |       |

#### Notes

### Table 6.3 ProcClockOut timings

1 Nominal value dependent upon processor speed selection (see section 6.5)

Figure 6.3 **ProcClockOut** timing

## 6.7 ProcClockOut stability

The following table shows how the variation in ProcClockOut period stability varies against Proc-ClockOut period. This parameter must be taken into account when calculating absolute PMI timing characteristics for specific PMI configurations. Refer to section 3.1.2 *AC timing characteristics* to see how this value is used.

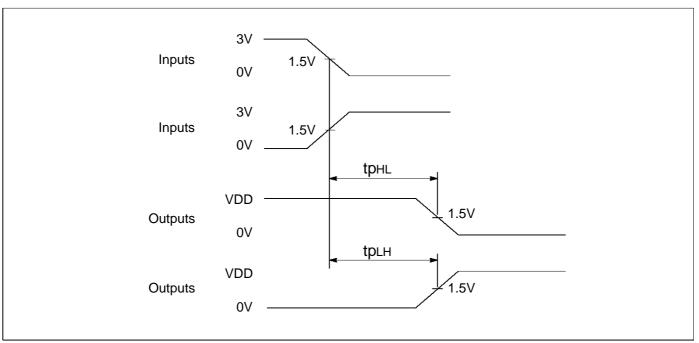

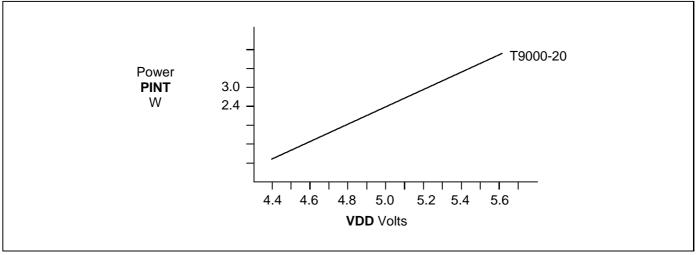

| Symbol         | Parameter | Units |    |    |      | Note |