# THE T9000 TRANSPUTER HARDWARE REFERENCE MANUAL

1st edition 1993

INMOS is a member of the SGS-THOMSON Microelectronics Group

# **INMOS transputer databook series**

Transputer Databook Military and Space Transputer Databook Transputer Development and *i***q** Systems Databook Transputer Applications Notebook: Architecture and Software Transputer Applications Notebook: Systems and Performance T9000 Transputer Hardware Reference Manual T9000 Transputer Instruction Set Manual T9000 Development Tools – Preliminary Datasheets

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate; however, no responsibility is assumed for its use, nor for any infringement of patents or other rights of third parties resulting from its use. No licence is granted under any patents, trademarks or other rights of INMOS.

**INMOS Limited 1993**

, inmos<sup>•</sup>, IMS, occam and DS-Link are trademarks of INMOS Limited.

SGS-THOMSON is a registered trademark of the SGS-THOMSON Microelectronics Group.

INMOS Limited is a member of the SGS-THOMSON Microelectronics Group.

INMOS document number: 72 TRN 238 01

ORDER CODE:DBT9000RMST/1

Printed in Italy

| $\sim$                 |      |      |           |        |           |

|------------------------|------|------|-----------|--------|-----------|

| (``                    | ntar | atc. | $\sim 10$ | \r\/I  | <b>()</b> |

| $\mathbf{U}\mathbf{U}$ | nter | 11.5 | UVE       | 51 V I | E VV      |

|                        |      |      |           |        |           |

| Part 1: IMS | T9000 Product Family Overview                       |     | 1   |

|-------------|-----------------------------------------------------|-----|-----|

| 1           | Introducing the IMS T9000                           | 3   |     |

| 2           | The IMS T9000 transputer                            | 7   |     |

| 3           | Simplicity of system design                         | 17  |     |

| 4           | Protection and error handling                       | 21  |     |

| 5           | Support for multiprocessing                         | 23  |     |

| 6           | Communication links                                 | 31  |     |

| 7           | Network communications                              | 39  |     |

| 8           | Other communications devices                        | 47  |     |

| 9           | Software and systems                                | 49  |     |

| Part 2: IMS | 5 T9000 Transputer Preliminary Data                 |     | 55  |

| 1           | IMS T9000 introduction                              | 59  |     |

| 2           | Pin designations                                    | 63  |     |

| 3           | Central processing unit                             | 65  |     |

| 4           | Floating point unit                                 | 77  |     |

| 5           | Memory management                                   | 79  |     |

| 6           | Instruction set                                     | 85  |     |

| 7           | Performance                                         | 101 |     |

| 8           | Control system                                      | 105 |     |

| 9           | Instruction and data cache                          | 129 |     |

| 10          | Programmable memory interface                       | 149 |     |

| 11          | Communications                                      | 187 |     |

| 12          | Events                                              | 205 |     |

| 13          | Data/Strobe links                                   | 209 |     |

| 14          | Clocking phase locked loops                         | 221 |     |

| 15          | Configuration register reference guide              | 225 |     |

| 16          | Package specifications                              | 233 |     |

| 17          | Thermal management                                  | 235 |     |

| 18          | Electrical specifications                           | 239 |     |

| Part 3: Con | nmunications Support Devices                        |     | 243 |

| 1           | IMS C100 system protocol converter preliminary data | 245 |     |

| 2           | IMS C104 packet routing switch product preview      | 305 |     |

| 3           | IMS C101 parallel DS-Link adaptor product preview   | 307 |     |

| Appendice   | S                                                   |     | 309 |

| А           | IMS T9000 special values                            | 309 |     |

| В           | IMS T9000 quick reference guide                     |     |     |

# Contents

| P    | refac  | e          | •••••                                   | xvii  |

|------|--------|------------|-----------------------------------------|-------|

| N    | otatio | on and r   | nomenclature                            | xviii |

|      | Signi  | ificanco   |                                         | xviii |

|      | 0      |            |                                         | xviii |

|      |        |            |                                         |       |

|      |        | • •        | n conventions                           | xviii |

|      |        |            | ons                                     | xviii |

|      |        |            | ••••••••••••••••••••••••••••••••••••••• | xix   |

|      | Tran   | sputer pro | oduct numbers                           | XX    |

| Part | 1: 1   | MS T90     | 000 Product Family Overview             | 1     |

| 1    | Intro  | oducing    | g the IMS T9000                         | 3     |

|      | 1.1    | Perform    | nance                                   | 3     |

|      | 1.2    | Multipro   | ocessing                                | 3     |

|      | 1.3    |            | unications support devices              | 4     |

|      | 1.4    |            | 'e                                      | 4     |

|      | 1.5    |            | tions                                   | 5     |

| 2    | The    | IMS T9     | 000 transputer                          | 7     |

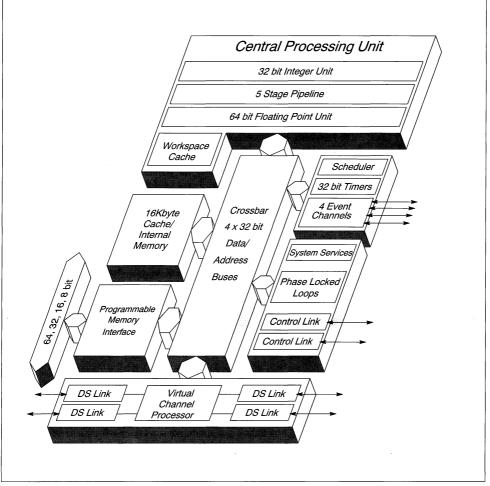

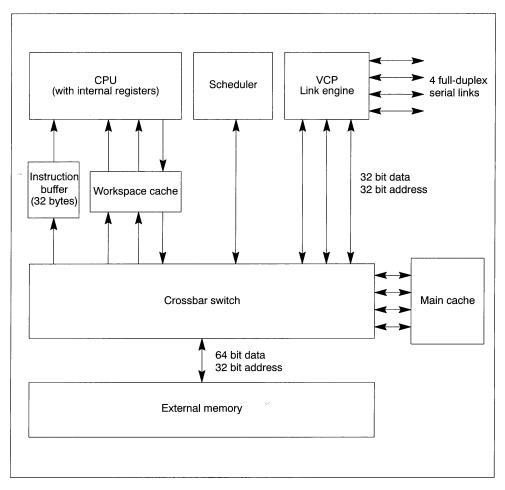

|      | 2.1    | Overvie    | 9W                                      | 7     |

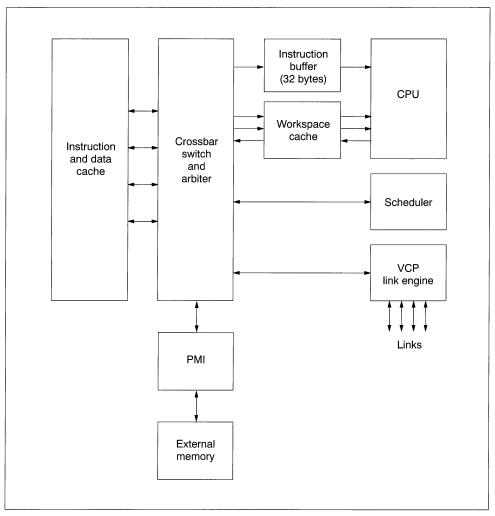

|      |        | 2.1.1      | Processor                               | 7     |

|      |        | 2.1.2      | Hierarchical memory system              | 8     |

|      |        | 2.1.3      | Communications system                   | 8     |

|      |        | 2.1.4      | Multiple internal buses                 | 8     |

|      |        | 2.1.5      | Control system                          | 9     |

|      |        | 2.1.6      |                                         | 9     |

|      | 2.2    |            | nsputer architecture                    | 9     |

|      | 2.3    |            | t for concurrent processes              | 10    |

|      | 2.4    | Pipeline   | ed, superscalar implementation          | 10    |

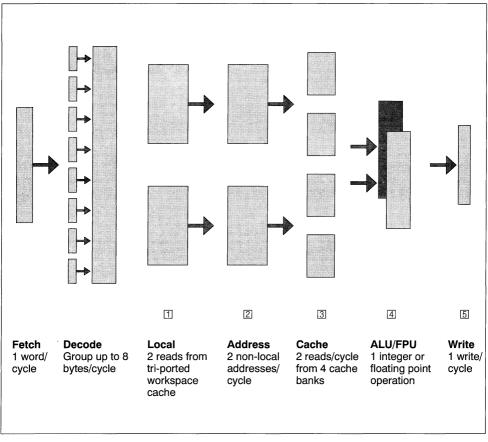

|      |        | 2.4.1      | The pipeline                            | 11    |

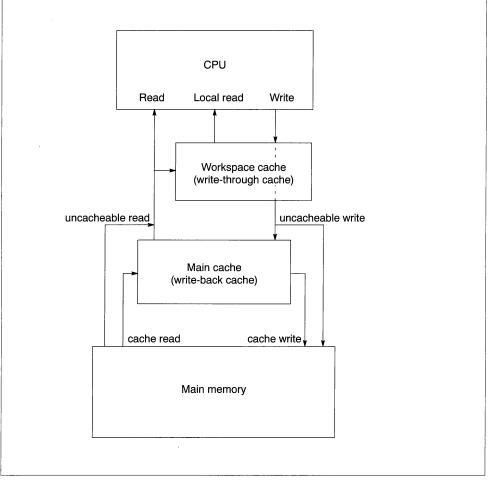

|      | 2.5    |            | hical memory system                     | 12    |

|      |        | 2.5.1      | Main cache                              | 13    |

|      |        |            | Cache operation                         | 14    |

|      |        | 050        | Use as on-chip RAM                      | 15    |

|      |        | 2.5.2      | Workspace cache                         | 15    |

| 3    |        |            | of system design                        | 17    |

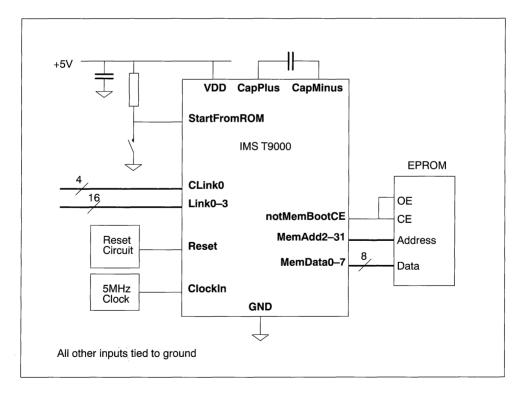

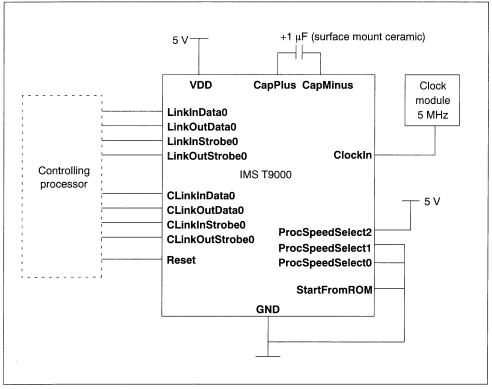

|      | 3.1    |            | 5 MHz clock input                       | 17    |

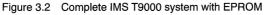

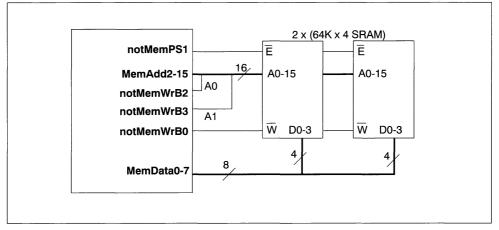

|      | 3.2    | Progran    | nmable memory interface                 | 17    |

|      | 3.3    | Control    | links and configuration                 | 17    |

|      | 3.4    | Loading    | and bootstrapping                       | 18    |

|      | 3.5    | Example    | es                                      | 19    |

| 4 | Prot       | ection a          | nd error handling                                                                | 21             |

|---|------------|-------------------|----------------------------------------------------------------------------------|----------------|

|   | 4.1<br>4.2 |                   | ndling<br>d mode<br>Protected mode processes                                     | 21<br>21<br>21 |

|   |            | 4.2.2<br>4.2.3    | Executing illegal instructions                                                   | 21<br>22       |

| 5 | Sup        | oort for          | multiprocessing                                                                  | 23             |

|   | 5.1        | The trans         | Fast interrupt response and process switch           sputer model of concurrency | 23<br>23       |

|   |            | 5.1.1<br>5.1.2    | Processes and channels<br>Program structure<br>Example                           | 23<br>23<br>24 |

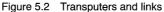

|   | 5.2        |                   | Multiprocessor programs                                                          | 25<br>26       |

|   | 5.3        | 5.2.1<br>Hardwar  | Shared memory                                                                    | 26<br>27       |

|   | 5.4        | Interrupts        | s, events and timers                                                             | 28             |

|   | 5.5        | Shared r          | esources                                                                         | 28             |

| 6 | Com        | municat           | tion links                                                                       | 31             |

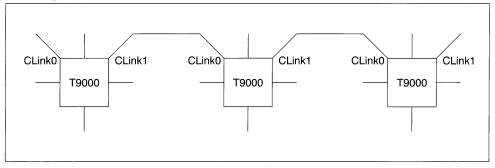

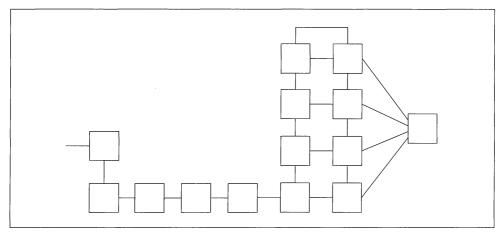

|   | 6.1        | Using lin         | ks between transputers                                                           | 31             |

|   | 6.2        | Advantag          | ges of using links                                                               | 31             |

|   |            | 6.2.1             | Efficiency                                                                       | 31             |

|   |            | 6.2.2             | Simplicity                                                                       | 31<br>32       |

|   | 6.3        | 6.2.3<br>IMS T900 | Hardware independence                                                            | 32<br>32       |

|   |            | 6.3.1             | Virtual channels                                                                 | 33<br>33       |

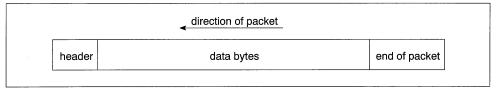

|   |            |                   | Sending packets                                                                  | 34<br>34       |

|   |            |                   | The virtual channel processor                                                    | 34             |

|   |            | 6.3.2             | Implementation                                                                   | 35<br>35       |

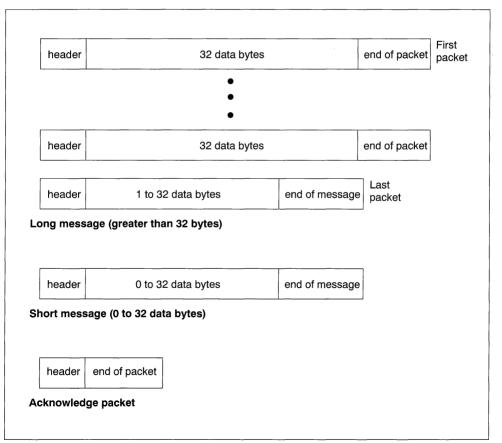

|   |            | 0.0.2             | Packet level protocol                                                            | 36             |

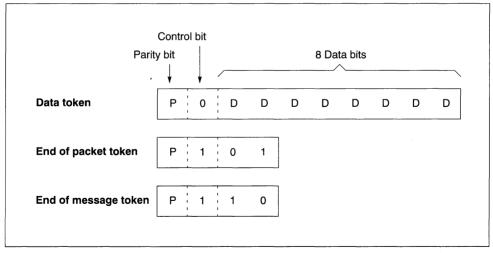

|   |            |                   | Token level protocol                                                             | 36             |

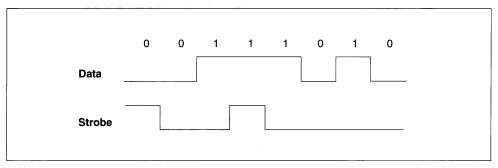

|   |            |                   | Bit level protocol                                                               | 37             |

| 7 | Netw       | ork con           | nmunications                                                                     | 39             |

|   | 7.1        | Message           | routing                                                                          | 39             |

|   |            |                   | Advantages for the programmer                                                    | 39             |

|   |            |                   | Routers                                                                          | 39             |

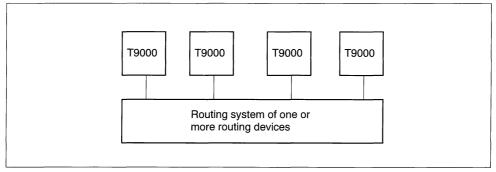

|   |            |                   | Separating routers and processors                                                | 40<br>40       |

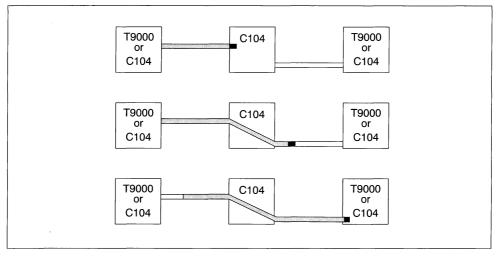

|   | 7.2        | The IMS           | C104                                                                             | 40             |

|   |            |                   | Wormhole routing                                                                 | 40             |

|   |            |                   | Minimizing routing delays                                                        | 41             |

|   |            |                   | Control links                                                                    | 42             |

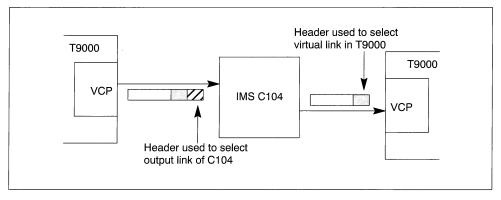

|   |      | 7.2.1     | Using IMS T9000s with IMS C104s    | 42<br>42 |

|---|------|-----------|------------------------------------|----------|

|   |      | <b>–</b>  | Routing control channels           | 44       |

|   | 7.3  |           | algorithms                         | 44       |

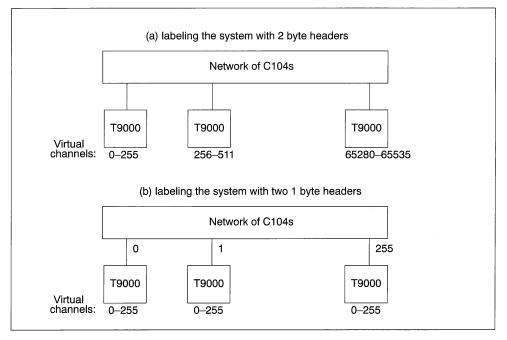

|   |      | 7.3.1     | Labeling networks                  | 45       |

|   |      | 7.3.2     | Avoiding deadlock                  | 46       |

| 8 | Othe | er comn   | nunications devices                | 47       |

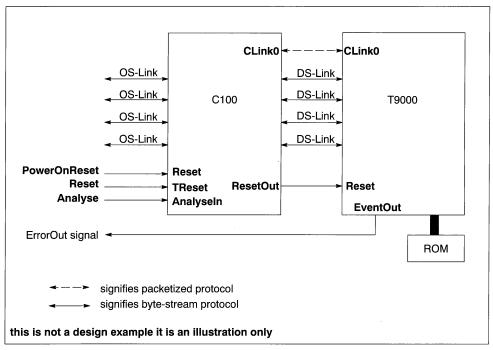

|   | 8.1  | Mixing t  | ransputer types: the IMS C100      | 47       |

|   | 8.2  | Interfaci | ng to peripherals and host systems | 47       |

| 9 | Soft | ware an   | id systems                         | 49       |

|   | 9.1  | Develop   | ment software                      | 49       |

|   |      | 9.1.1     | Configuration tools                | 49       |

|   |      |           | Hardware description               | 50       |

|   |      |           | Software description               | 50       |

|   |      |           | Mapping software to hardware       | 50       |

|   |      |           | Configuration languages            | 50       |

|   |      |           | Types of networks                  | 50       |

|   |      | 9.1.2     | Initializing and loading a network | 51       |

|   |      |           | Levels of initialization           | 51       |

|   |      |           | Booting a system from link         | 51       |

|   |      |           | Booting a system from ROM          | 51       |

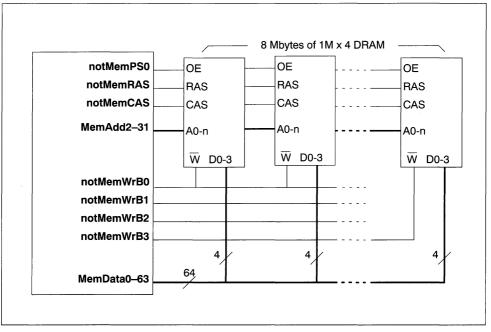

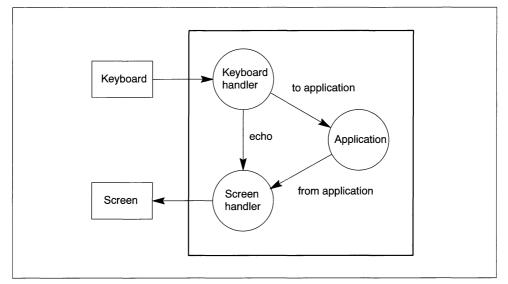

|   |      | 9.1.3     | Host servers                       | 51       |

|   |      | 9.1.4     | Debugging                          | 52       |

|   | 9.2  | IMS T90   | 000 systems products               | 53       |

| Part | 2: IN | IS T9000 Transputer Preliminary Data                                                                                                | 55                               |

|------|-------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1    | IMS   | T9000 introduction                                                                                                                  | 59                               |

| 2    | Pin   | designations                                                                                                                        | 63                               |

|      |       | Supplies<br>Phase locked loops<br>Programmable memory interface<br>Control system<br>Communication links<br>Events<br>Miscellaneous | 63<br>63<br>64<br>64<br>64<br>64 |

| 3    | Cen   | tral processing unit                                                                                                                | 65                               |

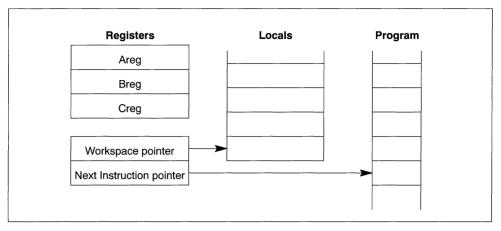

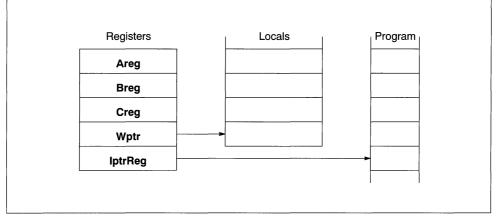

|      | 3.1   | Registers                                                                                                                           | 65                               |

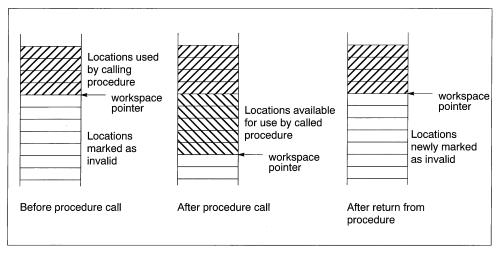

|      | 3.2   | Workspace cache                                                                                                                     | 66                               |

|      | 0.2   | Cache operation                                                                                                                     | 66                               |

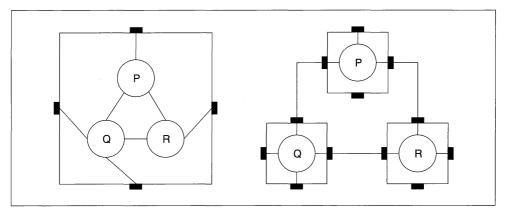

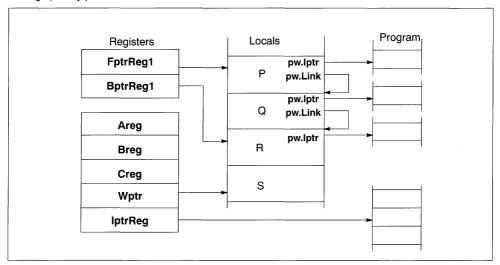

|      | 3.3   | Processes and concurrency                                                                                                           | 67                               |

|      | 3.4   | Priority                                                                                                                            | 68                               |

|      | 3.5   | L-processes: local error handling and debugging                                                                                     | 69                               |

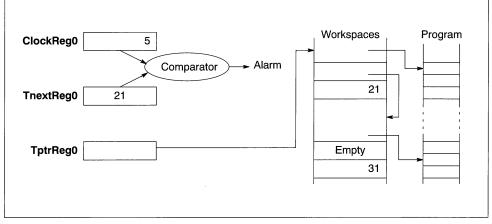

|      | 3.6   | Timers                                                                                                                              | 71                               |

|      | 3.7   | Block move                                                                                                                          | 72                               |

|      | 3.8   | Semaphores                                                                                                                          | 72                               |

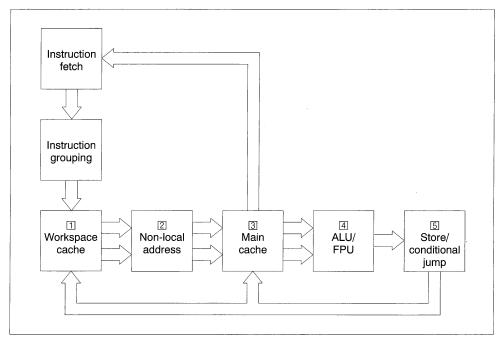

|      | 3.9   | Pipeline                                                                                                                            | 72                               |

|      |       | 3.9.1 Grouping of instructions                                                                                                      | 73                               |

|      | 3.10  | CPU configuration registers                                                                                                         | 75                               |

|      |       | Reason                                                                                                                              | 75                               |

|      |       | EmiBadAddress                                                                                                                       | 75                               |

|      |       | Initiallptr and InitialWptr                                                                                                         | 75                               |

| 4    | Floa  | ting point unit                                                                                                                     | 77                               |

|      | 4.1   | Floating point registers                                                                                                            | 77                               |

|      |       | 4.1.1 Floating-point stack                                                                                                          | 77                               |

|      |       | 4.1.2 Floating-point status register                                                                                                | 77                               |

|      | 4.2   | Floating point instructions                                                                                                         | 78                               |

| 5    | Mem   | ory management                                                                                                                      | 79                               |

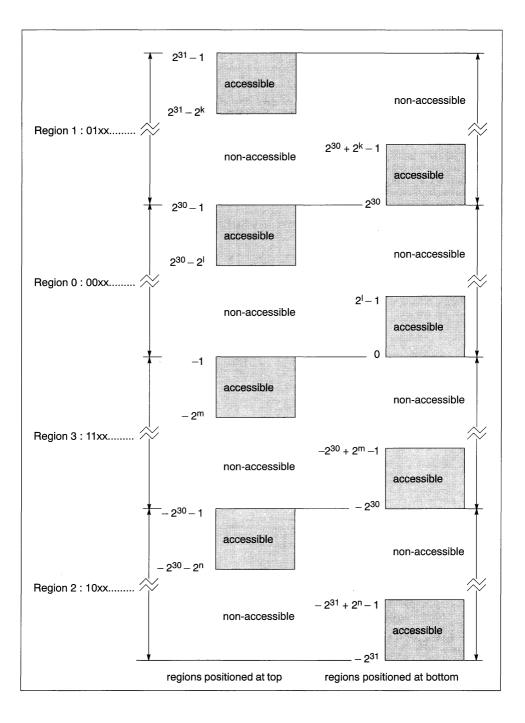

|      | 5.1   | Protection, stack extension, and logical to physical address translation                                                            | 79                               |

|      |       | 5.1.1 Protection                                                                                                                    | 79                               |

|      |       | 5.1.2 Stack extension                                                                                                               | 79<br>70                         |

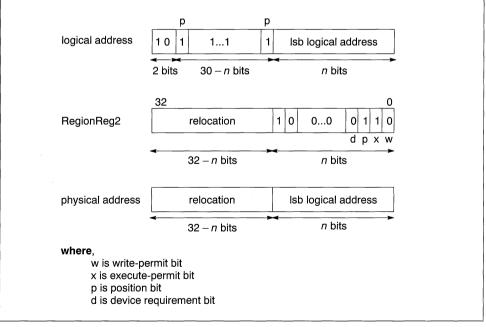

|      | 5.2   | 5.1.3 Logical to physical address translation                                                                                       | 79<br>80                         |

|      | 5.2   | 5.2.1 Region descriptors                                                                                                            | 82                               |

|      |       | 5.2.2 Non-overlapping regions                                                                                                       | 82                               |

|      | 5.3   | P-process machine registers                                                                                                         | 83                               |

|      | 5.4   | Debugging                                                                                                                           | 83                               |

| 6 | Instr | uction a       | set                                                  | 85         |

|---|-------|----------------|------------------------------------------------------|------------|

|   | 6.1   | Efficienc      | y of encoding                                        | 85         |

|   | 6.2   | Interacti      | on of the processor pipeline and the instruction set | 85         |

|   | 6.3   |                | on characteristics                                   | 88         |

|   | 6.4   |                | on set tables                                        | 90         |

|   | 0     | 6.4.1          | Primary instructions                                 | 90         |

|   |       | 6.4.2          | Secondary instructions                               | 91         |

|   |       | 01.112         | Sequential instructions                              | 91         |

|   |       |                | Communication instructions                           | 95         |

|   |       |                | Process scheduling instructions                      | 97         |

|   |       |                | Initialization and configuration instructions        | 98         |

|   |       |                | Cache operation instructions                         | 98         |

|   |       |                | Floating point instructions                          | 99         |

| 7 | Perf  | ormanc         | e                                                    | 101        |

|   |       |                |                                                      |            |

|   | 7.1   |                | operations                                           | 101        |

|   | 7.2   | -              | point operations                                     | 103        |

|   | 7.3   | Predefin       | es                                                   | 104        |

| 0 | Com   |                | to an                                                | 105        |

| 8 |       |                | tem                                                  | 105        |

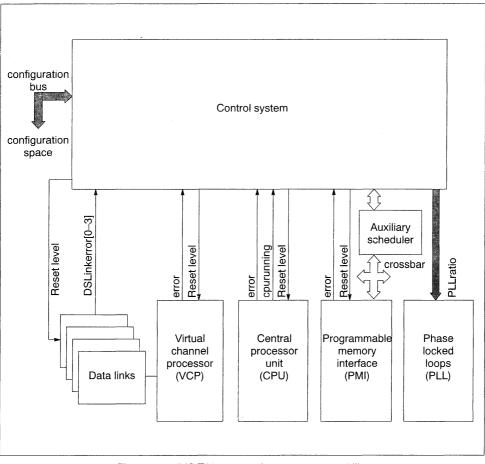

|   | 8.1   | Overview       | Ν                                                    | 105        |

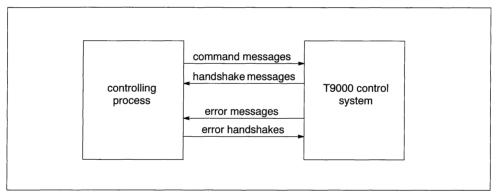

|   |       | 8.1.1          | Tiers of handshaking                                 | 106        |

|   |       | 8.1.2          | Autonomous operation                                 | 107        |

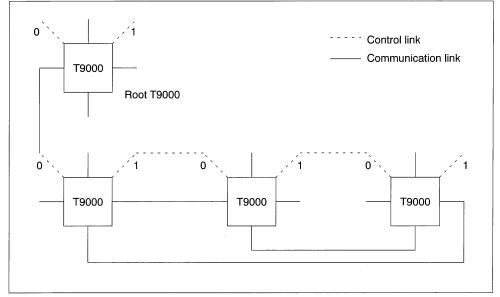

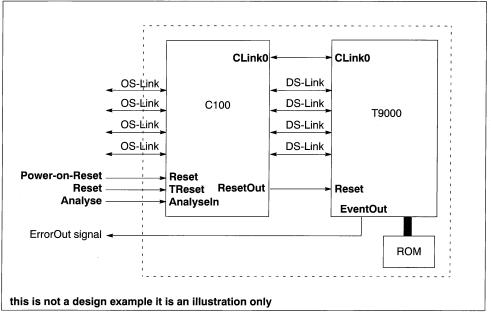

|   | 8.2   |                | system interconnections                              | 108        |

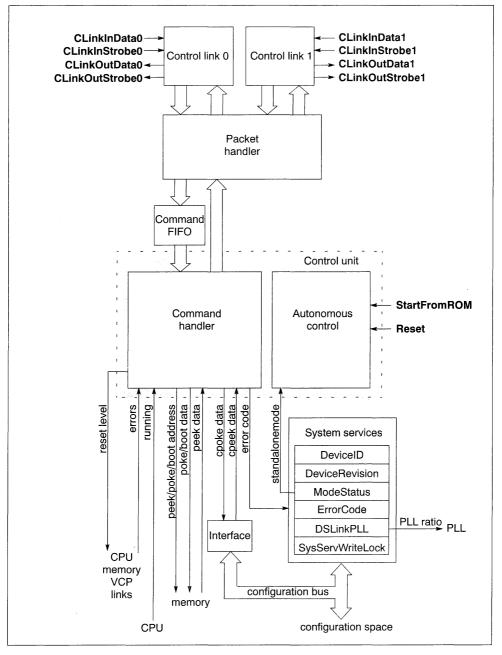

|   | 8.3   |                | system functional description                        | 109        |

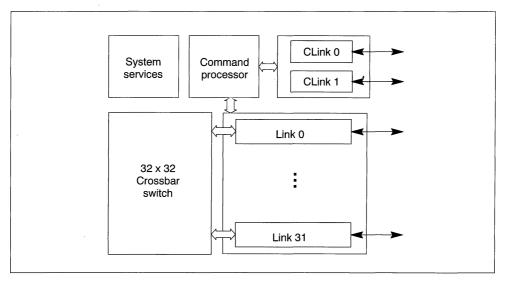

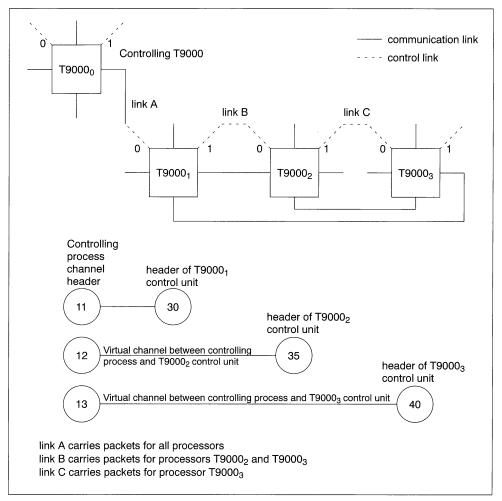

|   |       | 8.3.1          | Control links                                        | 110        |

|   |       | 8.3.2          |                                                      | 111        |

|   |       | 8.3.3          | Control unit                                         | 112<br>112 |

|   |       |                | Autonomous control                                   | 112        |

|   |       | 8.3.4          | System services                                      | 113        |

|   |       |                | DeviceID                                             | 113        |

|   |       |                | DeviceRevision                                       | 113        |

|   |       |                | ModeStatus                                           | 113        |

|   |       |                | ErrorCode                                            | 114        |

|   |       |                | DSLinkPLL                                            | 114        |

|   | • •   | <b>•</b> • • • | SysServWriteLock                                     | 114        |

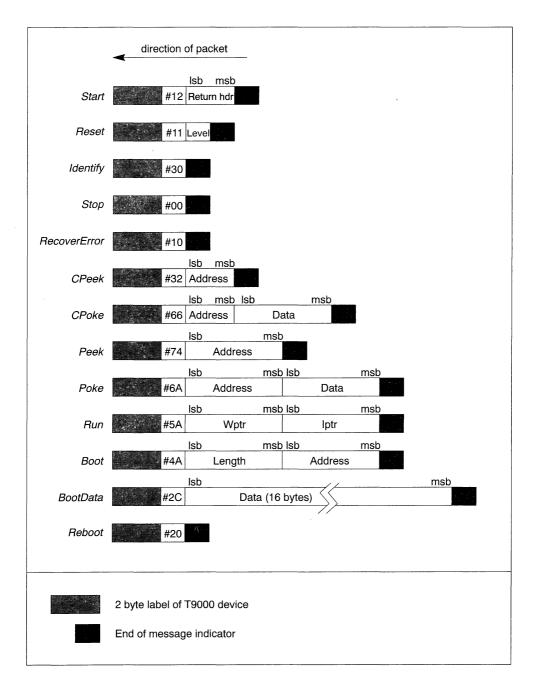

|   | 8.4   | Control        | commands                                             | 115        |

|   |       |                | Start                                                | 115        |

|   |       |                |                                                      | 115        |

|   |       |                | IdentifyStop                                         | 115<br>115 |

|   |       |                | RecoverError                                         | 116        |

|   |       |                | CPeek                                                | 116        |

|   |       |                | CPoke                                                | 116        |

|   |       |                | Peek                                                 | 116        |

|   |       |                | Poke                                                 | 116        |

|   |       |                | Boot                                                 | 116        |

|   |       |                | BootData                                             | 116        |

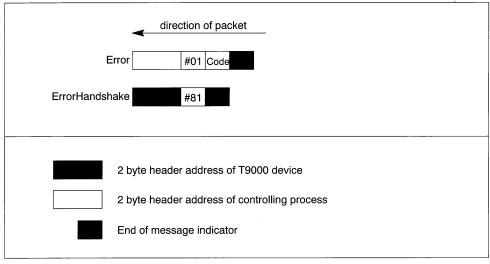

|   |       |               | Run<br>Reboot<br>Error message                     | 116<br>116<br>119 |

|---|-------|---------------|----------------------------------------------------|-------------------|

|   |       | 8.4.1         | IMS T9000 gross state and validity of commands     | 119               |

|   | 8.5   | Errors .      | ·····                                              | 121               |

|   |       | 8.5.1         | Recording of Errors                                | 121               |

|   |       | 8.5.2         | Stand alone mode errors                            | 122               |

|   |       | 8.5.3         | Errors on control links                            | 122               |

|   |       | 8.5.4         | Post-mortem debugging of IMS T9000 systems         | 123               |

|   |       |               | State delivered to the boot program                | 123               |

|   | 8.6   | Configura     | ation                                              | 124               |

|   |       | 8.6.1         | Booting from link                                  | 124               |

|   |       | 8.6.2         | Boot from ROM then link                            | 125               |

|   | 8.7   | Reset lev     | rels                                               | 126               |

|   |       | 8.7.1         | Level 0 – hardware reset                           | 126               |

|   |       | 8.7.2         | Level 1 – labelled control network                 | 126               |

|   |       | 8.7.3         | Level 2 – configured network                       | 127               |

|   |       | 8.7.4         | Level 3 – booted network                           | 127               |

|   |       | 8.7.5         | Loading code                                       | 127               |

|   |       | 8.7.6         | Levels of reset effect                             | 127               |

|   |       |               |                                                    |                   |

| 9 | Instr | uction a      | nd data cache                                      | 129               |

|   | 9.1   | Cache ov      | rerview                                            | 129               |

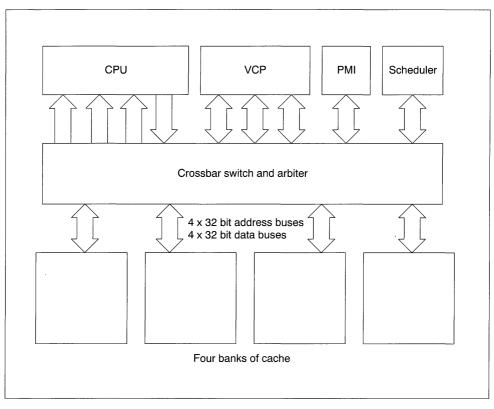

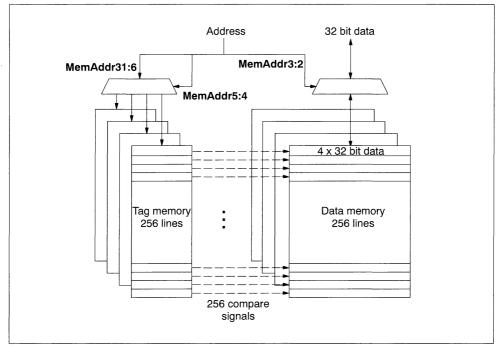

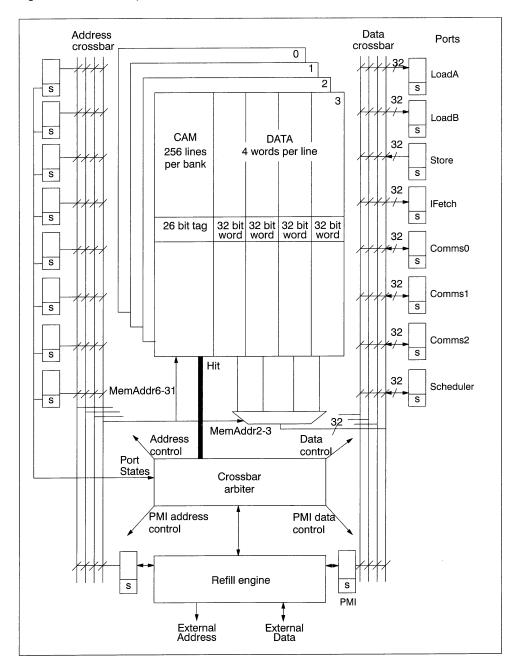

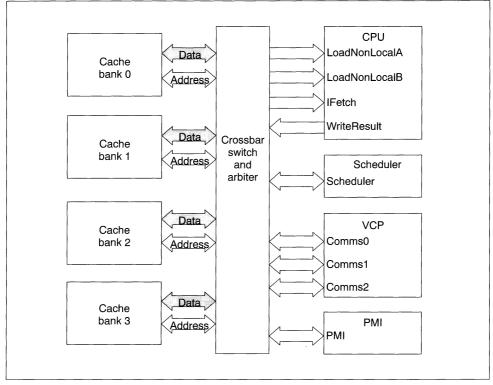

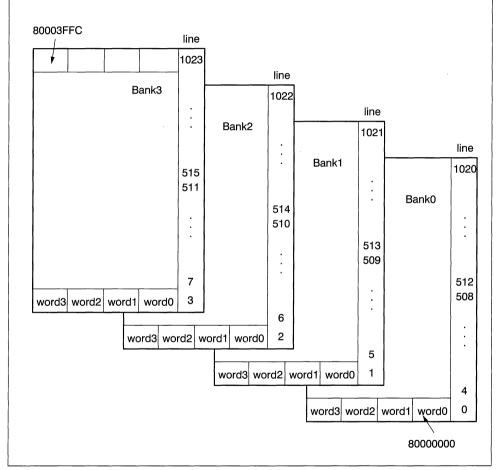

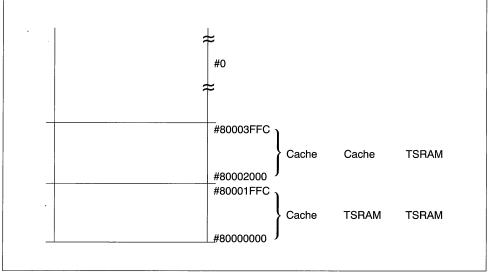

|   |       | 9.1.1         | Cache organization                                 | 130               |

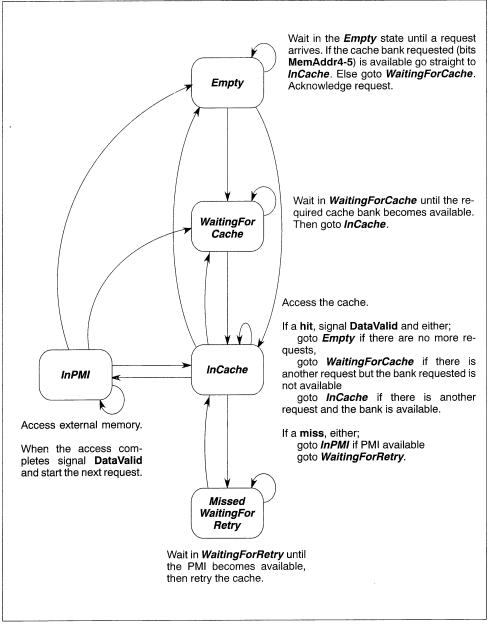

|   | 9.2   | Cache fu      | nctional description                               | 133               |

|   |       | 9.2.1         | Port crossbar switch and arbiter                   | 134               |

|   |       | 9.2.2         | Refill engine                                      | 135               |

|   |       | 9.2.3         | Replace pointer                                    | 135               |

|   | 9.3   | Cache op      | peration                                           | 136               |

|   |       | 9.3.1         | Cache request                                      | 136               |

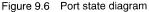

|   |       | 9.3.2         | Arbitration                                        | 138               |

|   |       |               | Queueing to ensure fairness                        | 138               |

|   |       | 9.3.3         | Cacheable and non-cacheable accesses               | 140               |

|   |       |               | Non-cacheable accesses                             | 140               |

|   |       |               | Cacheable accesses                                 | 140               |

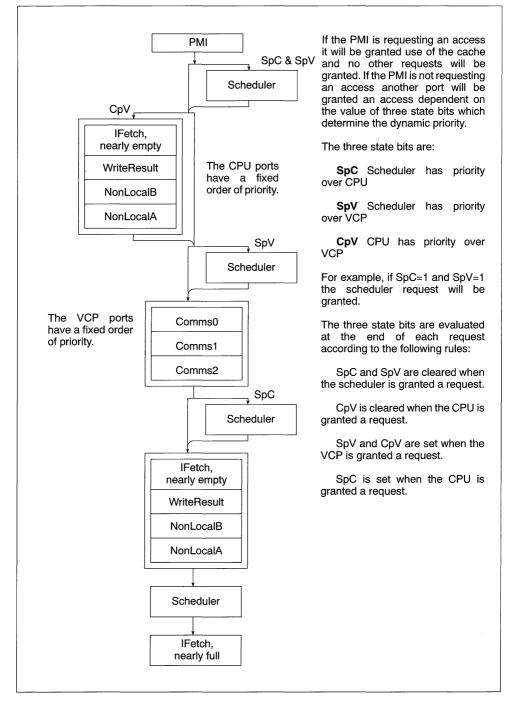

|   |       | 9.3.4         | Cache refill cycles                                | 141               |

|   |       |               | Cache refills from 8/16 bit ports                  | 142               |

|   |       |               | Write-back cycles                                  | 143               |

|   |       |               | DMA and cache-refill cycles                        | 143               |

|   | 9.4   | Cache ins     | structions                                         | 144               |

|   |       | 9.4.1         | Flushing data from the cache                       | 145               |

|   |       |               | Flush dirty cache address (fdca)                   | 145               |

|   |       |               | Flush dirty cache line (fdcl)                      | 145               |

|   |       | 9.4.2         | Invalidate cache block                             | 145               |

|   |       |               | Invalidate cache address (ica)                     | 145               |

|   |       |               | Invalidate cache line (icl)                        | 145               |

|   | 0.5   | 9.4.3         | Cache instruction performance                      | 145               |

|   | 9.5   |               | nfiguration registers                              | 146               |

|   |       | 9.5.1         | RamSize and DoRamSize registers                    | 146               |

|   |       | 9.5.2         | RamLineNumber, RamAddress and DoAllocate registers | 147               |

|   | 9.6   | Initializatio | on of the cache                                    | 147               |

|         | 9.6.1        | Reset state                         | 147 |

|---------|--------------|-------------------------------------|-----|

|         | 9.6.2        | Starting the cache                  | 148 |

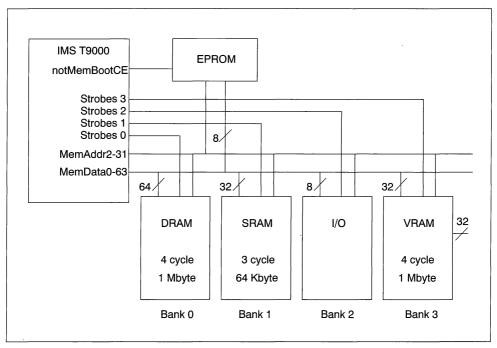

| 10 Prog | rammal       | ble memory interface                | 149 |

| 10.1    | Pin funct    | ions                                | 150 |

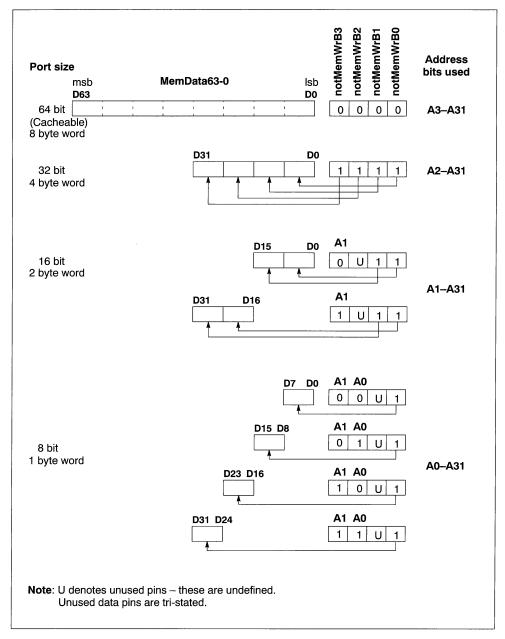

|         | 10.1.1       | MemData0-63                         | 150 |

|         | 10.1.2       | MemAddr2-31                         | 150 |

|         | 10.1.3       | notMemWrB0-3                        | 150 |

|         | 10.1.4       | notMemRAS0-3                        | 150 |

|         | 10.1.5       | notMemCAS0-3                        | 151 |

|         | 10.1.6       | notMemPS0-3                         | 151 |

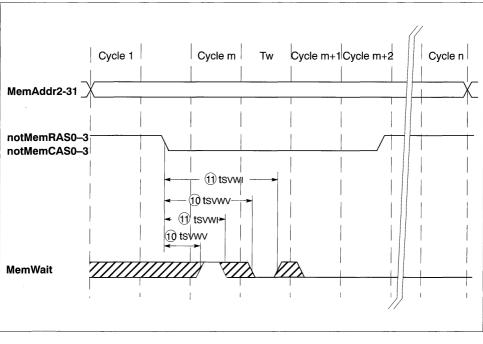

|         | 10.1.7       | MemWait                             | 151 |

|         | 10.1.8       | MemReqIn, MemGranted                | 151 |

|         | 10.1.9       | MemReqOut                           | 151 |

|         | 10.1.10      | notMemBootCE                        | 152 |

|         | 10.1.11      | notMemRf                            | 152 |

|         | 10.1.12      | notMemStrobe                        | 152 |

| 10.2    | External     | bus cycles                          | 152 |

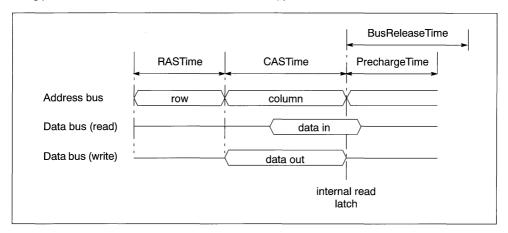

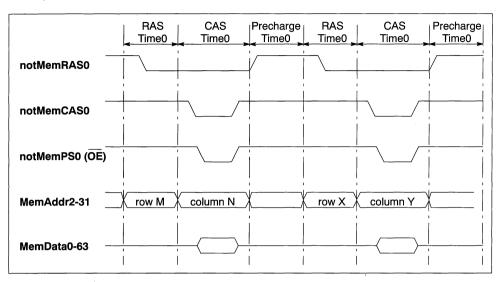

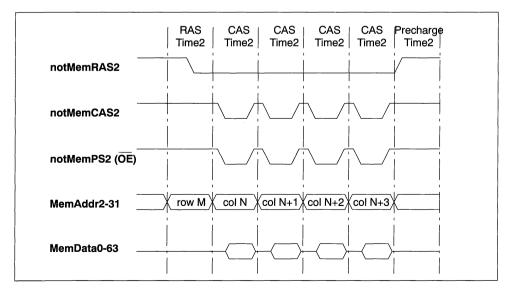

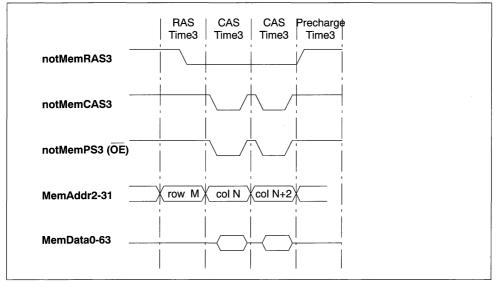

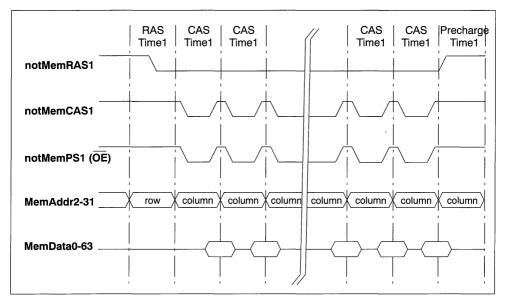

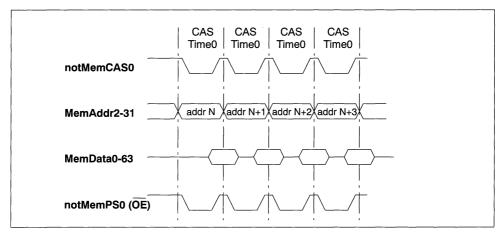

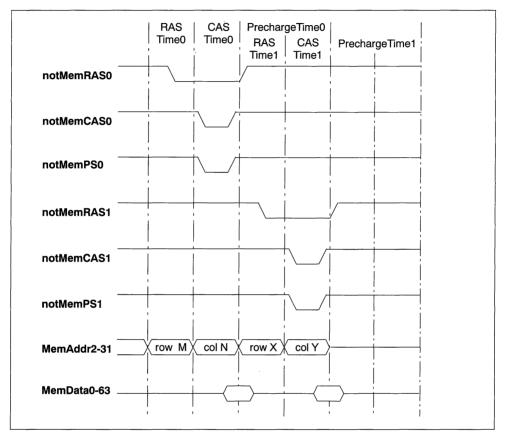

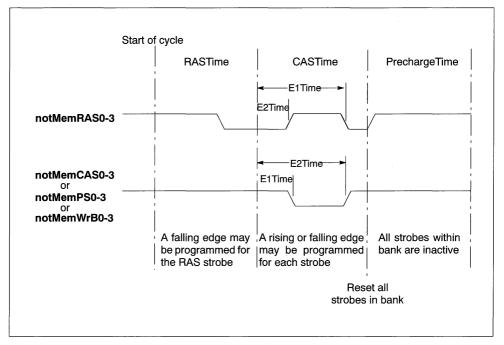

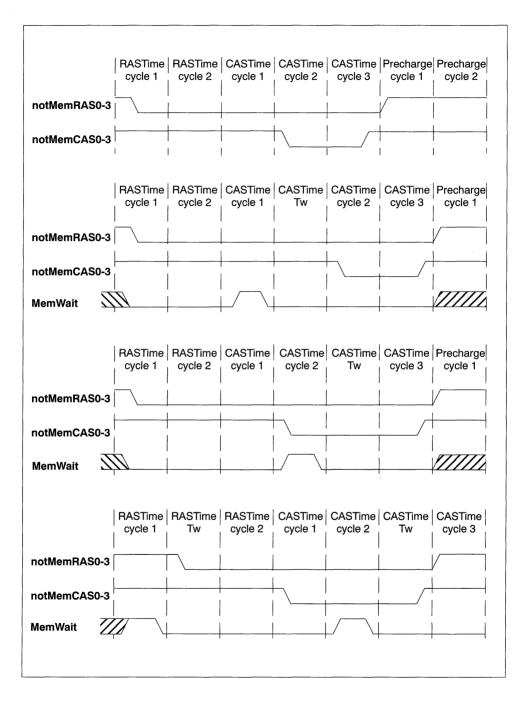

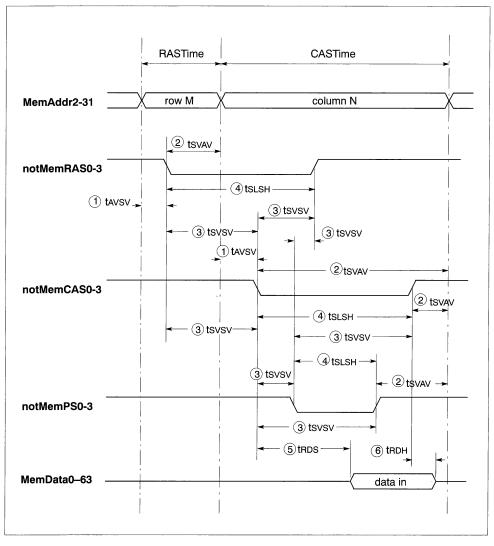

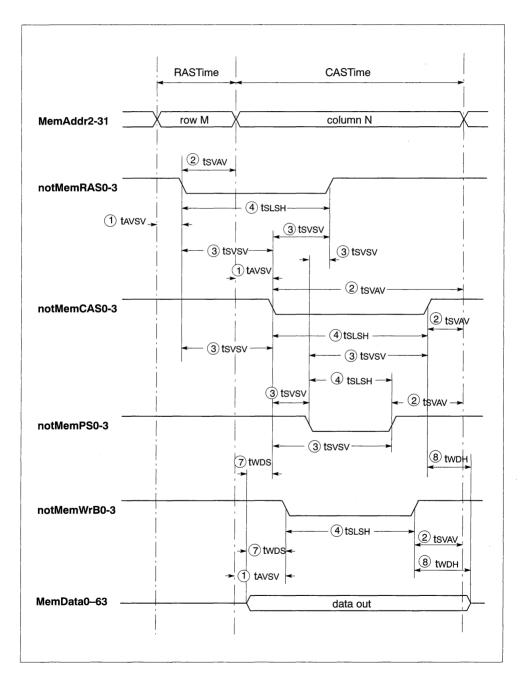

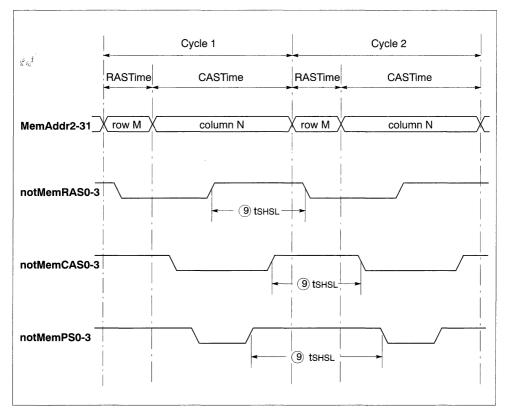

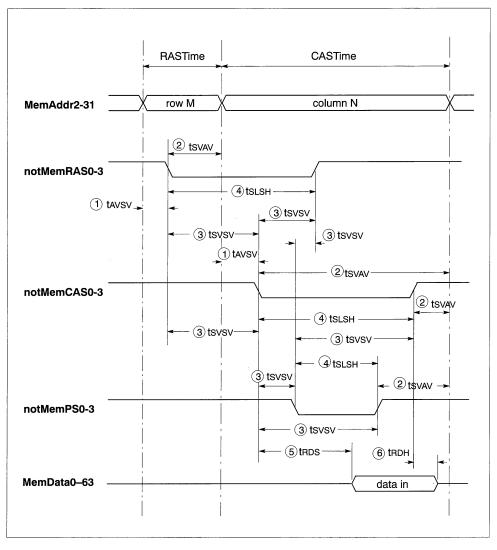

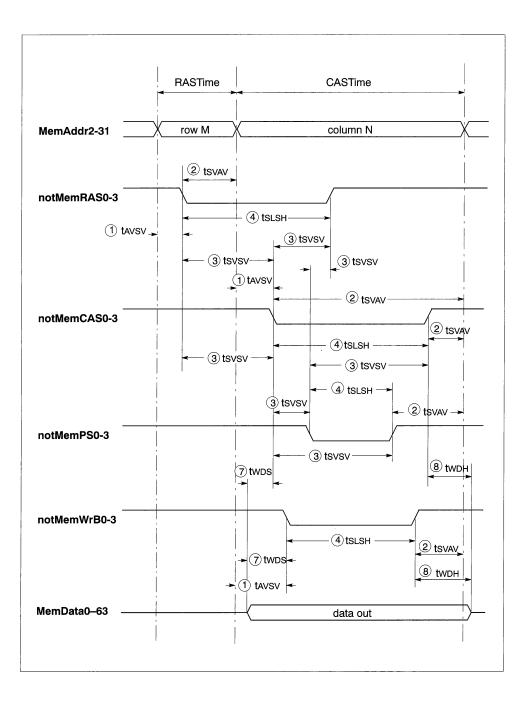

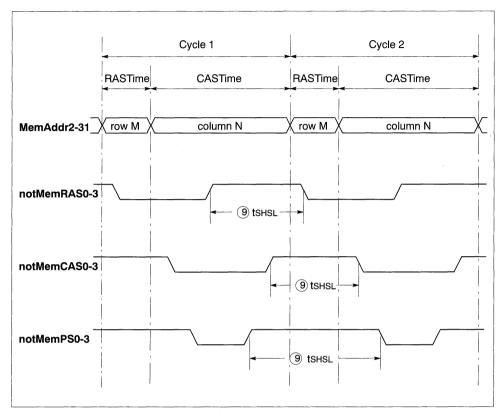

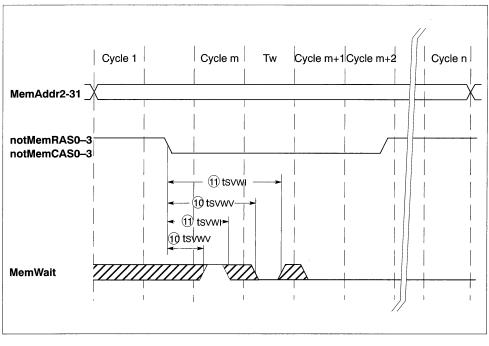

|         | 10.2.1       | External DRAM cycles                | 155 |

|         | 10.2.2       | External non-DRAM cycles            | 158 |

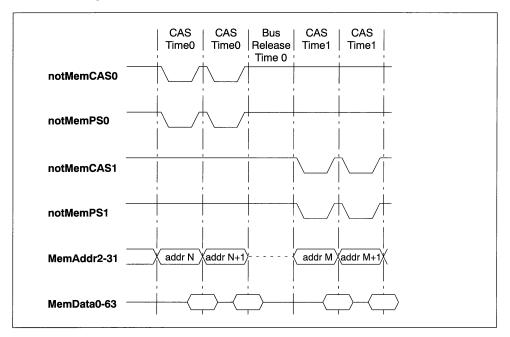

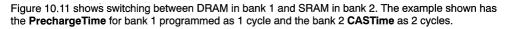

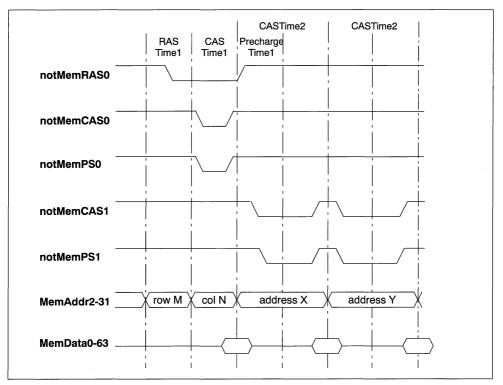

|         | 10.2.3       | Bank switching                      | 159 |

|         | 10.2.4       | Cache refill cycles                 | 162 |

|         |              | Cache refills from 8/16 bit ports   | 162 |

|         |              | Write-back cycles                   | 162 |

|         |              | Wait states and cache-refill cycles | 162 |

|         | 10.2.5       | External DMA                        | 163 |

| 10.3    | PMI conf     | iguration registers                 | 164 |

|         | 10.3.1       | Bank address registers              | 164 |

|         |              | Address registers                   | 164 |

|         |              | Mask registers                      | 165 |

|         |              | RAS bits registers                  | 165 |

|         |              | Format control registers            | 165 |

|         |              | DoPMIConfigured register            | 168 |

|         |              | Error address register              | 168 |

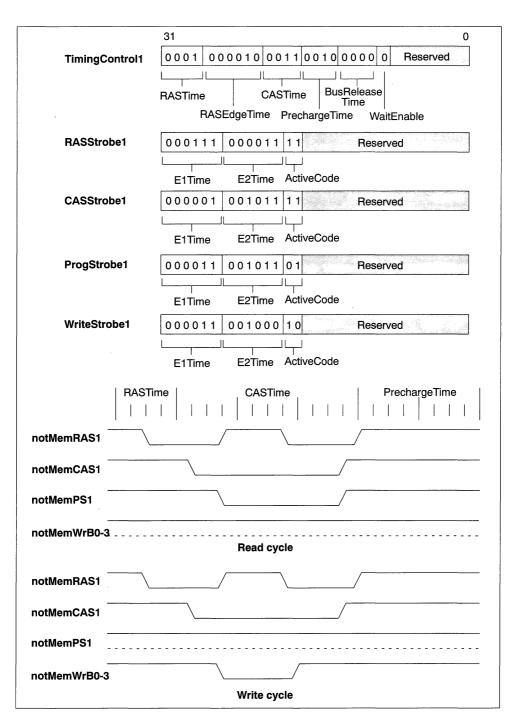

|         | 10.3.2       | Strobe timing registers             | 169 |

|         |              | Strobe registers                    | 169 |

|         |              | Timing control registers            | 171 |

|         |              | Refresh control register            | 174 |

|         |              | Remap boot bank register            | 175 |

|         | 10.3.3       | PMI write lock register             | 175 |

| 10.4    | PMI error    | rs                                  | 176 |

|         | 10.4.1       | Errors detected by the PMI          | 176 |

|         |              | PMI errors signalled by the CPU     | 176 |

|         |              | PMI errors signalled by the PMI     | 176 |

| 10.5    | Initializati | ion of the PMI                      | 177 |

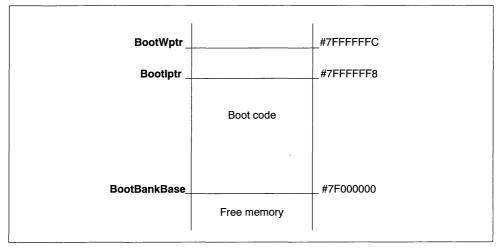

|         | 10.5.1       | Bootspace allocation                | 177 |

|         | 10.5.2       | The boot sequence                   | 177 |

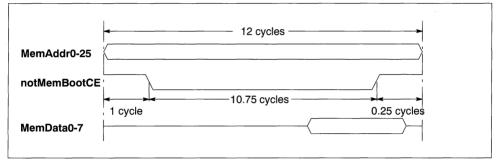

|         | 10.5.3       | Bootspace timing                    | 178 |

| 10.6    | Booting f    | rom ROM                             | 178 |

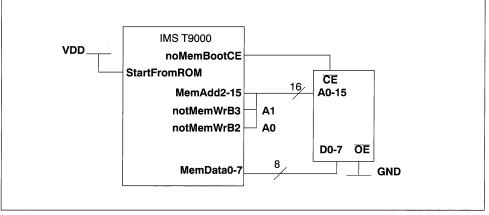

|         | 10.6.1       | Booting from EPROM                  | 178 |

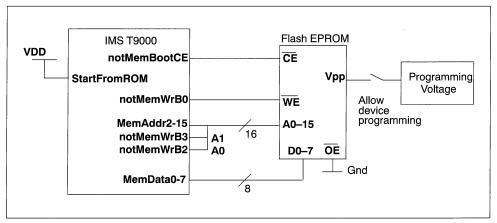

|         | 10.6.2       | Booting from Flash EPROM            | 179 |

| 10.7   | 10.6.3<br>PMLAC  | Re-mapping the boot bank                   | 180<br>181 |

|--------|------------------|--------------------------------------------|------------|

| 10.1   | 1 111 / 10       | Read cycle                                 | 183        |

|        |                  | Write cycle                                |            |

|        |                  | Consecutive cycles                         | 185        |

|        |                  | Memory wait                                | 186        |

| 11 Com | munica           | tions                                      | 187        |

| 11.1   | Overview         | Ν                                          | 187        |

|        | 11.1.1           | Channels                                   | 187        |

|        |                  | Internal channels                          | 187        |

|        | 11 1 0           | External channels                          | 187        |

|        | 11.1.2<br>11.1.3 | Channel addresses                          | 187<br>187 |

|        | 11.1.4           | Efficient variable-length communications   | 188        |

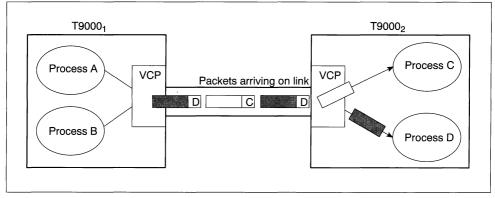

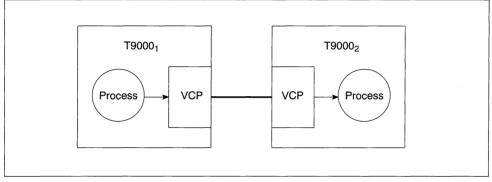

| 11.2   |                  | hannel processor                           | 189        |

|        | 11.2.1           |                                            | 189        |

|        | 11.2.2           | Virtual links                              | 189        |

|        | 11.2.3           | VCP link queues                            | 190        |

|        | 11.2.4           | Virtual link control blocks                | 191        |

|        |                  | vl.HeaderCtrl word                         | 191        |

| 11.3   | Operatio         | vl.DataQueueLink and vl.AckQueueLink words | 192        |

| 11.5   | •                |                                            | 193        |

|        | 11.3.1           | Channel states                             | 193<br>193 |

|        |                  | Stopping channels                          | 193        |

| 11.4   | Resourc          | es                                         | 194        |

| 11.5   | Bvte-stre        | am mode                                    | 195        |

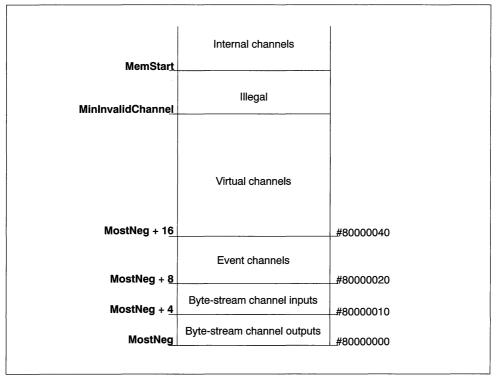

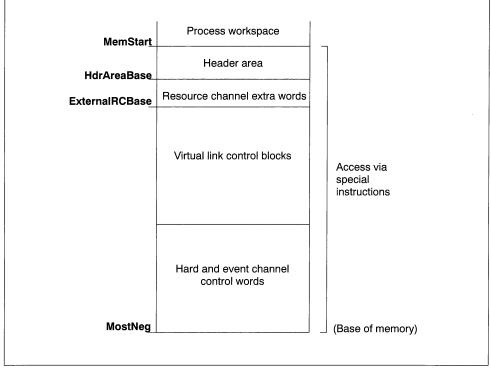

| 11.6   | •                | and channel address spaces                 | 196        |

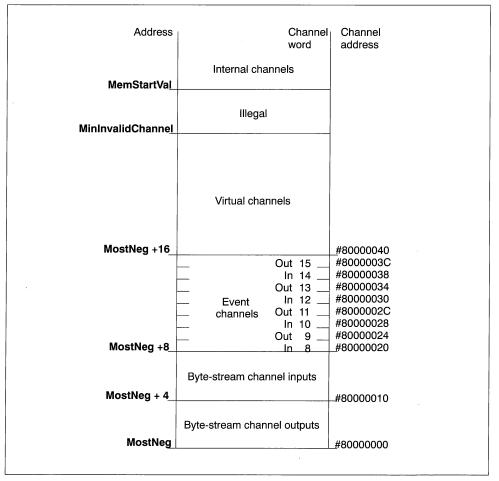

|        | 11.6.1           | Channel address space                      | 196        |

|        | 11.6.2           | Memory allocation for virtual links        | 197        |

|        |                  | Memory start value register                | 198        |

|        |                  | Minimum invalid virtual channel register   | 198        |

|        |                  | External resource channel base register    | 198        |

| 11.7   |                  | figuration registers                       | 199        |

|        | 11.7.1           | VCP command register                       | 199        |

|        | 11.7.2           | VCP status register                        | 199        |

|        | 11.7.3<br>11.7.4 | Header area base register                  | 200<br>200 |

|        | 11.7.5           | Packet header limit registers              | 200        |

|        | 11.7.6           | VCP link mode registers                    | 202        |

|        | 11.7.7           | ChanWriteLock                              | 202        |

| 11.8   | Initializat      | ion of the VCP                             | 203        |

|        | 11.8.1           | VCP state on start up                      | 203        |

|        | 11.8.2           | VCP state following reset                  | 203        |

| 11.9   | Errors .         |                                            | 204        |

|        |                  | Null buffer pointers                       | 204        |

\_\_\_\_\_

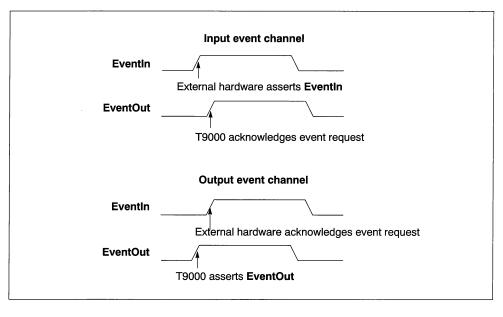

| 12 Eve  | nts                                                                                  | 205               |

|---------|--------------------------------------------------------------------------------------|-------------------|

|         | Input event channel<br>Output event channel<br>Use of event channels with interrupts | 205<br>205<br>205 |

| 12.1    | Event channel addresses                                                              | 205               |

| 12.2    | Event channel state                                                                  | 207               |

| 12.2    |                                                                                      | 207               |

|         | a/Strobe links                                                                       | 209               |

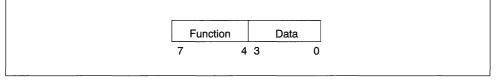

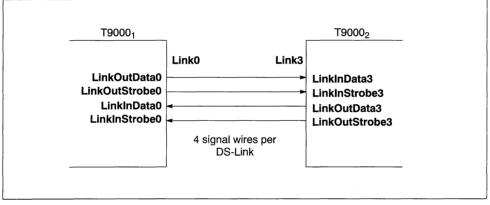

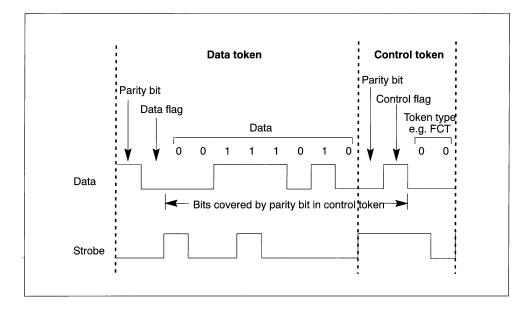

| 13.1    | Link format and protocol                                                             | 209               |

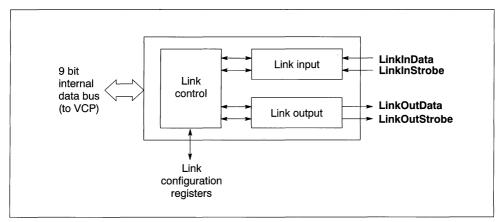

| 13.2    | Link functional description                                                          | 211               |

| 13.3    | Low-level flow control                                                               | 212               |

| 13.4    | Link speed select                                                                    | 212               |

| 13.5    | Errors on DS-Links                                                                   | 213               |

|         | 13.5.1 Reliable links                                                                | 214               |

|         | Handling of errors on reliable links                                                 | 214               |

| 13.6    | 13.5.2 Unreliable links                                                              | 214<br>215        |

| 13.0    | Initialization                                                                       | 213               |

| 13.7    |                                                                                      |                   |

|         | 13.7.1       Link state on start up         13.7.2       Link state following reset  | 217<br>217        |

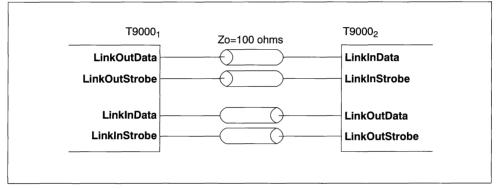

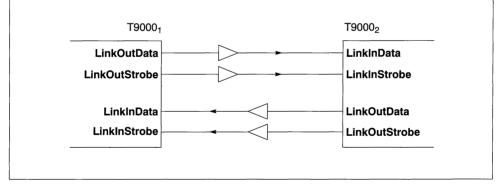

| 13.8    | Link connections                                                                     | 218               |

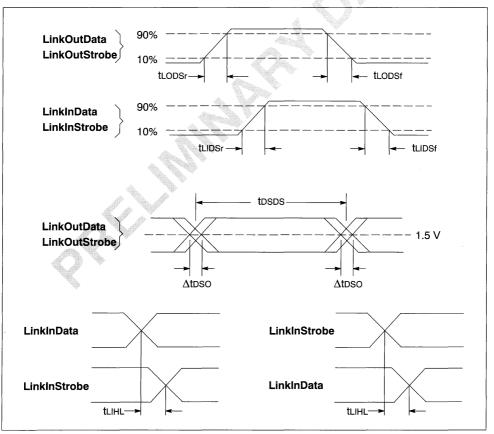

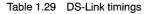

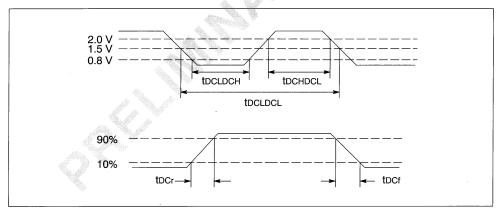

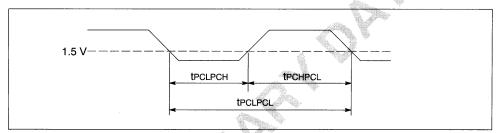

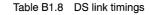

| 13.9    | DS-Link timings                                                                      | 219               |

| 10.0    |                                                                                      | 2.0               |

| 14 Cloc | cking phase locked loops                                                             | 221               |

| 14.1    | Clock input                                                                          | 221               |

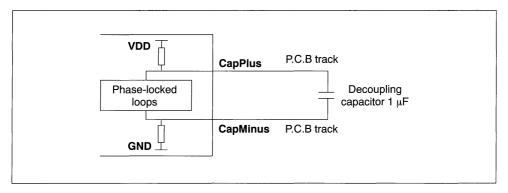

| 14.2    | PLL decoupling                                                                       | 221               |

| 14.3    | Processor speed selection                                                            | 222               |

| 14.4    | Processor clock output                                                               | 222               |

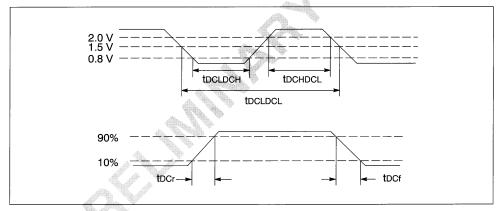

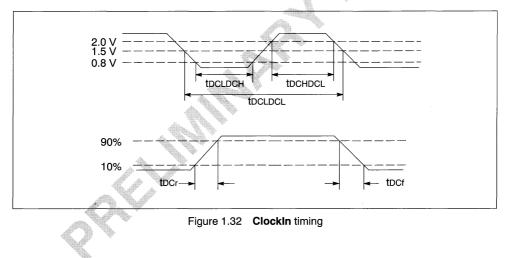

| 14.5    | ClockIn timings                                                                      | 223               |

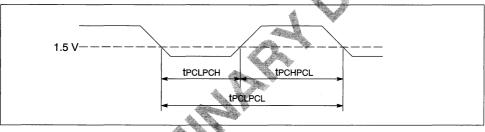

| 14.6    | ProcClockOut timings                                                                 | 224               |

| 15 Cont | figuration register reference guide                                                  | 225               |

|         |                                                                                      |                   |

| 15.1    | Configuration bus                                                                    | 225               |

| 15.2    | Subsystem addresses                                                                  | 225               |

| 45.0    | 15.2.1 Shared registers                                                              | 225               |

| 15.3    |                                                                                      | 226               |

| 15.4    | Subsystem registers                                                                  | 226               |

|         | 15.4.1 CPU configuration registers                                                   | 227               |

|         | 15.4.2 PMI configuration registers<br>PMI bank address configuration registers       | 227<br>227        |

|         | PMI strobe timing configuration registers                                            | 228               |

|         | 15.4.3 VCP configuration registers                                                   | 229               |

|         | 15.4.4 System services configuration registers                                       | 229               |

|         | 15.4.5 Cache configuration registers                                                 | 230               |

|         | 15.4.6 Scheduler configuration registers                                             | 230               |

|         | 15.4.7 Link configuration registers                                                  | 230               |

|         | 15.4.8 Control link configuration registers                                          | 231               |

| 16 Pac  | kage specifications                          | 233 |

|---------|----------------------------------------------|-----|

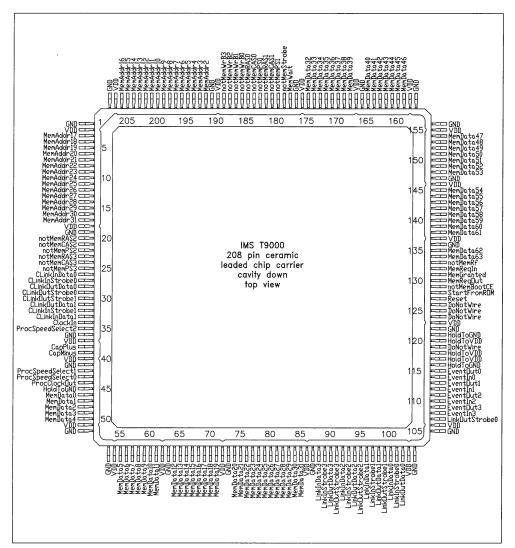

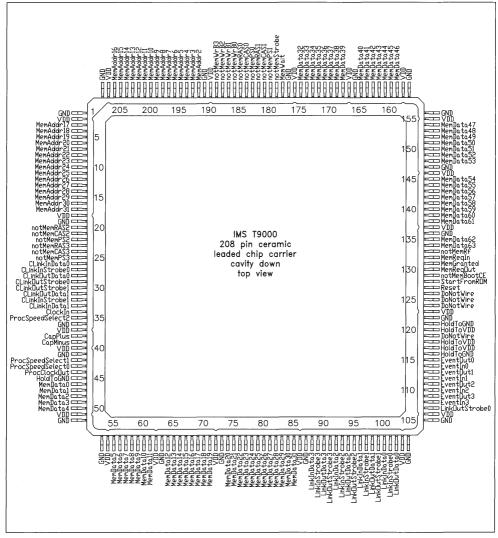

| 16.1    | 208 pin CLCC package pinout                  | 233 |

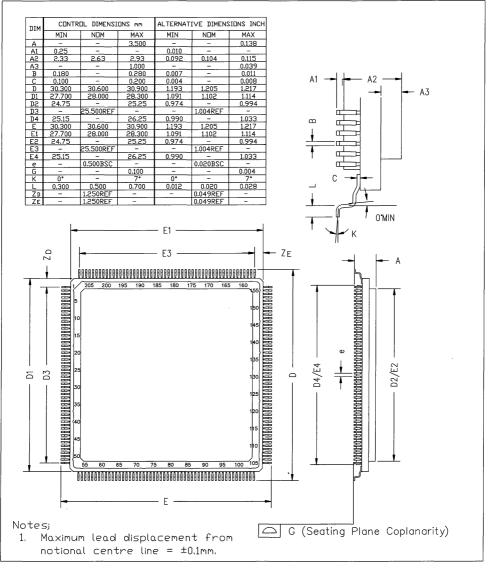

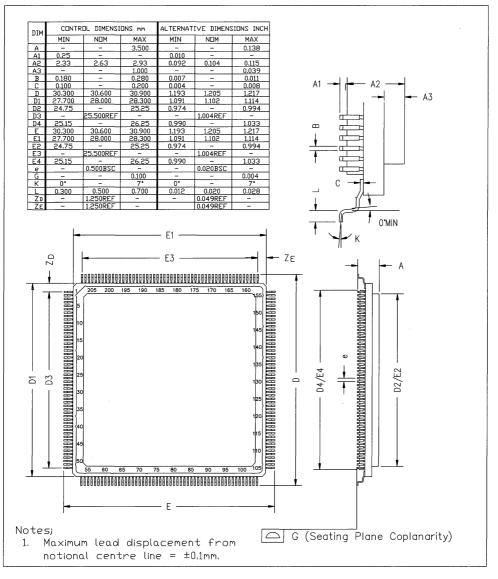

| 16.2    | 208 pin CLCC package dimensions              | 234 |

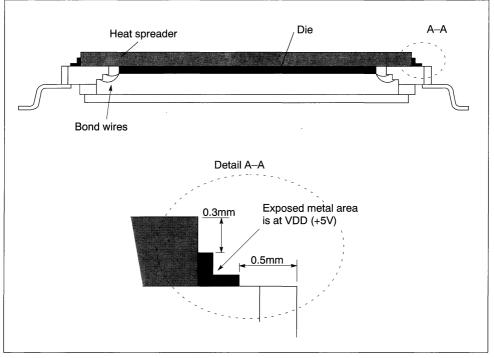

| 16.3    | 208 pin CLCC package thermal characteristics | 234 |

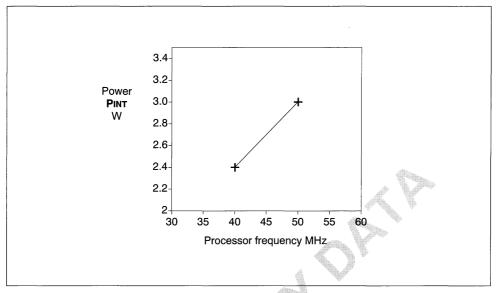

| 17 The  | rmal management                              | 235 |

| 17.1    | Forced air flow cooling                      | 236 |

| 17.2    | Heat sinks                                   | 236 |

| 17.3    | Other thermal management techniques          | 237 |

| 18 Elec | trical specifications                        | 239 |

| 18.1    | Absolute maximum ratings                     | 239 |

| 18.2    | Operating conditions                         | 239 |

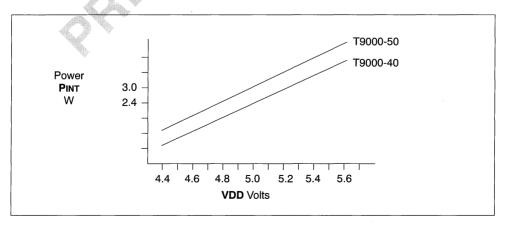

| 18.3    | Power rating                                 | 240 |

| Part | 3: C | ommu     | inications support devices                                                                                                       | 243        |

|------|------|----------|----------------------------------------------------------------------------------------------------------------------------------|------------|

| 1    | IMS  | C100 s   | ystem protocol converter preliminary data                                                                                        | 245        |

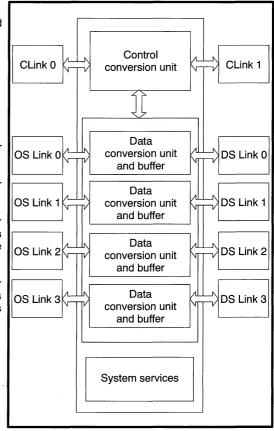

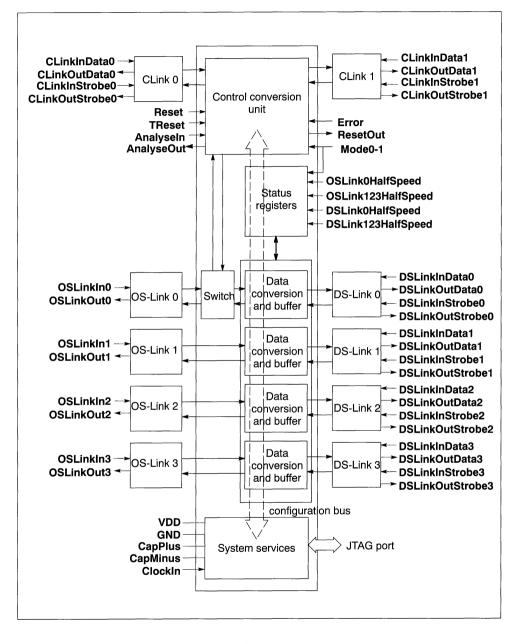

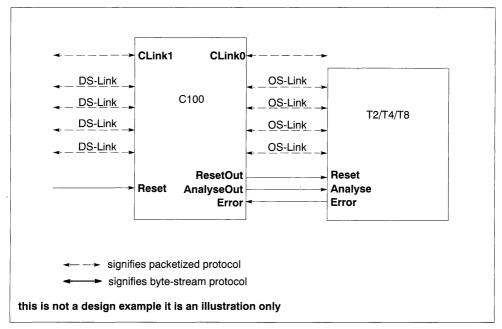

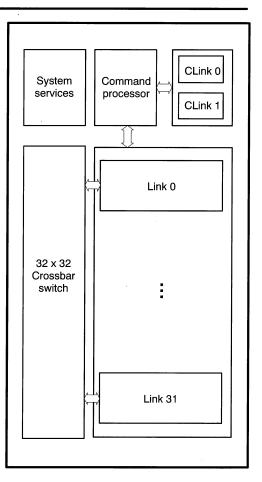

|      | 1.1  | IMS C1   | 00 introduction                                                                                                                  | 246        |

|      | 1.2  | IMS C1   | 00 modes of operation                                                                                                            | 248        |

|      |      | 1.2.1    | Mode pins                                                                                                                        | 248        |

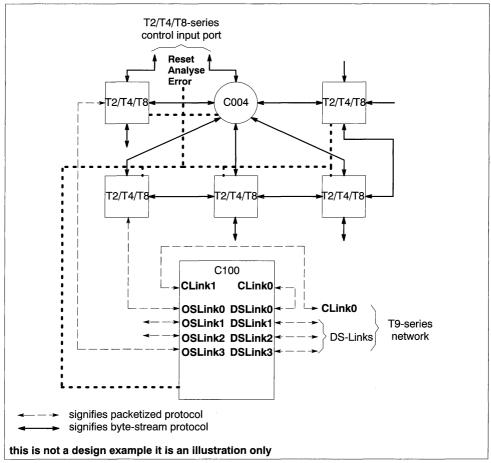

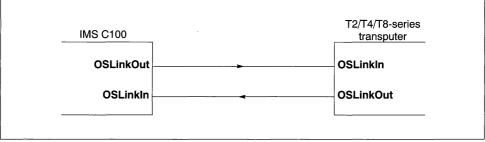

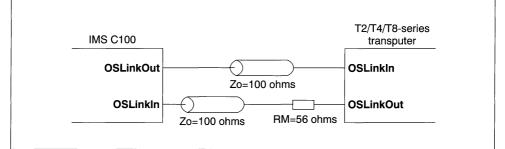

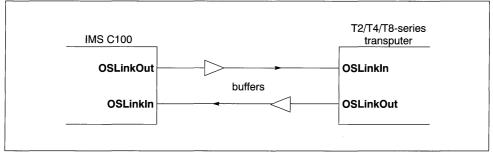

|      |      | 1.2.2    | Mode 0: Enables a single T9-series transputer to be used in a T2/T4/T8-series network                                            | 249        |

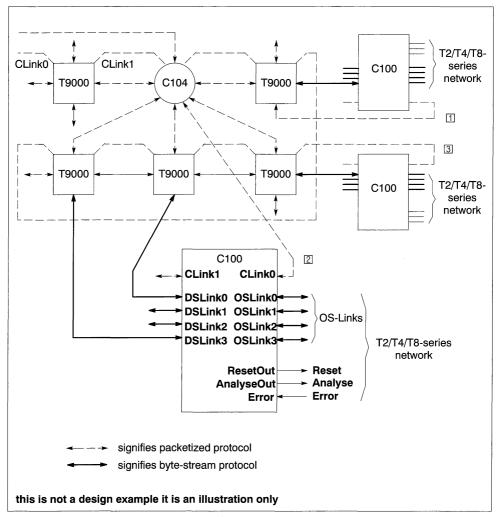

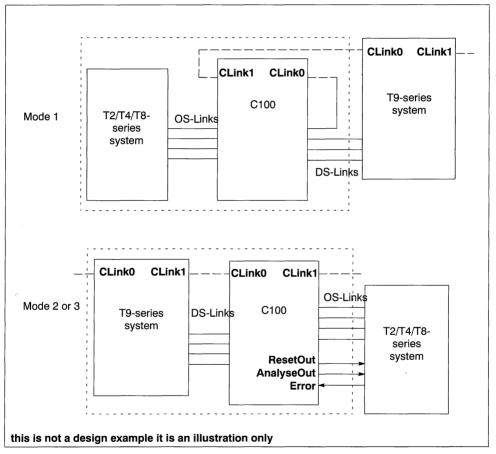

|      |      | 1.2.3    | Mode 1: Enables a T2/T4/T8-series system to use a T9-series subsystem                                                            | 251        |

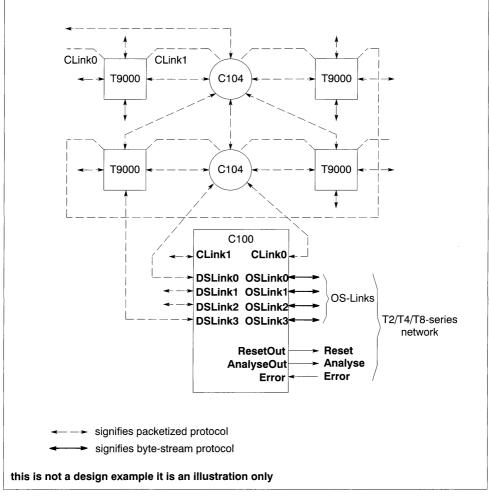

| :    |      | 1.2.4    | Mode 2: Enables a T9-series system to use an existing T2/T4/T8-series subsystem                                                  | 252        |

| i.   |      | 1.2.5    | Mode 3: Enables a T9-series system to use a T2/T4/T8-series subsystem                                                            | 254        |

|      | 1.3  | Link pro | ptocols                                                                                                                          | 256        |

|      |      | 1.3.1    | T2/T4/T8-series oversampled links                                                                                                | 256        |

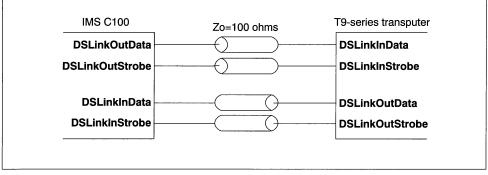

|      |      | 1.3.2    | T9-series data/strobe links                                                                                                      | 257        |

|      |      |          | Byte-stream mode                                                                                                                 | 259        |

|      | 1.4  | Link pro | ptocol conversion                                                                                                                | 260        |

|      |      | 1.4.1    | Byte-stream conversion – modes 0 and 2                                                                                           | 260        |

|      |      |          | Messages from the T9000 to the T2/T4/T8                                                                                          | 261        |

|      |      |          | Messages from the T2/T4/T8 to the T9000                                                                                          | 262        |

|      |      | 1.4.2    | Packetized conversion – modes 1 and 3                                                                                            | 262        |

|      |      |          | Messages from the T2/T4/T8 to the T9000                                                                                          | 263        |

|      |      | 0        | Messages from the T9000 to the T2/T4/T8                                                                                          | 263        |

|      | 1.5  |          | protocols                                                                                                                        | 265        |

|      |      | 1.5.1    | T2/T4/T8-type control                                                                                                            | 265        |

|      |      | 1.5.2    | T9-type control                                                                                                                  | 265        |

|      | 10   | Control  | Control link protocols                                                                                                           | 266        |

|      | 1.6  |          | protocol conversion                                                                                                              | 267        |

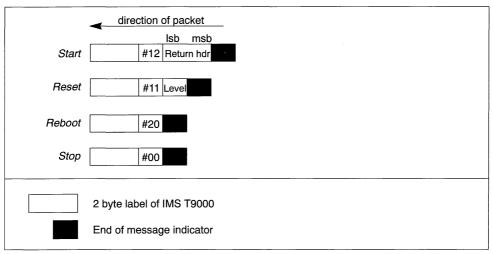

|      |      | 1.6.1    | RAE master control (mode 0)                                                                                                      | 268        |

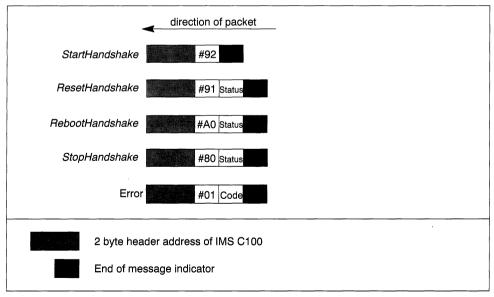

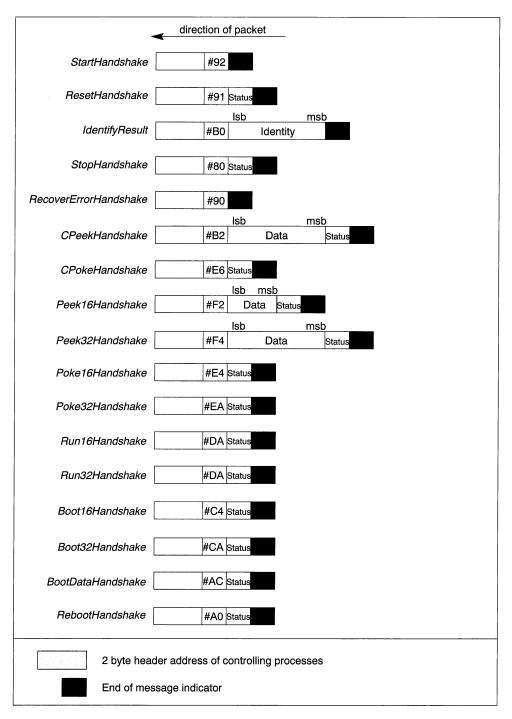

|      |      |          | Control commands sent by the IMS C100 in RAE master control mode .<br>Handshake and Error messages received by the IMS C100 from | 269<br>270 |

|      |      |          | the IMS T9000Behavior of the control system in RAE master mode                                                                   | 270        |

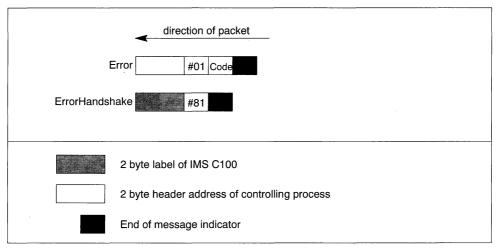

|      |      |          | Errors                                                                                                                           | 270        |

|      |      | 1.6.2    | CLink0 master control (modes 1, 2 and 3)                                                                                         | 272        |

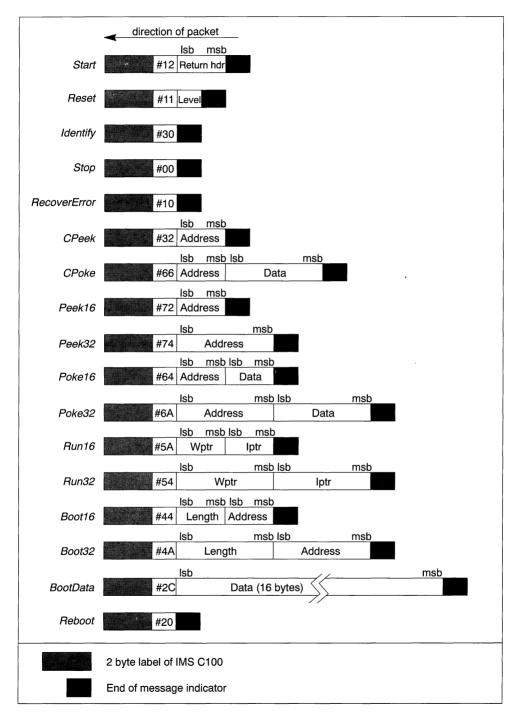

|      |      | 1.0.2    | Control commands sent by the controlling processor (IMS T9000) to                                                                | 212        |

|      |      |          | the IMS C100                                                                                                                     | 273        |

|      |      |          | Errors                                                                                                                           | 278        |

|      |      |          | OS-Link 0 special function – modes 2 and 3                                                                                       | 279        |

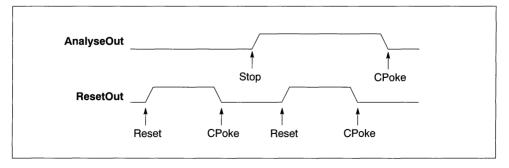

|      |      |          | Commands which correspond to the protocol of an unbooted T2/T4/T8 transputer                                                     | 279        |

|      |      |          | Resetting and Analyzing                                                                                                          | 280        |

|      | 1.7  |          | ••••••                                                                                                                           | 281        |

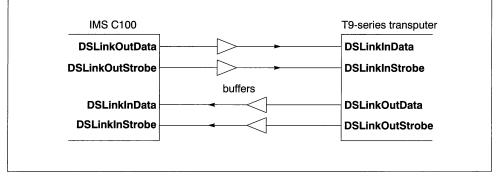

|      |      | 1.7.1    | Data links                                                                                                                       | 281        |

|      |      |          | Data link speed pins                                                                                                             | 281        |

|      |      |          | DS-Link speeds in mode 0                                                                                                         | 281        |

|      |      |          | DS-Link speeds in modes 1, 2 and 3                                                                                               | 281        |

|      |      |          | Errors on DS-Links                                                                                                               | 282        |

|      |      | 170      | Link connections                                                                                                                 | 284        |

|      |      | 1.7.2    | Control links                                                                                                                    | 286<br>286 |

|      |      | 1.7.3    | Control link speeds                                                                                                              | 200<br>286 |

|      |      | 1.7.0    |                                                                                                                                  | 200        |

|   | 1.8   | Levels of  | reset                                                           | 287 |

|---|-------|------------|-----------------------------------------------------------------|-----|

|   |       | 1.8.1      | Level 0 – hardware reset                                        | 287 |

|   |       | 1.8.2      | Level 1 – labelled control network                              | 287 |

|   |       | 1.8.3      | Level 2 – configured network                                    | 287 |

|   |       | 1.8.4      | Level 3                                                         | 287 |

|   |       | 1.8.5      | Effects of different levels of reset                            | 287 |

|   | 1.9   | Configura  | ation                                                           | 288 |

|   |       | 1.9.1      | Configuration space                                             | 288 |

|   |       | 1.9.2      | Configuration register addresses                                | 288 |

|   |       | 1.9.3      | Configuration registers                                         | 290 |

|   |       |            | System services configuration registers                         | 290 |

|   |       |            | Data DS-Link configuration registers                            | 291 |

|   |       |            | All data links                                                  | 292 |

|   |       |            | Control link configuration registers                            | 292 |

|   |       |            | Write lock registers                                            | 292 |

|   | 1.10  | Electrical | specifications                                                  | 293 |

|   |       | 1.10.1     | Absolute maximum ratings                                        | 293 |

|   |       | 1.10.2     | Operating conditions                                            | 293 |

|   | 1.11  | Recomm     | ended decoupling                                                | 294 |

|   |       | 1.11.1     | Power decoupling                                                | 294 |

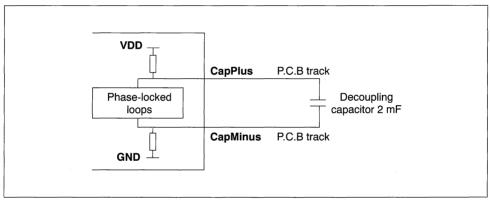

|   |       | 1.11.2     | Phase locked loop decoupling                                    | 294 |

|   | 1.12  | Clocks     |                                                                 | 294 |

|   |       | 1.12.1     | Clock input                                                     | 294 |

|   | 1.13  | Timing sp  | pecifications                                                   | 295 |

|   |       | 1.13.1     | Reset and Analyse timings                                       | 295 |

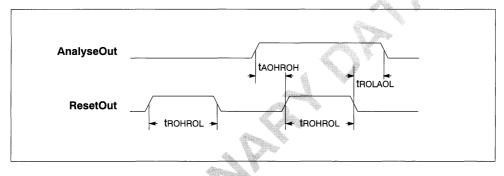

|   |       |            | ResetOut and AnalyseOut timings                                 | 295 |

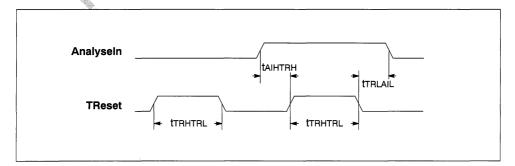

|   |       |            | TReset and AnalyseIn timings                                    | 295 |

|   |       | 1.13.2     | ClockIn timings                                                 | 296 |

|   |       | 1.13.3     | DS-Link timings                                                 | 297 |

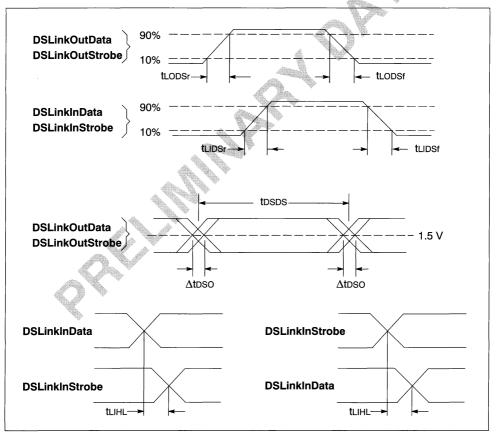

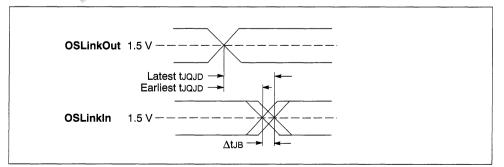

|   |       | 1.13.4     | OS-Link timings                                                 | 298 |

|   | 1.14  | Pin desig  | nations                                                         | 299 |

|   |       |            | Supplies                                                        | 299 |

|   |       |            | Clocks                                                          | 299 |

|   |       |            | Links                                                           | 299 |

|   |       |            | Control unit                                                    | 300 |

|   |       |            | JTAG support                                                    | 300 |

|   |       |            | Miscellaneous                                                   | 300 |

|   | 1.15  | Package    | specifications                                                  | 301 |

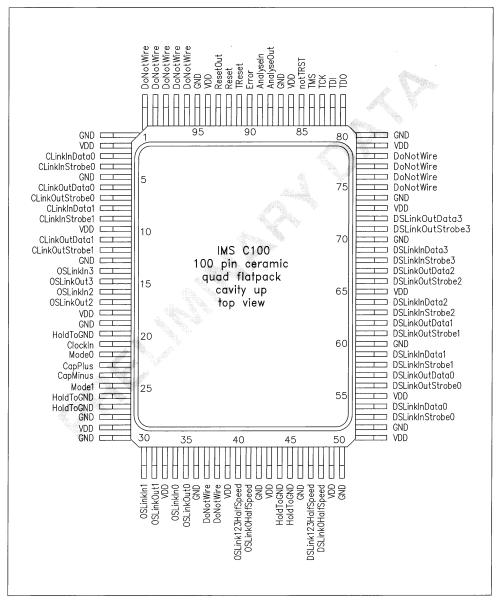

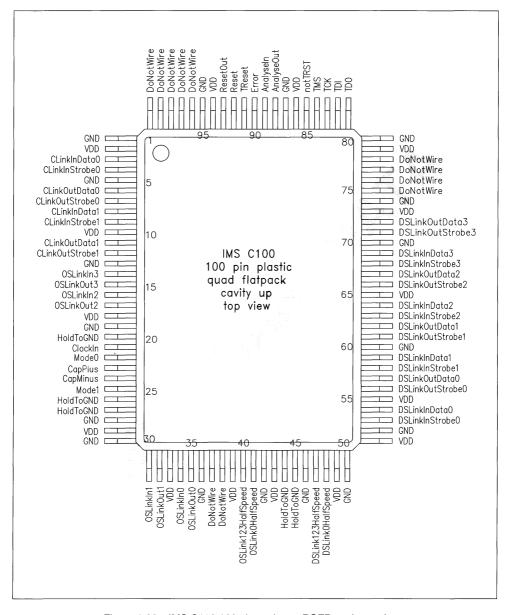

|   |       | 1.15.1     | IMS C100 100 pin cavity-up ceramic quad flatpack package pinout | 301 |

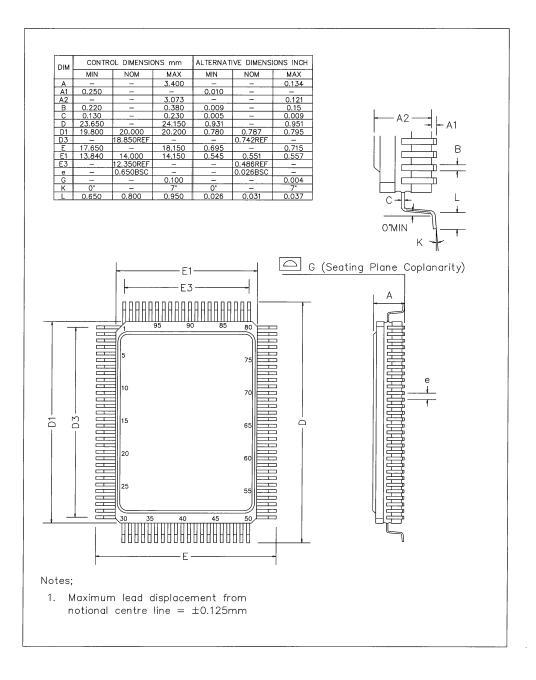

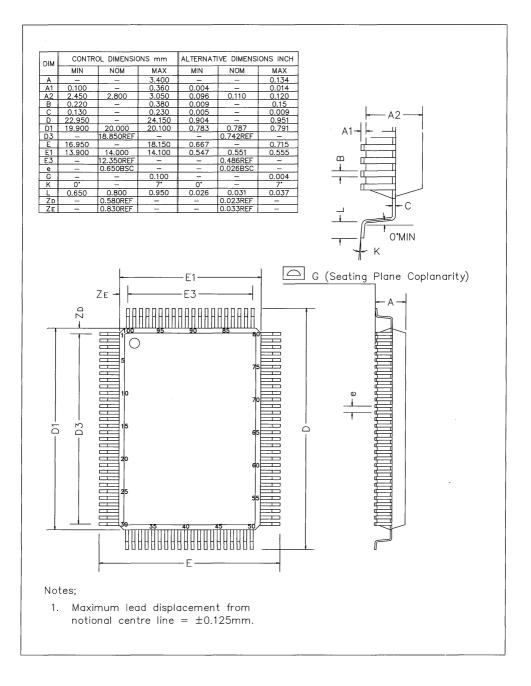

|   |       | 1.15.2     | 100 pin ceramic quad flatpack package dimensions                | 302 |

|   |       | 1.15.3     | IMS C100 100 pin cavity-up plastic quad flatpack package pinout | 303 |

|   |       | 1.15.4     | 100 pin plastic quad flatpack package dimensions                | 304 |

|   |       |            |                                                                 |     |

| 2 | IMS ( | C104 pao   | cket routing switch product preview                             | 305 |

|   | 2.1   | IMS C104   | Introduction                                                    | 306 |

|   |       |            |                                                                 |     |

| 3 | IMS ( | C101 par   | allel DS-Link adaptor product preview                           | 307 |

|   |       |            |                                                                 |     |

| Contents | 6 |

|----------|---|

|----------|---|

# Appendices

| IMS TS | 9000 sp                                                                    | pecial values                                                                                                                                                                                                             | . 309                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1 IMS | T9000 s                                                                    | pecial values                                                                                                                                                                                                             | . 310                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IMS TS | 9000 qu                                                                    | uick reference guide                                                                                                                                                                                                      | . 311                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| B1 IMS | T9000 q                                                                    | uick reference guide                                                                                                                                                                                                      | . 312                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

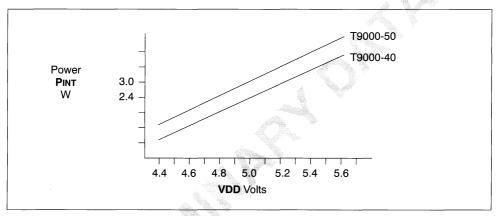

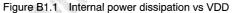

| B1.1   | Electrica                                                                  | Il specifications                                                                                                                                                                                                         | 313                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        |                                                                            |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        | B1.1.2                                                                     |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        | B1.1.3                                                                     |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B1.2   | Timing s                                                                   | pecifications                                                                                                                                                                                                             | 315                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | B1.2.1                                                                     | ClockIn timings                                                                                                                                                                                                           | 315                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        | B1.2.2                                                                     | 0                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        | B1.2.3                                                                     | Programmable memory interface timings                                                                                                                                                                                     | 317                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        |                                                                            | Read cycle                                                                                                                                                                                                                | 318                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        |                                                                            | Write cycle                                                                                                                                                                                                               | 319                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        |                                                                            | Consecutive cycles                                                                                                                                                                                                        | 320                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|        |                                                                            | -                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        |                                                                            |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| B1.3   | Process                                                                    | or speed select                                                                                                                                                                                                           | 323                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| B1.4   | Link spe                                                                   | ed select                                                                                                                                                                                                                 | 323                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

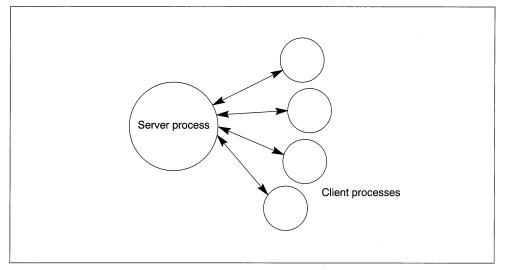

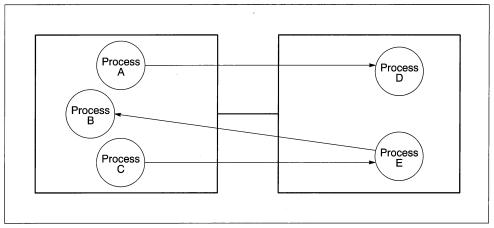

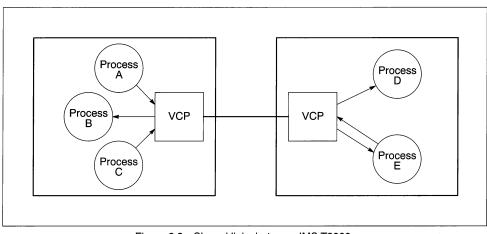

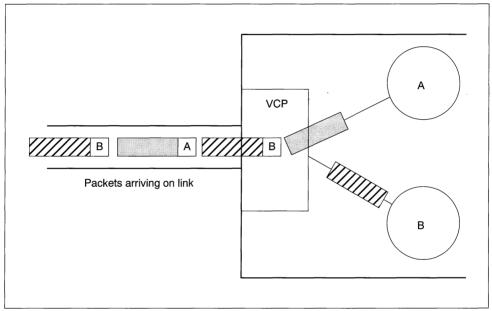

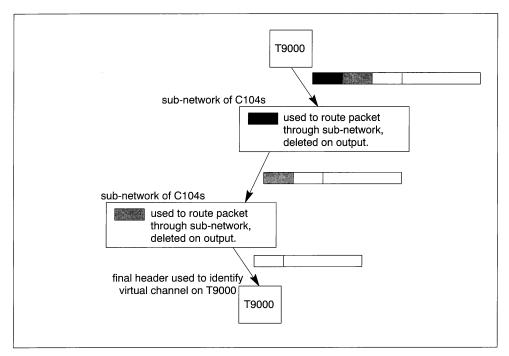

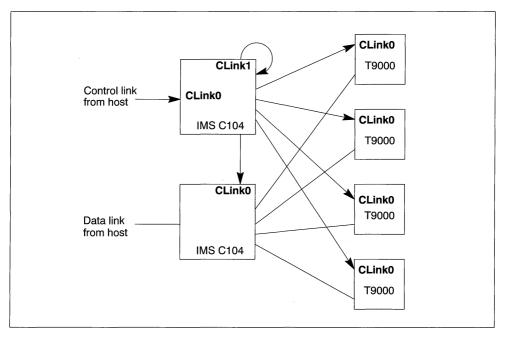

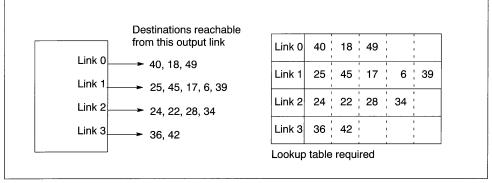

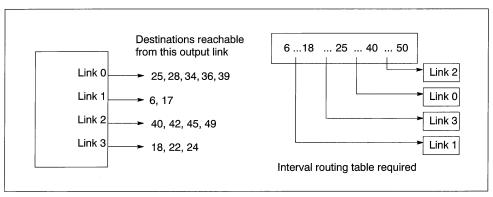

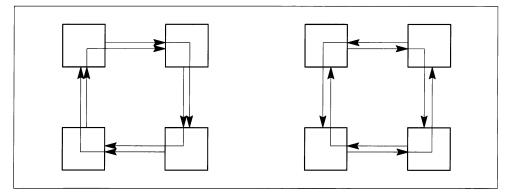

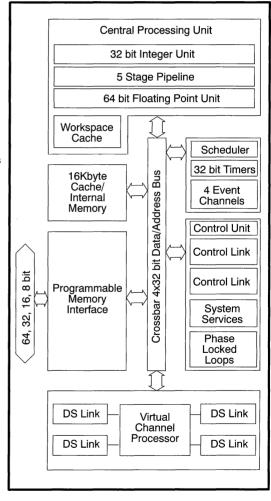

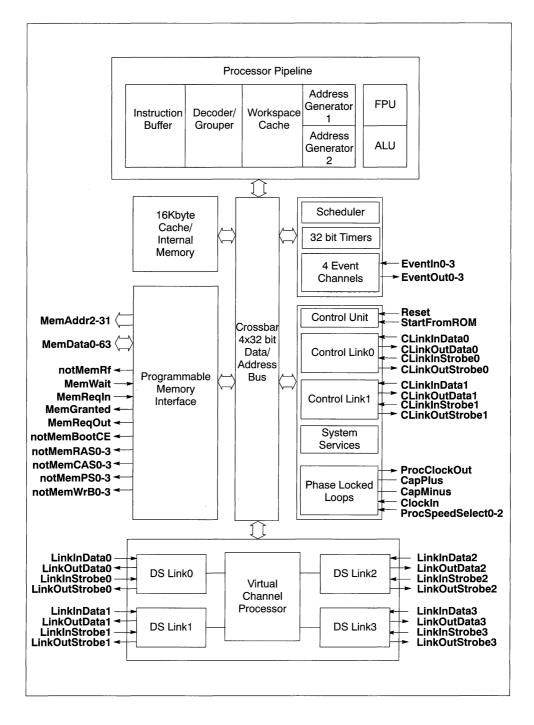

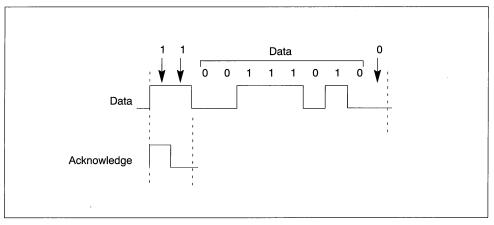

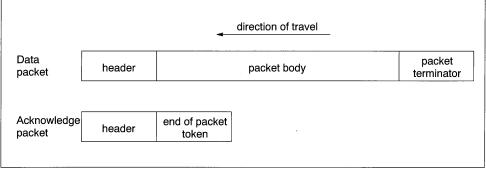

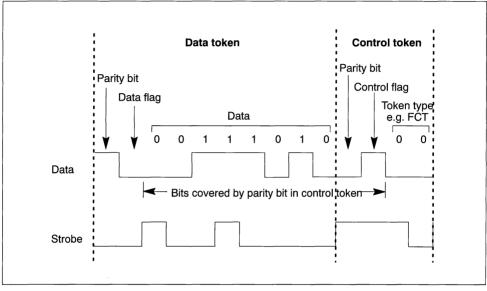

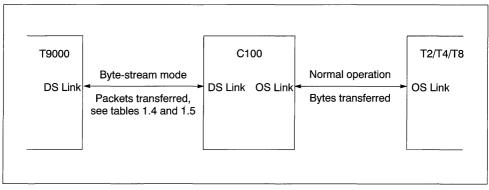

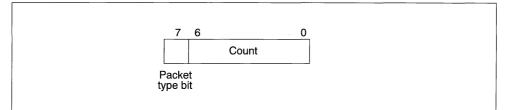

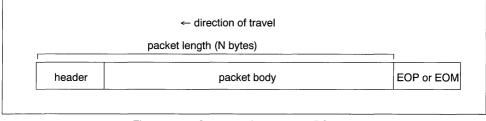

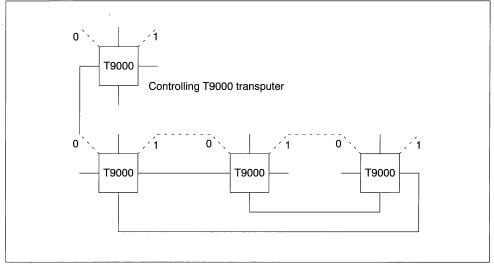

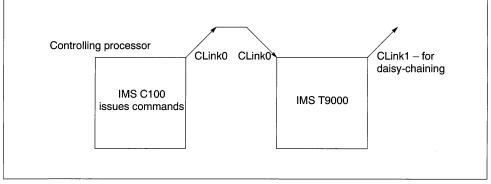

| B1.5   | Package                                                                    | edetails                                                                                                                                                                                                                  | 324                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |