# THE T9000 TRANSPUTER PRODUCTS OVERVIEW MANUAL

First Edition 1991

#### **INMOS** Databook series

Transputer Databook

Military and Space Transputer Databook

Transputer Development and *iq* Systems Databook

Graphics Databook

Transputer Applications Notebook: Architecture and Software Transputer Applications Notebook: Systems and Performance The T9000 Transputer Products Overview Manual

#### Copyright © INMOS Limited 1991

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate; however, no responsibility is assumed for its use, nor for any infringement of patents or other rights of third parties resulting from its use. No licence is granted under any patents, trademarks or other rights of INMOS.

, inmos, IMS and occam are trademarks of INMOS Limited.

SGS-THOMSON is a registered trademark of SGS-THOMSON Microelectronics Group. INMOS is a member of the SGS-THOMSON Microelectronics Group.

INMOS document number: 72 TRN 228 00

ORDER CODE: DBTRANSPST/1

## Contents overview

| Contents  | <b>3</b>                               | V    |

|-----------|----------------------------------------|------|

| Preface   |                                        | xiii |

| Part 1: P | roduct Family Overview                 | 1    |

| 1         | Introducing the INMOS IMS T9000 family | 3    |

| 2         | The IMS T9000 transputer               | 7    |

| 3         | Simplicity of system design            | 16   |

| 4         | Protection and error handling          | 20   |

| 5         | Support for multiprocessing            | 22   |

| 6         | Communication links                    | 28   |

| 7         | Network communications                 | 35   |

| 8         | Other communications devices           | 43   |

| 9         | Software and systems                   | 45   |

| 10        | References                             | 51   |

| Part 2: P | oduct Family Preliminary Information   | 53   |

| IMS       | T9000 transputer                       | 55   |

| IMS       | C104 packet routing switch             | 139  |

| IMS       | C100 system protocol converter         | 163  |

### Contents

|   |       |           | amily Overview                      |  |

|---|-------|-----------|-------------------------------------|--|

| 1 | Intro | oducing   | the INMOS IMS T9000 family          |  |

|   | 1.1   | _         | , enance                            |  |

|   | 1.2   |           | ocessing                            |  |

|   | 1.3   | •         | inications support devices          |  |

|   | 1.4   |           | e                                   |  |

|   | 1.5   |           | tions                               |  |

| 2 | The   | IMS T9    | 000 transputer                      |  |

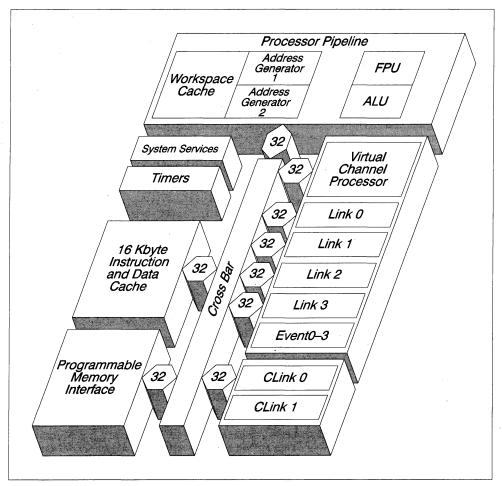

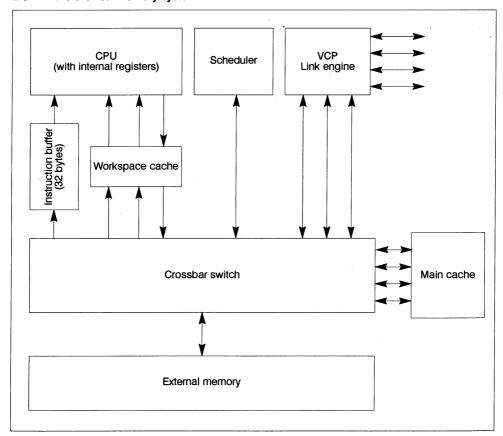

|   | 2.1   | Overvie   | w                                   |  |

|   |       |           | Processor                           |  |

|   |       |           | Hierarchical memory system          |  |

|   | *     |           | Communications system               |  |

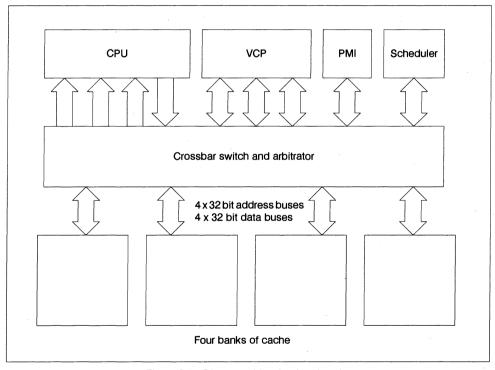

|   |       |           | Multiple internal buses             |  |

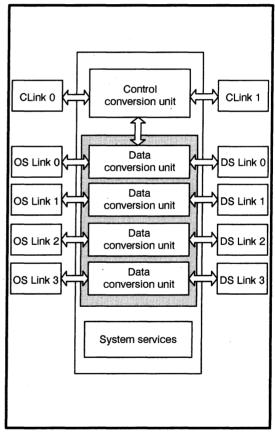

|   | 2.2   | The trai  | System servicesnsputer architecture |  |

|   | 2.3   |           | for concurrent processes            |  |

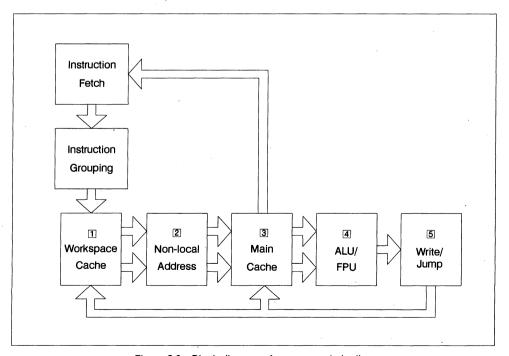

|   | 2.4   |           | ed, superscalar implementation      |  |

|   | 2.7   | Преше     | The pipeline                        |  |

|   |       |           | Grouping of instructions            |  |

|   |       |           | Improvements over IMS T805          |  |

|   | 2.5   | Hierarch  | nical memory system                 |  |

|   |       | 2.5.1     | Main cache                          |  |

|   |       |           | Cache operation                     |  |

|   |       |           | Use as on-chip RAM                  |  |

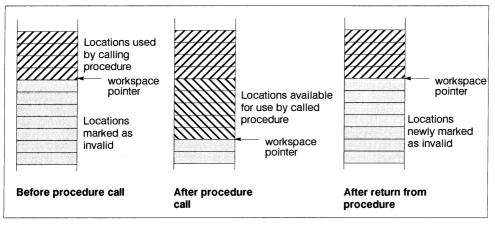

|   |       | 2.5.2     | Workspace cache  Cache operation    |  |

|   |       |           | ·                                   |  |

| 3 | Sim   | plicity o | f system design                     |  |

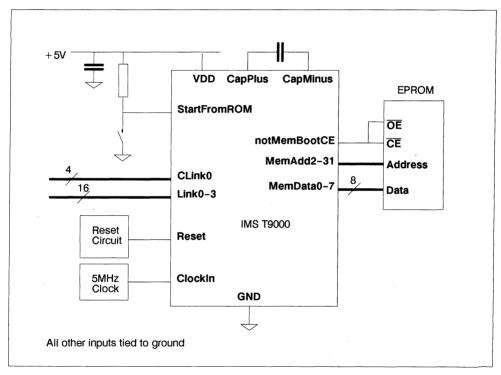

|   | 3.1   | Single 5  | MHz clock input                     |  |

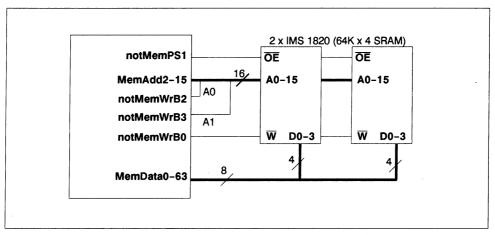

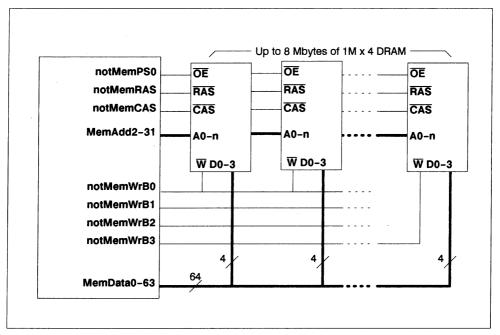

|   | 3.2   | Program   | mable memory interface              |  |

|   | 3.3   | Control   | links and configuration             |  |

|   | 3.4   | Loading   | and bootstrapping                   |  |

|   | 3.5   | Example   | es                                  |  |

| ļ | Prot  | ection a  | nd error handling                   |  |

|   | 4.1   | Error har | ndling                              |  |

|   | 4.2   | Protecte  | d mode                              |  |

|   |       |           | Protected mode processes            |  |

|   |       |           | Executing illegal instructions      |  |

|   |       |           | Memory management                   |  |

| 5 | Sup  | port for   | multiprocessing                            | 22       |

|---|------|------------|--------------------------------------------|----------|

|   |      |            | Fast interrupt response and process switch | 22       |

|   | 5.1  | The tran   | sputer model of concurrency                | 22       |

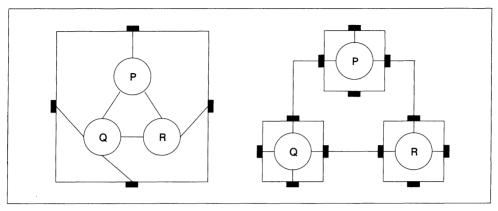

|   |      |            | Processes and channels                     | 22       |

|   |      |            | Program structure                          | 22       |

|   |      |            | Example                                    | 23<br>24 |

|   | 5.2  | Other m    | nodels of concurrency                      | 25       |

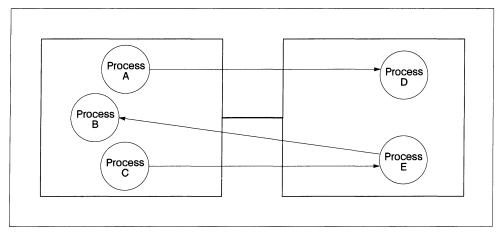

|   | 0.2  | Outlot III | Shared memory                              | 25       |

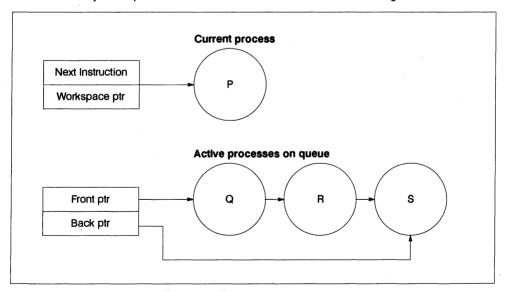

|   | 5.3  | Hardwa     | re scheduler                               | 26       |

|   | 5.4  |            | ts, events and timers                      | 26       |

|   |      | •          |                                            |          |

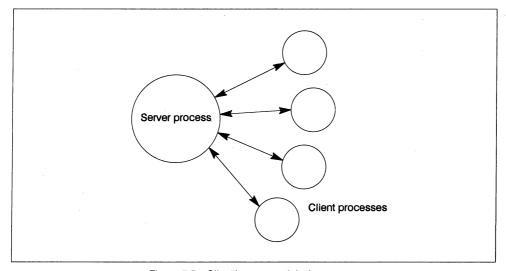

|   | 5.5  | Shared     | resources                                  | 27       |

| 6 | Com  | munica     | ation links                                | 28       |

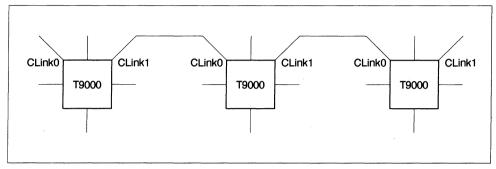

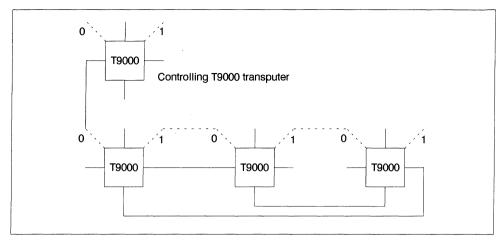

|   | 6.1  | Using lir  | nks between transputers                    | 28       |

|   | 6.2  | Advanta    | ges of using links                         | 28       |

|   |      |            | Efficiency                                 | 28       |

|   |      |            | Simplicity                                 | 28       |

|   |      |            | Hardware independence                      | 29       |

|   | 6.3  |            | 00 links                                   | 29       |

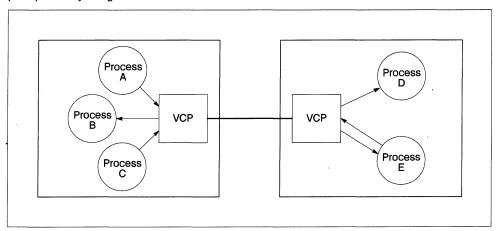

|   |      | 6.3.1      | Virtual channels                           | 30       |

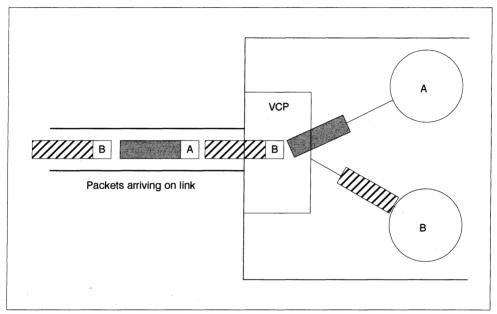

|   |      |            | Virtual links                              | 30       |

|   |      |            | Sending packets  Receiving packets         | 31<br>31 |

|   |      |            | The virtual channel processor              | 31       |

|   |      |            | Implementation                             | 32       |

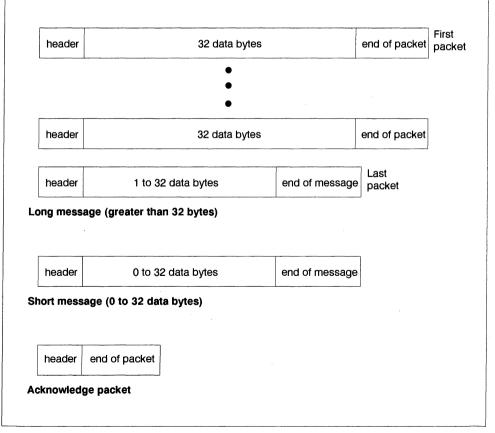

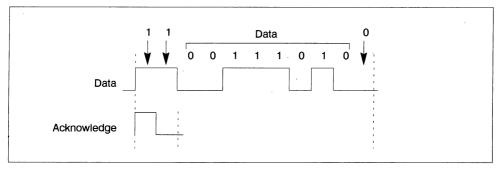

|   |      | 6.3.2      | Levels of link protocol.                   | 32       |

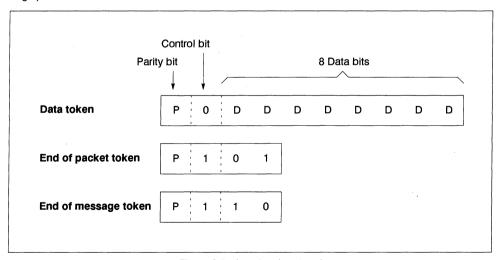

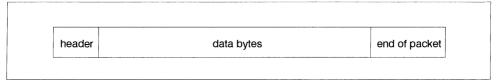

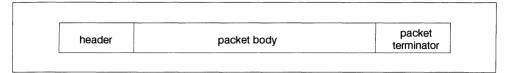

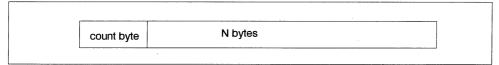

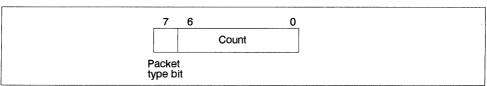

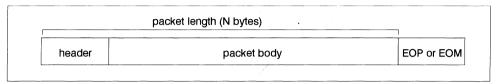

|   |      |            | Packet level protocol                      | 33       |

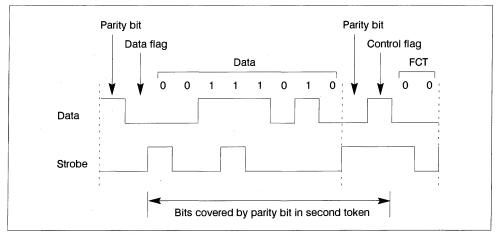

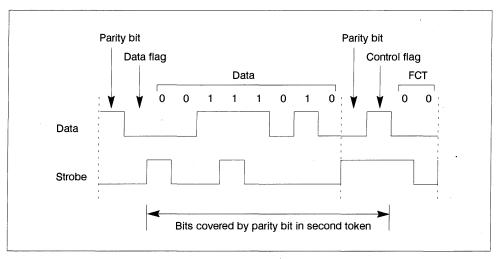

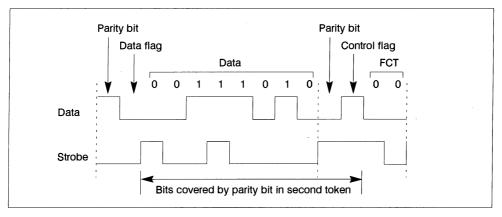

|   |      |            | Token level protocol                       | 33       |

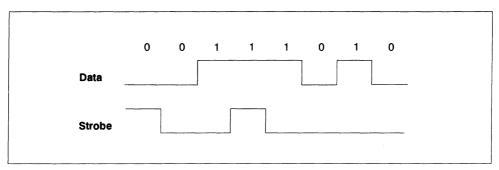

|   |      |            | Bit level protocol                         | 33       |

| 7 | Netw | ork cor    | mmunications                               | 35       |

|   | 7.1  | Message    | e routing                                  | 35       |

|   |      |            | Advantages for the programmer              | 35       |

|   |      | -          | Routers                                    | 35       |

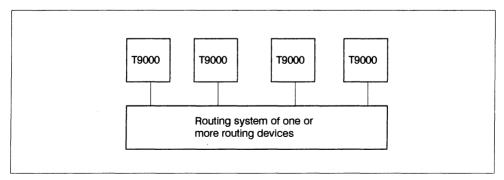

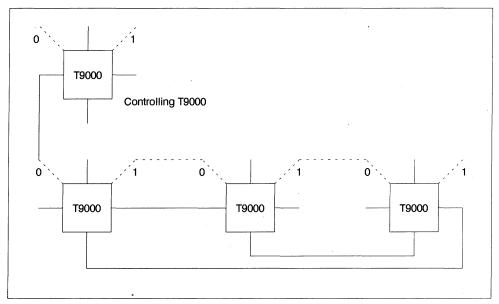

|   |      |            | Separating routers and processors          | 36       |

|   |      | =          | Parallel networks                          | 36       |

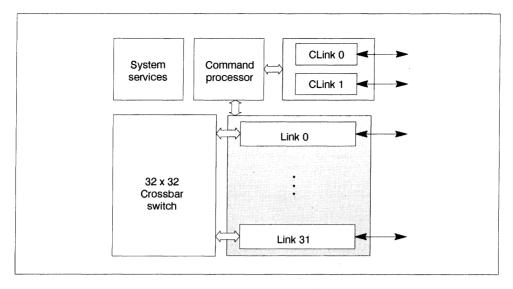

|   | 7.2  | ine ims    | C104                                       | 36       |

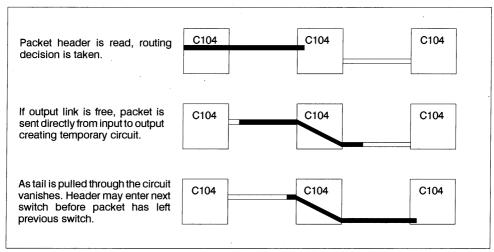

|   |      |            | Wormhole routing                           | 36       |

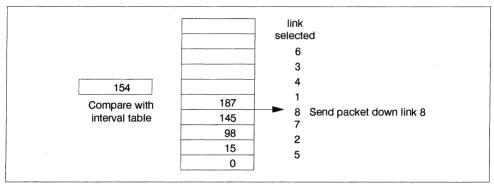

|   |      |            | Minimizing routing delays                  | 37<br>38 |

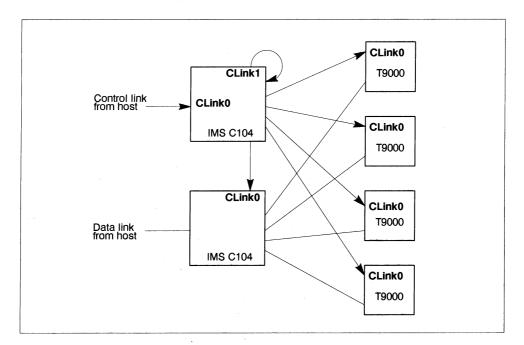

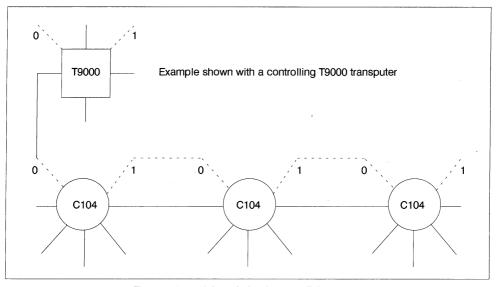

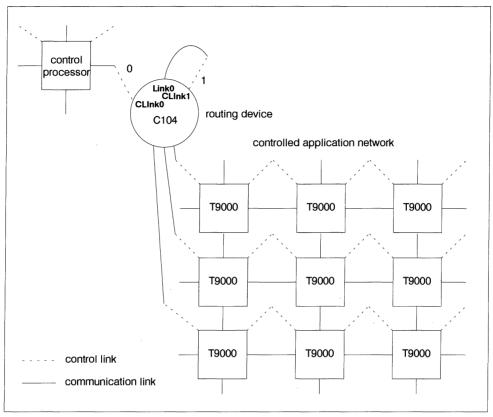

|   |      | 7.2.1      | Control links                              | 38       |

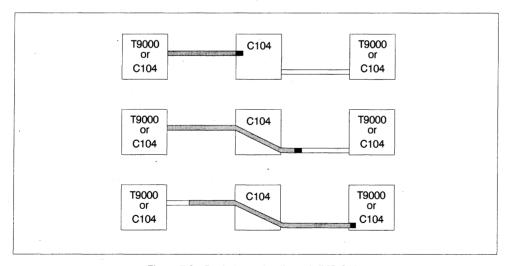

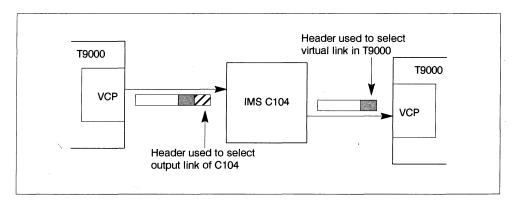

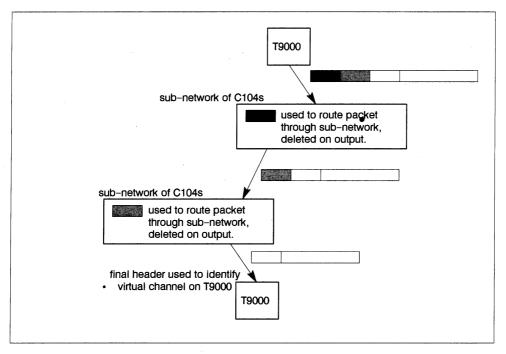

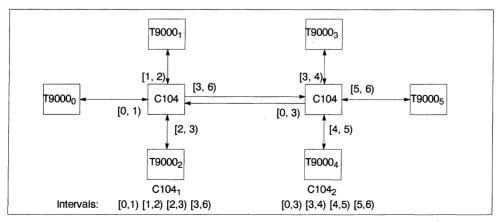

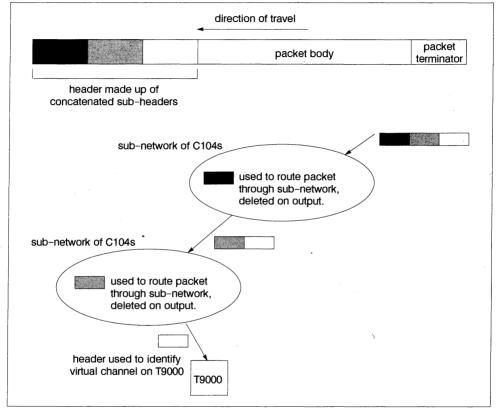

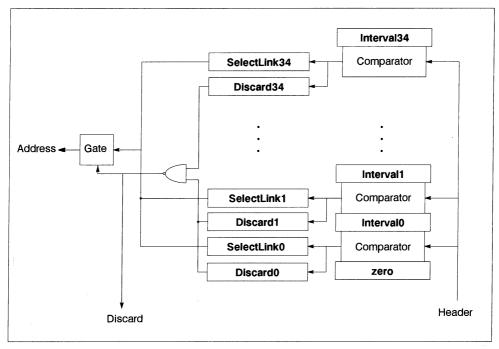

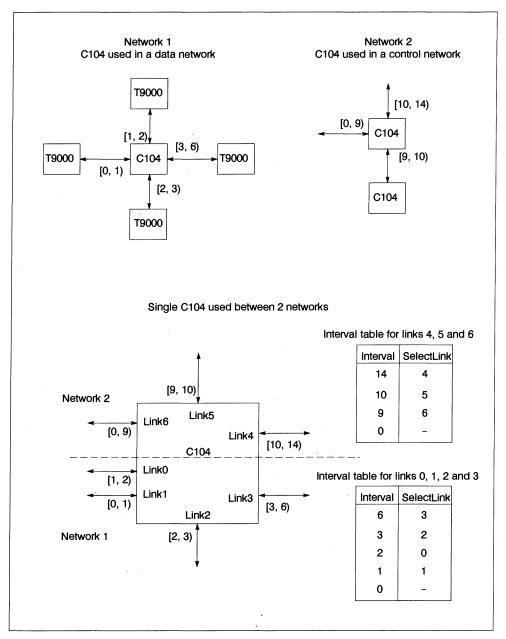

|   |      | 7.2.1      | Header deletion                            | 38       |

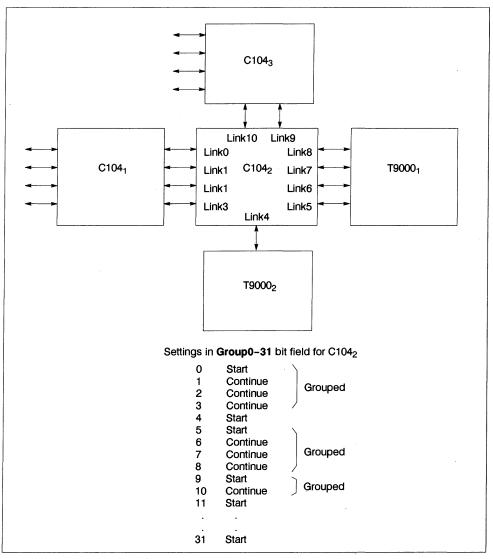

|   |      |            | Routing control channels                   | 40       |

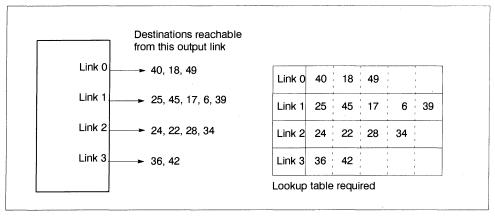

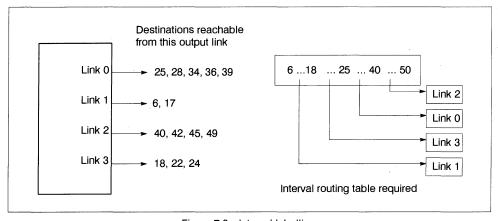

|   | 7.3  | Routing    | algorithms                                 | 40       |

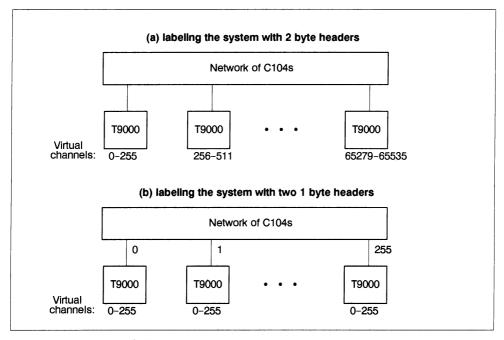

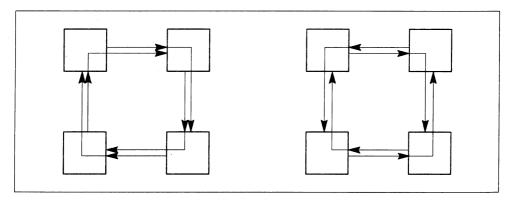

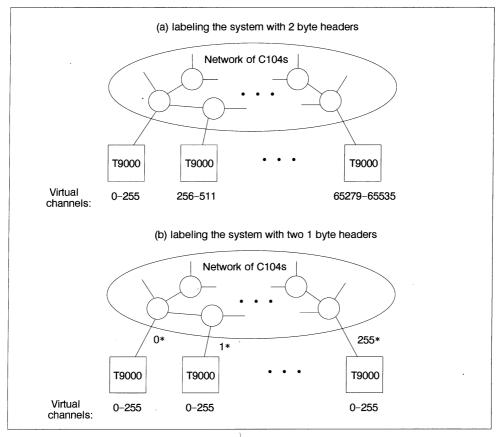

|   |      | 7.3.1      | Labelling networks                         | 41       |

|   |      | 7.3.2      | Avoiding deadlock                          | 42       |

| 8 | Othe | r comm     | nunications devices                        | 43       |

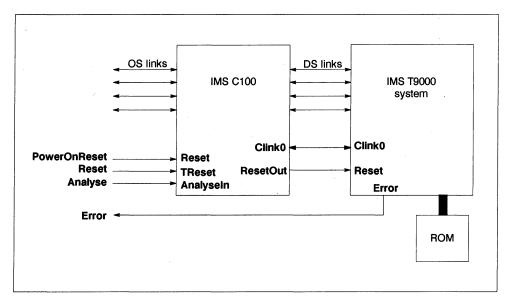

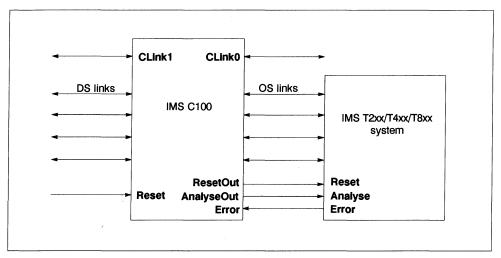

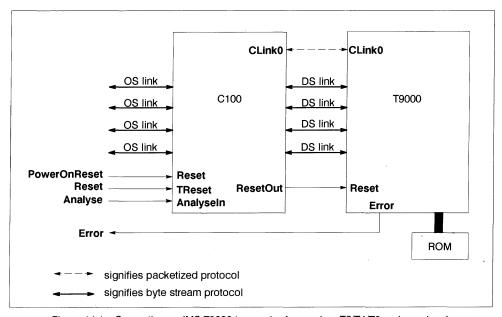

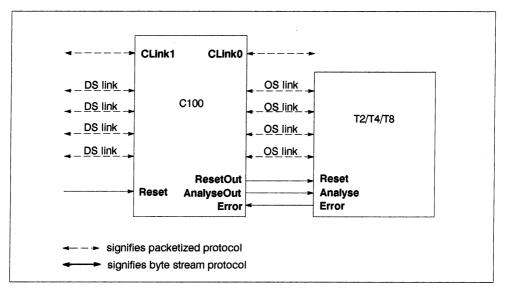

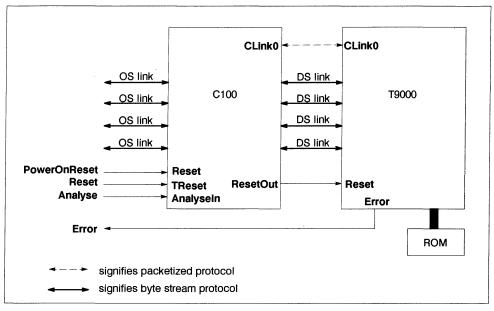

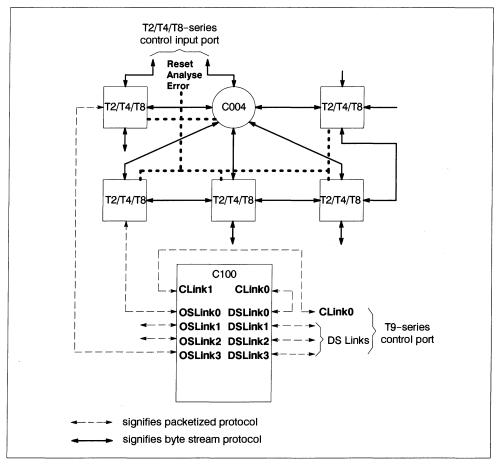

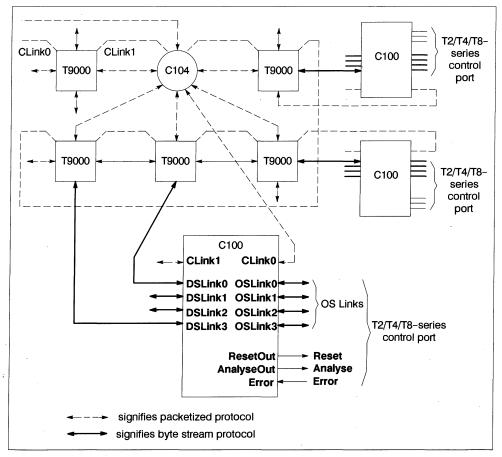

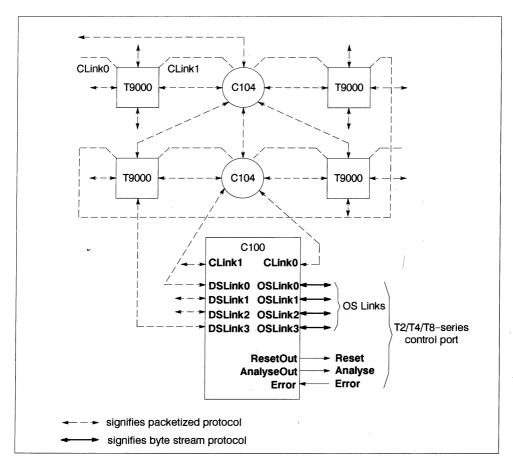

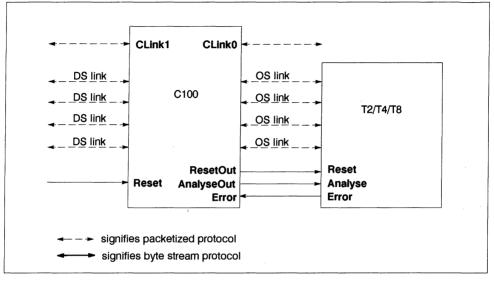

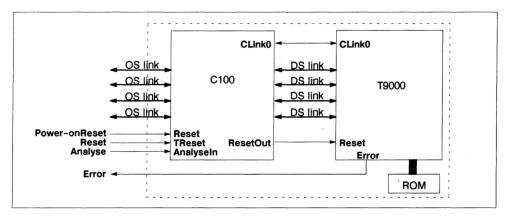

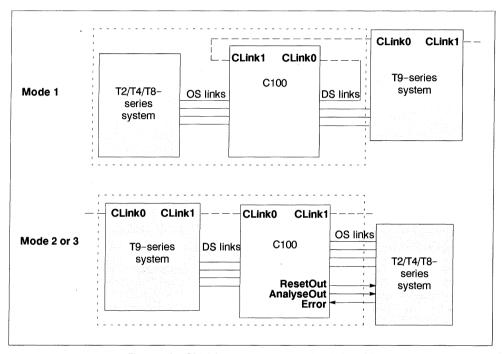

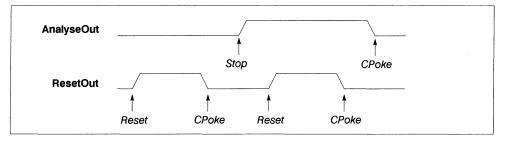

|   | 8.1  | Mixing tra | ansputer types: the IMS C100               | 43       |

Contents

|     | 8.2                                           | Interfac                                                                                    | ing to peripherals and host systems                                                                                                                    | 44                                                             |  |  |  |

|-----|-----------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|

| 9   | Sof                                           | oftware and systems                                                                         |                                                                                                                                                        |                                                                |  |  |  |

|     | 9.1                                           | Develo                                                                                      | pment software                                                                                                                                         | 45                                                             |  |  |  |

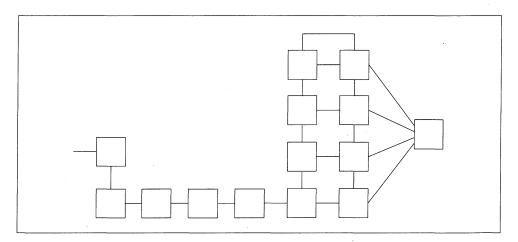

|     |                                               | 9.1.1                                                                                       | Configuration tools                                                                                                                                    | 45                                                             |  |  |  |

|     |                                               |                                                                                             | Hardware description                                                                                                                                   | 46                                                             |  |  |  |

|     |                                               |                                                                                             | Software description                                                                                                                                   | 46                                                             |  |  |  |

|     |                                               |                                                                                             | Mapping software to hardware                                                                                                                           | 46                                                             |  |  |  |

|     |                                               |                                                                                             | Configuration languages                                                                                                                                | 46                                                             |  |  |  |

|     |                                               | 0.4.0                                                                                       | Types of networks                                                                                                                                      | 46                                                             |  |  |  |

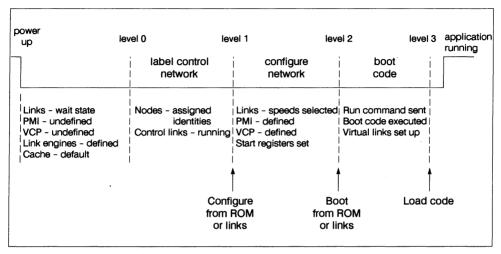

|     |                                               | 9.1.2                                                                                       | Initializing and loading a network                                                                                                                     | 47<br>47                                                       |  |  |  |

|     |                                               |                                                                                             | Levels of initialization                                                                                                                               | 47                                                             |  |  |  |

|     |                                               |                                                                                             | Booting a system from ROM                                                                                                                              | 47                                                             |  |  |  |

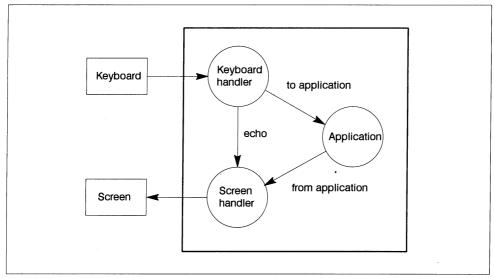

|     |                                               | 9.1.3                                                                                       | Host servers                                                                                                                                           | 47                                                             |  |  |  |

|     |                                               | 9.1.4                                                                                       | Debugging                                                                                                                                              | 48                                                             |  |  |  |

|     |                                               | 9.1.5                                                                                       | IMS T805 emulation                                                                                                                                     | 48                                                             |  |  |  |

|     | 9.2                                           | iq Syste                                                                                    | ems products                                                                                                                                           | 48                                                             |  |  |  |

|     |                                               | 9.2.1                                                                                       | IMS T9000 products                                                                                                                                     | 48                                                             |  |  |  |

|     |                                               |                                                                                             | Compatible development products                                                                                                                        | 49                                                             |  |  |  |

|     |                                               |                                                                                             | IMS T9000 specific products                                                                                                                            | 49                                                             |  |  |  |

|     |                                               |                                                                                             | Host interfaces                                                                                                                                        | 50                                                             |  |  |  |

| 1   | 0 Refe                                        | erences                                                                                     |                                                                                                                                                        | 51                                                             |  |  |  |

|     | O. D                                          | F.                                                                                          | and the Destination and Information                                                                                                                    |                                                                |  |  |  |

| art | 2: Pro                                        | oduct Fa                                                                                    | amily Preliminary Information                                                                                                                          | 53                                                             |  |  |  |

| 1   | MS T9                                         | 000 trar                                                                                    | nsputer                                                                                                                                                | 55                                                             |  |  |  |

| 1   | Intro                                         |                                                                                             |                                                                                                                                                        |                                                                |  |  |  |

|     |                                               | auction                                                                                     | 1                                                                                                                                                      | 56                                                             |  |  |  |

| 2   |                                               | auction                                                                                     | 1                                                                                                                                                      | 56                                                             |  |  |  |

|     | Prei                                          |                                                                                             | pin designations                                                                                                                                       | 56<br>58                                                       |  |  |  |

| 3   |                                               | iminary                                                                                     |                                                                                                                                                        |                                                                |  |  |  |

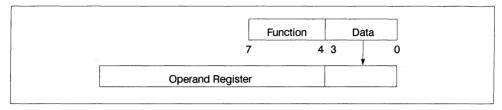

| 3   | Proc                                          | iminary<br>cessor .                                                                         | pin designations                                                                                                                                       | 58<br>60                                                       |  |  |  |

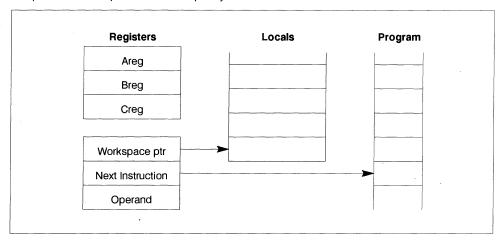

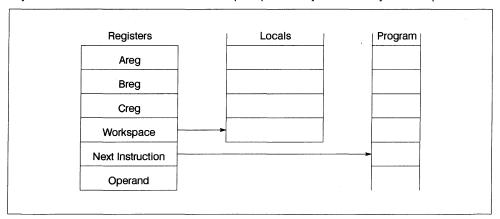

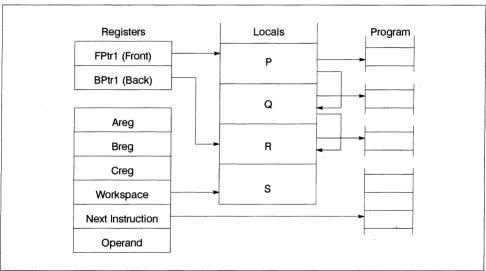

| 3   | <b>Proc</b> 3.1                               | iminary<br>cessor .                                                                         | pin designations                                                                                                                                       | <b>58 60</b> 60                                                |  |  |  |

| 3   | <b>Proc</b><br>3.1<br>3.2                     | iminary<br>cessor .<br>Register<br>Process                                                  | pin designations  rs  es and concurrency                                                                                                               | <b>58 60</b> 60 61                                             |  |  |  |

| 3   | 3.1<br>3.2<br>3.3                             | cessor . Register Process Priority                                                          | pin designations  rs  es and concurrency                                                                                                               | <b>58 60</b> 60 61 62                                          |  |  |  |

| 3   | <b>Proc</b><br>3.1<br>3.2                     | cessor . Register Process Priority                                                          | pin designations  rs  es and concurrency                                                                                                               | <b>58 60</b> 60 61                                             |  |  |  |

| 3   | 3.1<br>3.2<br>3.3                             | iminary  cessor .  Register  Process  Priority  Process  3.4.1                              | pin designations  TS  TS  TES  TES  TES  TES  TES  TES                                                                                                 | 58<br>60<br>60<br>61<br>62<br>63<br>63                         |  |  |  |

| 3   | 3.1<br>3.2<br>3.3<br>3.4                      | iminary  cessor .  Register  Process  Priority  Process  3.4.1                              | pin designations  rs  es and concurrency  types                                                                                                        | <b>58 60</b> 60 61 62 63 63 64                                 |  |  |  |

| 3   | 3.1<br>3.2<br>3.3                             | Register<br>Process<br>Priority<br>Process<br>3.4.1<br>3.4.2                                | pin designations  TS  TS  TES  TES  TES  TES  TES  TES                                                                                                 | 58<br>60<br>60<br>61<br>62<br>63<br>63                         |  |  |  |

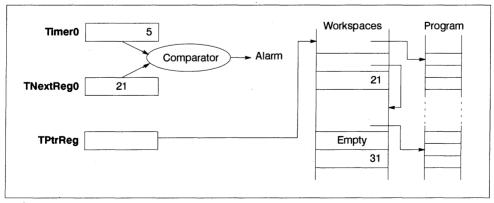

| 3   | 3.1<br>3.2<br>3.3<br>3.4                      | Register<br>Process<br>Priority<br>Process<br>3.4.1<br>3.4.2<br>Timers                      | pin designations  TS  TS  TS  TS  TS  TS  TS  TS  TS  T                                                                                                | <b>58 60</b> 60 61 62 63 63 64                                 |  |  |  |

| 3   | 3.1<br>3.2<br>3.3<br>3.4                      | Register<br>Process<br>Priority<br>Process<br>3.4.1<br>3.4.2<br>Timers<br>Block m           | pin designations  TS  Les and concurrency  Les types  G-processes: global trap-handling and debugging  L-processes: local error handling and debugging | 58<br>60<br>60<br>61<br>62<br>63<br>63<br>64<br>67             |  |  |  |

| 3   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Register<br>Process<br>Priority<br>Process<br>3.4.1<br>3.4.2<br>Timers<br>Block m<br>Semaph | pin designations  TS  TS  TS  TS  TS  TS  TS  TS  TS  T                                                                                                | 58<br>60<br>61<br>62<br>63<br>63<br>64<br>67<br>68             |  |  |  |

|     | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Register Process Priority Process 3.4.1 3.4.2 Timers Block m Semaph                         | pin designations  TS  TS  TS  TS  TS  TS  TS  TS  TS  T                                                                                                | 58<br>60<br>60<br>61<br>62<br>63<br>63<br>64<br>67<br>68<br>68 |  |  |  |

|     | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7 | Register<br>Process<br>Priority<br>Process<br>3.4.1<br>3.4.2<br>Timers<br>Block m<br>Semaph | pin designations  TS  TS  TS  TS  TS  TS  TS  TS  TS  T                                                                                                | 58<br>60<br>60<br>61<br>62<br>63<br>64<br>67<br>68<br>68       |  |  |  |

Viii Contents

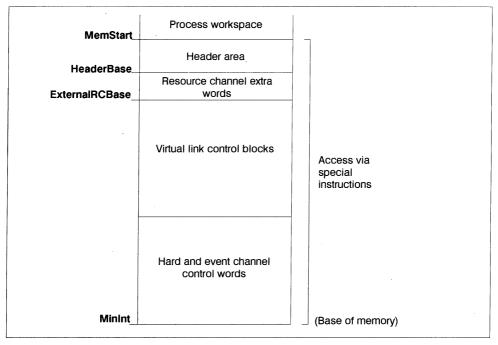

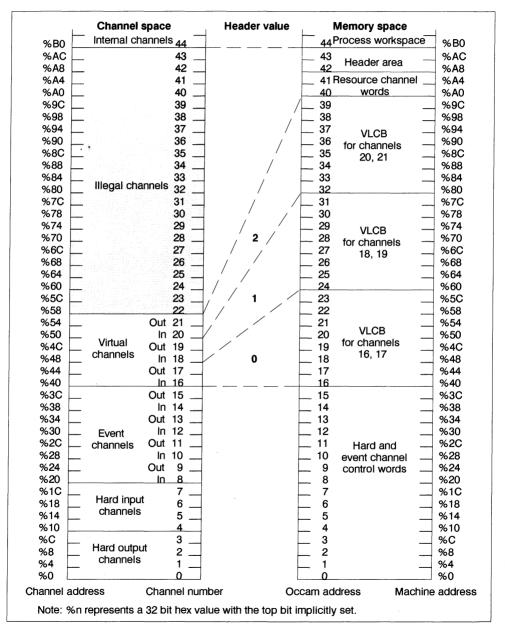

|   | 4.3      | Virtual link control blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 71       |

|---|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|   |          | 4.3.1 Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71       |

|   | 4.4      | VCP and CPU configuration registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72       |

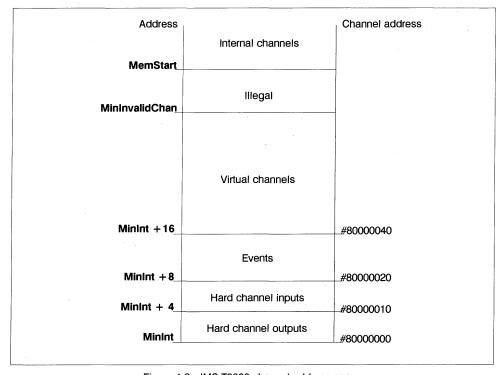

|   |          | 4.4.1 MemStart register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72       |

|   |          | 4.4.2 Minimum invalid virtual channel register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73       |

|   |          | 4.4.3 External resource channel base register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73       |

|   |          | 4.4.4 Header area base register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73       |

|   |          | 4.4.5 Header offset register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73       |

|   |          | 4.4.6 Packet header limit registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75       |

|   |          | 4.4.7 VCP command register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75       |

|   |          | 4.4.8 VCP status register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75       |

|   |          | 4.4.9 VCP link mode register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75<br>75 |

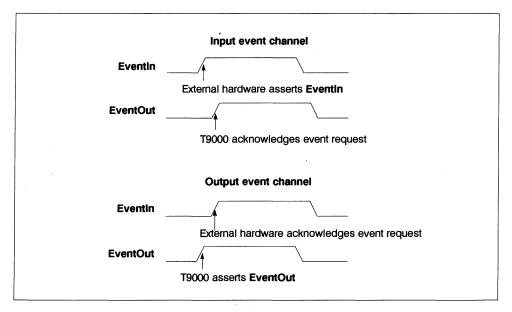

|   | 4.5      | 4.4.10 Event mode register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75<br>76 |

|   |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76       |

|   | 4.6      | Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 77       |

| _ |          | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| 5 | men      | nory management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 78       |

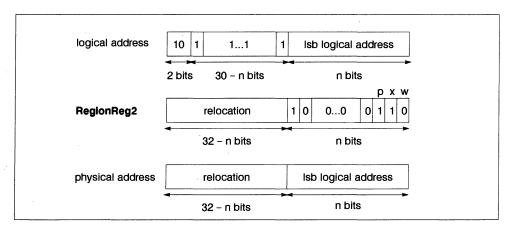

|   | 5.1      | Protection, stack extension, and logical to physical address translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78       |

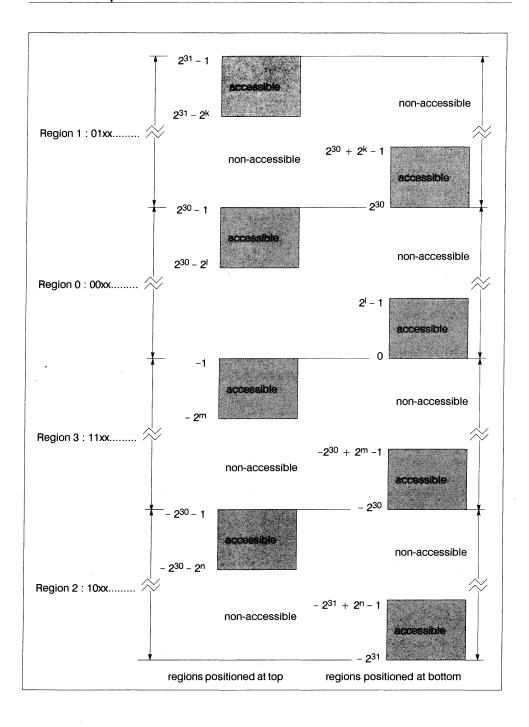

|   | 5.2      | Regions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 78       |

|   | 5.3      | Region descriptors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80       |

|   | 5.4      | Machine registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 81       |

|   | 5.5      | Debugging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 81       |

|   | 5.5      | Debugging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 01       |

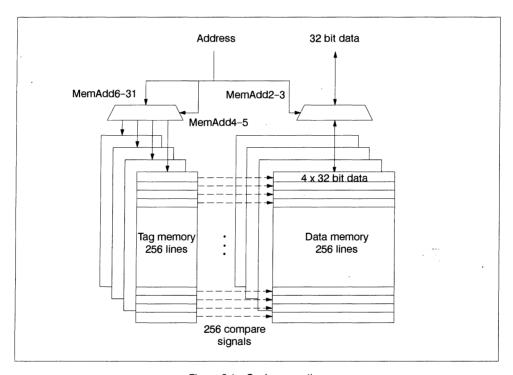

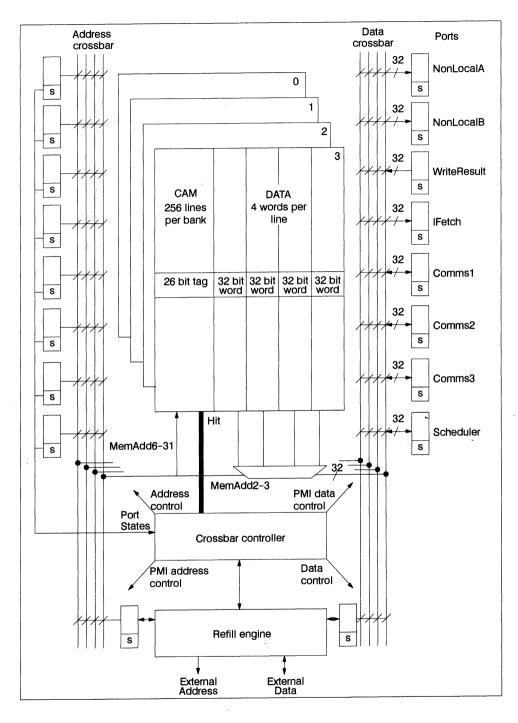

| 6 | Main     | Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82       |

| _ |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |