# TRANSPUTER DEVELOPMENT AND *i*q SYSTEMS DATABOOK

Second Edition 1991

INMOS is a member of the SGS-THOMSON Microelectronics Group

## **INMOS Databook series**

Transputer Databook

Military and Space Transputer Databook

Transputer Development and *iq* Systems Databook

Graphics Databook

Transputer Applications Notebook: Architecture and Software Transputer Applications Notebook: Systems and Performance

Copyright © INMOS Limited 1991

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate; however, no responsibility is assumed for its use, nor for any infringement of patents or other rights of third parties resulting from its use. No licence is granted under any patents, trademarks or other rights of INMOS.

(), Immos, IMS and occam are trademarks of INMOS Limited.

INMOS is a member of the SGS-THOMSON Microelectronics Group.

INMOS document number: 72 TRN 219 01

Printed at Redwood Press Limited, Melksham, Wiltshire

# **Contents overview**

| 1 | System Products overview . |  |

|---|----------------------------|--|

|---|----------------------------|--|

# **Development Systems**

## **Software Development Tools**

| 2 | OCCAM 2 Toolset         | 9  |

|---|-------------------------|----|

| 3 | ANSI C Toolset          | 23 |

| 4 | Glockenspiel C + +      | 35 |

| 5 | ANSI FORTRAN 77 Toolset | 43 |

| 6 | ALSYS Ada Compiler      | 53 |

|   |                         |    |

# **Transputer Development Kits**

| 7 | Transputer Development Kits | 63 |

|---|-----------------------------|----|

|   |                             |    |

# **Systems Software**

## **Board Support Software**

| 8  | IMS F000B VecTRAM library                       | 69  |

|----|-------------------------------------------------|-----|

| 9  | IMS F001B GPIB libraries                        | 83  |

| 10 | IMS F002B SCSI libraries                        | 93  |

| 11 | IMS F003A 2D Graphics libraries                 | 109 |

| 12 | IMS F007A DSP libraries and development tools   | 119 |

| 13 | Device Drivers and Motherboard Support Software | 127 |

| 14 | Network Support Software                        | 131 |

|    |                                                 |     |

# **Real Time Kernels and Operating Systems**

| 15 | VRTX32/T Real-time Executive | 139 |

|----|------------------------------|-----|

| 16 | C Executive                  | 141 |

# **Hardware Products**

### **TRAnsputer Modules (TRAMS)**

| 17 | IMS B401 32Kbyte TRAM  | 149 |

|----|------------------------|-----|

| 18 | IMS B416 64Kbyte TRAM  | 155 |

| 19 | IMS B410 160Kbyte TRAM | 161 |

| 20 | IMS B411 1Mbyte TRAM   | 167 |

| 21 | IMS B404 2Mbyte TRAM   | 173 |

| 22 | IMS B428 2Mbyte TRAM   | 181 |

| 23 | IMS B417 4Mbyte TRAM   | 189 |

| 24 | IMS B426 4Mbyte TRAM   | 197 |

| 25 | IMS B427 8Mbyte TRAM                       | 203 |

|----|--------------------------------------------|-----|

| 26 | IMS B408 Frame store TRAM                  | 209 |

| 27 | IMS B409 Display TRAM                      | 219 |

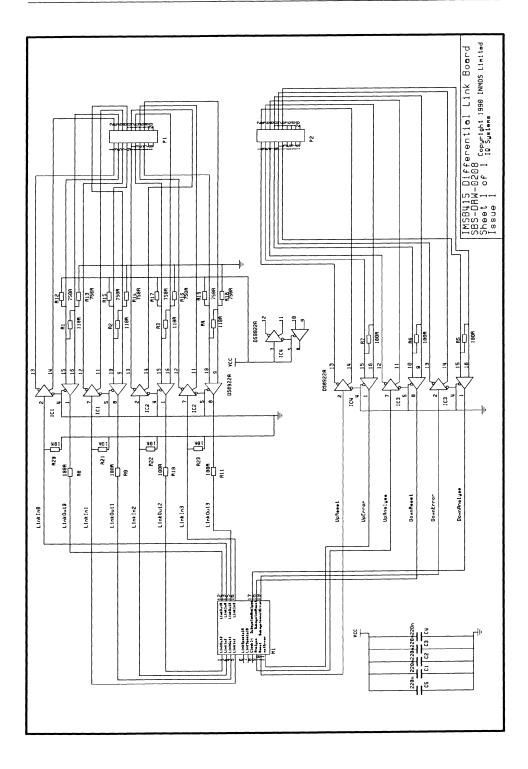

| 28 | IMS B415 Differential link buffer TRAM     | 229 |

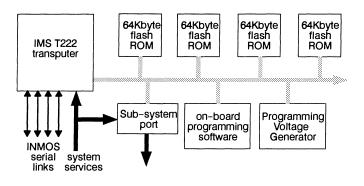

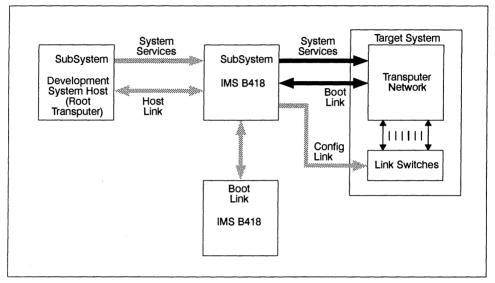

| 29 | IMS B418 Flash ROM TRAM                    | 237 |

| 30 | IMS B419 Graphics TRAM                     | 243 |

| 31 | IMS B420 Vector processing TRAM            | 255 |

| 32 | IMS B421 IEEE-488 GPIB TRAM                | 265 |

| 33 | IMS B422 SCSI TRAM                         | 283 |

| 34 | IMS B429 Video Image Processing TRAM (VIP) | 295 |

| 35 | IMS B430 Prototyping TRAM                  | 301 |

| 36 | IMS B431 Ethernet TRAM                     | 305 |

## Motherboards and other Standard Interface Boards

| 37 | IMS B008 IBM PC Motherboard         | 309 |

|----|-------------------------------------|-----|

| 38 | IMS B017 IBM PS/2 Motherboard       | 321 |

| 39 | IMS B014 VMEbus slave card          | 329 |

| 40 | IMS B016 VMEbus Master/Slave        | 333 |

| 41 | IMS B015 NEC 9800 series PC Board   | 353 |

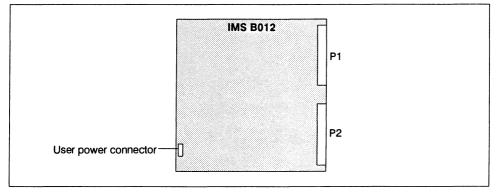

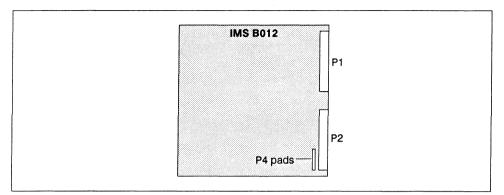

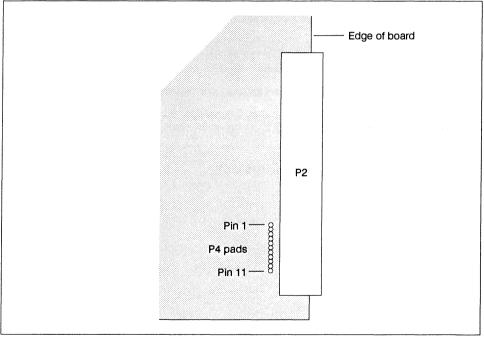

| 42 | IMS B012 Double extended eurocard   | 361 |

| 43 | IMS B018 TRAM motherboard           | 375 |

| 44 | IMS B300 Ethernet connection system | 377 |

## Associated Hardware Products

| 45 | IMS B250 VME Rack           | 381 |

|----|-----------------------------|-----|

| 46 | IMS CA12 Card Frame Adapter | 383 |

| 47 | Cables for Board Products   | 385 |

# **Application Notes**

| 48 | Dual-In-Line Transputer Modules (TRAMs)        | 389 |

|----|------------------------------------------------|-----|

| 49 | Module Motherboard Architecture                | 409 |

| 50 | Developing parallel C programs for transputers | 435 |

# **Appendices**

|       | А    | Quality and Reliability  | 463 |

|-------|------|--------------------------|-----|

|       | в    | Software Licensing       | 465 |

|       | С    | Product Reference Tables | 467 |

| Index | es   |                          |     |

|       | Inde | x by product number      | 471 |

|       | Inde | x by product name        | 472 |

# Contents

| Pr  | eface    |           |                                            | ii |

|-----|----------|-----------|--------------------------------------------|----|

| 1   | Syst     | tem Pro   | ducts overview                             | 1  |

|     | 1.1      | Introduc  | tion                                       | 2  |

|     |          |           |                                            |    |

|     | 1.2      |           | on and Quality                             | 2  |

|     | 1.3      | TRAMS     | (TRAnsputer Modules)                       | 3  |

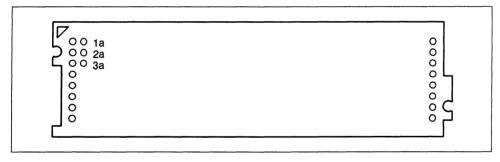

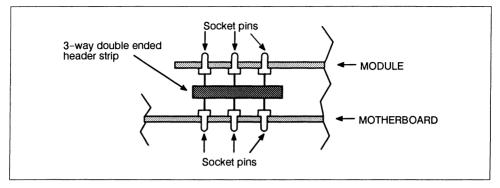

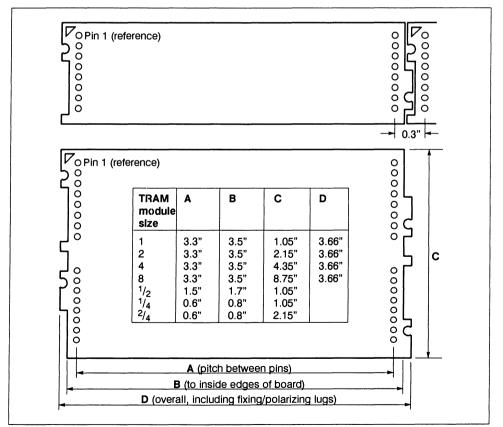

|     |          | 1.3.1     | Standard Interface                         | 3  |

|     |          | 1.3.2     | Upgradability                              | 3  |

|     |          | 1.3.3     | Flexibility                                | 4  |

|     |          | 1.3.4     | Evaluation                                 | 4  |

|     | 1.4      | Quality a | and Reliability                            | 4  |

| Dev | elopr    | ment S    | ystems                                     | 5  |

| S   | oftwa    | are Dev   | velopment Tools                            | 7  |

| 2   | occ      | am 2 To   | oolset                                     | 9  |

|     | 2.1      | Introduc  | tion                                       | 10 |

|     | 2.2      | Mapping   | g occam Programs Onto Transputer Networks  | 10 |

|     | 2.3      |           | Overview                                   | 14 |

|     |          | 2.3.1     | OCCam 2 development system                 | 14 |

|     |          | 2.3.1     | Libraries                                  | 15 |

|     |          | 2.0.2     |                                            | 15 |

|     |          |           | OCCAM compiler librarysnglmath.lib         | 15 |

|     |          |           | tbmaths.lib                                | 15 |

|     |          |           | string.lib                                 | 15 |

|     |          |           | hostio.lib                                 | 15 |

|     |          |           | streamio.lib                               | 15 |

|     |          |           | msdos.lib                                  | 15 |

|     |          |           | crc.lib                                    | 15 |

|     |          |           | convert.lib                                | 15 |

|     |          |           | xlink.lib                                  | 15 |

|     |          |           | debug.lib                                  | 15 |

|     |          | 2.3.3     | Mixed language programs                    | 16 |

|     |          | 2.3.4     | Debugging                                  | 16 |

|     |          |           | Interactive symbolic debugging             | 16 |

|     |          |           | Post-mortem symbolic debugging             | 16 |

|     |          |           | T425 simulation                            | 16 |

|     |          | 2.3.5     | Optimised code generation                  | 17 |

|     |          | 2.3.6     | Assembler inserts                          | 17 |

|     |          | 2.3.7     | D700 transputer development system support | 18 |

|     | <b>.</b> | 2.3.8     | Improvements over previous releases        | 18 |

|     | 2.4      |           | Toolset Product Components                 | 18 |

|     |          | 2.4.1     |                                            | 18 |

|     |          | 2.4.2     | Software Tools                             | 19 |

|     |          | 2.4.3     | Software libraries                         | 19 |

|     |          | 2.4.4     | Source code                                | 19 |

|   | 2.5  | Product        | t Variants                                                    | 19       |

|---|------|----------------|---------------------------------------------------------------|----------|

|   |      | 2.5.1          | IMS D7205 IBM PC and NEC PC version                           | 19       |

|   |      |                | Operating requirements                                        | 20       |

|   |      |                | Distribution media                                            | 20       |

|   |      | 2.5.2          | IMS D6205 VAX VMS version                                     | 20       |

|   |      |                | Operating requirements                                        | 20       |

|   |      |                | Distribution media                                            | 20       |

|   |      | 2.5.3          | IMS D5205 Sun 3 version, IMS D4205 Sun 4 version              | 20       |

|   |      |                | Operating requirements                                        | 21       |

|   |      |                | Distribution media                                            | 21       |

|   | 2.6  |                | ng Information                                                | 21       |

|   | 2.7  | Problem        | n Reporting And Field Support                                 | 21       |

| 3 | ANS  | I C Tool       | lset                                                          | 23       |

|   | 3.1  | Introduc       | tion                                                          | 24       |

|   | 3.2  | Product        | Overview                                                      | 24       |

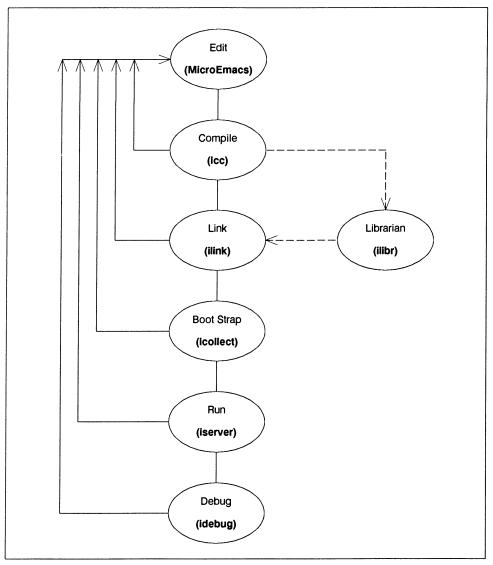

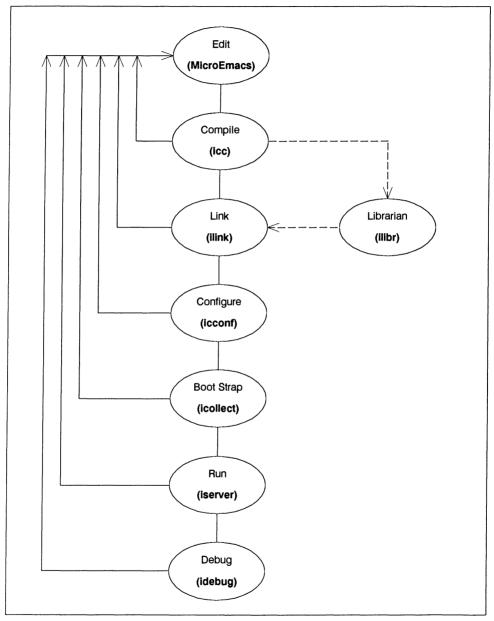

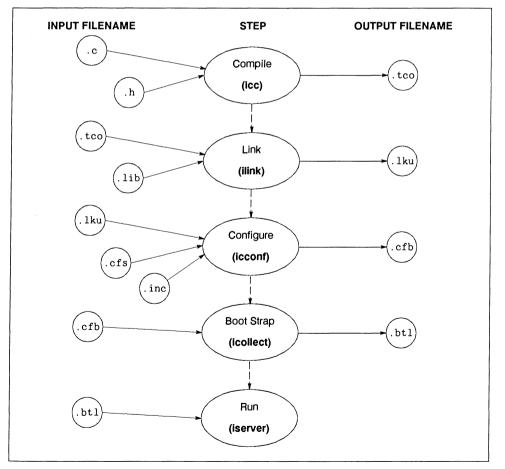

|   |      | 3.2.1          | How programs are built                                        | 24       |

|   |      | 3.2.2          | ANSI C compilation system                                     | 24       |

|   |      |                | Compiler operation                                            | 24       |

|   |      |                | ANSI conformance                                              | 24       |

|   |      |                | Optimised code generation                                     | 25       |

|   |      |                | Libraries                                                     | 25       |

|   |      |                | Mixed language programs                                       | 26       |

|   |      |                | Assembler inserts                                             | 26       |

|   |      | 3.2.3          | Target systems                                                | 27       |

|   |      | 3.2.4          | Support for parallelism                                       | 28       |

|   |      | 3.2.5          |                                                               | 30       |

|   |      |                | T425 simulation                                               | 30<br>30 |

|   |      |                | Interactive symbolic debugging Post-mortem symbolic debugging | 30       |

|   |      | 3.2.6          | Improvements over previous releases                           | 32       |

|   | 3.3  |                | Toolset Product Components                                    | 32       |

|   | 0.0  |                |                                                               | 32       |

|   |      | 3.3.1<br>3.3.2 |                                                               | 32       |

|   |      | 3.3.2          | Software Tools                                                | 33       |

|   | 3.4  | Product        |                                                               | 33       |

|   | 0.4  |                |                                                               | 33       |

|   |      | 3.4.1          | IMS D7214 IBM PC version                                      | 33       |

|   |      |                | Operating requirements<br>Distribution media                  | 33       |

|   |      | 3.4.2          | IMS D6214 VAX VMS version                                     | 33       |

|   |      | 0.4.2          | Operating requirements                                        | 34       |

|   |      |                | Distribution media                                            | 34       |

|   |      | 3.4.3          | IMS D5214 Sun 3 version, IMS D4214 Sun 4 version              | 34       |

|   |      | 0.1.0          | Operating requirements                                        | 34       |

|   |      |                | Distribution media                                            | 34       |

|   | 3.5  | Error Rep      | porting And Field Support                                     | 34       |

| 4 | Gloc | kenspie        | el C+ +                                                       | 35       |

|   | 4.1  | Product (      | Overview                                                      | 36       |

|   |      | 4.1.1          | C+ +                                                          | 36       |

|   |      | 1.1.1          | ••••                                                          | 50       |

\_\_\_\_\_

|   | 4.2               | 4.1.2<br>Glocken                                                                                                         | Use with the INMOS ANSI C toolset                                                                                                                                                                                                                                                                                | 36<br>37                                                                                                                   |

|---|-------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|   |                   | 4.2.1<br>4.2.2                                                                                                           | Documentation                                                                                                                                                                                                                                                                                                    | 37<br>37                                                                                                                   |

|   |                   | 4.2.3                                                                                                                    | Software Libraries                                                                                                                                                                                                                                                                                               | 37                                                                                                                         |

|   | 4.3               |                                                                                                                          | Variants                                                                                                                                                                                                                                                                                                         | 37                                                                                                                         |

|   | 7.0               | 4.3.1                                                                                                                    |                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

|   |                   | 4.3.1                                                                                                                    | IMS D7217 IBM PC version<br>Cross-development operating requirements                                                                                                                                                                                                                                             | 37<br>37                                                                                                                   |

|   |                   |                                                                                                                          | Native development operating requirements                                                                                                                                                                                                                                                                        | 38                                                                                                                         |

|   |                   |                                                                                                                          | Distribution media                                                                                                                                                                                                                                                                                               | 38                                                                                                                         |

|   |                   | 4.3.2                                                                                                                    | IMS D6214 VAX VMS version                                                                                                                                                                                                                                                                                        | 38                                                                                                                         |

|   |                   |                                                                                                                          | Cross-development operating requirements                                                                                                                                                                                                                                                                         | 38                                                                                                                         |

|   |                   |                                                                                                                          | Native development operating requirements                                                                                                                                                                                                                                                                        | 38                                                                                                                         |

|   |                   |                                                                                                                          | Distribution media                                                                                                                                                                                                                                                                                               | 38                                                                                                                         |

|   |                   |                                                                                                                          | Licensing variants                                                                                                                                                                                                                                                                                               | 38                                                                                                                         |

|   |                   | 4.3.3                                                                                                                    | IMS D5217 Sun 3 version                                                                                                                                                                                                                                                                                          | 39                                                                                                                         |

|   |                   |                                                                                                                          | Cross-development operating requirements                                                                                                                                                                                                                                                                         | 39                                                                                                                         |

|   |                   |                                                                                                                          | Native development operating requirements                                                                                                                                                                                                                                                                        | 39                                                                                                                         |

|   |                   |                                                                                                                          | Distribution media                                                                                                                                                                                                                                                                                               | 40                                                                                                                         |

|   |                   |                                                                                                                          | Licensing variants                                                                                                                                                                                                                                                                                               | 40                                                                                                                         |

|   |                   | 4.3.4                                                                                                                    | IMS D4217 Sun 4 version                                                                                                                                                                                                                                                                                          | 40                                                                                                                         |

|   |                   |                                                                                                                          | Cross-development operating requirements                                                                                                                                                                                                                                                                         | 40                                                                                                                         |

|   |                   |                                                                                                                          | Native development operating requirements                                                                                                                                                                                                                                                                        | 40                                                                                                                         |

|   |                   |                                                                                                                          | Licensing variants                                                                                                                                                                                                                                                                                               | 40                                                                                                                         |

|   |                   | Fror Dor                                                                                                                 |                                                                                                                                                                                                                                                                                                                  | 41                                                                                                                         |

|   | 4.4               | Elloi net                                                                                                                | borting And Field Support                                                                                                                                                                                                                                                                                        | 41                                                                                                                         |

|   |                   |                                                                                                                          |                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

| 5 |                   |                                                                                                                          | AN 77 Toolset                                                                                                                                                                                                                                                                                                    | 43                                                                                                                         |

| 5 | 5.1               |                                                                                                                          | RAN 77 Toolset                                                                                                                                                                                                                                                                                                   | <b>43</b><br>44                                                                                                            |

| 5 |                   | Introducti                                                                                                               |                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

| 5 | 5.1               | Introducti                                                                                                               | ion                                                                                                                                                                                                                                                                                                              | 44                                                                                                                         |

| 5 | 5.1               | Introducti<br>Product (                                                                                                  | ion<br>Overview                                                                                                                                                                                                                                                                                                  | 44<br>44                                                                                                                   |

| 5 | 5.1               | Introducti<br>Product (<br>5.2.1                                                                                         | ion                                                                                                                                                                                                                                                                                                              | 44<br>44<br>44                                                                                                             |

| 5 | 5.1               | Introducti<br>Product (<br>5.2.1                                                                                         | ion<br>Dverview<br>How programs are built<br>ANSI FORTRAN compilation system<br>Compiler operation<br>ANSI conformance                                                                                                                                                                                           | 44<br>44<br>44<br>44<br>44                                                                                                 |

| 5 | 5.1               | Introducti<br>Product (<br>5.2.1                                                                                         | ion<br>Dverview<br>How programs are built<br>ANSI FORTRAN compilation system<br>Compiler operation<br>ANSI conformance<br>Optimised code generation                                                                                                                                                              | 44<br>44<br>44<br>44<br>44<br>44<br>44                                                                                     |

| 5 | 5.1               | Introducti<br>Product (<br>5.2.1                                                                                         | ion<br>Dverview<br>How programs are built<br>ANSI FORTRAN compilation system<br>Compiler operation<br>ANSI conformance<br>Optimised code generation<br>Run-Time System                                                                                                                                           | 44<br>44<br>44<br>44<br>44<br>44<br>45                                                                                     |

| 5 | 5.1               | Introducti<br>Product (<br>5.2.1<br>5.2.2                                                                                | ion<br>Dverview<br>How programs are built<br>ANSI FORTRAN compilation system<br>Compiler operation<br>ANSI conformance<br>Optimised code generation<br>Run-Time System<br>Mixed language programs                                                                                                                | 44<br>44<br>44<br>44<br>44<br>44<br>45<br>45                                                                               |

| 5 | 5.1               | Introducti<br>Product (<br>5.2.1<br>5.2.2<br>5.2.3                                                                       | ion<br>Dverview<br>How programs are built<br>ANSI FORTRAN compilation system<br>Compiler operation<br>ANSI conformance<br>Optimised code generation<br>Run-Time System<br>Mixed language programs<br>Target systems                                                                                              | 44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>45                                                                         |

| 5 | 5.1               | Introducti<br>Product (<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.3<br>5.2.4                                                     | ion Dverview How programs are built ANSI FORTRAN compilation system Compiler operation ANSI conformance Optimised code generation Run-Time System Mixed language programs Target systems Support for parallelism                                                                                                 | 44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>46<br>46                                                                   |

| 5 | 5.1               | Introducti<br>Product (<br>5.2.1<br>5.2.2<br>5.2.3                                                                       | ion<br>Dverview<br>How programs are built<br>ANSI FORTRAN compilation system<br>Compiler operation<br>ANSI conformance<br>Optimised code generation<br>Run-Time System<br>Mixed language programs<br>Target systems<br>Support for parallelism<br>Debugging                                                      | 44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>46<br>46<br>48                                                             |

| 5 | 5.1               | Introducti<br>Product (<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.3<br>5.2.4                                                     | ion                                                                                                                                                                                                                                                                                                              | 44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>46<br>46<br>48<br>48                                                       |

| 5 | 5.1               | Introducti<br>Product (<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.3<br>5.2.4                                                     | ion<br>Dverview<br>How programs are built<br>ANSI FORTRAN compilation system<br>Compiler operation<br>ANSI conformance<br>Optimised code generation<br>Run-Time System<br>Mixed language programs<br>Target systems<br>Support for parallelism<br>Debugging<br>T425 simulation<br>Interactive symbolic debugging | 44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>46<br>46<br>48<br>48<br>48                                                 |

| 5 | 5.1               | Introducti<br>Product (<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                                                     | ion                                                                                                                                                                                                                                                                                                              | 44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>46<br>46<br>46<br>48<br>48<br>48<br>48<br>49                               |

| 5 | 5.1<br>5.2        | Introducti<br>Product (<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6                                            | ion                                                                                                                                                                                                                                                                                                              | 44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>46<br>46<br>48<br>48<br>48<br>48<br>49<br>50                               |

| 5 | 5.1               | Introducti<br>Product (<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>ANSI FOR                                | ion                                                                                                                                                                                                                                                                                                              | 44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>46<br>46<br>46<br>48<br>48<br>48<br>49<br>50<br>50                         |

| 5 | 5.1<br>5.2        | Introducti<br>Product (<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>ANSI FOR<br>5.3.1                       | ion                                                                                                                                                                                                                                                                                                              | 44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>46<br>46<br>46<br>48<br>48<br>48<br>48<br>49<br>50<br>50<br>50             |

| 5 | 5.1<br>5.2<br>5.3 | Introducti<br>Product (<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>ANSI FOR<br>5.3.1<br>5.3.2              | ion                                                                                                                                                                                                                                                                                                              | 44<br>44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>46<br>46<br>46<br>48<br>48<br>48<br>48<br>49<br>50<br>50<br>50<br>50 |

| 5 | 5.1<br>5.2        | Introducti<br>Product (<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>ANSI FOF<br>5.3.1<br>5.3.2<br>Product V | ion                                                                                                                                                                                                                                                                                                              | 44<br>44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>46<br>46<br>48<br>48<br>48<br>49<br>50<br>50<br>50<br>50<br>50       |

| 5 | 5.1<br>5.2<br>5.3 | Introducti<br>Product (<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>ANSI FOR<br>5.3.1<br>5.3.2              | ion                                                                                                                                                                                                                                                                                                              | 44<br>44<br>44<br>44<br>44<br>44<br>44<br>45<br>45<br>46<br>46<br>46<br>48<br>48<br>48<br>48<br>49<br>50<br>50<br>50<br>50 |

|    |       | 5.4.2     | IMS D6216 VAX VMS version                                    | 51 |

|----|-------|-----------|--------------------------------------------------------------|----|

|    |       |           | Operating requirements                                       | 51 |

|    |       |           | Distribution media                                           | 51 |

|    |       | 5.4.3     | IMS D5216 Sun 3 version, IMS D4214 Sun 4 version             | 52 |

|    |       |           | Operating requirements                                       | 52 |

|    |       |           | Distribution media                                           | 52 |

|    | 5.5   | Error Re  | porting And Field Support                                    | 52 |

|    |       |           |                                                              |    |

| 6  | ALS'  | VS ∆da    | Compiler                                                     | 53 |

| •  |       |           |                                                              |    |

|    | 6.1   |           | Overview                                                     | 54 |

|    | 6.2   | Product   | Highlights                                                   | 54 |

|    |       | 6.2.1     | Supports easy implementation of distributed Ada applications | 54 |

|    |       | 6.2.2     | Efficient sharing of Ada Libraries                           | 54 |

|    |       | 6.2.3     | Generates high performance, compact application code         | 54 |

|    |       |           | Ada Code Generation                                          | 54 |

|    |       |           | Floating point support                                       | 54 |

|    |       |           | Ada Run Time                                                 | 54 |

|    |       |           | Supports low level programming features                      | 54 |

|    |       | 6.2.4     | Increased development productivity                           | 55 |

|    |       | 6.2.5     | Advanced debugging support                                   | 55 |

|    |       | 6.2.6     | Ada predefined Input and Output                              | 55 |

|    |       | 6.2.7     | Transfers the loadable Ada program to the target             | 55 |

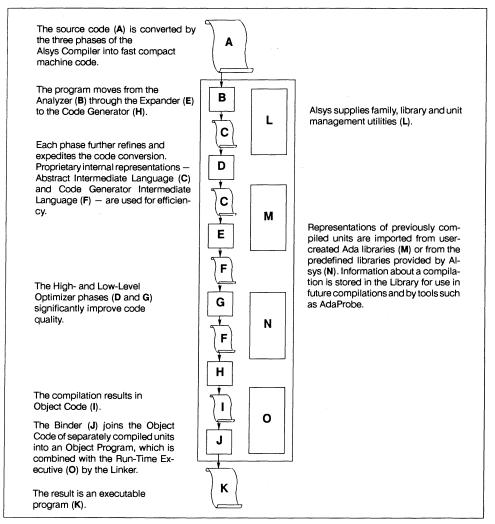

|    | 6.3   | The Alsy  | s Ada Compilation System                                     | 55 |

|    | 6.4   | Ada Con   | npiler Toolset Product Components                            | 55 |

|    |       | 6.4.1     |                                                              | 55 |

|    |       |           | User's Guide                                                 | 55 |

|    |       |           | Project Development Guide                                    | 55 |

|    |       |           | Installation Guide                                           | 55 |

|    |       |           | Ada Reference Manual                                         | 55 |

|    |       |           | Appendix F                                                   | 56 |

|    |       |           | Application Developer's Guide                                | 56 |

|    |       | 6.4.2     | Software Components                                          | 57 |

|    | 6.5   | Product V | Variants                                                     | 57 |

|    |       | 6.5.1     | IBM PC Alsys Ada Compiler                                    | 57 |

|    |       |           | Operating requirements                                       | 57 |

|    |       |           | Distribution media                                           | 57 |

|    |       | 6.5.2     | VAX VMS Alsys Ada Compiler                                   | 57 |

|    |       |           | Operating requirements                                       | 57 |

|    |       |           | Distribution media                                           | 57 |

|    | 6.6   | Custome   | r Support And Upgrade Services                               | 58 |

|    | 6.7   | Alsvs An  | d Ada                                                        | 58 |

|    | 0.7   | /         |                                                              |    |

|    |       |           | Alsys Offices and Addresses                                  | 59 |

| Tr | ansp  | uter D    | evelopment Kits                                              | 61 |

|    | -     |           |                                                              |    |

| 7  | Trans | sputer C  | Development Kits                                             | 63 |

| -  |       | •         |                                                              |    |

|    | 7.1   | Transpute | er Development Kits                                          | 63 |

| Sy | /st | ems  | Softwa           | are                                                                                            | 65       |

|----|-----|------|------------------|------------------------------------------------------------------------------------------------|----------|

|    | B   | oard | Suppo            | ort Software                                                                                   | 67       |

|    | 8   | IMC  |                  | /ecTRAM library                                                                                | 69       |

|    | 0   |      |                  |                                                                                                |          |

|    |     | 8.1  | Introduct        | lion                                                                                           | 70       |

|    |     | 8.2  | Product          | Overview                                                                                       | 70       |

|    |     | 8.3  | Using IM         | IS F000B                                                                                       | 70       |

|    |     |      | 8.3.1            | Incorporation into a C program                                                                 | 72       |

|    |     |      | 8.3.2            | Incorporation into an OCCam program                                                            | 72       |

|    |     | 8.4  | Supplied         | I Routines                                                                                     | 73       |

|    |     |      | 8.4.1            | Vector Absolute Value - Real                                                                   | 74       |

|    |     |      | 8.4.2            | Vector Addition – Real                                                                         | 74       |

|    |     |      | 8.4.3            | Vector Compare – Real                                                                          | 74       |

|    |     |      | 8.4.4            | Disable Co-processor Error Flags                                                               | 74       |

|    |     |      | 8.4.5            | Vector Division - Real                                                                         | 75       |

|    |     |      | 8.4.6            | Vector Dot Product – Complex                                                                   | 75       |

|    |     |      | 8.4.7            | Vector Dot Product - Real                                                                      | 75       |

|    |     |      | 8.4.8            | Enable Co-processor Error Interrupts                                                           | 75       |

|    |     |      | 8.4.9            | Fast Fourier Transform – Complex                                                               | 76       |

|    |     |      | 8.4.10           | Finite Impulse Response (FIR) Filter                                                           | 76       |

|    |     |      | 8.4.11           | Vector Floating Point to Integer (16-bit) Conversion.                                          | 76       |

|    |     |      | 8.4.12           | Infinite Impulse Response (IIR) Filter – Complex.                                              | 77       |

|    |     |      | 8.4.13           | Infinite Impulse Response (IIR) Filter – Real.                                                 | 77       |

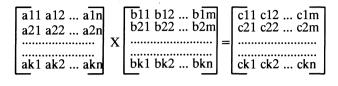

|    |     |      | 8.4.14           | Matrix Multiplication - Complex                                                                | 77       |

|    |     |      | 8.4.15           | Matrix Multiplication – Real                                                                   | 78       |

|    |     |      | 8.4.16<br>8.4.17 | Inverse Fast Fourier Transform – Complex                                                       | 78<br>78 |

|    |     |      | 8.4.17<br>8.4.18 | Vector Integer(16-bit) to 32-bit floating-point Conversion<br>Vector Log to the base 10 – Real | 78       |

|    |     |      | 8.4.19           | Vector Magnitude – Complex                                                                     | 79       |

|    |     |      | 8.4.20           | Vector Magnitude – Complex                                                                     | 79       |

|    |     |      | 8.4.21           | Find the Element with the Maximum Value and Its Position – Real                                | 79       |

|    |     |      | 8.4.22           | Vector Mean – Real                                                                             | 79       |

|    |     |      | 8.4.23           | Find the Element with the Minimum Value and Its Position – Real                                | 79       |

|    |     |      | 8.4.24           | Vector Move – Bytes                                                                            | 80       |

|    |     |      | 8.4.25           | Vector Move – Words (32-bit)                                                                   | 80       |

|    |     |      | 8.4.26           | Vector Multiply - Complex                                                                      | 80       |

|    |     |      | 8.4.27           | Vector Multiply - Real                                                                         | 80       |

|    |     |      | 8.4.28           | Vector Power - Real                                                                            | 80       |

|    |     |      | 8.4.29           | Modify Co-processor Rounding Mode                                                              | 81       |

|    |     |      | 8.4.30           | Vector Scale - Real                                                                            | 81       |

|    |     |      | 8.4.31           | Vector Square Root - Real                                                                      | 81       |

|    |     |      | 8.4.32           | Vector Subtract - Real                                                                         | 81       |

|    |     | 8.5  | Environm         | ent                                                                                            | 82       |

|    |     | 8.6  | IMS F000         | B Product Components                                                                           | 82       |

|    |     |      | 8.6.1            | Distribution media                                                                             | 82       |

|    |     |      | 8.6.2            | Documentation                                                                                  | 82       |

|    |     | 8.7  | Error Rep        | orting And Field Support                                                                       | 82       |

|    |     | 8.8  | Reference        | es                                                                                             | 82       |

| 9  | IMS      | F001B GPIB libraries                                                            | 83       |

|----|----------|---------------------------------------------------------------------------------|----------|

|    | 9.1      | Introduction                                                                    | 84       |

|    | 9.2      | Product Overview                                                                | 84       |

|    |          | 9.2.1 IMS F001B command format                                                  | 85       |

|    |          | Summary of the IMS F001B commands                                               | 86       |

|    | <u>.</u> | 9.2.2 Using IMS F001B                                                           | 87<br>92 |

|    | 9.3      |                                                                                 |          |

|    | 9.4      | IMS F001B Product Components                                                    | 92       |

|    |          | 9.4.1 Distribution media                                                        | 92<br>92 |

|    | 9.5      | Error Reporting And Field Support                                               | 92       |

|    | 0.0      |                                                                                 | 02       |

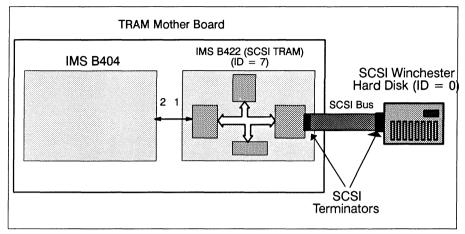

| 10 | IMS      | F002B SCSI libraries                                                            | 93       |

|    | 10.1     | Introduction                                                                    | 94       |

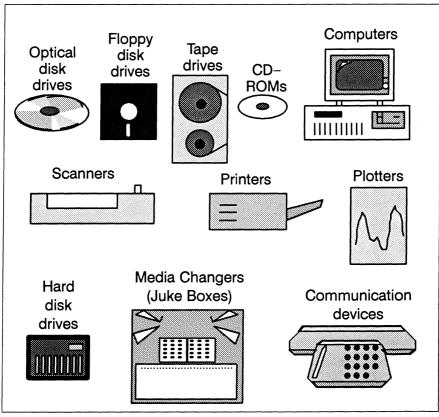

|    |          | 10.1.1 SCSI overview                                                            | 94       |

|    | 10.2     | Product Overview                                                                | 95       |

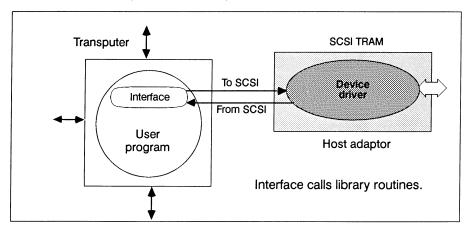

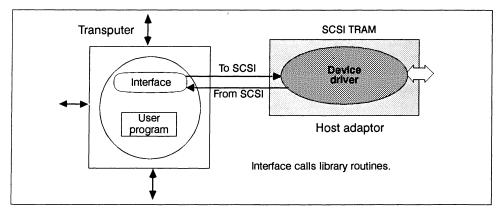

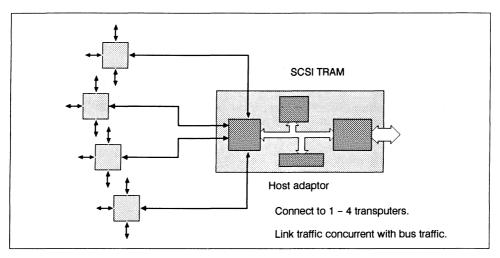

|    |          | 10.2.1 IMS B422 Device Driver.                                                  | 95       |

|    |          | 10.2.2 Initialisation Interface                                                 | 95       |

|    |          | 10.2.3 Initiator Mode Interface.                                                | 96       |

|    |          | Common Command Set                                                              | 96<br>97 |

|    |          | 10.2.4         Target Mode Interface.           10.2.5         Diagnostic tests | 97<br>98 |

|    |          | 10.2.6 Initialisation Interfaces                                                | 98       |

|    | 10.3     | Incorporation into a user program                                               | 98       |

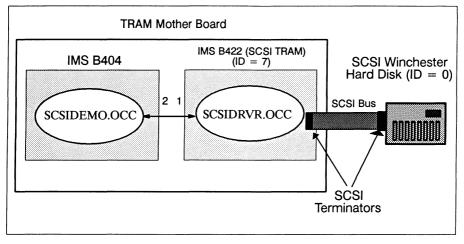

|    |          | Incorporation of initiator mode into a user program                             | 98       |

|    | 10.4     | Simple Initiator mode example.                                                  | 99       |

|    |          | Configuration                                                                   | 99       |

|    | 10.5     | List of supplied procedures.                                                    | 103      |

|    | 10.6     | Performance                                                                     | 104      |

|    | 10.7     | Compatibility.                                                                  | 105      |

|    | 10.8     | Operating environment                                                           | 106      |

|    | 10.9     | IMS F002B Product Components                                                    | 106      |

|    |          | 10.9.1 Distribution media                                                       | 106      |

|    | 10.10    | 10.9.2 Documentation                                                            | 106      |

|    |          | Error Reporting And Field Support                                               | 107      |

|    | 10.11    | References                                                                      | 107      |

| 11 | IMS      | F003A 2D Graphics libraries                                                     | 109      |

|    | 11.1     |                                                                                 | 110      |

|    | 11.2     | Product Overview                                                                | 110      |

|    |          | 11.2.1 Summary of the IMS F003 commands                                         | 111      |

|    | 11.3     | Using IMS F003                                                                  | 115      |

|    | 11.4     | IMS F003 Product Components                                                     | 118      |

|    |          | 11.4.1 Distribution media                                                       | 118      |

|    |          | 11.4.2 Documentation                                                            | 118      |

|    |          | 11.4.3 Operating environment                                                    | 118      |

|    | 11.5     | Error Reporting And Field Support                                               | 118      |

X

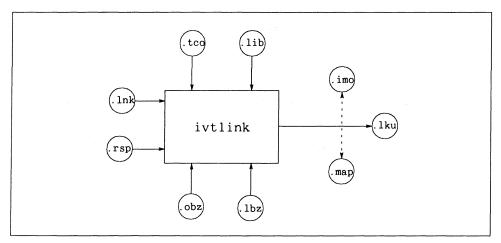

| 12 IMS  | F007A DSP libraries and development tools                                                                                        | 119        |

|---------|----------------------------------------------------------------------------------------------------------------------------------|------------|

| 12.1    |                                                                                                                                  | 120        |

| 12.2    | Product Overview                                                                                                                 | 120        |

|         | 12.2.1 Library usage                                                                                                             | 120        |

|         | 12.2.2 intgen - VecTRAM Interface Generation Utility                                                                             | 121        |

|         | Running the intgen utility                                                                                                       | 121        |

| 12.3    | 12.2.3 ivtlink - VecTRAM Linker                                                                                                  | 122<br>123 |

| 12.3    | Environment                                                                                                                      | 123        |

| 12.4    |                                                                                                                                  | 120        |

| 12.5    | IMS F007A Product Components                                                                                                     |            |

|         | 12.5.1       Distribution media         12.5.2       Documentation                                                               | 126<br>126 |

| 12.6    | Error Reporting And Field Support                                                                                                | 126        |

| 12.7    | References                                                                                                                       | 126        |

| 12.8    | Ordering Information                                                                                                             | 126        |

| 12.0    |                                                                                                                                  | .=0        |

| 13 Devi | ce Drivers and Motherboard Support Software                                                                                      | 127        |

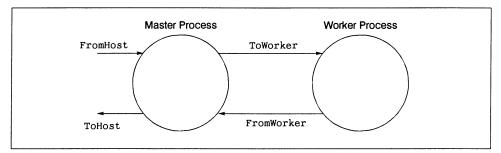

| 13.1    | Product overview                                                                                                                 | 128        |

|         | 13.1.1 Device driver                                                                                                             | 128        |

|         | 13.1.2 INMOS server                                                                                                              | 128        |

|         | 13.1.3 Transputer mapping software                                                                                               | 128        |

| 13.2    | 13.1.4     Switch setting support       Product components summary                                                               | 129<br>129 |

| 10.2    | 13.2.1 Documentation                                                                                                             | 129        |

|         | User manual                                                                                                                      | 129        |

|         | 13.2.2 Software                                                                                                                  | 129        |

|         | Device driver                                                                                                                    | 129        |

|         | INMOS iserver (with sources)                                                                                                     | 129        |

|         | Transputer mapping tool                                                                                                          | 129<br>129 |

| 13.3    | Product variants                                                                                                                 | 129        |

|         | 13.3.1 General operating requirements                                                                                            | 129        |

|         | 13.3.2 Distribution media                                                                                                        | 129        |

|         | IMS S217                                                                                                                         | 129        |

|         | IMS S308                                                                                                                         | 129        |

|         | IMS S708                                                                                                                         | 129        |

| 13.4    | IMS S514 OEM support                                                                                                             | 129<br>130 |

| 10.4    |                                                                                                                                  | 100        |

| 14 Netw | vork Support Software                                                                                                            | 131        |

| 14.1    | Introduction                                                                                                                     | 132        |

| 14.2    | Product Overview                                                                                                                 | 132        |

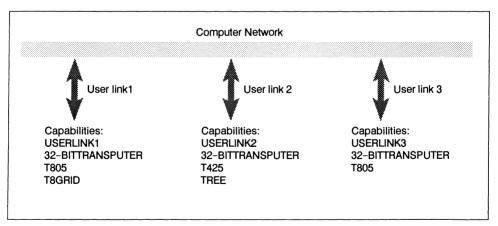

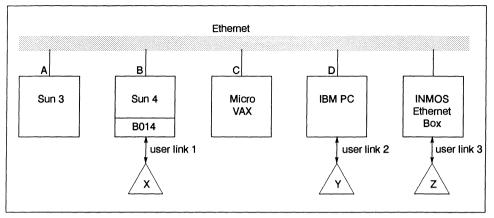

|         | 14.2.1 Connecting transputers to computer networks                                                                               | 132        |

|         | 14.2.2 Capabilities                                                                                                              | 132        |

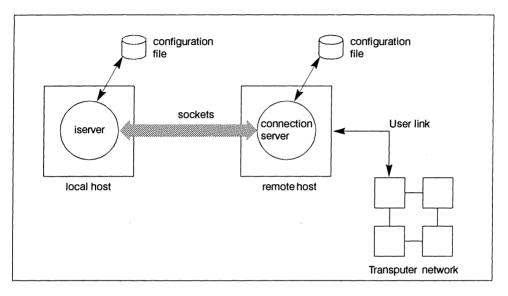

|         | 14.2.3 System configuration                                                                                                      | 133        |

|         | 14.2.4 Support for INMOS development tools                                                                                       | 133        |

|         | 14.2.5       Support for INMOS Ethernet connection system (IMS B300)         14.2.6       Support for mixed networks of machines | 133<br>133 |

| 14.3    | Product Component Summary                                                                                                        | 134        |

xi

|          | 14.3.1    | Documentation                            | 134<br>134 |

|----------|-----------|------------------------------------------|------------|

|          | 14.3.2    | User Manual                              | 134        |

|          | 14.0.2    | Extended INMOS iserver                   | 134        |

|          |           | Connection server                        | 134        |

|          |           | INMOS Ethernet box configuration program | 134        |

| 14.4     | Product V | Variants                                 | 134        |

|          | 14.4.1    | IMS S707 IBM PC                          | 134        |

|          |           | Operating requirements                   | 134        |

|          |           | Boards supported                         | 135        |

|          |           | Distribution media                       | 135        |

|          | 14.4.2    | IMS S607 VAX VMS                         | 135        |

|          |           | Operating requirements                   | 135        |

|          |           | Distribution media                       | 135        |

|          | 14.4.3    | IMS S507 Sun 3 and Sun 4                 | 135        |

|          |           | Operating requirements                   | 135<br>135 |

|          |           | Boards supported                         | 135        |

| 14.5     | Error Ber | porting And Field Support                | 135        |

| 14.5     | Enormor   |                                          | 100        |

| Roal T   | ima Ka    | rnels and Operating Systems              | 137        |

| neari    |           |                                          | 107        |

|          |           |                                          |            |

| 15 VRT   | X32/T Re  | eal-time Executive                       | 139        |

| 15.1     | Overview  | /                                        | 140        |

|          |           | Deterministic Performance                | 140        |

|          |           | Distributed Environment                  | 140        |

|          |           | Support                                  | 140        |

|          |           |                                          |            |

| 16 C Ex  |           | ••••••                                   | 141        |

| 16.1     | C Execut  | ive For The Transputer                   | 142        |

| 16.2     | Benefits  | Of C Executive                           | 142        |

| 16.3     | CE-VIEW   |                                          | 143        |

| 16.4     |           | ntation                                  | 143        |

|          |           |                                          |            |

| 16.5     |           | ty                                       | 143        |

| 16.6     | -         | ]                                        | 143        |

| 16.7     | How To C  | Order                                    | 144        |

|          |           |                                          |            |

| Hardware | e Produ   | cts                                      | 145        |

|          |           |                                          |            |

| TDAne    | nutor N   | Nodules (TRAMS)                          | 1/7        |

| INAIIS   | puter n   |                                          | 147        |

|          |           |                                          |            |

| 17 IMS   | B401 32   | Kbyte TRAM                               | 149        |

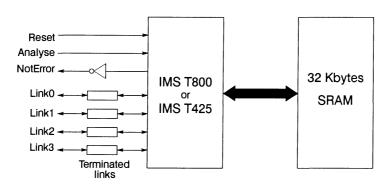

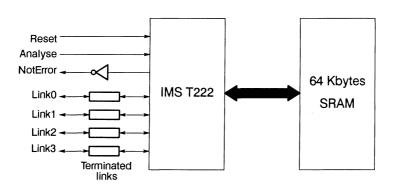

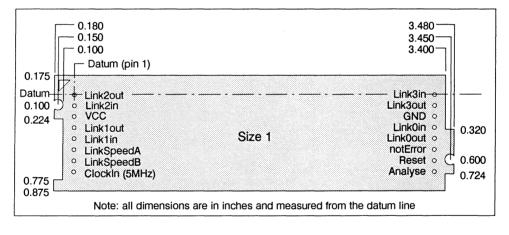

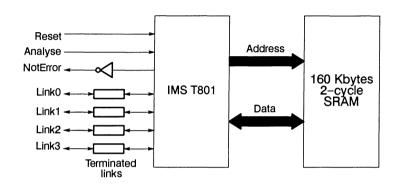

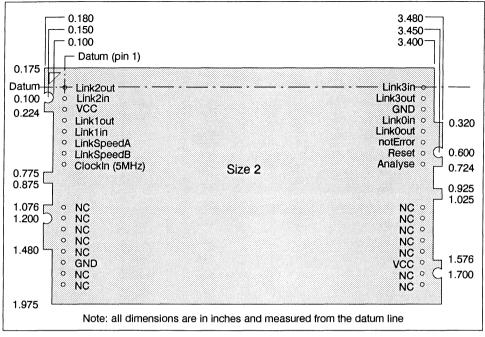

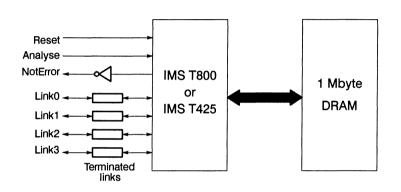

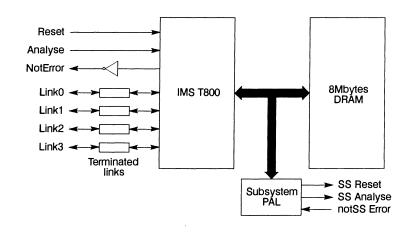

| 17.1     | IMS B401  | TRAM engineering data                    | 150        |

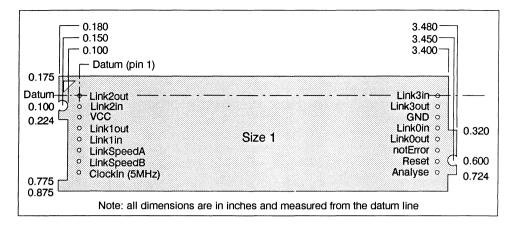

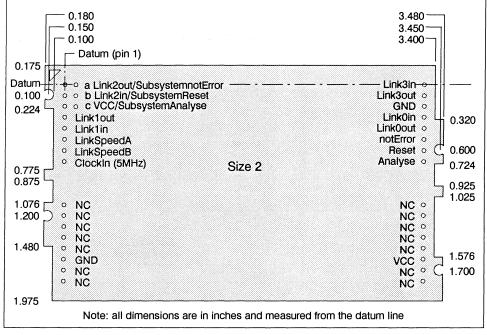

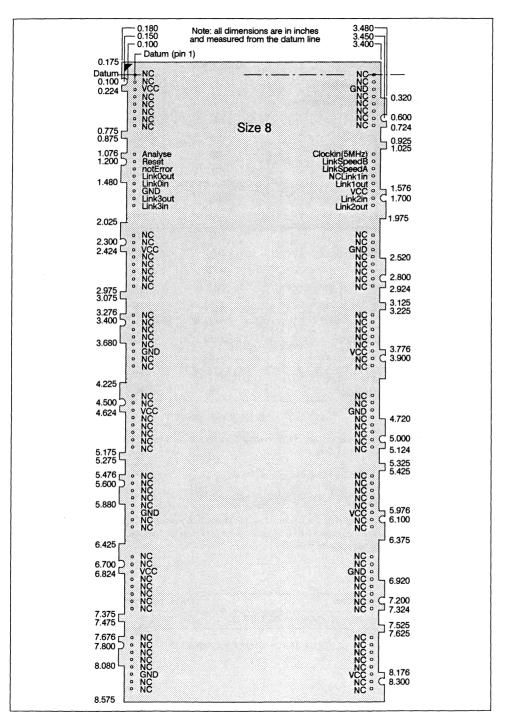

|          | 17.1.1    |                                          | 150        |

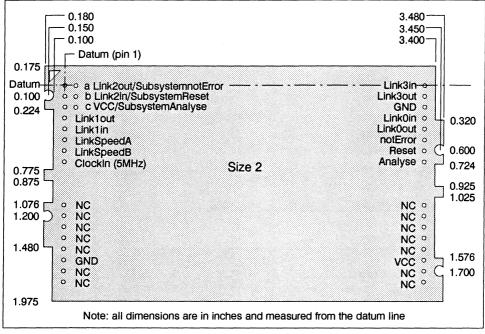

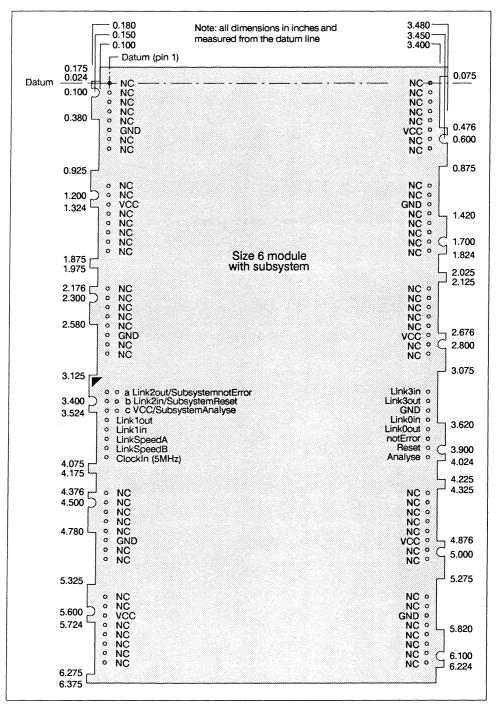

|          | 17.1.2    | Pin descriptions                         | 150        |

\_\_\_\_\_

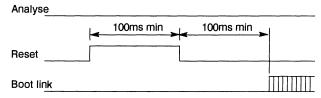

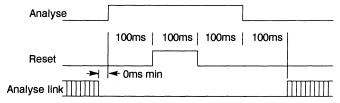

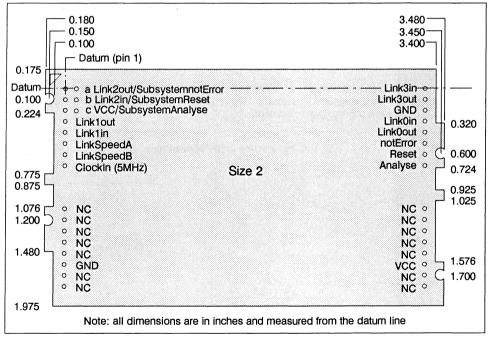

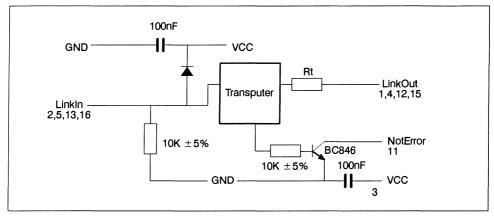

|                | 17.1.3                                                                                                                                                                   | Standard TRAM signalsnotError (pin 11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 151<br>151                                                                                                                                      |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                                                                                                                                                                          | LinkspeedA and LinkspeedB (pins 6 and 7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 151                                                                                                                                             |

|                |                                                                                                                                                                          | Link signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 151                                                                                                                                             |

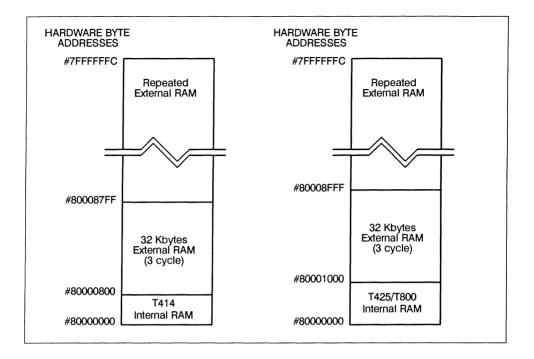

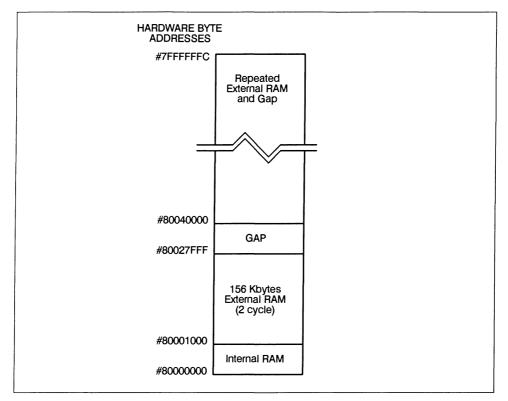

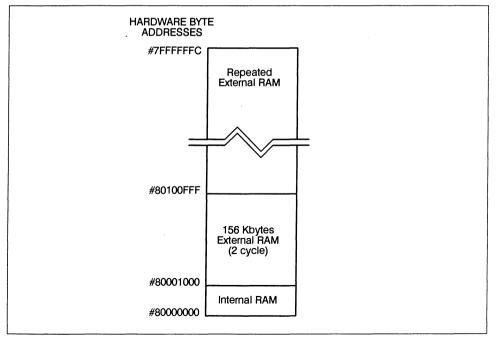

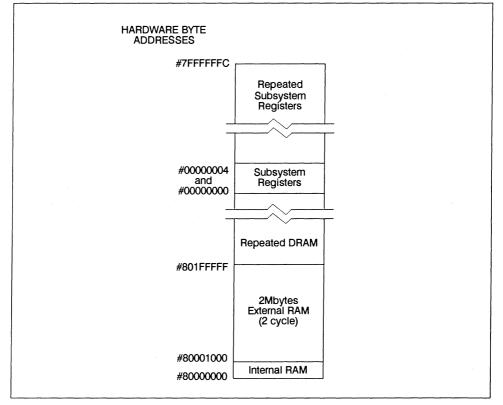

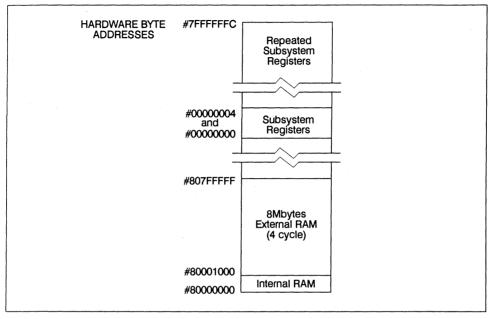

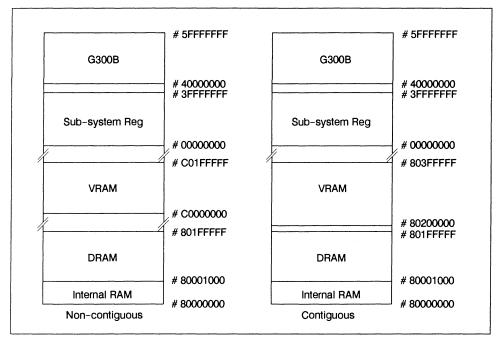

|                | 17.1.4                                                                                                                                                                   | Memory configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 151                                                                                                                                             |

|                |                                                                                                                                                                          | Location of external memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 151                                                                                                                                             |

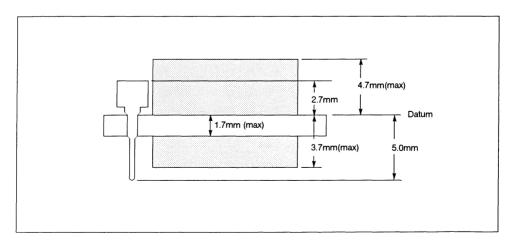

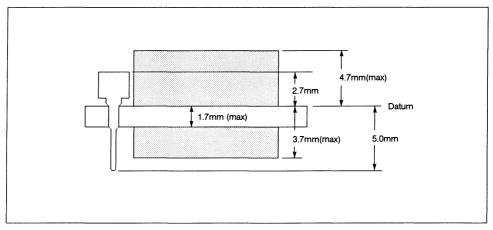

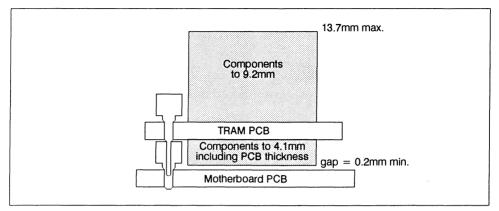

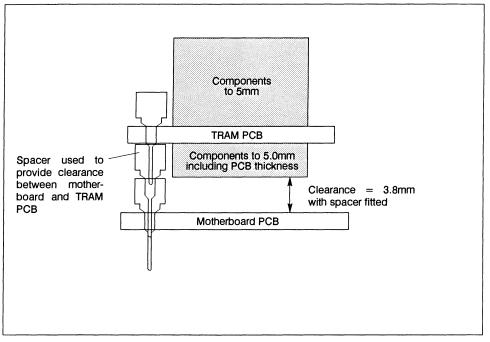

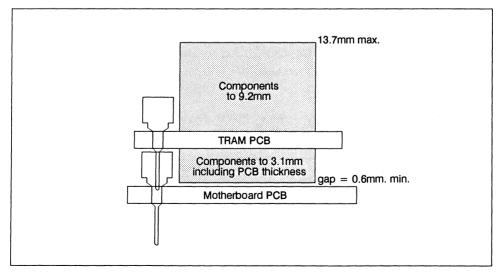

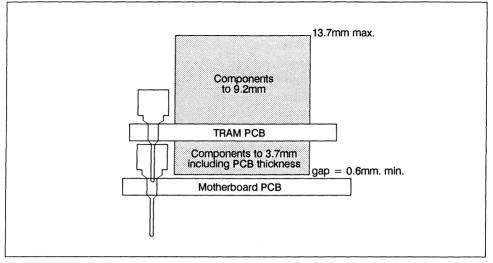

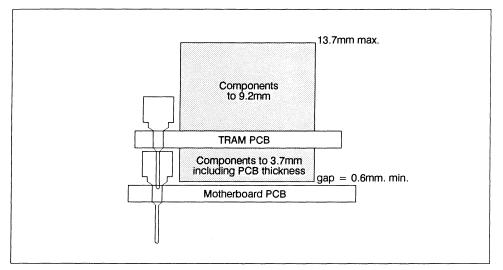

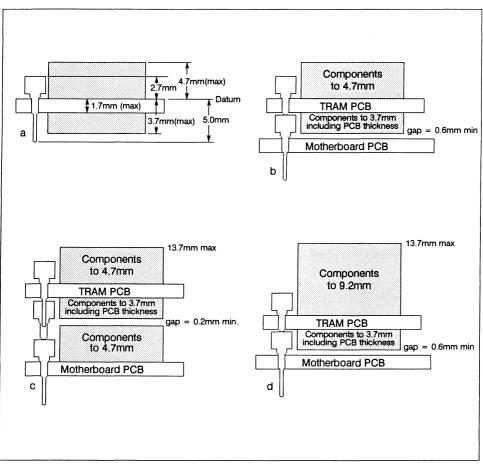

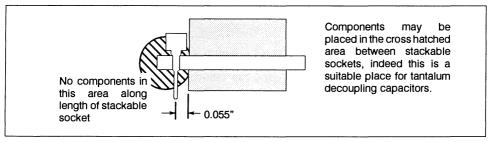

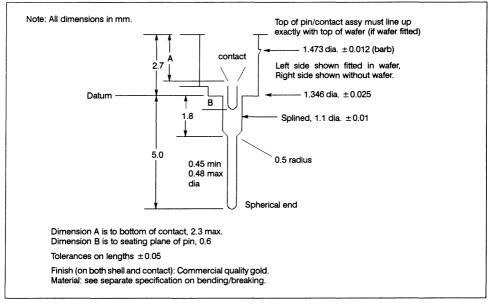

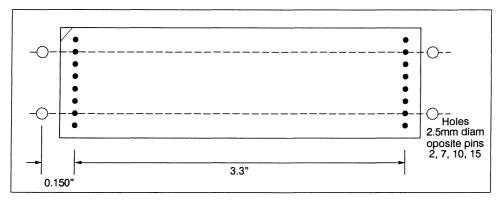

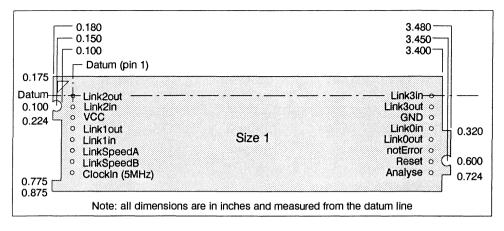

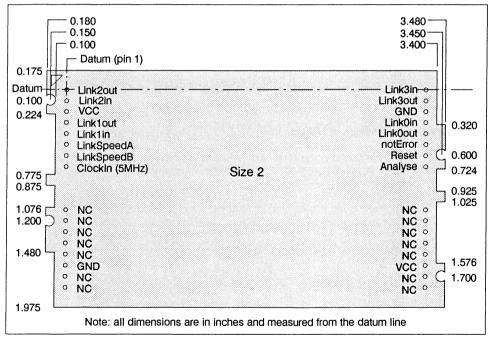

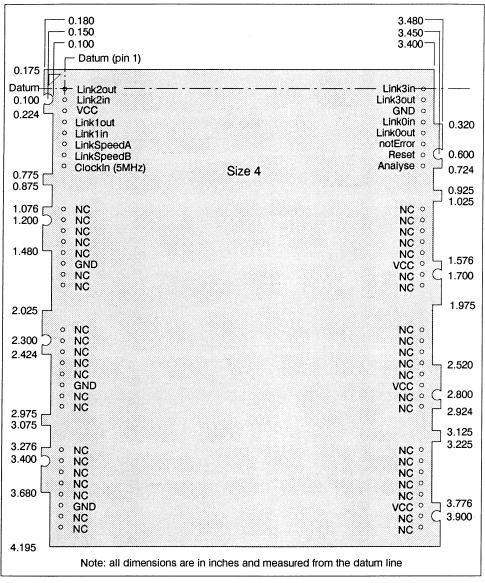

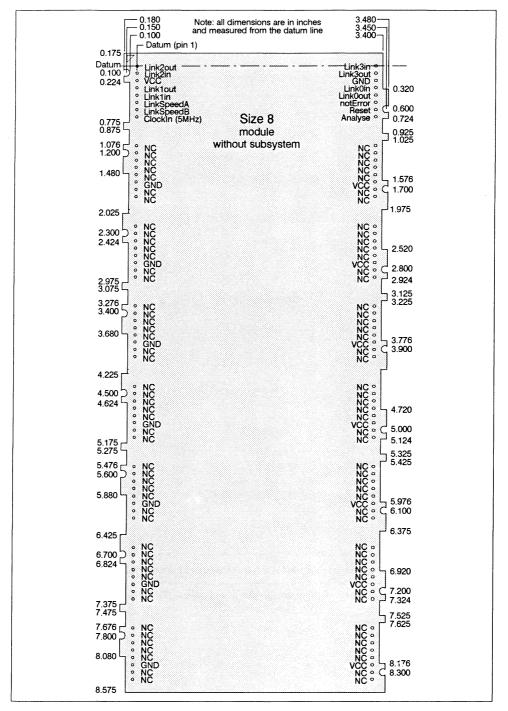

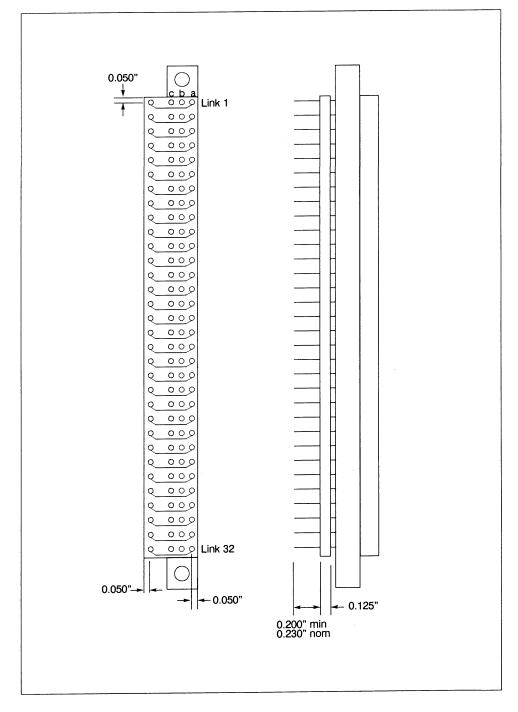

|                | 17.1.5                                                                                                                                                                   | Mechanical details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 152                                                                                                                                             |

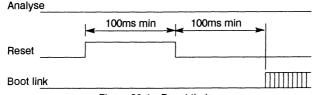

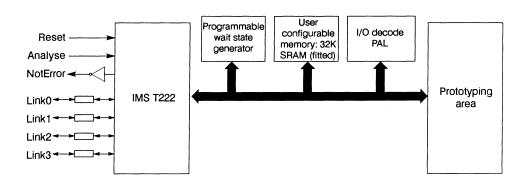

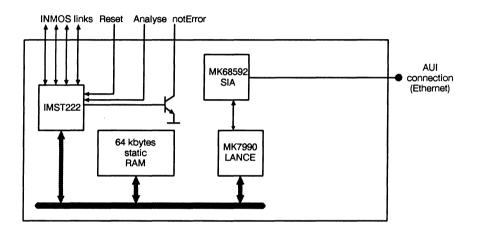

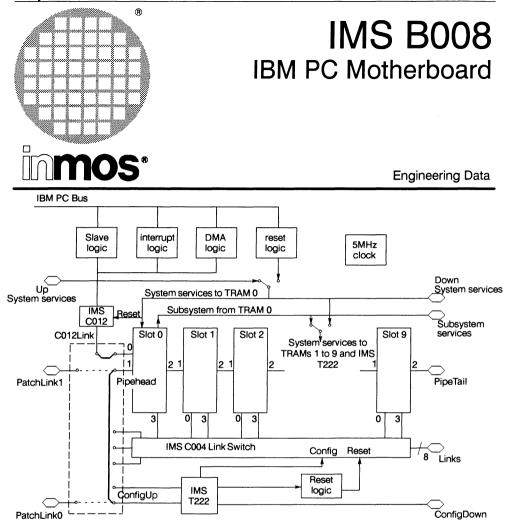

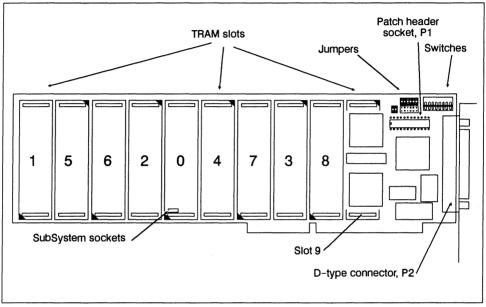

|                | 17.1.6                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 153                                                                                                                                             |