# TRANSPUTER DATABOOK

Third edition 1992

INMOS is a member of the SGS-THOMSON Microelectronics Group

## **INMOS Databook Series**

Transputer Databook

Military and Space Transputer Databook Transputer Development and *i***q** Systems Databook Transputer Applications Notebook: Architecture and Software Transputer Applications Notebook: Systems and Performance T9000 Transputer Products Overview Manual Graphics Databook

Copyright INMOS Limited 1992

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate; however, no responsibility is assumed for its use, nor for any infringement of patents or other rights of third parties resulting from its use. No licence is granted under any patents, trademarks or other rights of INMOS.

. INS and occam are trademarks of INMOS Limited.

INMOS Limited is a member of the SGS-THOMSON Microelectronics Group.

INMOS document number: 72 TRN 203 02

**ORDER CODE: DBTRANST/3**

PRINTED IN ITALY

## Contents overview

| Co | ontents                            | i     |

|----|------------------------------------|-------|

| No | otation and nomenclature           | xvii  |

| Tr | ansputer product numbers           | xviii |

| 1  | Company overview                   | 1     |

| 2  | Transputer architecture            | 5     |

| 3  | Transputer overview                | 25    |

| 4  | Transputer instruction set summary | 45    |

| 5  | Transputer performance             | 59    |

| 6  | IMS T805 transputer                | 71    |

| 7  | IMS T801 transputer                | 127   |

| 8  | IMS T426 transputer                | 163   |

| 9  | IMS T425 transputer                | 219   |

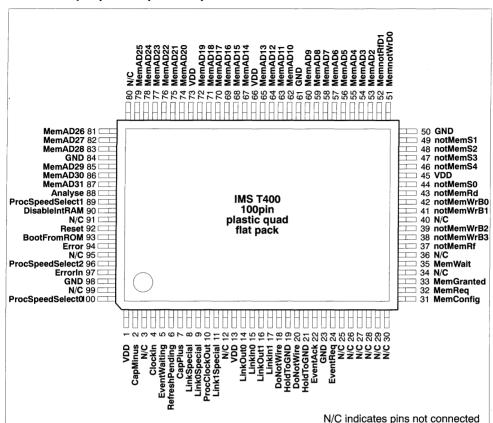

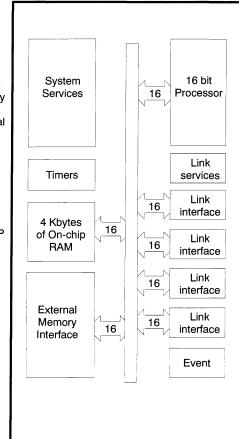

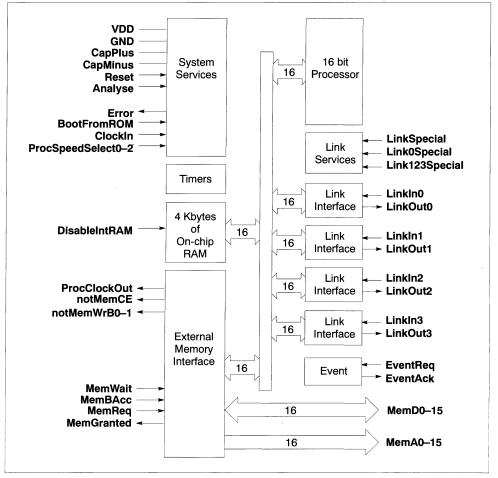

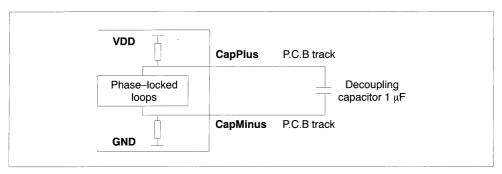

| 10 | IMS T400 transputer                | 271   |

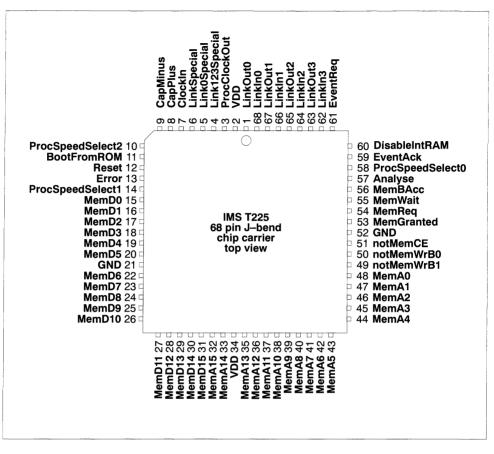

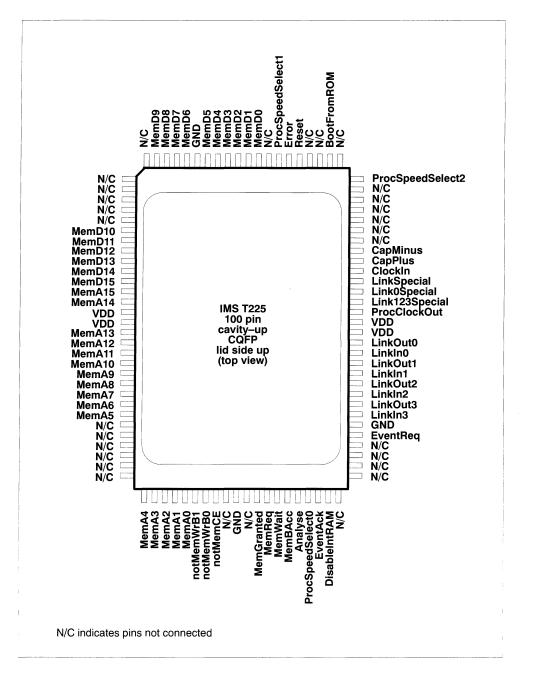

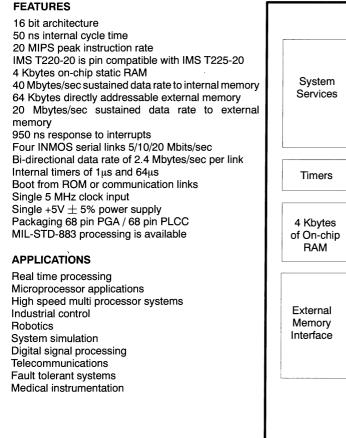

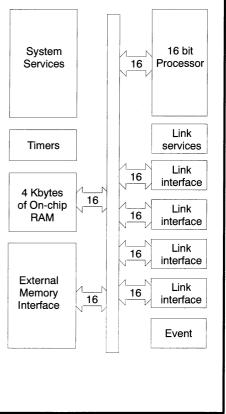

| 11 | IMS T225 transputer                | 323   |

| 12 | IMS T222 transputer                | 361   |

| 13 | IMS C004 programmable link switch  | 397   |

| 14 | IMS C011 link adaptor              | 417   |

| 15 | IMS C012 link adaptor              | 441   |

| A  | Packaging specifications           | 463   |

| в  | Obsolete devices                   | 479   |

# Contents

|   | N  | otatio | on and n       | omenclature                                   | xvii     |

|---|----|--------|----------------|-----------------------------------------------|----------|

|   |    | Signi  | ificance .     |                                               | xvii     |

|   |    | Signa  | al naming (    | conventions                                   | xvii     |

|   |    | Refe   | rences         |                                               | xvii     |

|   |    | Exan   | nples          |                                               | xvii     |

|   | Tr | ansp   | uter pro       | duct numbers                                  | xviii    |

| 1 | C  | ompa   | iny over       | view                                          | 1        |

|   | 1  | INM    | os             |                                               | 2        |

|   | 2  | SGS    | S-THOMS        | SON Microelectronics                          | 2        |

|   | 3  | Intro  | oduction       | to transputers                                | 3        |

|   | 4  | Qua    | lity and       | reliability                                   | 3        |

|   | 5  | Milit  | ary proc       | lucts                                         | 3        |

|   | 6  | Dev    | elopmen        | it systems                                    | 3        |

| 2 | Tr | ansp   | uter arcl      | hitecture                                     | 5        |

|   | 1  | Intro  | oduction       |                                               | 6        |

|   |    | 1.1    | Overview       | ۷                                             | 6        |

|   |    |        |                | Transputers and occam                         | 7        |

|   |    | 1.2    | System of      | design rationale                              | 8        |

|   |    |        | 1.2.1          | Programming                                   | 8        |

|   |    |        | 1.2.2<br>1.2.3 | Hardware                                      | 8        |

|   |    | 1.3    |                | Programmable componentsarchitecture rationale | 8<br>9   |

|   |    |        | 1.3.1          | Point to point communication links            | 9        |

|   |    |        | 1.3.2          | Local memory                                  | 9        |

|   |    | 1.4    | Commun         | ication                                       | 9        |

|   | 2  | occa   | am mode        | əl                                            | 11       |

|   |    | 2.1    | Overview       | 1                                             | 11       |

|   |    | 2.2    | occam ov       | verview                                       | 12       |

|   |    |        | 2.2.1          | Processes                                     | 12       |

|   |    |        |                | Assignment                                    | 12<br>12 |

|   |    |        |                |                                               |          |

|   |         |                                                  | •                                                                                                                                                   | Output                                                                                                                                                                                                                                                                                                                                            | 13                                                                                                                                                                     |

|---|---------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |         |                                                  | 2.2.2                                                                                                                                               | Constructions                                                                                                                                                                                                                                                                                                                                     | 13                                                                                                                                                                     |

|   |         |                                                  |                                                                                                                                                     | Sequence                                                                                                                                                                                                                                                                                                                                          | 13                                                                                                                                                                     |

|   |         |                                                  |                                                                                                                                                     | Parallel                                                                                                                                                                                                                                                                                                                                          | 13                                                                                                                                                                     |

|   |         |                                                  |                                                                                                                                                     | Communication                                                                                                                                                                                                                                                                                                                                     | 14                                                                                                                                                                     |

|   |         |                                                  |                                                                                                                                                     | Conditional                                                                                                                                                                                                                                                                                                                                       | 14                                                                                                                                                                     |

|   |         |                                                  |                                                                                                                                                     | Alternation                                                                                                                                                                                                                                                                                                                                       | 14                                                                                                                                                                     |

|   |         |                                                  |                                                                                                                                                     | Loop                                                                                                                                                                                                                                                                                                                                              | 15                                                                                                                                                                     |

|   |         |                                                  |                                                                                                                                                     | Selection                                                                                                                                                                                                                                                                                                                                         | 15                                                                                                                                                                     |

|   |         |                                                  |                                                                                                                                                     | Replication                                                                                                                                                                                                                                                                                                                                       | 15                                                                                                                                                                     |

|   |         |                                                  | 2.2.3                                                                                                                                               | Types                                                                                                                                                                                                                                                                                                                                             | 16                                                                                                                                                                     |

|   |         |                                                  | 2.2.4                                                                                                                                               | Declarations, arrays and subscripts                                                                                                                                                                                                                                                                                                               | 16                                                                                                                                                                     |

|   |         |                                                  | 2.2.5                                                                                                                                               | Procedures                                                                                                                                                                                                                                                                                                                                        | 16                                                                                                                                                                     |

|   |         |                                                  | 2.2.6                                                                                                                                               | Functions                                                                                                                                                                                                                                                                                                                                         | 17                                                                                                                                                                     |

|   |         |                                                  | 2.2.7                                                                                                                                               | Expressions                                                                                                                                                                                                                                                                                                                                       | 17                                                                                                                                                                     |

|   |         |                                                  | 2.2.8                                                                                                                                               | Timer                                                                                                                                                                                                                                                                                                                                             | 17                                                                                                                                                                     |

|   |         |                                                  | 2.2.9                                                                                                                                               | Peripheral access                                                                                                                                                                                                                                                                                                                                 | 18                                                                                                                                                                     |

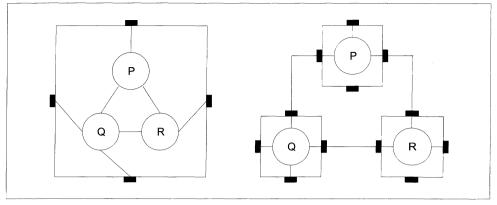

|   |         | 2.3                                              | Configu                                                                                                                                             | ration                                                                                                                                                                                                                                                                                                                                            | 18                                                                                                                                                                     |

|   |         |                                                  |                                                                                                                                                     | PLACED PAR                                                                                                                                                                                                                                                                                                                                        | 18                                                                                                                                                                     |

|   |         |                                                  |                                                                                                                                                     | PRI PAR                                                                                                                                                                                                                                                                                                                                           | 18                                                                                                                                                                     |

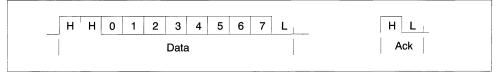

|   |         |                                                  | 2.3.1                                                                                                                                               | INMOS standard links                                                                                                                                                                                                                                                                                                                              | 18                                                                                                                                                                     |

|   | -       | _                                                |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

|   | 3       | Erro                                             | r handl                                                                                                                                             | ing                                                                                                                                                                                                                                                                                                                                               | 19                                                                                                                                                                     |

|   |         |                                                  |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

|   | 4       | Prog                                             | gram de                                                                                                                                             | velopment                                                                                                                                                                                                                                                                                                                                         | 20                                                                                                                                                                     |

|   |         | 4.1                                              | Logical                                                                                                                                             | behavior                                                                                                                                                                                                                                                                                                                                          | 20                                                                                                                                                                     |

|   |         |                                                  | -                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

|   |         | 4.2                                              |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                   | 20                                                                                                                                                                     |

|   |         | 4.3                                              | Separat                                                                                                                                             | e compilation of occam and other languages                                                                                                                                                                                                                                                                                                        | 20                                                                                                                                                                     |

|   |         | 4.4                                              |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                        |

|   | 5       |                                                  | Memory                                                                                                                                              | map and placement                                                                                                                                                                                                                                                                                                                                 | 21                                                                                                                                                                     |

|   |         | Phys                                             | -                                                                                                                                                   | map and placement                                                                                                                                                                                                                                                                                                                                 | 21<br><b>22</b>                                                                                                                                                        |

|   |         | •                                                | sical are                                                                                                                                           | chitecture                                                                                                                                                                                                                                                                                                                                        | 22                                                                                                                                                                     |

|   |         | <b>Phy</b> ៖<br>5.1                              | sical are                                                                                                                                           | chitecture                                                                                                                                                                                                                                                                                                                                        | <b>22</b><br>22                                                                                                                                                        |

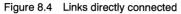

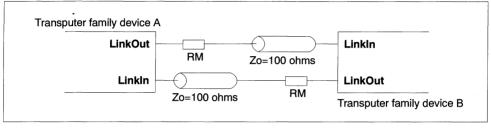

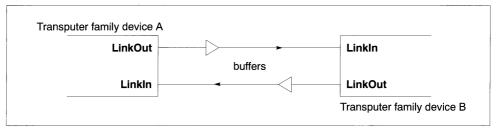

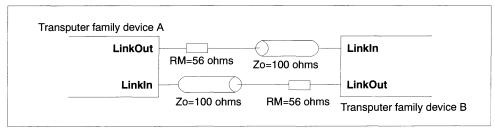

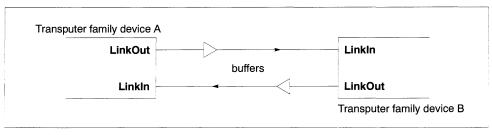

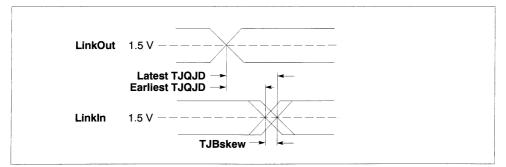

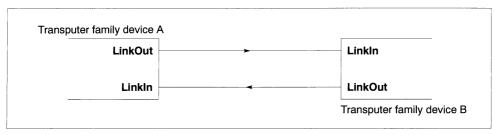

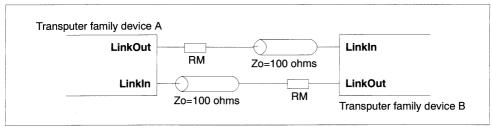

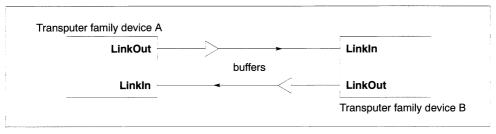

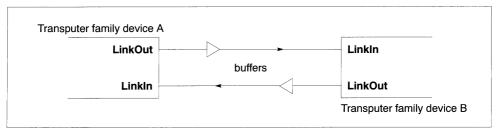

|   |         | •                                                | sical ard<br>INMOS<br>5.1.1                                                                                                                         | chitecture<br>serial links<br>Overview                                                                                                                                                                                                                                                                                                            | <b>22</b><br>22<br>22                                                                                                                                                  |

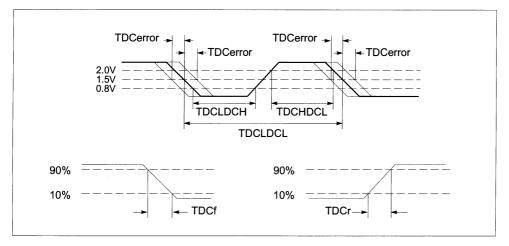

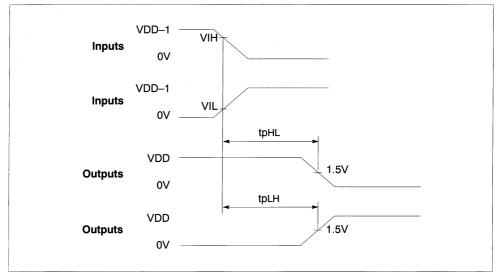

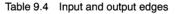

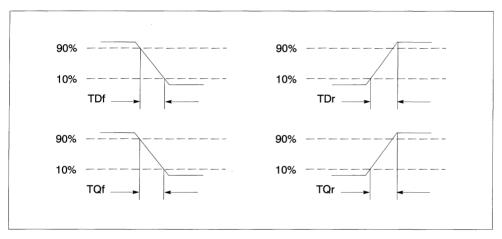

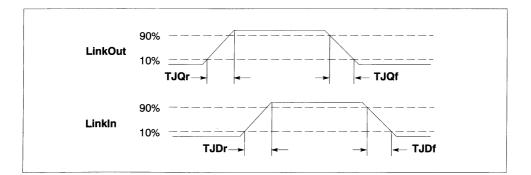

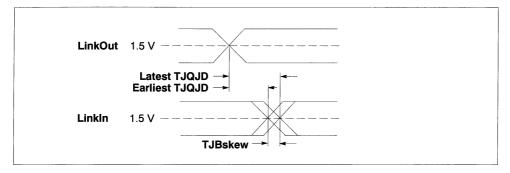

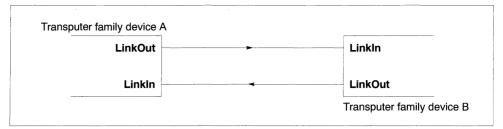

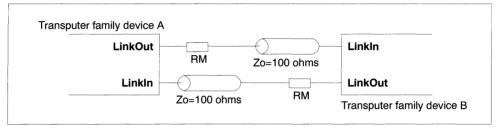

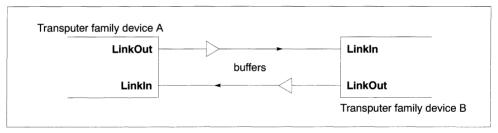

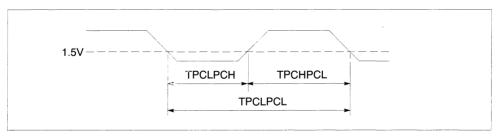

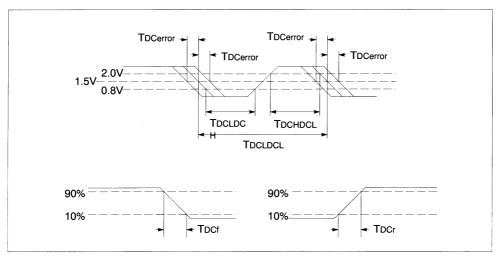

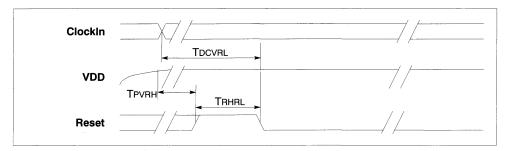

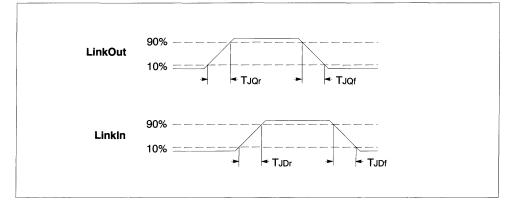

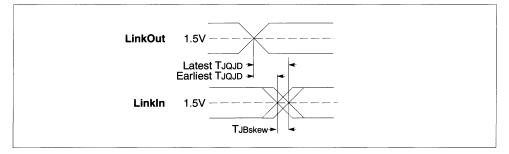

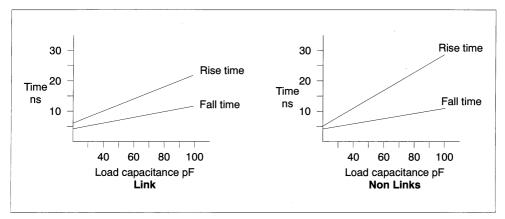

|   |         | 5.1                                              | sical ard<br>INMOS<br>5.1.1<br>5.1.2                                                                                                                | chitecture<br>serial links<br>Overview<br>Link electrical specification                                                                                                                                                                                                                                                                           | <b>22</b><br>22<br>22<br>22                                                                                                                                            |

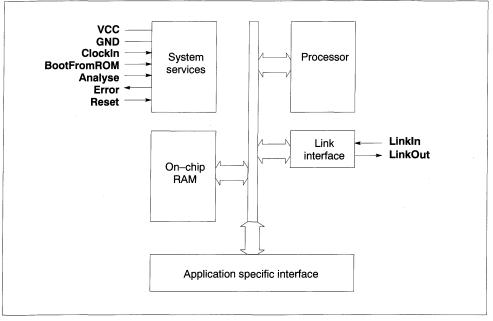

|   |         | •                                                | sical arc<br>INMOS<br>5.1.1<br>5.1.2<br>System                                                                                                      | chitecture<br>serial links<br>Overview<br>Link electrical specification<br>services                                                                                                                                                                                                                                                               | <b>22</b><br>22<br>22<br>22<br>22                                                                                                                                      |

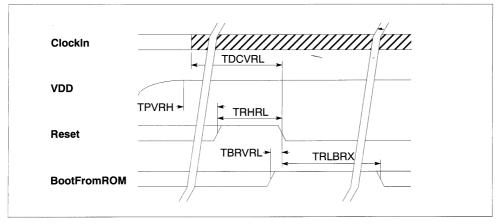

|   |         | 5.1                                              | sical arc<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1                                                                                             | chitecture<br>serial links<br>Overview<br>Link electrical specification<br>services<br>Powering up and down, running and stopping                                                                                                                                                                                                                 | 22<br>22<br>22<br>22<br>22<br>22<br>22                                                                                                                                 |

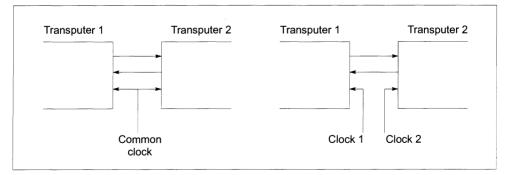

|   |         | 5.1<br>5.2                                       | sical arc<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2                                                                                    | chitecture<br>serial links<br>Overview<br>Link electrical specification<br>services<br>Powering up and down, running and stopping<br>Clock distribution                                                                                                                                                                                           | 22<br>22<br>22<br>22<br>22<br>22<br>22<br>23                                                                                                                           |

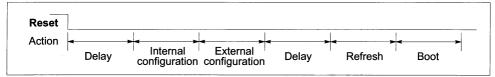

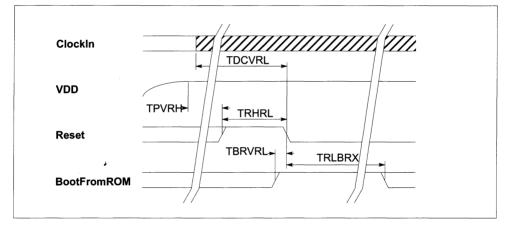

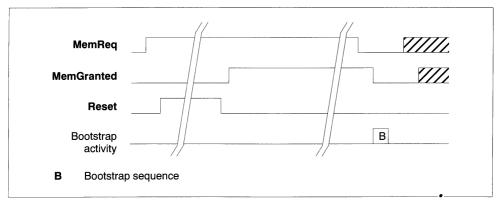

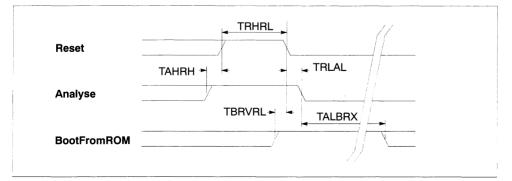

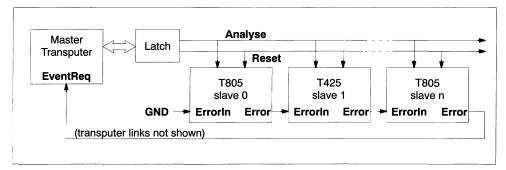

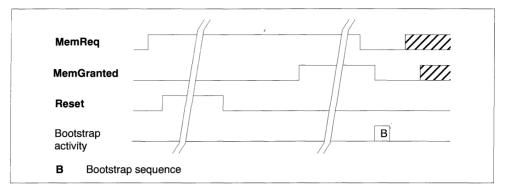

|   |         | 5.1<br>5.2<br>5.3                                | sical arc<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>Bootstra                                                                        | chitecture<br>serial links<br>Overview<br>Link electrical specification<br>services<br>Powering up and down, running and stopping<br>Clock distribution<br>apping from ROM or from a link                                                                                                                                                         | 22<br>22<br>22<br>22<br>22<br>22<br>22<br>23<br>23                                                                                                                     |

|   |         | 5.1<br>5.2                                       | sical arc<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>Bootstra                                                                        | chitecture<br>serial links<br>Overview<br>Link electrical specification<br>services<br>Powering up and down, running and stopping<br>Clock distribution                                                                                                                                                                                           | 22<br>22<br>22<br>22<br>22<br>22<br>22<br>23                                                                                                                           |

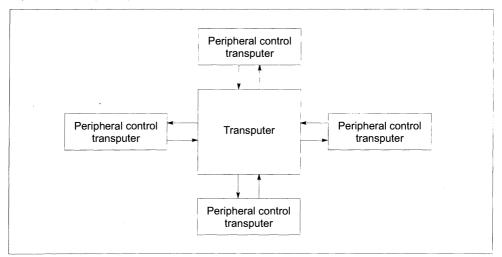

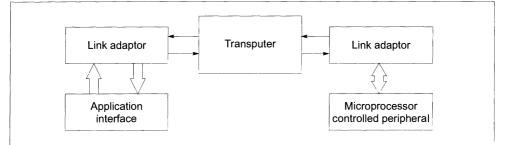

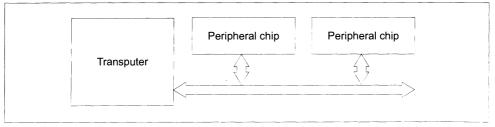

| 2 | т.      | 5.1<br>5.2<br>5.3<br>5.4                         | sical arc<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>Bootstra<br>Peripher                                                            | chitecture<br>serial links<br>Overview<br>Link electrical specification<br>services<br>Powering up and down, running and stopping<br>Clock distribution<br>apping from ROM or from a link<br>ral interfacing                                                                                                                                      | 22<br>22<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>23                                                                                                               |

| 3 | Tr      | 5.1<br>5.2<br>5.3<br>5.4                         | sical arc<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>Bootstra<br>Peripher                                                            | chitecture<br>serial links<br>Overview<br>Link electrical specification<br>services<br>Powering up and down, running and stopping<br>Clock distribution<br>apping from ROM or from a link                                                                                                                                                         | 22<br>22<br>22<br>22<br>22<br>22<br>22<br>23<br>23                                                                                                                     |

| 3 |         | 5.1<br>5.2<br>5.3<br>5.4<br><b>ansp</b> i        | sical arc<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>Bootstra<br>Peripher                                                            | chitecture         serial links         Overview         Link electrical specification         services         Powering up and down, running and stopping         Clock distribution         apping from ROM or from a link         ral interfacing                                                                                              | 22<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>23<br>23<br>23                                                                                                         |

| 3 | Tr<br>1 | 5.1<br>5.2<br>5.3<br>5.4<br><b>ansp</b> i        | sical arc<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>Bootstra<br>Peripher                                                            | chitecture<br>serial links<br>Overview<br>Link electrical specification<br>services<br>Powering up and down, running and stopping<br>Clock distribution<br>apping from ROM or from a link<br>ral interfacing                                                                                                                                      | 22<br>22<br>22<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>23                                                                                                         |

| 3 |         | 5.1<br>5.2<br>5.3<br>5.4<br><b>ansp</b> i        | sical arc<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>Bootstra<br>Peripher<br>uter ove                                                | chitecture         serial links         Overview         Link electrical specification         services         Powering up and down, running and stopping         Clock distribution         apping from ROM or from a link         ral interfacing                                                                                              | 22<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>23<br>23<br>23                                                                                                         |

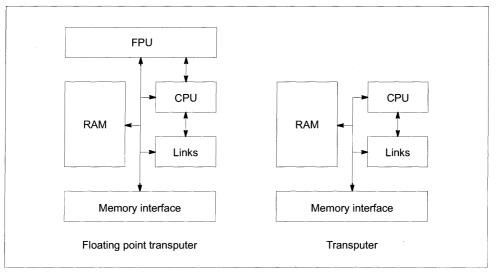

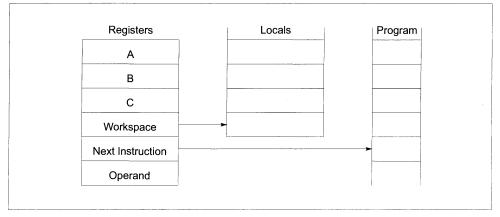

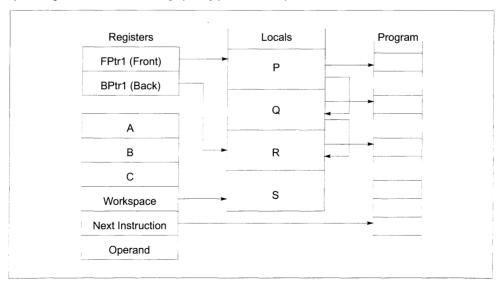

| 3 |         | 5.1<br>5.2<br>5.3<br>5.4<br>anspu<br>Tran        | sical arc<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>Bootstra<br>Peripher<br>uter ove<br>sputer i<br>Register                        | chitecture         serial links         Overview         Link electrical specification         services         Powering up and down, running and stopping         Clock distribution         apping from ROM or from a link         ral interfacing         erview         internal architecture                                                 | <ul> <li>22</li> <li>22</li> <li>22</li> <li>22</li> <li>22</li> <li>23</li> <li>23</li> <li>23</li> <li>25</li> <li>26</li> </ul>                                     |

| 3 |         | 5.1<br>5.2<br>5.3<br>5.4<br>anspu<br>Tran<br>1.1 | sical arc<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>Bootstra<br>Peripher<br>uter ove<br>sputer i<br>Register                        | chitecture         serial links         Overview         Link electrical specification         services         Powering up and down, running and stopping         Clock distribution         apping from ROM or from a link         ral interfacing         erview         internal architecture                                                 | <ul> <li>22</li> <li>22</li> <li>22</li> <li>22</li> <li>22</li> <li>23</li> <li>23</li> <li>23</li> <li>25</li> <li>26</li> <li>27</li> </ul>                         |

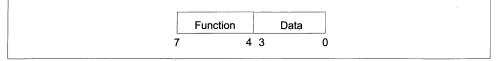

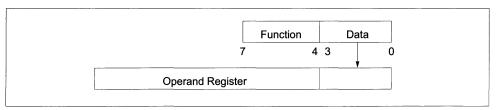

| 3 |         | 5.1<br>5.2<br>5.3<br>5.4<br>anspu<br>Tran<br>1.1 | sical ard<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>Bootstra<br>Peripher<br>uter ove<br>sputer i<br>Register<br>Instructio          | chitecture<br>serial links<br>Overview<br>Link electrical specification<br>services<br>Powering up and down, running and stopping<br>Clock distribution<br>apping from ROM or from a link<br>ral interfacing<br>erview<br>internal architecture<br>rs<br>ons                                                                                      | <ul> <li>22</li> <li>22</li> <li>22</li> <li>22</li> <li>22</li> <li>23</li> <li>23</li> <li>23</li> <li>25</li> <li>26</li> <li>27</li> <li>27</li> </ul>             |

| 3 |         | 5.1<br>5.2<br>5.3<br>5.4<br>anspu<br>Tran<br>1.1 | sical ard<br>INMOS<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>Bootstra<br>Peripher<br>uter ove<br>sputer i<br>Register<br>Instructio<br>1.2.1 | chitecture         serial links         Overview         Link electrical specification         services         Powering up and down, running and stopping         Clock distribution         apping from ROM or from a link         ral interfacing         erview         internal architecture         rs         ons         Direct functions | <ul> <li>22</li> <li>22</li> <li>22</li> <li>22</li> <li>22</li> <li>23</li> <li>23</li> <li>23</li> <li>25</li> <li>26</li> <li>27</li> <li>27</li> <li>28</li> </ul> |

|   |     | 1.2.4 Expression evaluation                                                                   | 29              |

|---|-----|-----------------------------------------------------------------------------------------------|-----------------|

|   |     | 1.2.5     Efficiency of encoding       1.3     Support for concurrency                        | 29<br>30        |

|   |     | 1.3.1 Priority                                                                                | 31              |

|   |     | 1.3.2 Interrupt latency                                                                       | 32              |

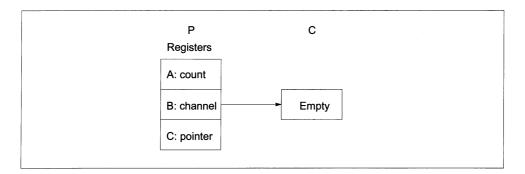

|   |     | 1.4 Communications                                                                            | 32              |

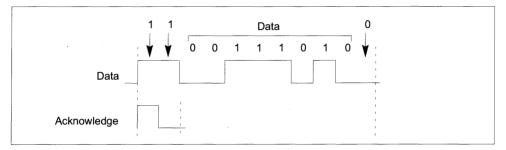

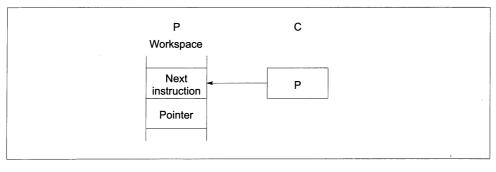

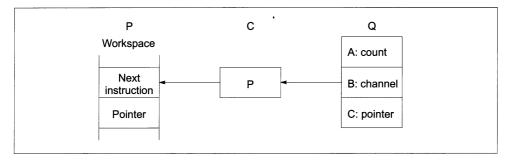

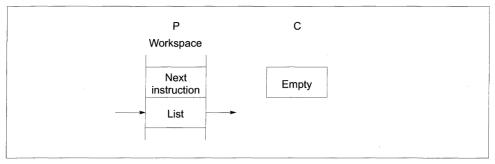

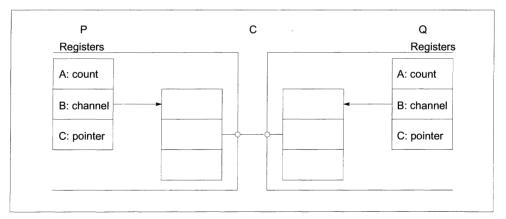

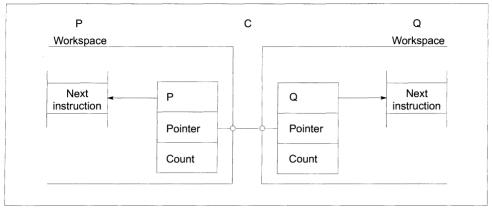

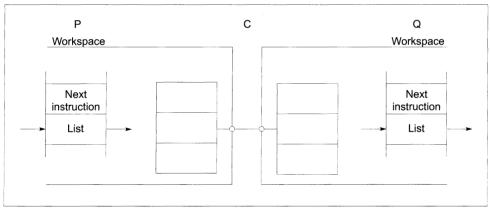

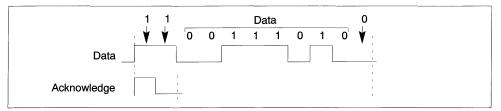

|   |     | 1.4.1       Internal channel communication         1.4.2       External channel communication | 32<br>34        |

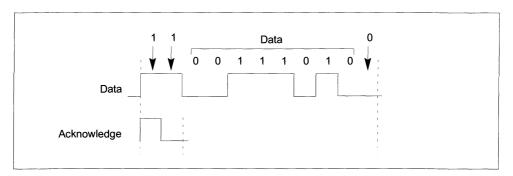

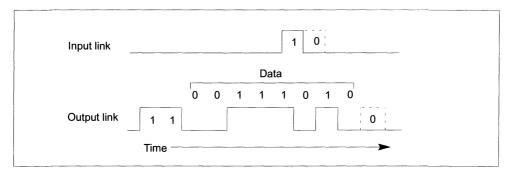

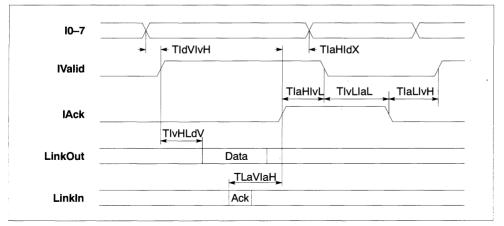

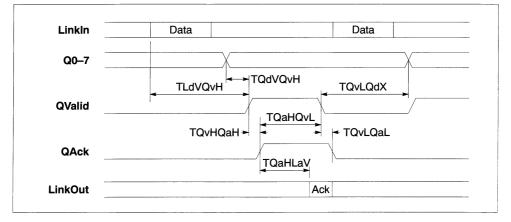

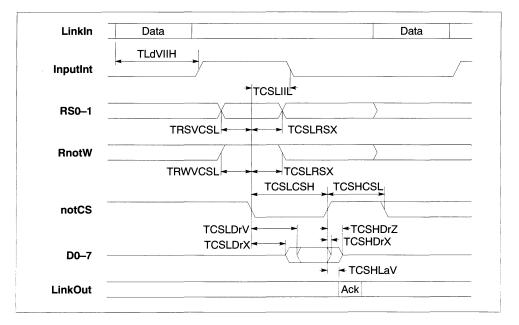

|   |     | 1.4.3 Communication links                                                                     | 35              |

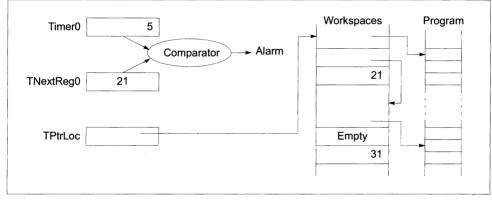

|   |     | 1.5 Timer                                                                                     | 36              |

|   |     | 1.6       Alternative         1.7       Floating point instructions                           | 37<br>37        |

|   |     | 1.7       Produing point instructions         1.7.1       Optimizing use of the stack         | 38              |

|   |     | 1.7.2 Concurrent operation of FPU and CPU                                                     | 38              |

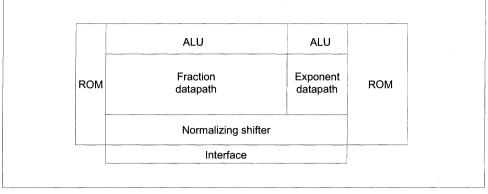

|   |     | 1.8 Floating point unit design                                                                | 39              |

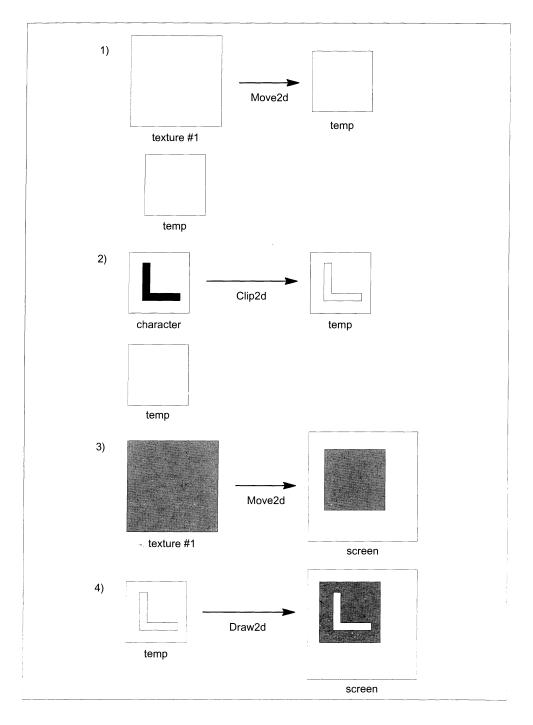

|   |     | 1.9 Graphics capability                                                                       | 40              |

|   |     |                                                                                               | 40              |

|   | 2   | Conclusion                                                                                    | 43              |

| 4 | Tr  | ansputer instruction set summary                                                              | 45              |

|   | 1   | Introduction                                                                                  | 46              |

|   | -   |                                                                                               | 47              |

|   |     | Floating point unit                                                                           | 47              |

|   |     | Notation                                                                                      | 47              |

|   | 2   | Descheduling points                                                                           | 48              |

|   | 3   | Error instructions                                                                            | 48              |

|   | 4   | Debugging support                                                                             | 48              |

|   | 5   | Floating point errors for the IMS T801 and IMS T805 only                                      | 49              |

|   | 6   | Block move                                                                                    | 49              |

|   | 7   | General instructions                                                                          | 49              |

|   | 8   | Floating point instructions                                                                   | 56              |

|   |     |                                                                                               | 56              |

|   |     |                                                                                               | 58              |

| 5 | Tra | ansputer performance                                                                          | 59              |

|   | 1   | Introduction                                                                                  | 60              |

|   | 2   | Performance overview                                                                          | 60              |

|   | 3   | Fast multiply, TIMES                                                                          | 63              |

|   | 4   |                                                                                               | 63              |

|   | -   |                                                                                               | 03              |

|   | 5   |                                                                                               | <b>65</b><br>65 |

|   |     |                                                                                               |                 |

|   |    | 5.2   | 5.1.1 Floating point functions Floating point operations for IMS T222 and IMS T225 | 65<br>66 |

|---|----|-------|------------------------------------------------------------------------------------|----------|

|   |    | 5.3   | Floating point operations for IMS T400, IMS T425 and IMS T426                      | 66       |

|   |    | 5.4   | Special purpose functions and procedures                                           | 67       |

|   | 6  | Effe  | ct of external memory                                                              | 68       |

|   | 7  | Inte  | rrupt latency                                                                      | 70       |

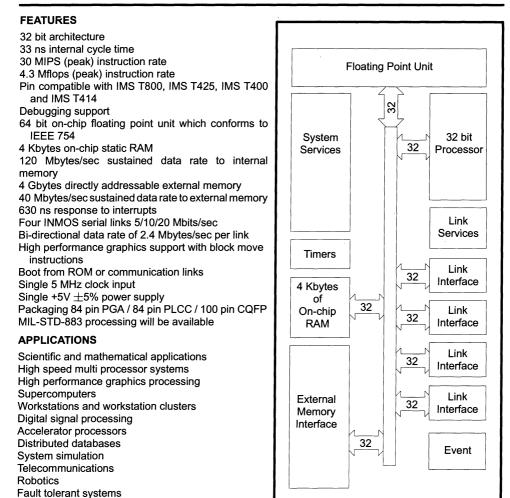

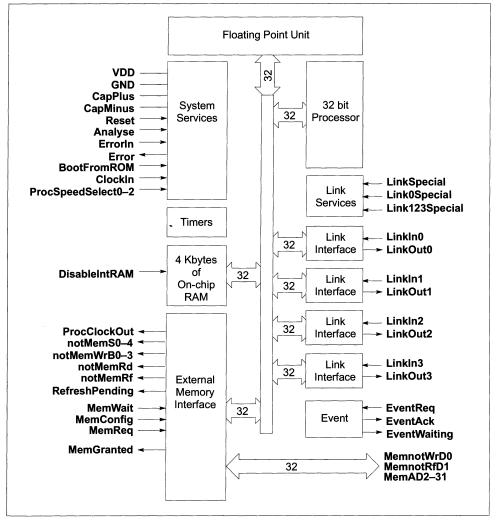

| 6 | IN | IS T8 | 05 transputer                                                                      | 71       |

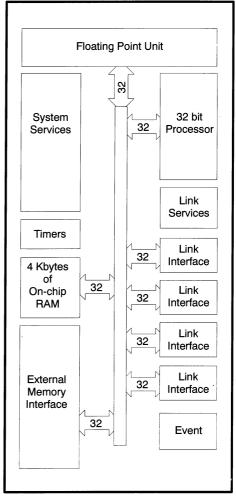

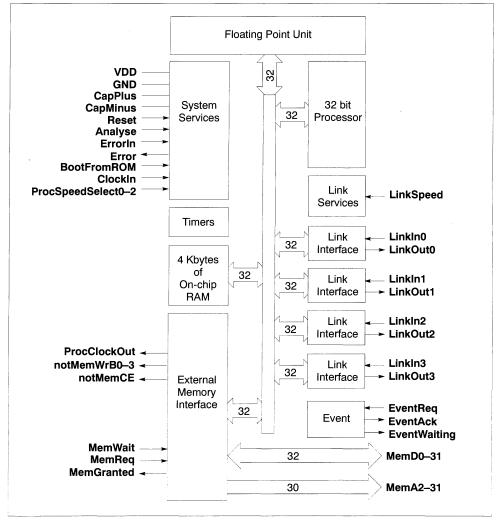

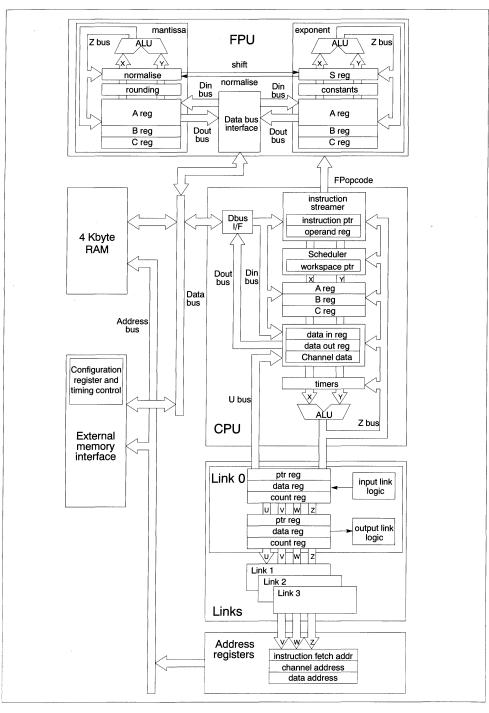

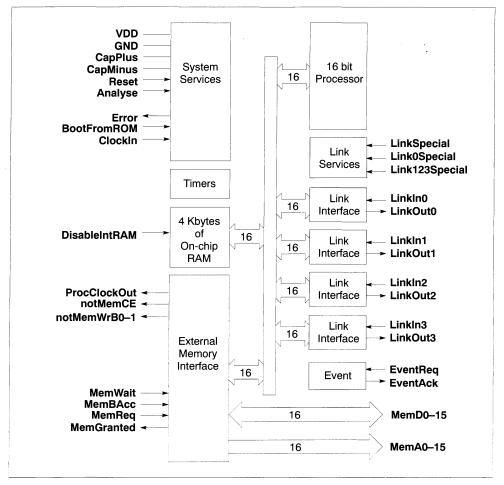

|   | 1  | Intro | oduction                                                                           | 72       |

|   | 2  | Pin   | designations                                                                       | 75       |

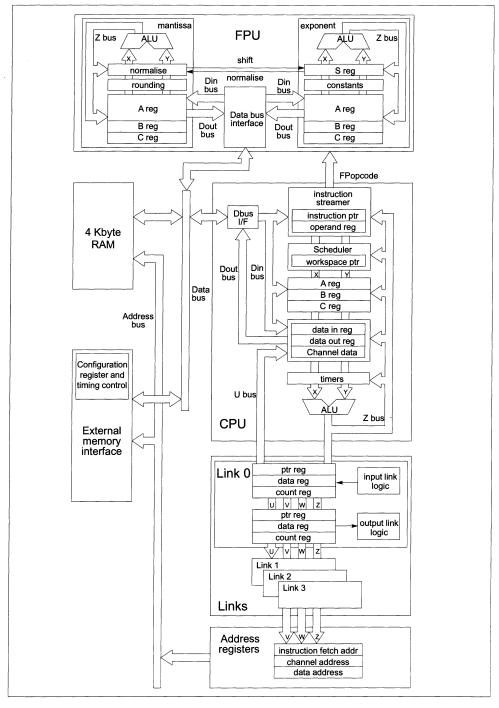

|   | 3  | Floa  | ting point unit                                                                    | 76       |

|   | 4  | Syst  | tem services                                                                       | 78       |

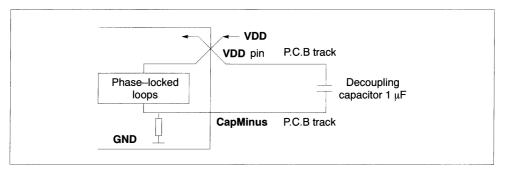

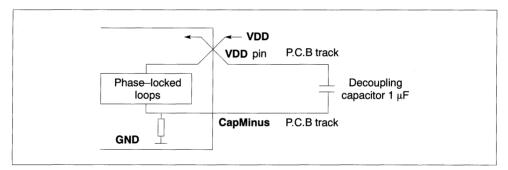

|   |    | 4.1   | Power                                                                              | 78       |

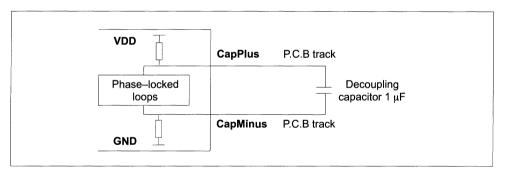

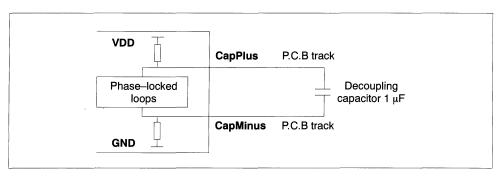

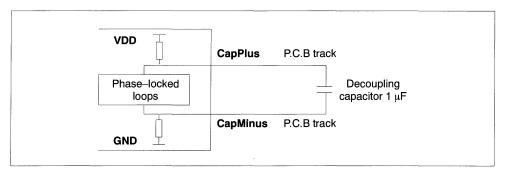

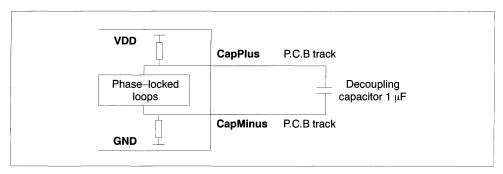

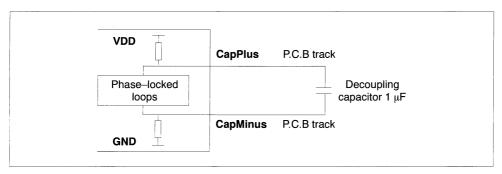

|   |    | 4.2   | CapPlus, CapMinus                                                                  | 78       |

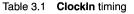

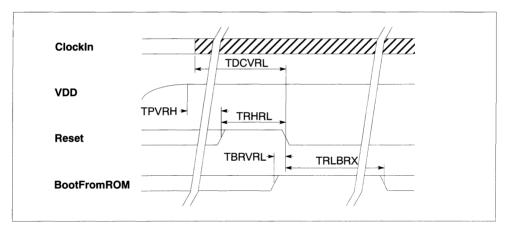

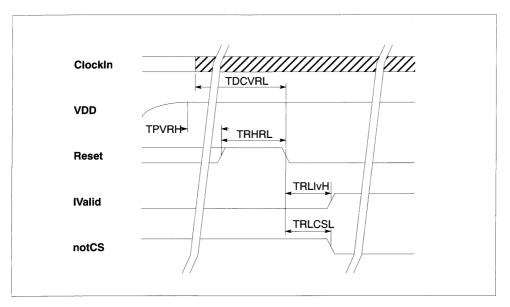

|   |    | 4.3   | ClockIn                                                                            | 78       |

|   |    | 4.4   | ProcSpeedSelect0-2                                                                 | 79       |

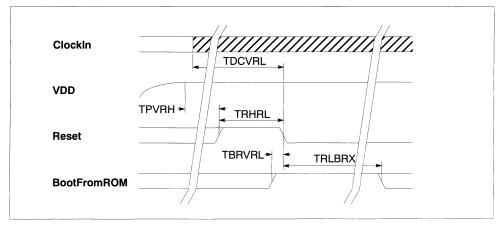

|   |    | 4.5   | •                                                                                  | 80       |

|   |    | 4.6   |                                                                                    | 80       |

|   |    | 4.7   |                                                                                    | 81       |

|   |    | 4.8   |                                                                                    | 81       |

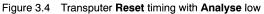

|   |    | 4.9   | ,                                                                                  | 83       |

|   | 5  |       |                                                                                    | 84       |

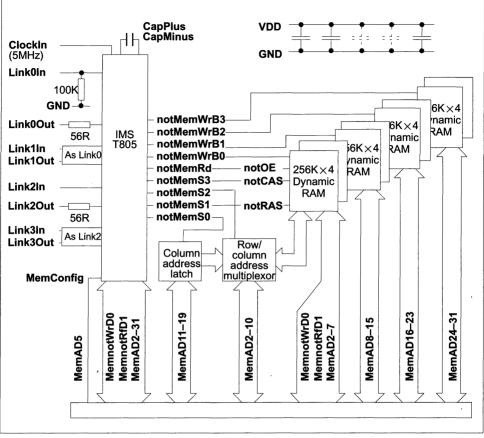

|   | 6  | Exte  | rnal memory interface                                                              | 86       |

|   |    | 6.1   | Pin functions                                                                      | 87       |

|   |    |       |                                                                                    | 87       |

|   |    |       |                                                                                    | 87       |

|   |    |       |                                                                                    | 87       |

|   |    |       |                                                                                    | 87<br>97 |

|   |    |       |                                                                                    | 87<br>87 |

|   |    |       |                                                                                    | 87       |

|   |    |       |                                                                                    | 87       |

|   |    |       |                                                                                    | 87       |

|   |    |       |                                                                                    | 88       |

|   |    |       | 6                                                                                  | 88       |

|   |    | 6.0   |                                                                                    | 88       |

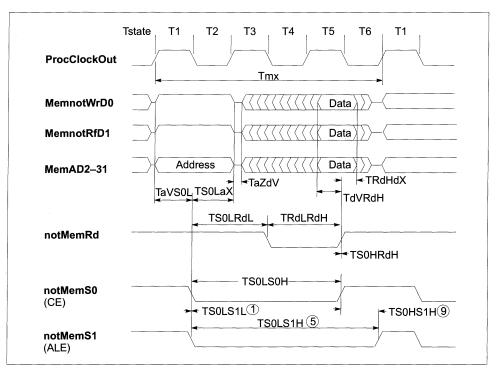

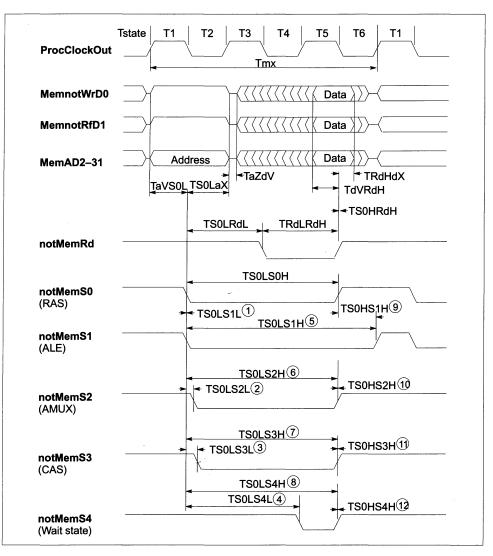

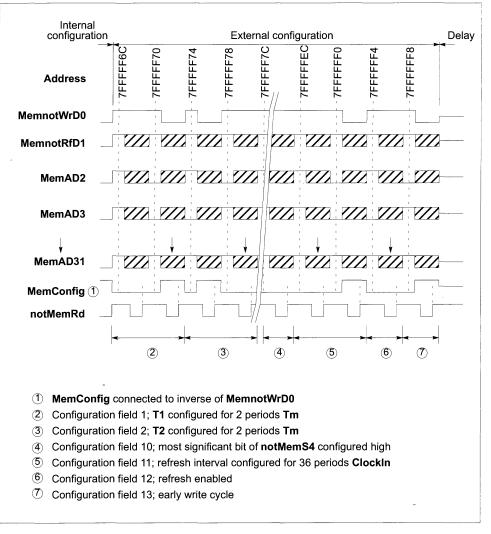

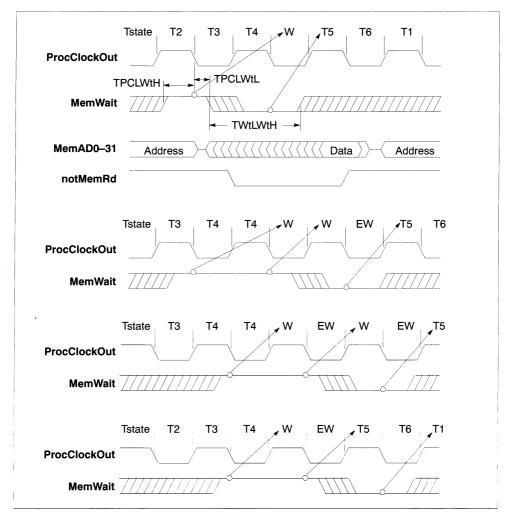

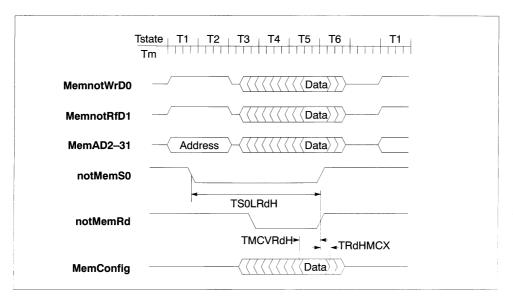

|   |    | 6.2   | Read cycle                                                                         | 90       |

| Contents |

|----------|

|----------|

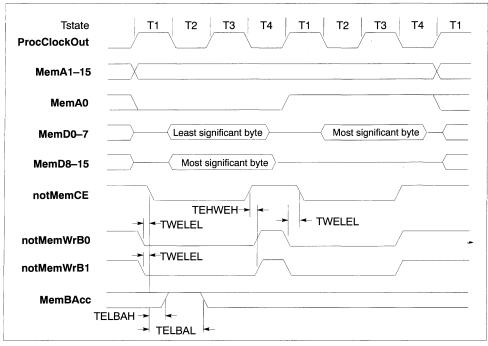

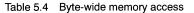

|   |      | 6.3                                    | Write cycle                                                                   | 95                                     |

|---|------|----------------------------------------|-------------------------------------------------------------------------------|----------------------------------------|

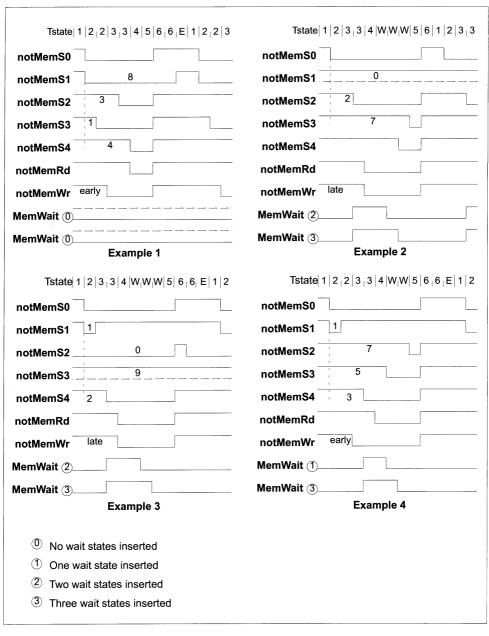

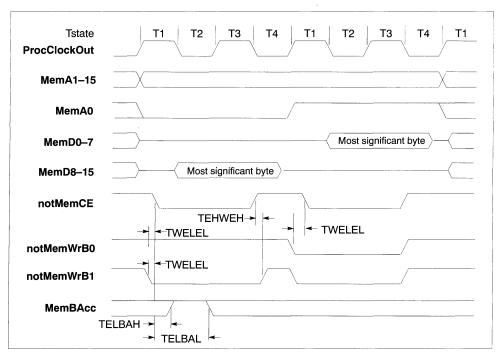

|   |      | 6.4                                    | Wait                                                                          | 96                                     |

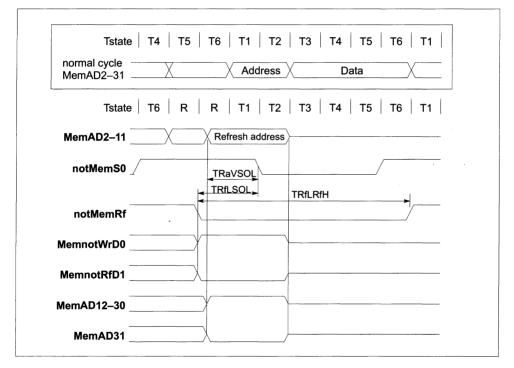

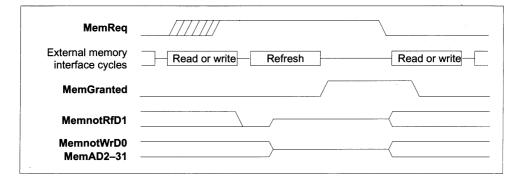

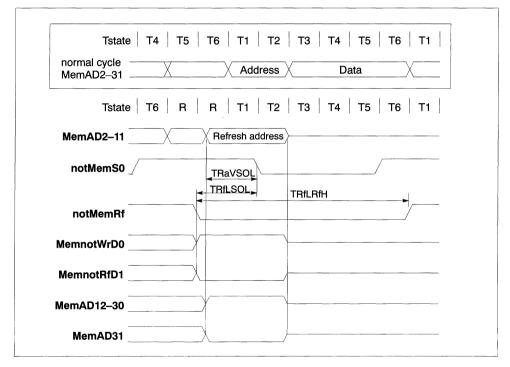

|   |      | 6.5                                    | Memory refresh                                                                | 98                                     |

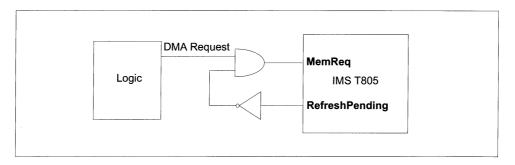

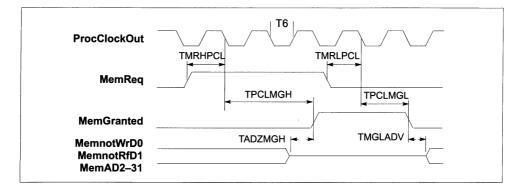

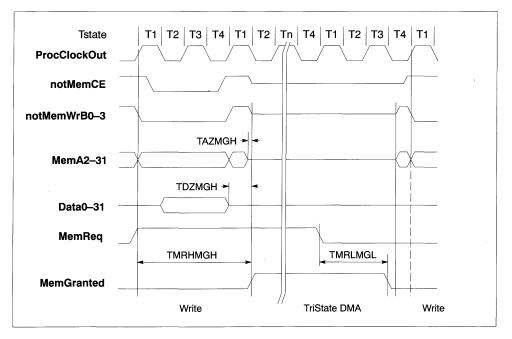

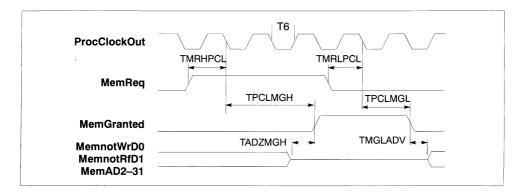

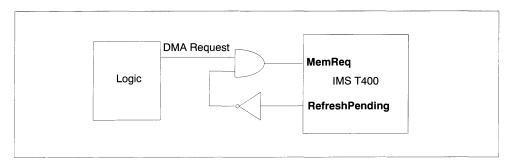

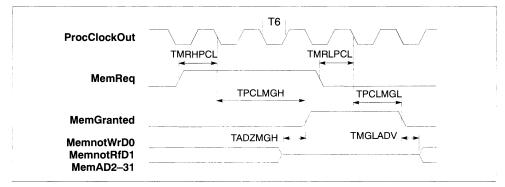

|   |      | 6.6                                    | Direct memory access                                                          | 101                                    |

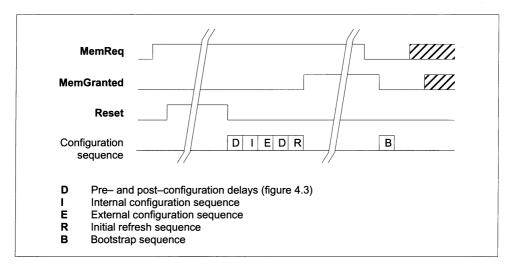

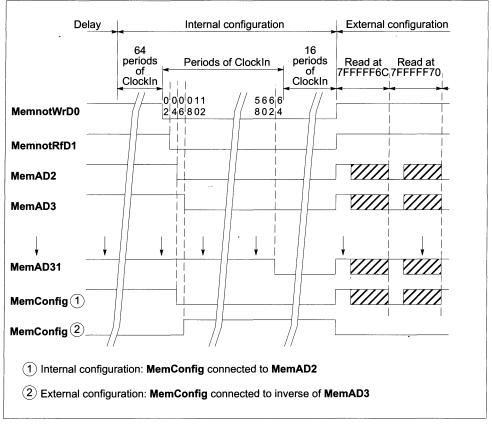

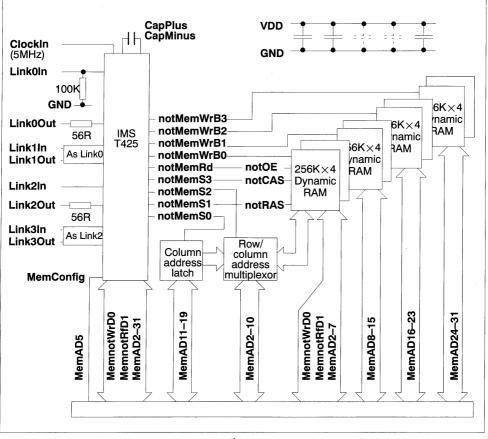

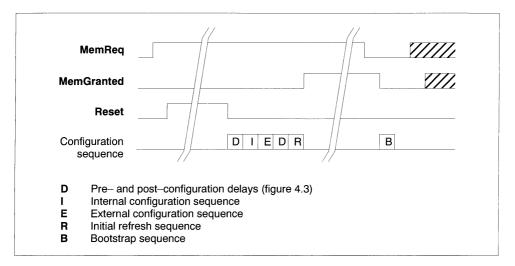

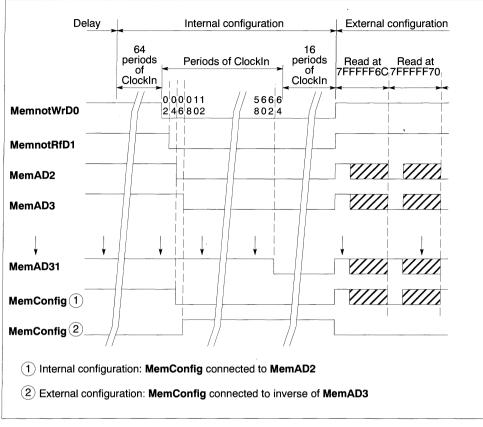

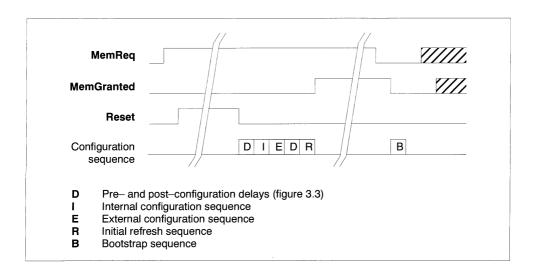

|   |      | 6.7                                    | Memory configuration                                                          | 104                                    |

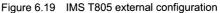

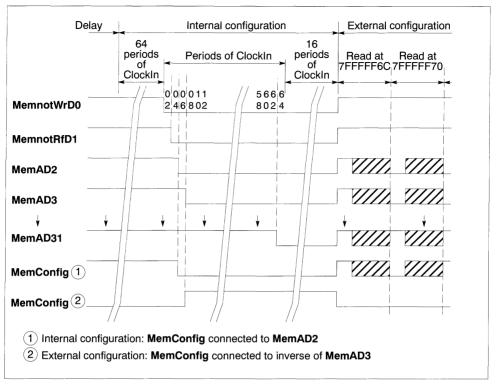

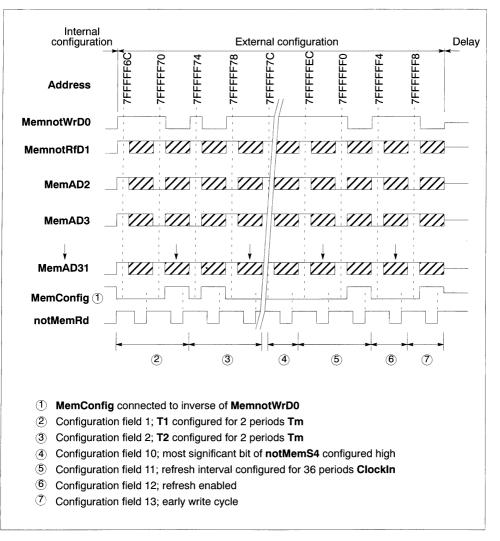

|   |      |                                        | 6.7.1       Internal configuration         6.7.2       External configuration | 104<br>106                             |

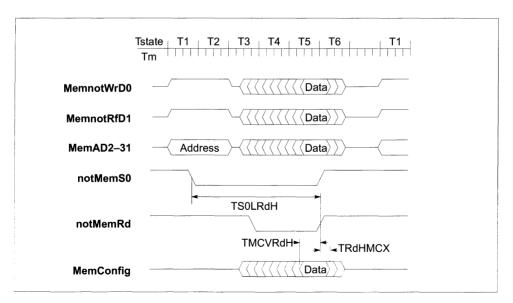

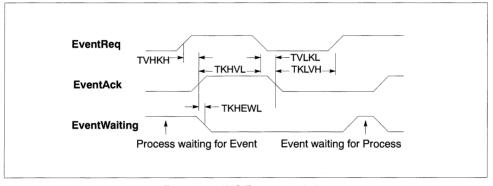

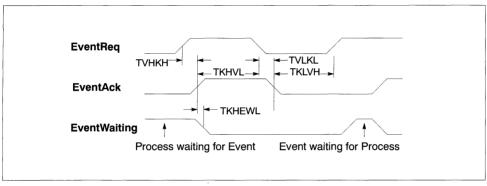

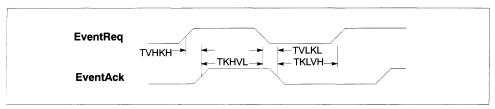

|   | 7    | Ever                                   | ts                                                                            | 112                                    |

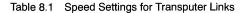

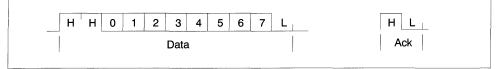

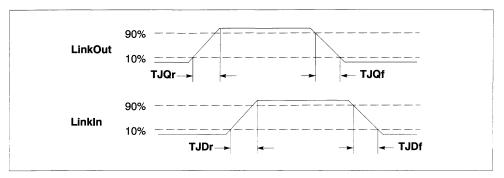

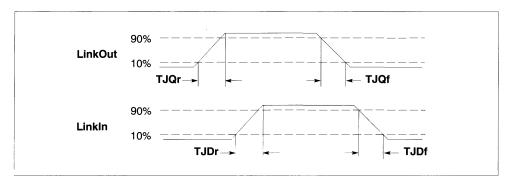

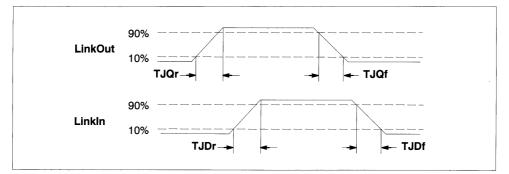

|   | 8    | Link                                   | \$                                                                            | 114                                    |

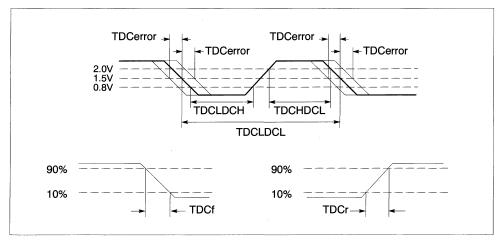

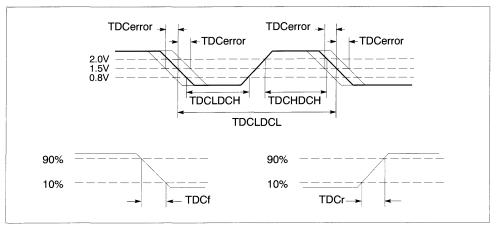

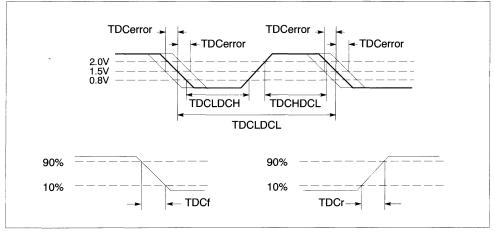

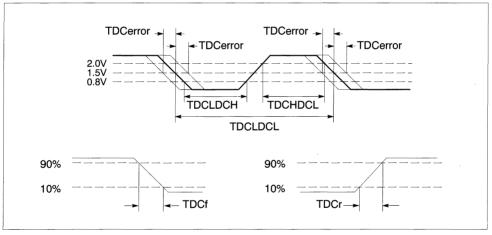

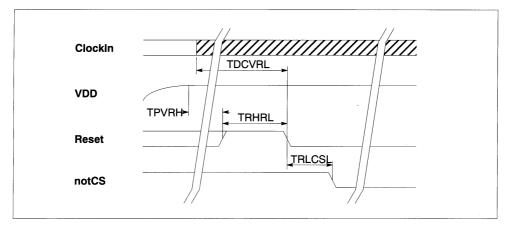

|   | 9    | Floo                                   | rical specifications                                                          | 117                                    |

|   | 3    |                                        |                                                                               |                                        |

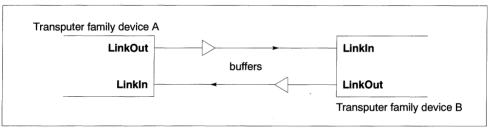

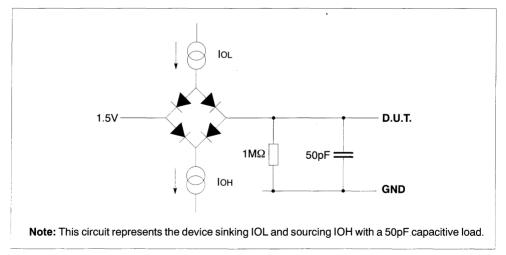

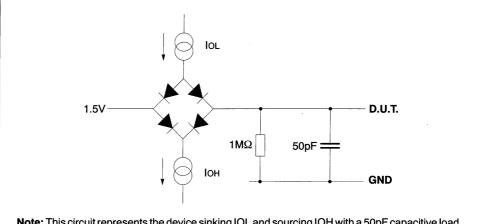

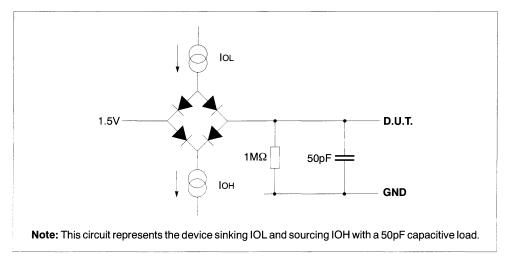

|   |      | 9.1                                    | DC electrical characteristics                                                 | 117                                    |

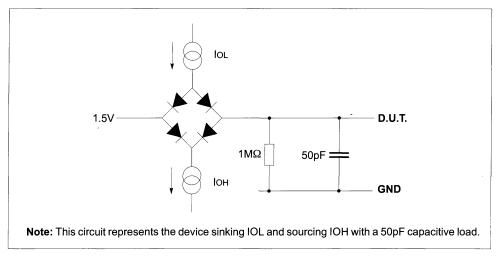

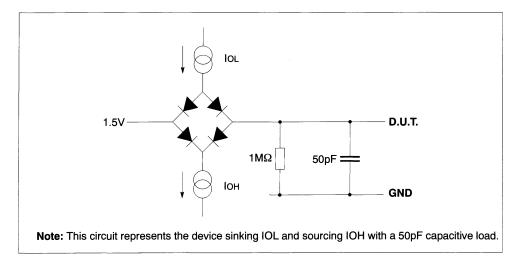

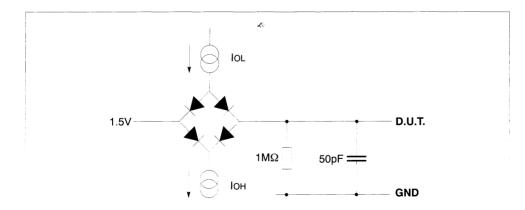

|   |      | 9.2                                    | Equivalent circuits                                                           | 118                                    |

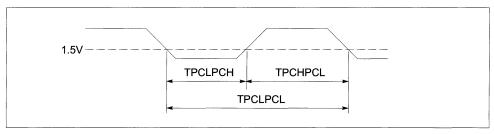

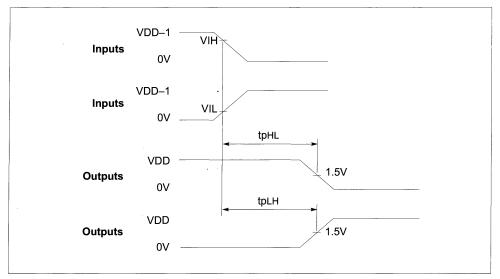

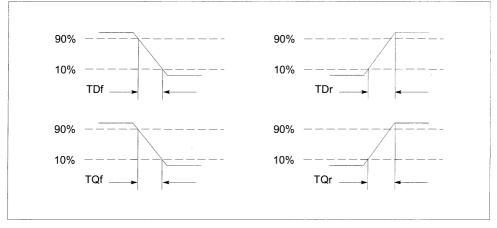

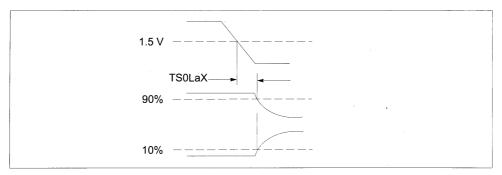

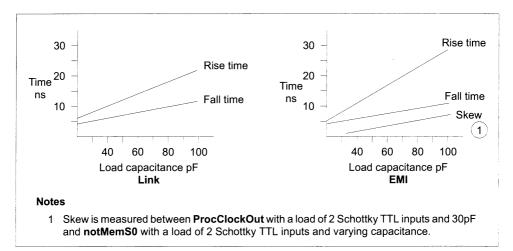

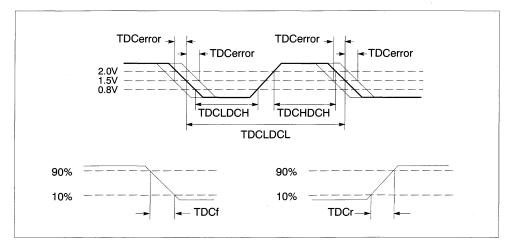

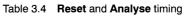

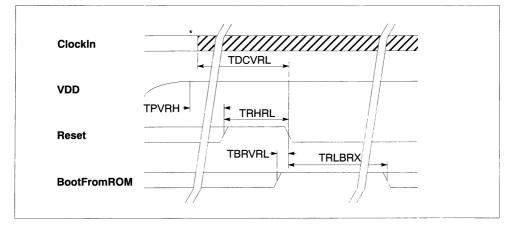

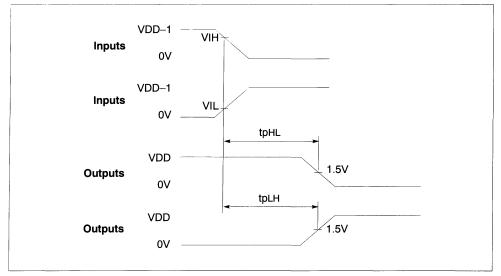

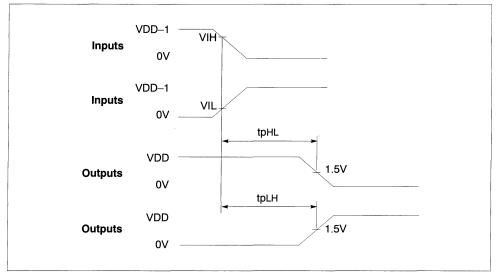

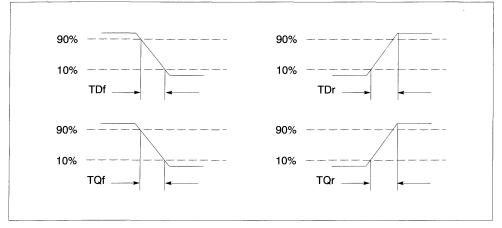

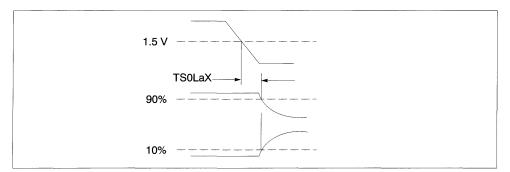

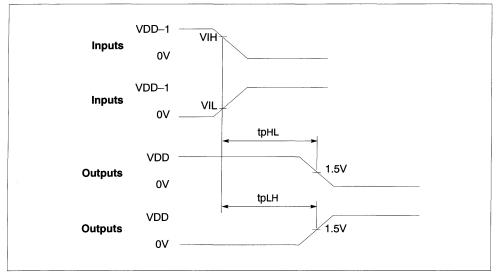

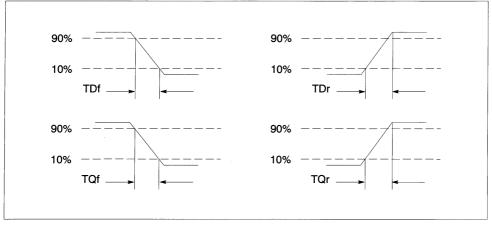

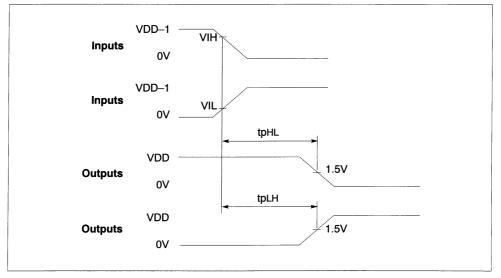

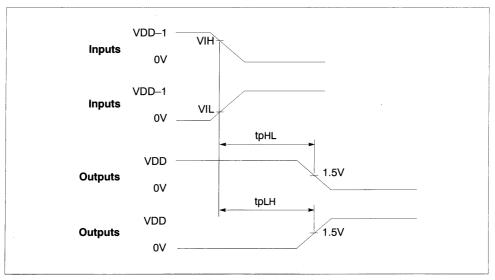

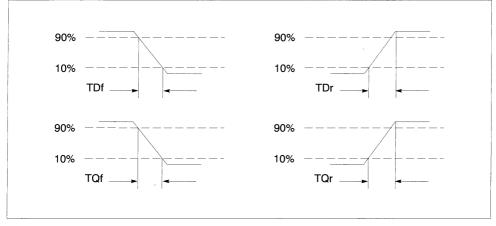

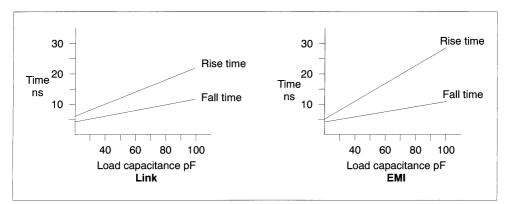

|   |      | 9.3                                    | AC timing characteristics                                                     | 119                                    |

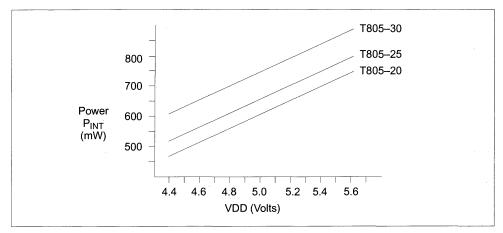

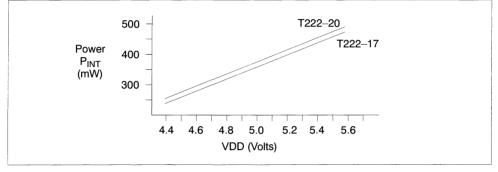

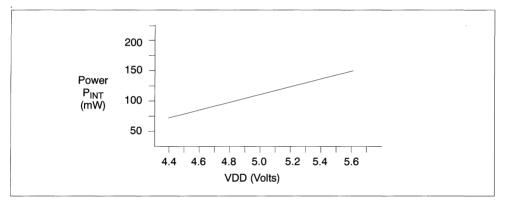

|   |      | 9.4                                    | Power rating                                                                  | 121                                    |

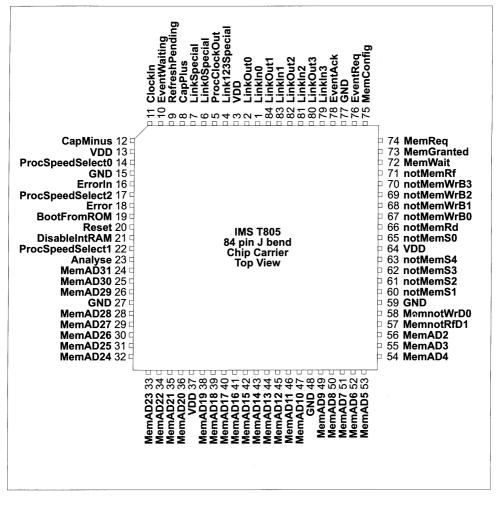

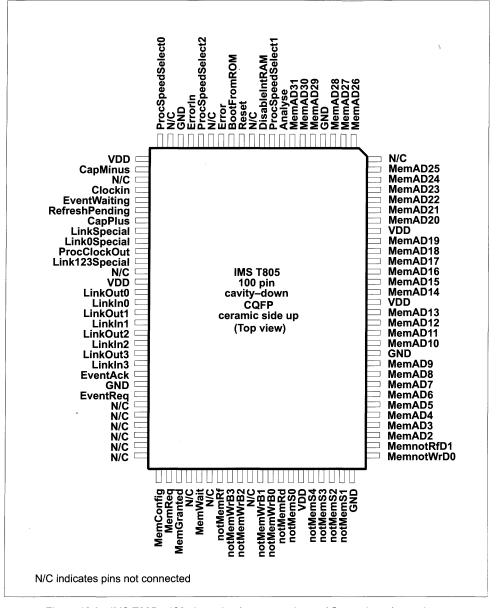

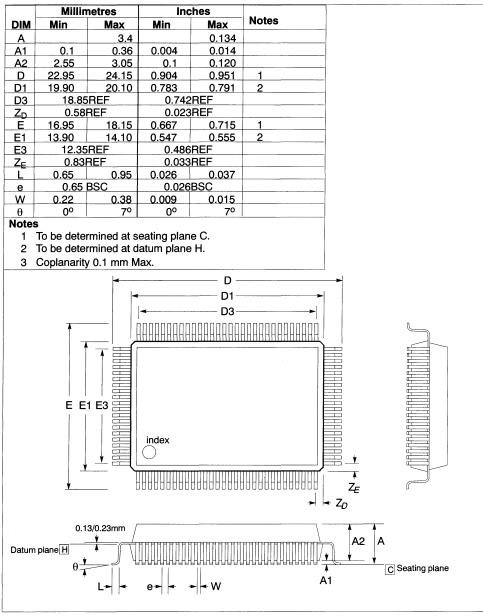

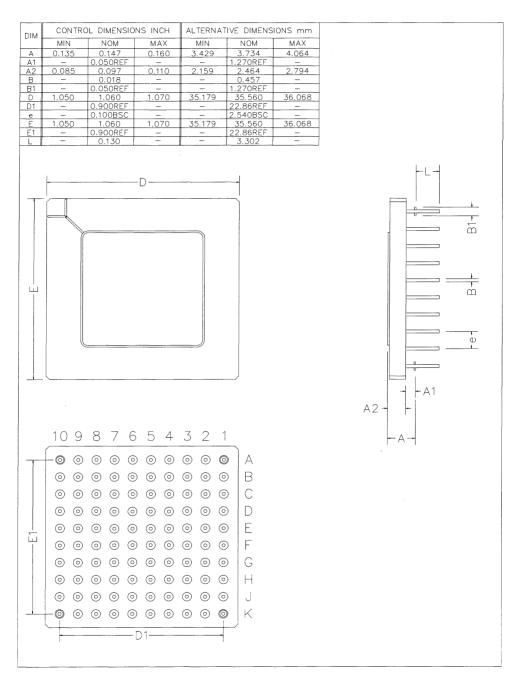

|   | 10   | Pack                                   | age pinouts                                                                   | 122                                    |

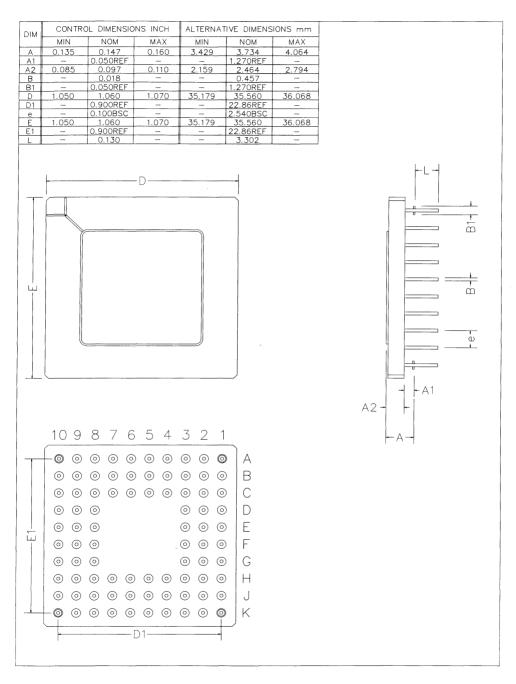

|   |      | 10.1                                   | 84 pin grid array package                                                     | 122                                    |

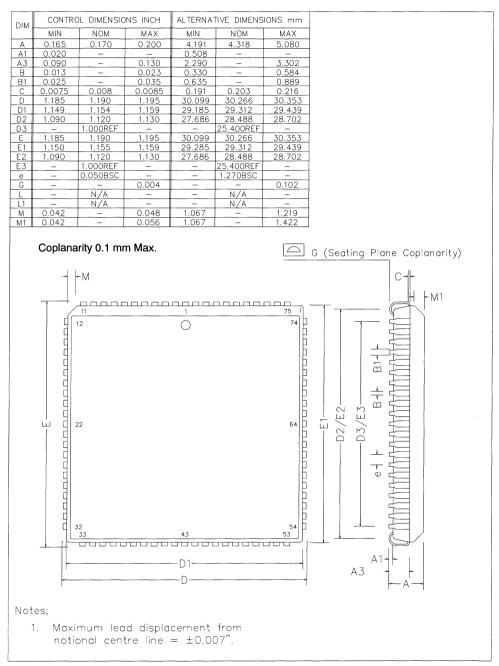

|   |      | 10.2                                   | 84 pin PLCC J-bend package                                                    | 123                                    |

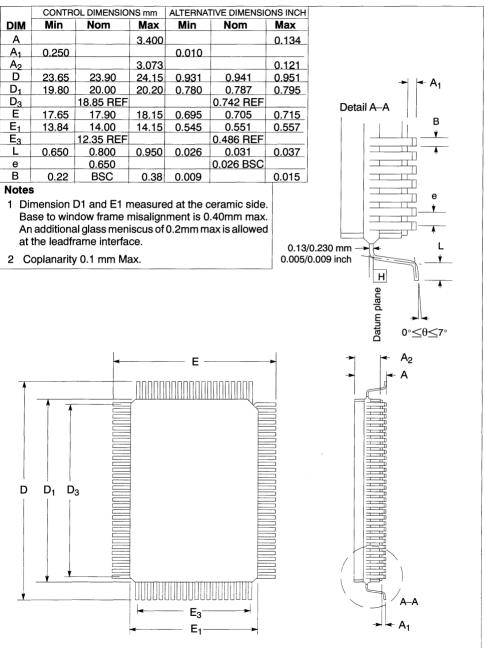

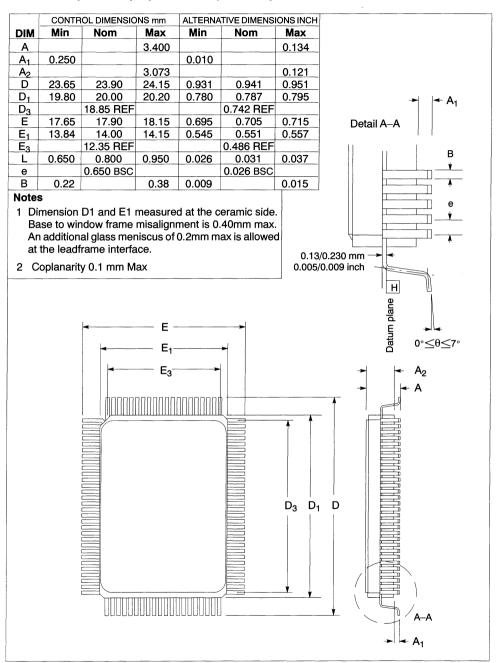

|   |      | 10.3                                   | 100 pin cavity-down ceramic quad flat pack package                            | 124                                    |

|   | 11   | Orde                                   | ring                                                                          | 125                                    |

| 7 | IM   | S 780                                  | 1 transputer                                                                  | 127                                    |

| ' | 1101 | 0,100                                  |                                                                               | 121                                    |

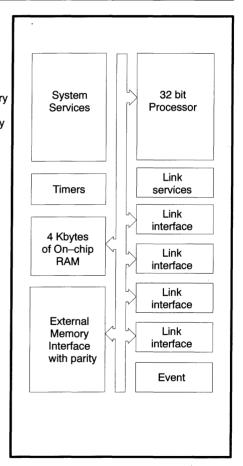

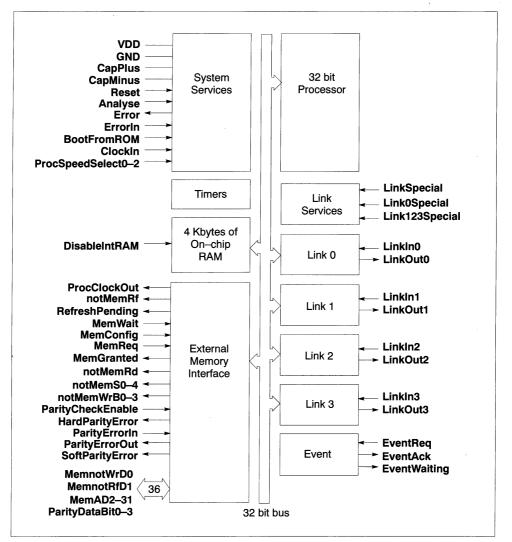

|   | 1    | Intro                                  | duction                                                                       | 128                                    |

|   | 2    | Pin d                                  | esignations                                                                   | 131                                    |

|   |      |                                        |                                                                               |                                        |

|   | 3    | Float                                  | ing point unit                                                                | 132                                    |

|   |      |                                        |                                                                               |                                        |

|   | 4    | Syste                                  | em services                                                                   | 134                                    |

|   | 4    | <b>Syste</b><br>4.1                    | em services                                                                   | <b>134</b><br>134                      |

|   | 4    | -                                      | Power                                                                         |                                        |

|   | 4    | 4.1                                    |                                                                               | 134                                    |

|   | 4    | 4.1<br>4.2                             | Power<br>CapPlus, CapMinus<br>ClockIn                                         | 134<br>134                             |

|   | 4    | 4.1<br>4.2<br>4.3                      | Power                                                                         | 134<br>134<br>134                      |

|   | 4    | 4.1<br>4.2<br>4.3<br>4.4               | Power<br>CapPlus, CapMinus<br>ClockIn<br>ProcSpeedSelect0-2                   | 134<br>134<br>134<br>135               |

|   | 4    | 4.1<br>4.2<br>4.3<br>4.4<br>4.5        | Power<br>CapPlus, CapMinus<br>ClockIn<br>ProcSpeedSelect0–2<br>Bootstrap      | 134<br>134<br>134<br>135<br>136        |

|   | 4    | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Power                                                                         | 134<br>134<br>134<br>135<br>135<br>136 |

|   | 5  | Men    | nory                                                             | 140        |

|---|----|--------|------------------------------------------------------------------|------------|

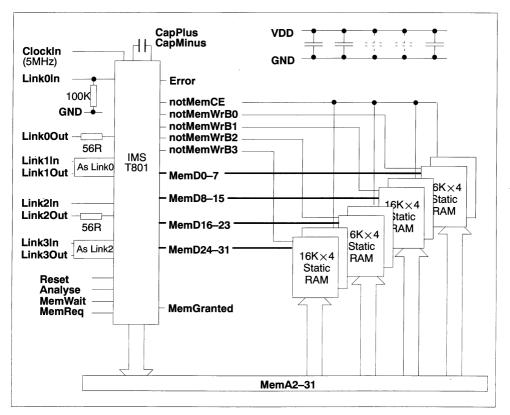

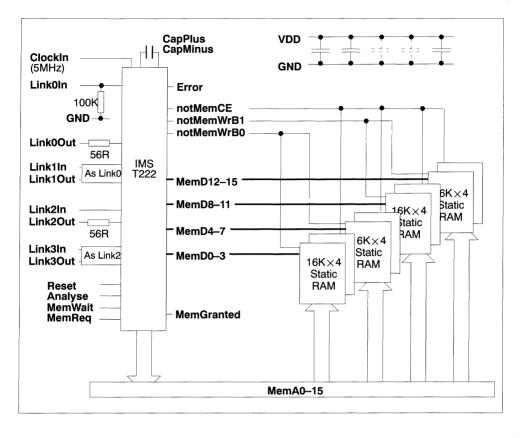

|   | 6  | Exte   | ernal memory interface                                           | 142        |

|   |    | 6.1    | Pin functions                                                    | 142        |

|   |    |        | 6.1.1 MemA2–31                                                   | 142        |

|   |    |        | 6.1.2 MemD0-31                                                   | 142        |

|   |    |        | 6.1.3 notMemCE                                                   | 143        |

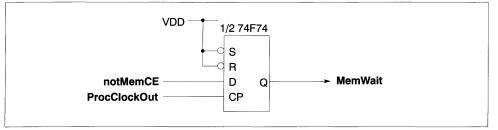

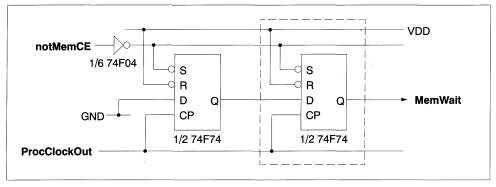

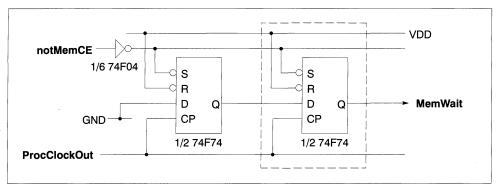

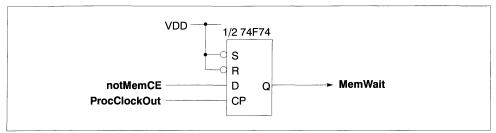

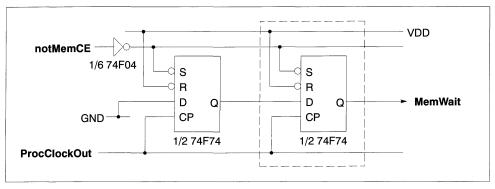

|   |    |        | 6.1.4 notMemWrB0–3<br>6.1.5 MemWait                              | 144        |

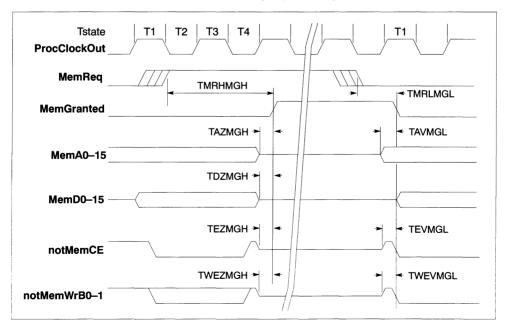

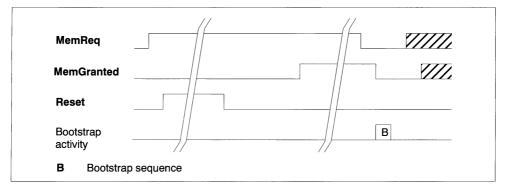

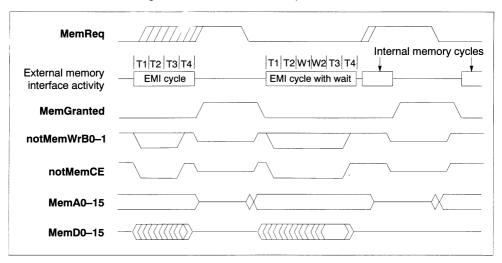

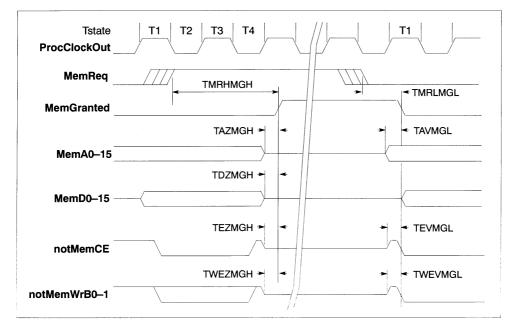

|   |    |        | 6.1.5         MemWait           6.1.6         MemReq, MemGranted | 144<br>144 |

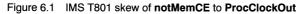

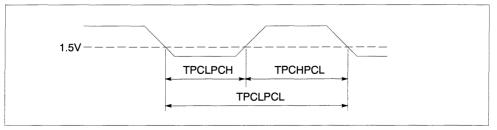

|   |    |        | 6.1.7 ProcClockOut                                               | 144        |

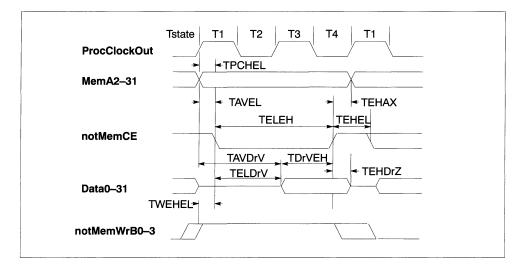

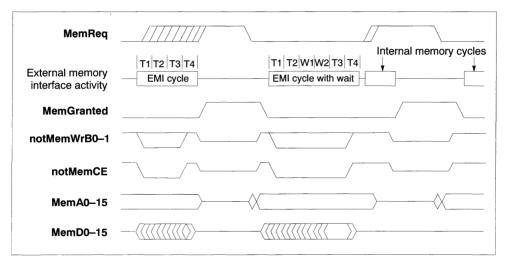

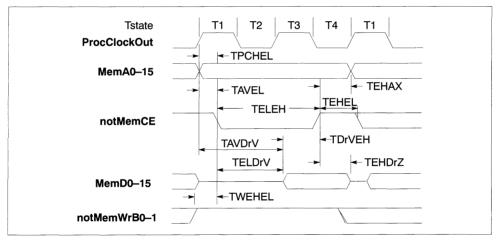

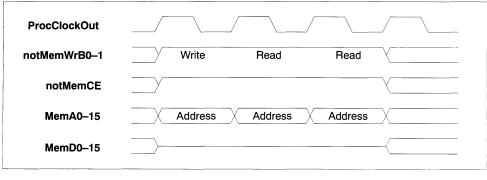

|   |    | 6.2    | Read cycle                                                       | 145        |

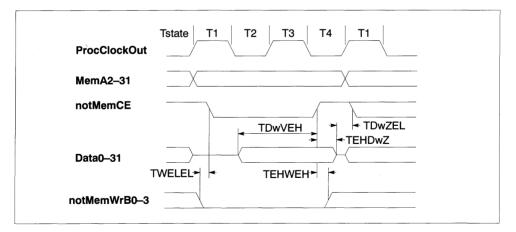

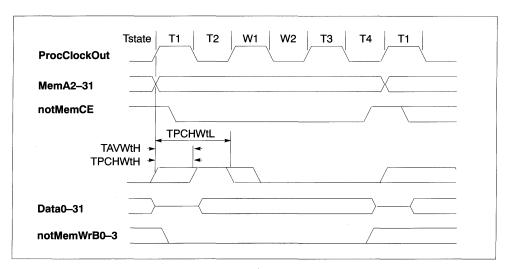

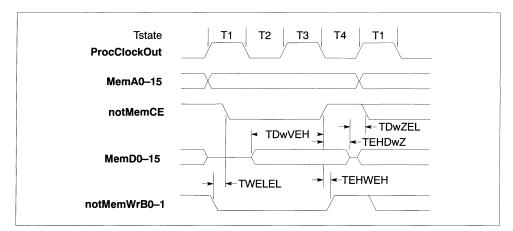

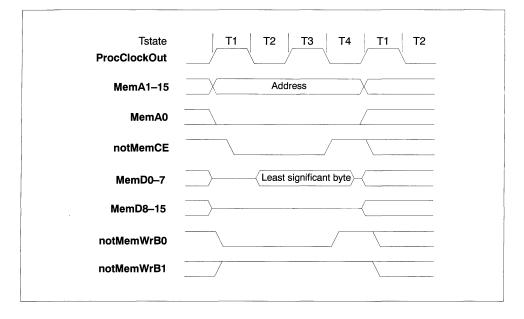

|   |    | 6.3    | Write cycle                                                      | 146        |

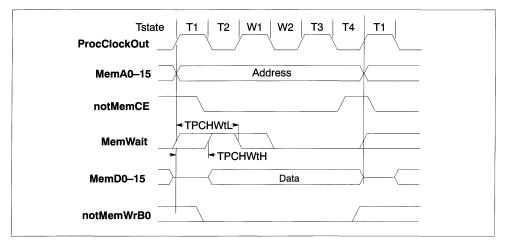

|   |    | 6.4    | Wait                                                             | 147        |

|   |    | 6.5    | Direct memory access                                             | 149        |

|   | 7  | Ever   | nts                                                              | 151        |

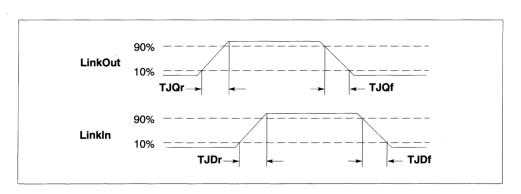

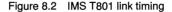

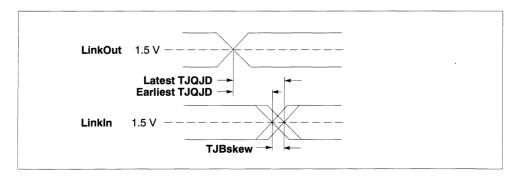

|   | 8  | Link   | S                                                                | 153        |

|   | 9  | Elec   | trical specifications                                            | 156        |

|   |    | 9.1    | DC electrical characteristics                                    | 156        |

|   |    | 9.2    | Equivalent circuits                                              | 158        |

|   |    | 9.3    | AC timing characteristics                                        | 159        |

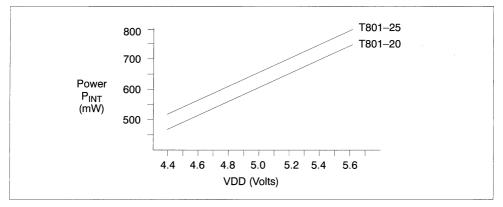

|   |    | 9.4    | Power rating                                                     | 160        |

|   | 10 | ) Pack | age pinouts                                                      | 161        |

|   |    | 10.1   | 100 pin grid array package                                       | 161        |

|   | 11 | Orde   | ring                                                             | 162        |

| 8 | IM | IS T42 | 6 transputer                                                     | 163        |

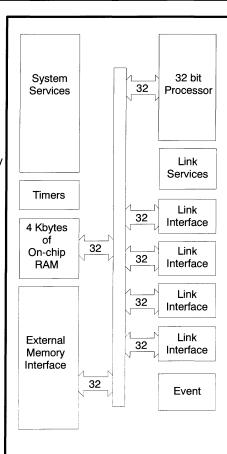

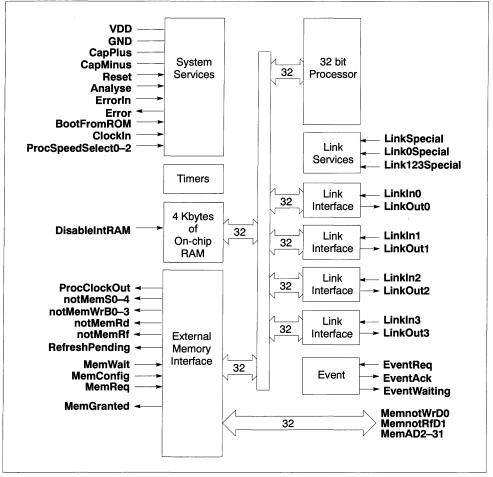

|   | 1  | Intro  | duction                                                          | 164        |

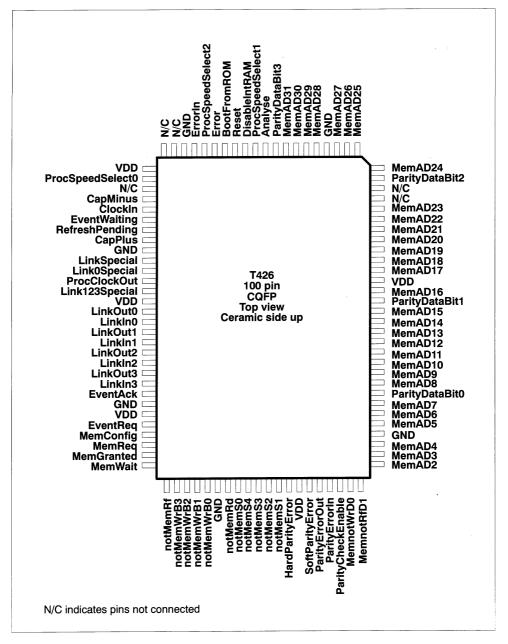

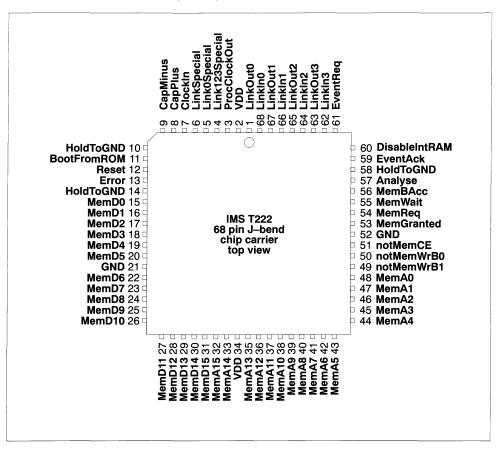

|   | 2  | Pin o  | lesignations                                                     | 166        |

|   | 3  | Syst   | em services                                                      | 168        |

|   |    | 3.1    | Power                                                            | 168        |

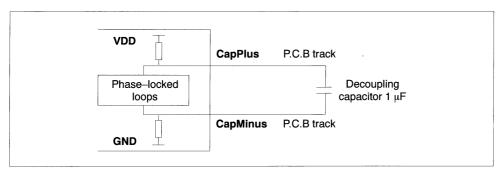

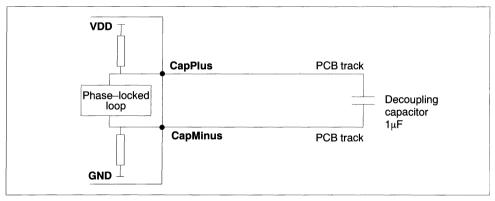

|   |    | 3.2    | CapPlus, CapMinus                                                | 168        |

|   |    | 3.3    | ClockIn                                                          | 168        |

|   |    | 3.4    | ProcSpeedSelect0-2                                               | 169        |

|   |    | 3.5    | Bootstrap                                                        | 170        |

|   |    | 3.6    | Peek and poke                                                    | 170        |

|   |    |        |                                                                  |            |

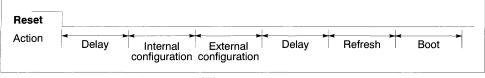

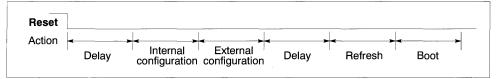

|   | 3.7   | Reset         |                             | 171        |

|---|-------|---------------|-----------------------------|------------|

|   | 3.8   |               | ·                           | 171        |

|   | 3.9   | -             |                             | 173        |

| 4 | Mem   | ory           |                             | 174        |

|   |       | -             |                             |            |

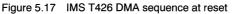

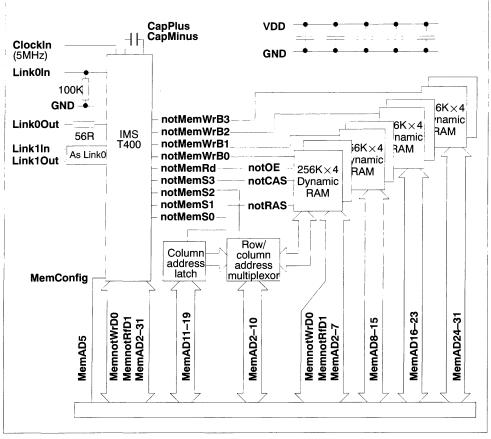

| 5 | Exte  | rnal memo     | ry interface                | 176        |

|   | 5.1   | Pin functions |                             | 177        |

|   |       | 5.1.1 Me      | emAD2–31                    | 177        |

|   |       | 5.1.2 Pa      | rityDataBit0–3              | 177        |

|   |       |               | rityCheckEnable             | 177        |

|   |       | 5.1.4 So      | ftParityError               | 177        |

|   |       |               | rdParityError               | 177        |

|   |       |               | rityErrorIn, ParityErrorOut | 177        |

|   |       |               | tMemRd                      | 177        |

|   |       |               | emnotWrD0                   | 177        |

|   |       |               | tMemWrB0–3                  | 177        |

|   |       |               | tMemS0–4                    | 178        |

|   |       |               | mWait                       | 178        |

|   |       |               | emnotRfD1                   | 178        |

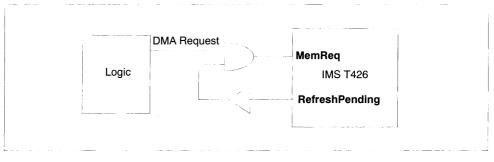

|   |       |               |                             | 178        |

|   |       |               | freshPending                | 178        |

|   |       |               | emReq, MemGrantedemConfig   | 178<br>178 |

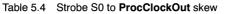

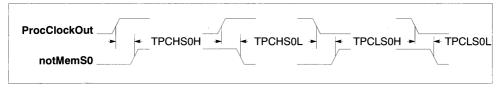

|   |       |               | pcClockOut                  | 178        |

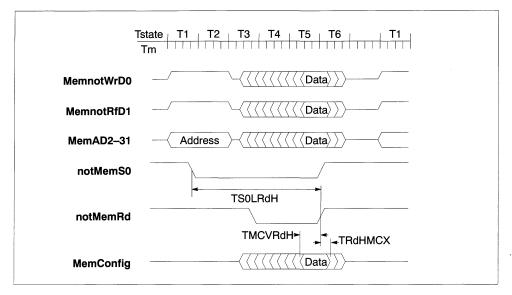

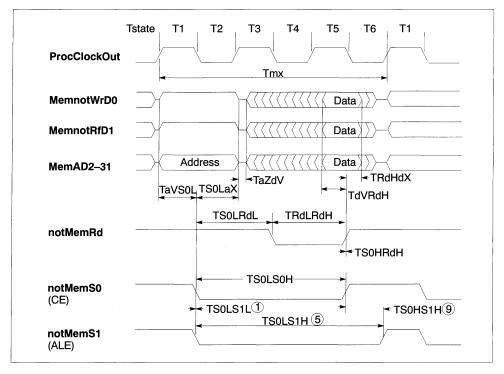

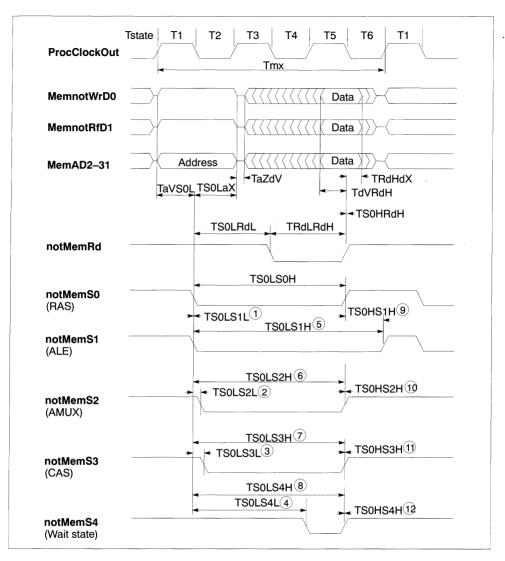

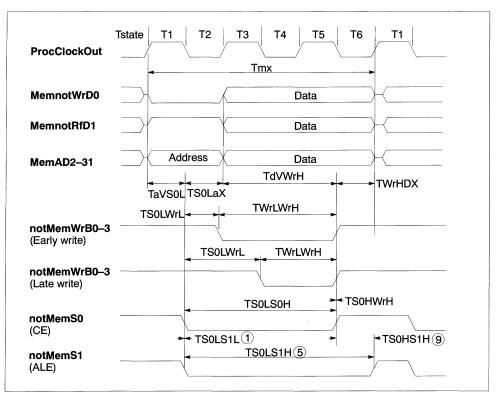

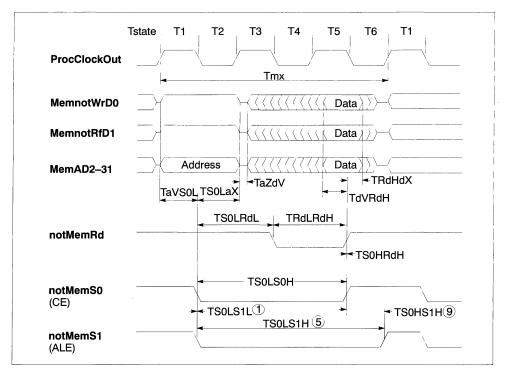

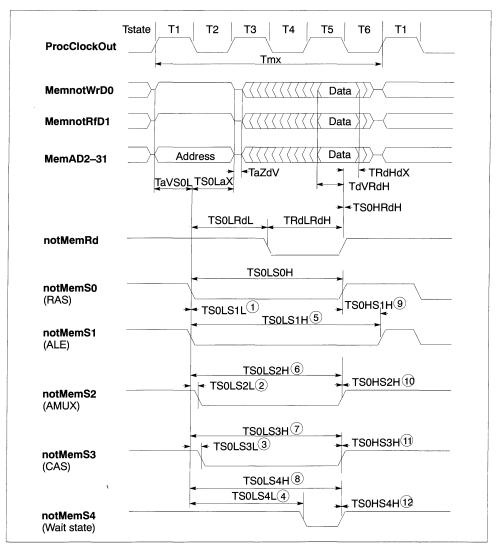

|   | 5.2   |               | bolice.cout                 | 179        |

|   | 5.3   |               |                             | 180        |

|   |       |               |                             |            |

|   | 5.4   |               |                             | 182        |

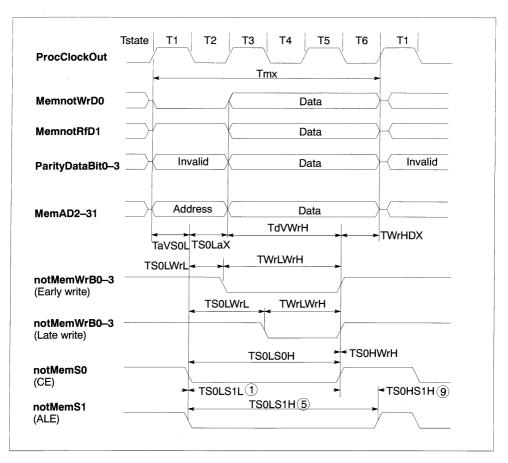

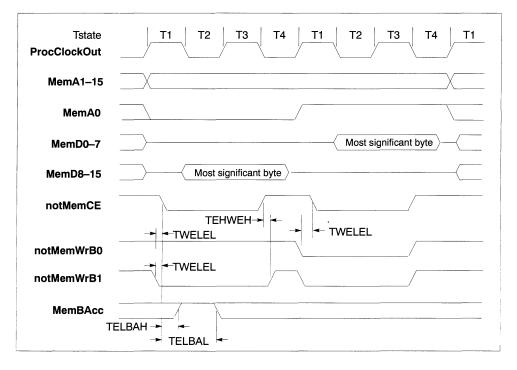

|   | 5.5   | Write cycle . |                             | 185        |

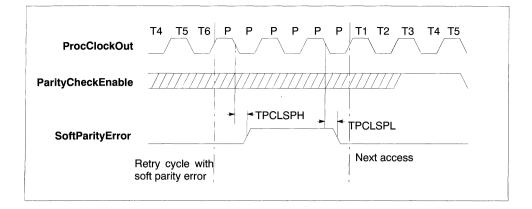

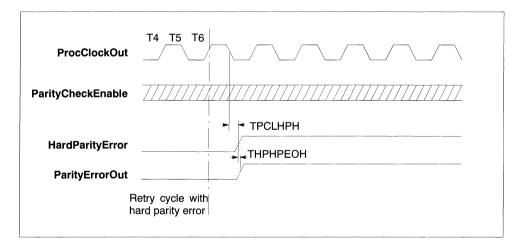

|   | 5.6   | Parity errors |                             | 187        |

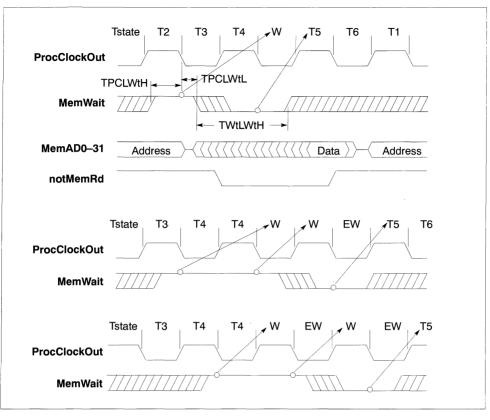

|   | 5.7   | Wait          |                             | 190        |

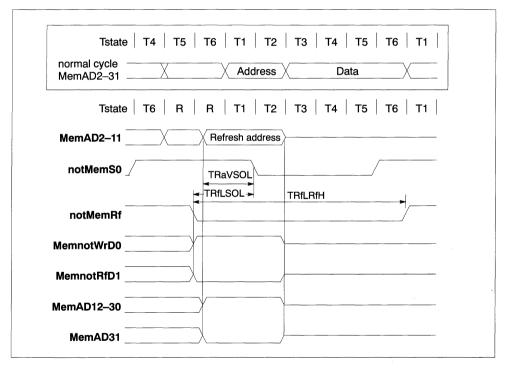

|   | 5.8   | Memory refre  | sh                          | 192        |

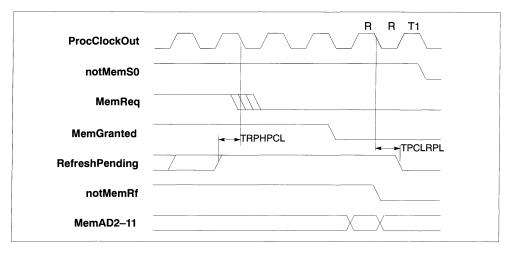

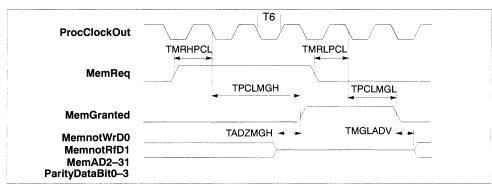

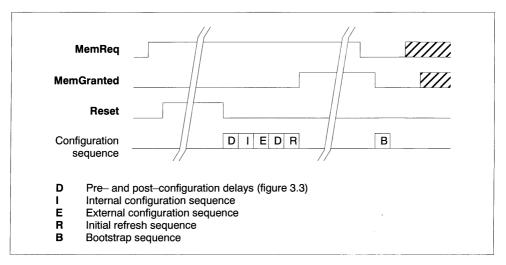

|   | 5.9   | -             | y access                    | 195        |

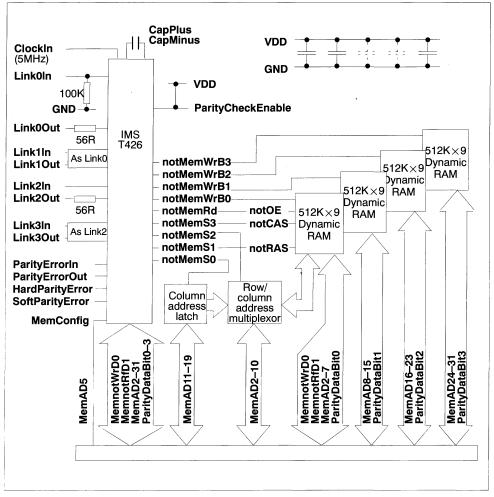

|   | 5.10  |               | iguration                   | 197        |

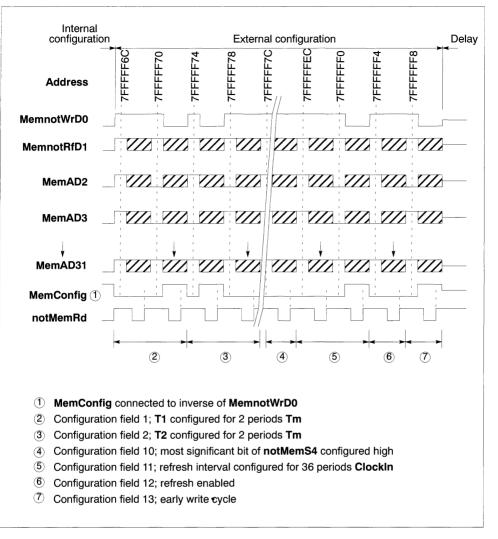

|   | 5.10  | -             | -                           |            |

|   |       |               | ernal configuration         | 198<br>201 |

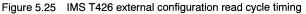

| 6 | Evon  |               |                             | 206        |

| Ů | Lven  |               |                             | 200        |

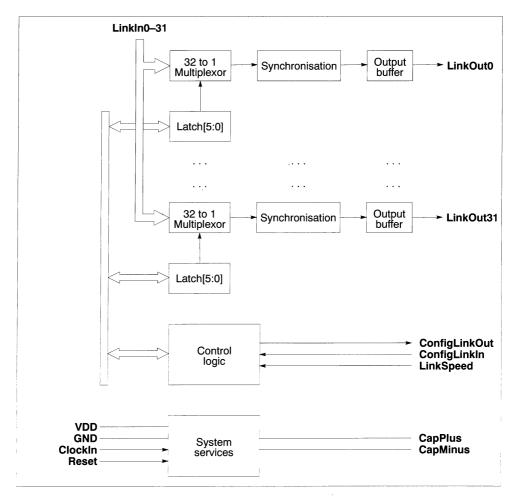

| 7 | Links |               | ••••••                      | 208        |

| 8 | Elect | rical specif  | fications                   | 211        |

|   | 8.1   | Absolute max  | imum ratings                | 211        |

|   | 8.2   |               | nditions                    | 211        |

|   |       |               | characteristics             |            |

|   | 8.3   |               |                             | 212        |

|   | 8.4   | •             | cuits                       | 212        |

|   | 8.5   | AC timing cha | aracteristics               | 213        |

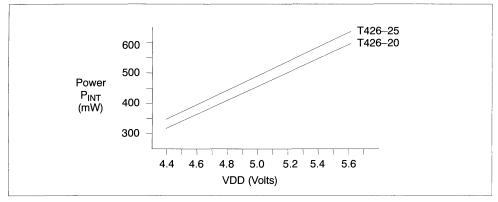

|   |    | 8.6    | Power rating                                       | 215        |

|---|----|--------|----------------------------------------------------|------------|

|   | 9  | Pack   | age pinouts                                        | 216        |

|   |    | 9.1    | 100 pin cavity-down ceramic quad flat pack package | 216        |

|   | 10 | ) Orde | ering                                              | 217        |

|   |    |        | anng                                               | 217        |

| 9 | IN | IS T42 | 25 transputer                                      | 219        |

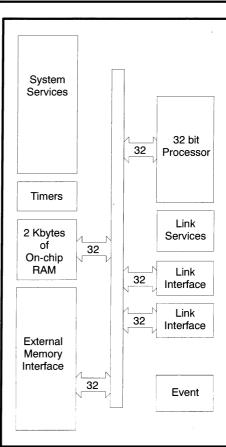

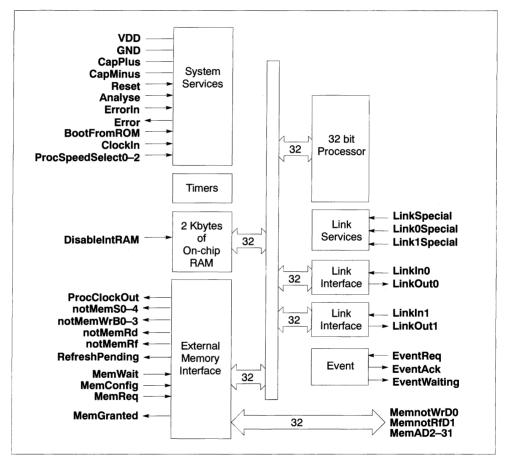

|   | 1  | Intro  | duction                                            | 220        |

|   | 2  | Pin c  | designations                                       | 222        |

|   | 3  | Syst   | em services                                        | 223        |

|   |    | 3.1    | Power                                              | 223        |

|   |    | 3.2    | CapPlus, CapMinus                                  | 223        |

|   |    | 3.3    | ClockIn                                            | 223        |

|   |    | 3.4    | ProcSpeedSelect0-2                                 | 224        |

|   |    | 3.5    | Bootstrap                                          | 225        |

|   |    | 3.6    | Peek and poke                                      | 225        |

|   |    | 3.7    | Reset                                              | 226        |

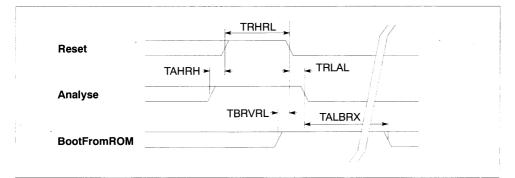

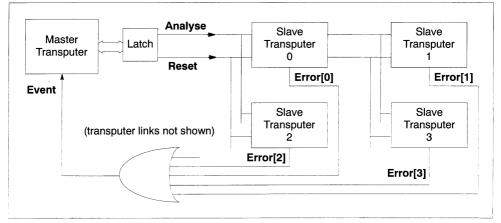

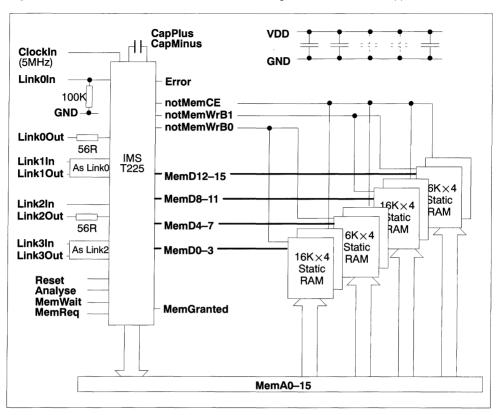

|   |    | 3.8    | Analyse                                            | 226        |

|   |    | 3.9    | Error, Errorin                                     | 228        |

|   | 4  | Mem    | ory                                                | 229        |

|   | 5  | Exte   | rnal memory interface                              | 231        |

|   |    | 5.1    | Pin functions                                      | 232        |

|   |    |        | 5.1.1 MemAD2–31                                    | 232        |

|   |    |        | 5.1.2 notMemRd                                     | 232        |

|   |    |        | 5.1.3 MemnotWrD0                                   | 232        |

|   |    |        | 5.1.4 notMemWrB0–3                                 | 232        |

|   |    |        | 5.1.5 notMemS0–4                                   | 232        |

|   |    |        | 5.1.6 MemWait                                      | 232<br>232 |

|   |    |        | 5.1.8 notMemRf                                     | 232        |

|   |    |        | 5.1.9 RefreshPending                               | 232        |

|   |    |        | 5.1.10 MemReq, MemGranted                          | 233        |

|   |    |        | 5.1.11 MemConfig                                   | 233        |

|   |    |        | 5.1.12 ProcClockOut                                | 233        |

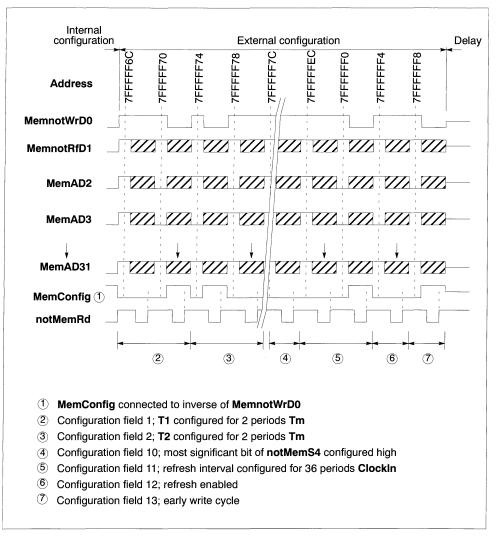

|   |    | 5.2    | Read cycle                                         | 235        |

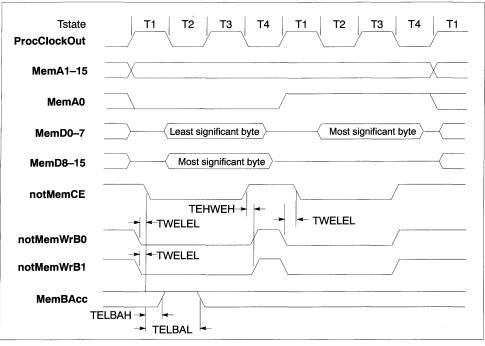

|   |    | 5.3    | Write cycle                                        | 240        |

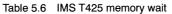

|   |    | 5.4    | Wait                                               | 241        |

|   |    | 5.5    | Memory refresh                                     | 243        |

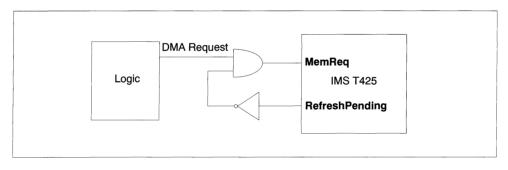

|   |    | 5.6    | Direct memory access                               | 246        |

## Contents

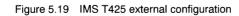

|                      | 5.7                                                                                                     | Memory                                                                                                                                                    | configuration                                                                                                 | 249                                                                                                                                                                                                                                                                                                                            |

|----------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |                                                                                                         | 5.7.1                                                                                                                                                     | Internal configuration                                                                                        | 249                                                                                                                                                                                                                                                                                                                            |

|                      |                                                                                                         | 5.7.2                                                                                                                                                     | External configuration                                                                                        | 251                                                                                                                                                                                                                                                                                                                            |

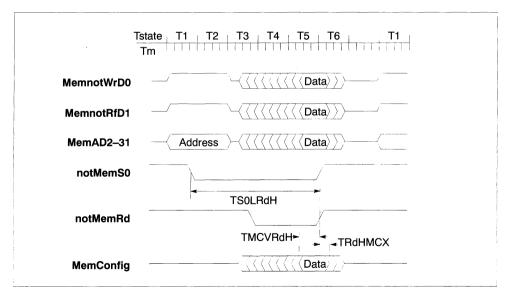

| 6                    | Evei                                                                                                    | nts                                                                                                                                                       |                                                                                                               | 257                                                                                                                                                                                                                                                                                                                            |

| 7                    | Link                                                                                                    | s                                                                                                                                                         |                                                                                                               | 259                                                                                                                                                                                                                                                                                                                            |

| 8                    | Elec                                                                                                    | trical sp                                                                                                                                                 | pecifications                                                                                                 | 262                                                                                                                                                                                                                                                                                                                            |

|                      | 8.1                                                                                                     | Absolute                                                                                                                                                  | e maximum ratings                                                                                             | 262                                                                                                                                                                                                                                                                                                                            |

|                      | 8.2                                                                                                     |                                                                                                                                                           | ng conditions                                                                                                 |                                                                                                                                                                                                                                                                                                                                |

|                      | 8.3                                                                                                     | DC elect                                                                                                                                                  | rical characteristics                                                                                         | 263                                                                                                                                                                                                                                                                                                                            |

|                      | 8.4                                                                                                     | Equivale                                                                                                                                                  | ent circuits                                                                                                  | 263                                                                                                                                                                                                                                                                                                                            |

|                      | 8.5                                                                                                     | AC timin                                                                                                                                                  | g characteristics                                                                                             | 264                                                                                                                                                                                                                                                                                                                            |

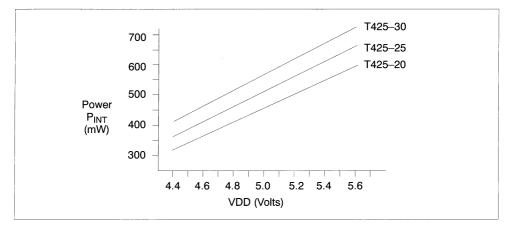

|                      | 8.6                                                                                                     | Power ra                                                                                                                                                  | ating                                                                                                         | 266                                                                                                                                                                                                                                                                                                                            |

| 9                    | Pack                                                                                                    | age pin                                                                                                                                                   | iouts                                                                                                         | 267                                                                                                                                                                                                                                                                                                                            |