## **Product range**

# **IMS T424 transputer**

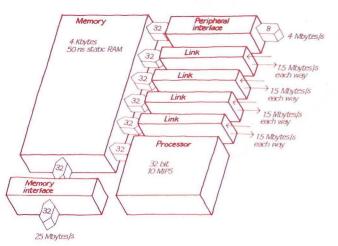

The IMS T424 is a 32 bit transputer providing 10 MIPS, with 4 Kbytes of static RAM, a 32 bit multiplexed memory interface, an 8 bit peripheral interface and four standard INMOS links.

## **IMS T222 transputer**

The IMS T222 is a 16 bit transputer. It has an identical instruction set to the IMS T424 and programs will behave identically on both the T222 and T424, providing the 16 bit range of the T222 is not exceeded.

## IMS G213 graphics processor

The IMS G213 is a high performance programmable graphics controller, suitable for high quality colour graphics. It includes a 16 bit processor, 2 Kbytes of static RAM and two INMOS links for connecting to transputer systems.

## IMS M212 disk processor

The IMS M212 is an integrated programmable disk controller for floppy disks and Winchesters. It includes software configurable crc/ecc, as well as a 16 bit processor, 2 Kbytes of static RAM and two INMOS links for connecting to transputer systems.

## Occam

A simple high level language for both specifying and programming concurrent systems of one or more processors.

## **Occam evaluation kit**

The occam evaluation kit is an electronic tutorial system for demonstrating the basic principles of occam.

# Occam programming system

A personal workstation with 256 Kbytes of memory providing an initial programming tool for developing occam programs.

# Inmos

**INMOS** Limited Whitefriars Lewins Mead Bristol BS1 2NP Telephone (0272) 290861 Telex 444723

**INMOS** Corporation PO Box 16000 Colorado Springs CO 80935 USA Telephone (303) 630 4000 Telex 910 920 4904

**INMOS SARL** Immeuble Monaco 7 rue Le Corbusier SILIC 219 94518 Rungis Cedex France Telephone (1) 687 22 01 Telex 201222

**INMOS GmbH** Untere Hauptstrasse 7 8057 Echina West Germany Telephone (089) 319 10 28 Telex 522645

72-TRN-002 000

DATA12526

mos

**Data card**

The IMS T424 is the first of a range of transputer products which will span the entire spectrum of microprocessor applications, from low cost microcontrollers up to supercomputers and fifth generation systems. All transputers will be totally compatible, whatever their word length, instruction set, processor speed, or interfaces.

# **IMS T424**

32 bit system providing 10 MIPS (millions of instructions per second) processing power with memory and concurrent communication capability, all on a single chip.

## Processor

Reduced instruction set for compact programs, efficient high level language implementation and direct support of concurrency.

High performance arithmetic with 50 ns basic instructions, 600 ns process switch and 950 ns multiplication.

# Memory

4 Kbytes of static memory giving a maximum data rate of 80 Mbytes/s. Multiport access for processor, peripheral interface and each INMOS link.

## **Memory Interface**

32 bit multiplexed interface, with programmable timing to support mixed memory systems. Extends direct address memory space up to 4 Gbytes with a maximum data rate of 25 Mbytes/s.

| Memor            | y interface signals                        | Periph        | eral interface signals                                                   |

|------------------|--------------------------------------------|---------------|--------------------------------------------------------------------------|

| Ras              | → Address valid                            | Iclk          | - Peripheral interface clock                                             |

| Cas              | → Column address strobe                    | Req           | $\longrightarrow$ Request for data transfer                              |

| Re               | $\rightarrow$ Read data enable             | Ack           | - Acknowledge data transfer                                              |

| We0-3            | $\rightarrow$ Byte 0 to 3 write data valid | 1/0           | $\longrightarrow$ Direction of transfer                                  |

| Amux             | → Address multiplex                        | C0,1          |                                                                          |

| AD0-31<br>Mcycle |                                            | D0-7<br>Event | is being addressed<br>↔ 8 bit wide data bus<br>← Event input to schedule |

| Await            | ← Asynchronous wait input                  |               | a process                                                                |

# **Peripheral Interface**

8 bit bi-directional interface, providing connection to industry standard devices like controllers, processors and memory.

Concurrent block transfer capability of 4 Mbytes/s.

# **INMOS** links

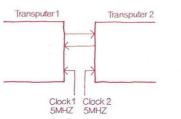

Four INMOS standard serial links providing concurrent message passing capability to other transputer devices.

Programmable data rate up to 1.5 Mbytes/s full duplex on each link to enable local and remote connection.

# Technology

250 000 devices fabricated in an advanced 2 micron cMOS process, mounted in an 84 contact leadless chip carrier.

# Programming

Programmable in most standard high level languages: Ada, Basic, C, PASCAL...

Direct execution of occam for maximum performance and exploitation of concurrency.

Interactive program development using occam as the lowest level image of the system.

## Performance

|                       |                       | Program<br>size<br>(bytes) | Execution<br>time<br>(ns) |

|-----------------------|-----------------------|----------------------------|---------------------------|

| Arithmetic operators  | +,-                   | 1                          | 50                        |

|                       | * (multiplication)    | 1                          | 950                       |

|                       | /(division)           | 2                          | 1950                      |

| Comparison operators  | >,-,<>,<,<-,>-        | 2                          | 100                       |

| Logical operators     | AND, OR               | 1                          | 50                        |

|                       | /\/,>< (xor)          | 2                          | 100                       |

| Shift operators       | <<[n],>>[n]           | 2                          | 50n+50                    |

| Identifiers           | variable              | 1.7                        | 120                       |

| Expression evaluation | constant              | 1.3                        | 70                        |

| Constructors          | SEQ [n]               | 0                          | 0                         |

|                       | PAR [n]               | 9n-7 .                     | 450n-200                  |

|                       | ALT [n]               | 8n+7                       | 600n+600                  |

|                       | IF [n]                | Зn                         | 150n                      |

|                       | WHILE                 | 4                          | 200                       |

| Primitives            | ! (output), ? (input) | 4                          | 625                       |

|                       | ! [n], ? [n] (vector) | 4                          | 50n+625                   |

|                       | :- (assignment)       | 0                          | 0                         |

|                       | := [n] (vector)       | 4                          | 100n+300                  |

The transputer is a high performance component when used in single transputer configurations. Pipelines and arrays of transputers can be used to provide greatly increased performance by exploiting the concurrency inherent in many applications.