## MEMORY DATABOOK

First Edition February 1989

#### **INMOS Databook Series**

Transputer Databook Transputer Support Databook: Development and Sub-systems Memory Databook Graphics Databook Digital Signal Processing Databook

Copyright ©INMOS Limited 1989

INMOS reserves the right to make changes in specifications at any time and without notice. The information furnished by INMOS in this publication is believed to be accurate; however, no responsibility is assumed for its use, nor for any infringement of patents or other rights of third parties resulting from its use. No licence is granted under any patents, trademarks or other rights of INMOS.

, Inmos, IMS and OCCAM are trademarks of the INMOS Group of Companies.

INMOS document number: 42-1261-00

#### Contents

|          | Preface and Selection Guide                                               | v          |

|----------|---------------------------------------------------------------------------|------------|

|          | INMOS                                                                     |            |

| 1        | 1.1 Introduction                                                          | 1.1        |

| <u> </u> | 1.2 Static RAMs                                                           | 1.3        |

|          | 1.3 Manufacturing                                                         | 1.3        |

|          | 1.4 Assembly                                                              | 1.3        |

| ····     | 1.5 Test                                                                  | 1.3        |

|          | 1.6 Quality and reliability                                               | 1.3        |

|          | 1.7 Military                                                              | 1.3        |

|          | 1.8 Future developments                                                   | 1.4        |

|          | 1.8.1 Research and development                                            | 1.4        |

|          | 1.8.1 Process developments                                                | 1.4        |

|          | 1.9 Package developments                                                  | 1.4        |

|          |                                                                           |            |

| 2        | Commercial RAMs                                                           | 2.1        |

|          | IMS 1203 (4K) 4K×1 CMOS Static RAM                                        | 2.3        |

|          | IMS 1223 (4K) 1K×4 CMOS Static RAM                                        | 2.11       |

|          | IMS 1403 (16K) 16K×1 CMOS Static RAM                                      | 2.19       |

|          | IMS 1423 (16K) 4K×4 CMOS Static RAM                                       | 2.27       |

|          | IMS 1600/1601 (64K) 64K×1 CMOS Static RAM                                 | 2.35       |

|          | IMS 1620 (64K) 16K×4 CMOS Static RAM                                      | 2.43       |

|          | IMS 1624 (64K) 16K×4 (OE) CMOS Static RAM                                 | 2.51       |

| 3        | Military RAMs                                                             | 3.1        |

| -        | IMS1203M (4K) 4K×1 CMOS Static RAM                                        | 3.3        |

|          | IMS1223M (4K) 1K×4 CMOS Static RAM                                        | 3.11       |

|          | IMS1400M (16K) 16K×1 NMOS Static RAM                                      | 3.19       |

|          | IMS1403M/LM (16K) 16K×1 CMOS Static RAM                                   | 3.27       |

|          | IMS1420M (16K) 4K×4 NMOS Static RAM                                       | 3.35       |

|          | IMS1423M (16K) 4K×4 CMOS Static RAM                                       | 3.43       |

|          | IMS1600M/1601LM (64K) 64K×1 CMOS Static RAM                               | 3.51       |

|          | IMS1620M/LM (64K) 16K×4 CMOS Static RAM                                   | 3.59       |

|          | IMS1624M/LM (64K) 16K×4 (OE) CMOS Static RAM                              | 3.67       |

|          | IMS1630M/LM (64K) 8K×8 CMOS Static RAM                                    | 3.75       |

|          | IMS2600M (64K) 64K×1 NMOS Dynamic RAM                                     | 3.83       |

|          | <u> </u>                                                                  |            |

| <u>A</u> | Military qualification                                                    | A.1        |

|          | A.1 Military qualification                                                | A.3        |

|          | A.1.1 Military product program<br>A.1.2 Standard military drawing program | A.3<br>A.3 |

|          |                                                                           | <u></u>    |

| В        | Cross reference                                                           | B.1        |

|          | B.1 Product cross reference                                               | B.3        |

|          | B.2 Standard military drawing reference                                   | B.7        |

| С        | Quality and reliability                                                   | C.1        |

|          | C.1 Total quality control (TQC) and reliability program                   | C.3        |

|          | C.2 Quality and reliability in design                                     | C.3        |

|          | C.3 Document control                                                      | C.4        |

|          | C.4 New product qualification                                             | C.4        |

|   | C.5     | Product monitoring programme                                    | C.4  |

|---|---------|-----------------------------------------------------------------|------|

|   | C.6     | Production testing and quality monitoring procedure             | C.5  |

|   |         | C.6.1 Reliability testing                                       | C.5  |

|   |         | C.6.2 Production testing                                        | C.5  |

|   |         | C.6.3 Quality monitoring procedure                              | C.6  |

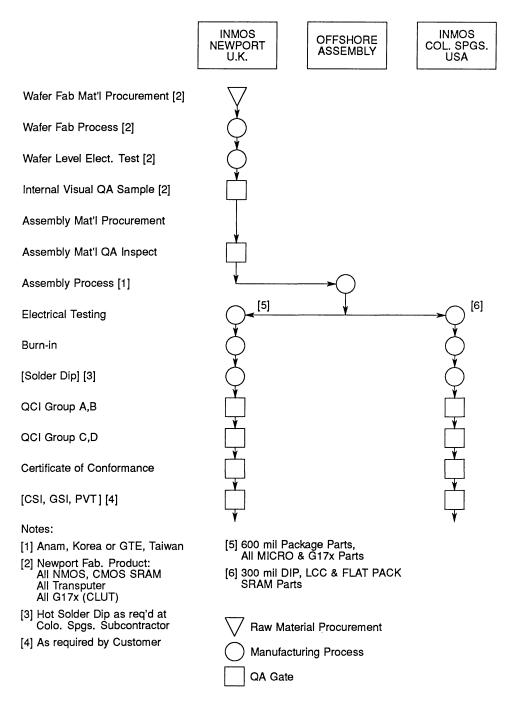

|   |         | Material procurement and product flow diagram                   | C.7  |

| D | Gene    | ral information                                                 | D.1  |

| - | D.1     | Thermal considerations                                          | D.3  |

|   | <u></u> | D.1.1 Thermal resistance                                        | D.3  |

|   |         | D.1.2 Junction temperature                                      | D.3  |

|   |         | D.1.3 K-factor and $\theta_{ia}$ measurement                    | D.3  |

|   |         | D.1.4 Factors affecting $\theta_{ia}$                           | D.3  |

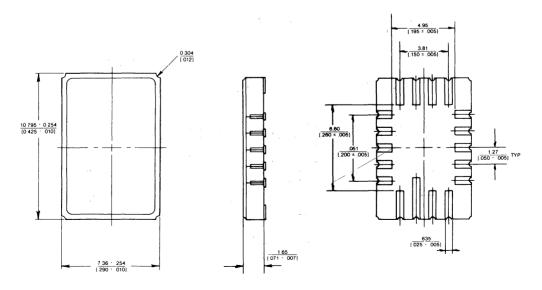

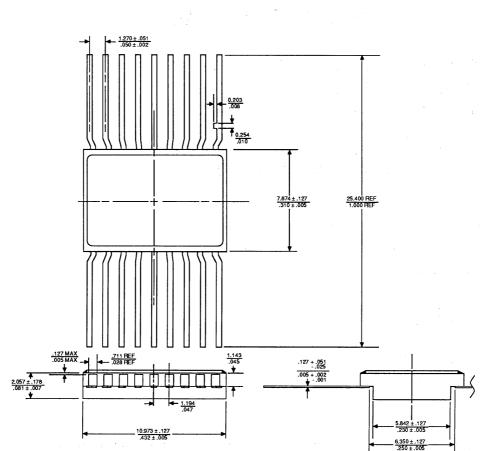

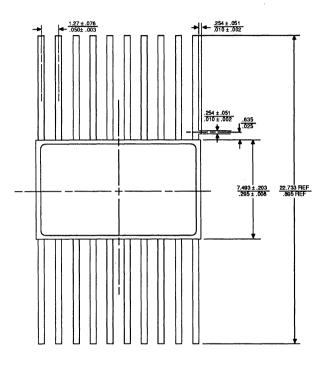

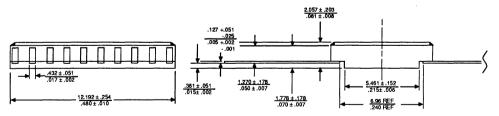

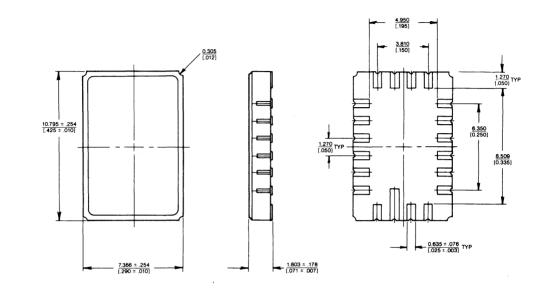

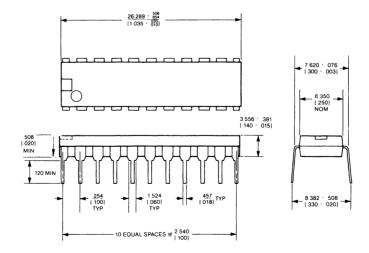

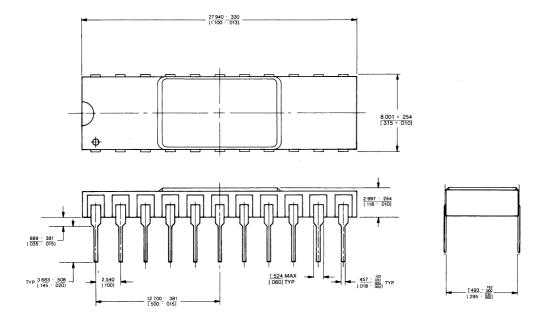

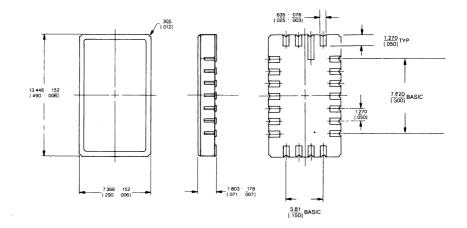

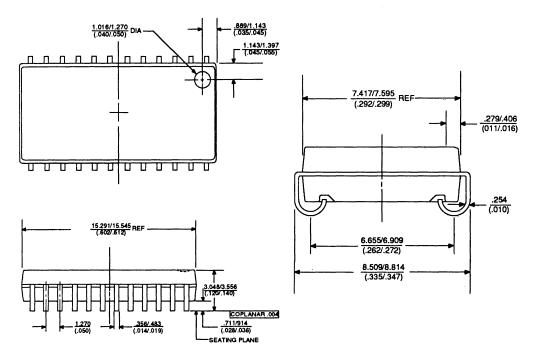

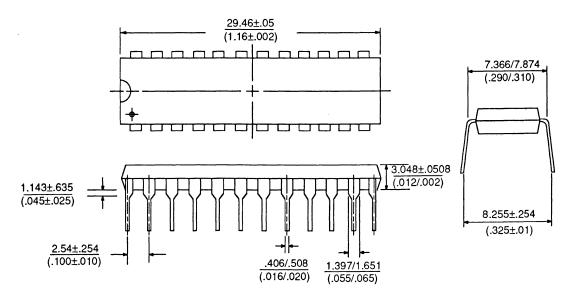

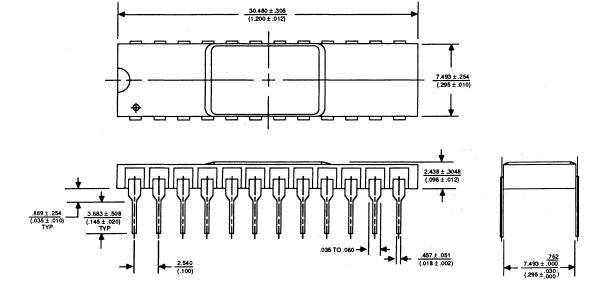

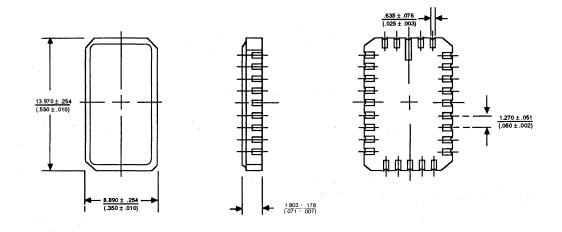

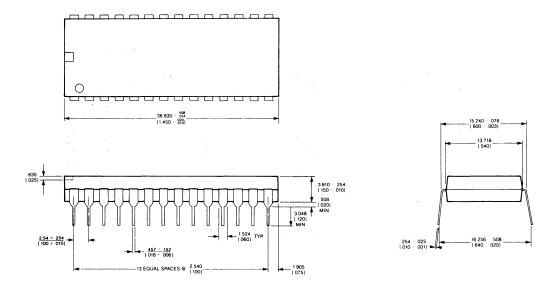

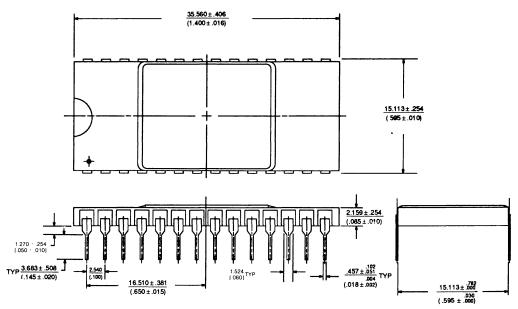

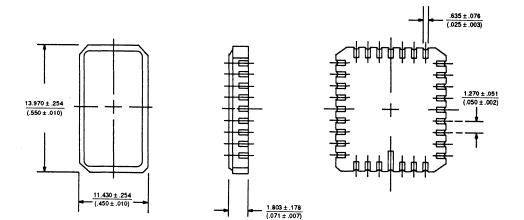

|   | D.2     | Packaging information                                           | D.5  |

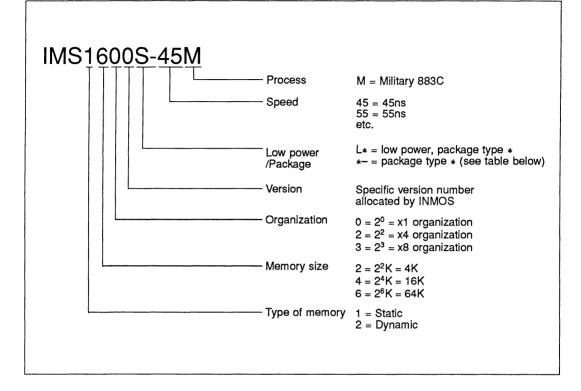

|   | D.3     | Product numbering, package designators and ordering information | D.17 |

'

#### Preface

#### 1 Preface and selection Guide

High performance memory devices form an integral part of the INMOS product range. The INMOS Memory Databook has been published to provide comprehensive information regarding the current range of INMOS memory devices.

The databook comprises a selection guide, INMOS overview and engineering data for the current range of commercial and military memory devices. Additional information is provided detailing military qualification, quality and reliability information and general information covering thermal performance, product numbering, packaging and ordering.

All INMOS military products are designed to satisfy the requirements of a military environment in terms of temperature and reliability under adverse conditions. The majority of the military versions of INMOS memory devices fully comply with MIL-STD-883C and the US Government Standard Military Drawing (SMD) Program.

In addition to memory devices, the INMOS product range also includes transputer products, digital signal processing devices and graphics devices. For further information concerning INMOS products, please contact your local INMOS sales outlet.

| CMOS Static RAMs |                        |                    |                         |            |                  |  |  |  |  |

|------------------|------------------------|--------------------|-------------------------|------------|------------------|--|--|--|--|

|                  | Co                     | ommercial          | Milit                   |            |                  |  |  |  |  |

| Organisation     | Device Speed(ns)       |                    | Device                  | Speed(ns)  | Packages *       |  |  |  |  |

| 4K x 1           | IMS1203                | 25, 35, 45         | IMS1203M                | 25, 35, 45 | P, S, A          |  |  |  |  |

| 1K x 4           | IMS1223                | 25, 35, 45         | IMS1223M                | 25, 35, 45 | P, S, A          |  |  |  |  |

| 16K x 1          | IMS1403                | 25, 35, 45, 55     | IMS1403M <sup>(1)</sup> | 35, 45, 55 | P, S, W, N       |  |  |  |  |

| 4K x 4           | IMS1423                | 25, 35, 45, 55     | IMS1423M                | 35, 45, 55 | P, S, E, W, Y, N |  |  |  |  |

| 64K x 1          | IMS1600 <sup>(1)</sup> | 25, 30, 35, 45, 55 | IMS1600M <sup>(1)</sup> | 45, 55, 70 | P, S, E, W, N    |  |  |  |  |

| 16K x 4          | IMS1620                | 25, 30, 35, 45, 55 | IMS1620M <sup>(1)</sup> | 45, 55, 70 | P, S, E, W, N    |  |  |  |  |

| 16K x 4          | IMS1624 <sup>(2)</sup> | 25, 30, 35, 45, 55 | IMS1624M <sup>(1)</sup> | 45, 55, 70 | P, S, E, W, N    |  |  |  |  |

| 8K x 8           |                        |                    | IMS1630M <sup>(1)</sup> | 45, 55, 70 | S, N             |  |  |  |  |

| NMOS RAMs (Military Only)                   |         |          |               |         |  |  |  |  |  |

|---------------------------------------------|---------|----------|---------------|---------|--|--|--|--|--|

| Organisation Type Device Speed(ns) Packages |         |          |               |         |  |  |  |  |  |

| 16K x 1                                     | Static  | IMS1400M | 45, 55, 70    | S, N, Y |  |  |  |  |  |

| 4K x 4                                      | Static  | IMS1420M | 55, 70        | S, N, Y |  |  |  |  |  |

| 64K x 1                                     | Dynamic | IMS2600M | 100, 120, 150 | S, N, K |  |  |  |  |  |

<sup>(1)</sup> Low-power/battery back-up versions available.

<sup>(2)</sup> With Output Enable function.

\* Solder dip lead finish available for all products, refer to Appendix D for details.

Inmos

Chapter 1

#### 1 INMOS

#### 1.1 Introduction

INMOS supplies high performance memory and microprocessor products to companies manufacturing systems in the United States, Europe, Japan and the Far East. The current INMOS product lines include very fast static random access memories (RAMs), microprocessors called transputers, colour graphics devices and digital signal processing devices.

The Company's fabrication facility is at Newport, South Wales with final test facilities located both at Newport and Colorado Springs, Colorado, USA. The corporate headquarters, product design team and worldwide sales and marketing management are all based at Bristol, UK.

#### 1.2 Static RAMs

INMOS designs and manufactures a broad range of fast static RAMs, ranging from 4K to 64K bits, in a number of configurations. Revenues from memory products in 1988/89 accounted for approximately one third of total revenues.

As microprocessors become faster, so the demand for fast memory products increases. Despite the semiconductor recession of 1985/86 the number of fast static RAMs shipped worldwide continued to grow throughout the period. The growth of the computer market, coupled with the increasing amount of memory in each computer, has led to the continued demand for static RAMs. From Dataquest's actual figures of \$330M in 1986 for the worldwide fast static RAM market ('fast' includes 70ns cycle time and above) it is anticipated that market growth will continue rising to \$839M by 1991.

#### 1.3 Manufacturing

All products are manufactured at the INMOS Newport, Duffryn facility which began operations in 1983. This is an 8000 square metre building with a 3000 square metre cleanroom operating to Class 10 environment in the work areas.

To produce high performance products, where each microchip may consist of up to 300,000 transistors, INMOS uses advanced manufacturing equipment. Wafer steppers, plasma etchers and ion implantors form the basis of fabrication.

#### 1.4 Assembly

Sub-contractors in Korea, Taiwan, Hong Kong and the UK are used to assemble devices.

#### 1.5 Test

The final testing of commercial products is carried out at the INMOS Newport, Coed Rhedyn facility. Military final testing takes place at Colorado Springs.

#### 1.6 Quality and Reliability

Stringent controls of quality and reliability provide the customer with early failure rates of less than 1000 ppm and long term reliability rates of better than 100 FITs (one FIT is one failure per 1000 million device hours). Requirements for military products are even more stringent.

#### 1.7 Military

Most INMOS static RAMs are available in military versions processed in full compliance with MIL-STD-883C. INMOS also supports the US Government Defense Electronics Supply Center (DESC) Standard Military Drawing (SMD) program and is an approved supplier of a range of the SMDs already established by DESC.

#### 1.8 Future developments

#### 1.8.1 Research and Development

INMOS has achieved technical success based on a position of leadership in products and process technology in conjunction with substantial research and development investment. R and D investment has averaged 18 percent of revenues since inception and it is anticipated that future investment levels will be maintained at this level.

#### 1.8.2 Process developments

One aspect of the work of the Technology Development Group at Newport is to scale the present technology to 1.0 micron for products to be manufactured in 1989/90. Additionally, work is in progress on the development of 0.8 micron CMOS technology.

A new process technology developed in Colorado Springs for an advanced range of 256K static RAMs and other products is currently being transferred to Newport. To achieve early expertise in this new process a new 64K static RAM, based on the new technology, is being brought into production.

#### 1.9 Package developments

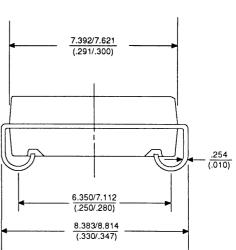

Where surface mount technology is desirable, the range of fast 64K static RAM will also be introduced in SOJ packaging.

Inmos

Chapter 2

# commercial RAMs

## IMS1203 CMOS High Performance 4K x 1 Static RAM

#### FEATURES

- INMOS' Very High Speed CMOS

- Advanced Process 1.6 Micron Design Rules

- · 4K x 1 Bit Organization

- · 25, 35, and 45 nsec Access Times

- 25, 35, and 45 nsec Chip Enable Access Times

- Fully TTL Compatible

- Separate Data Input and Output

- Three-state Output

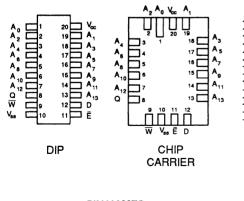

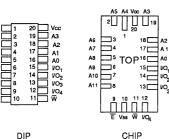

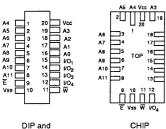

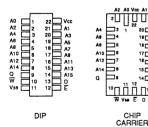

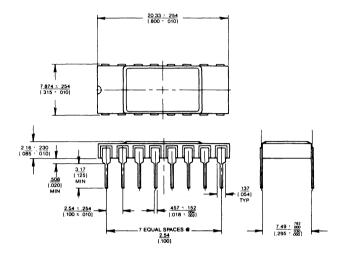

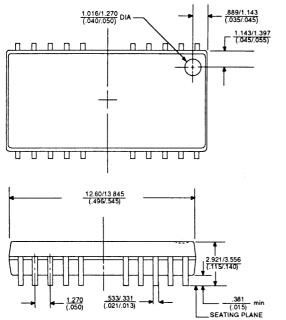

- 18 Pin, 300-mil DIP

- Single +5V ± 10% Operation

- Power Down Function

#### DESCRIPTION

The INMOS IMS1203 is a high performance 4Kx1 CMOS static RAM. The IMS1203 allows speed enhancements to existing 4Kx1 applications with the additional benefit of reduced power consumption.

The IMS1203 features fully static operation requiring no external clocks or timing strobes, and equal address access and cycle times. Additionally, the IMS1203 provides a Chip Enable (/E) function that can be used to place the device into a low-power standby mode.

The IMS1203M is a MIL-STD-883 version intended for military applications.

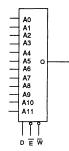

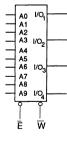

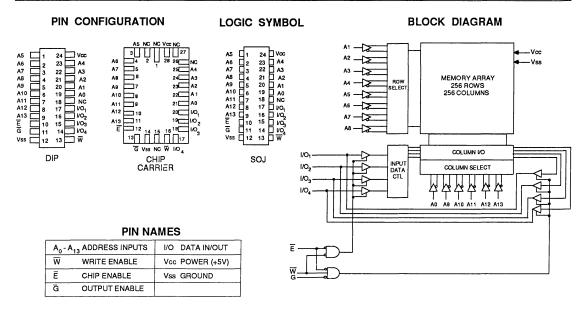

#### PIN CONFIGURATION

#### LOGIC SYMBOL

#### **PIN NAMES**

| A <sub>0</sub> - A | A11 ADDRESS INPUTS | Vcc POWER  |

|--------------------|--------------------|------------|

| w                  | WRITE ENABLE       | Vss GROUND |

| D                  | DATA INPUT         |            |

| Ē                  | CHIP ENABLE        |            |

| Q                  | DATA OUTPUT        |            |

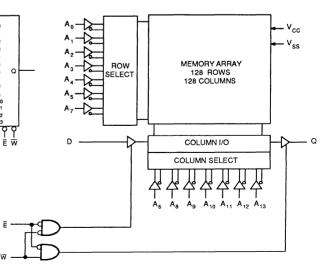

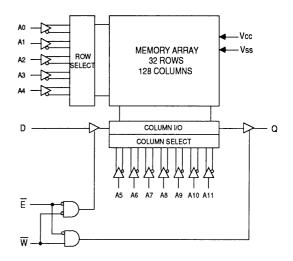

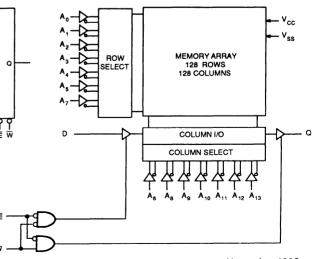

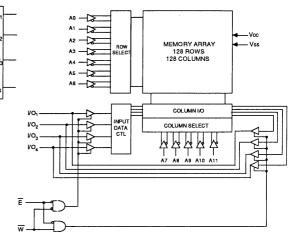

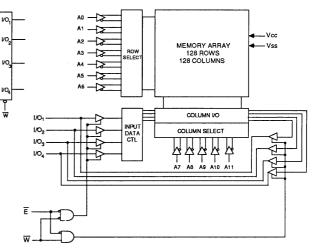

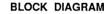

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin relative to $V_{ss}$         |

|-------------------------------------------------|

| Voltage on Q $-1.0$ to (V <sub>CC</sub> + 0.5V) |

| Temperature Under Bias                          |

| Storage Temperature                             |

| Power Dissipation 1W                            |

| DC Output Current                               |

| (One Second Duration)                           |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **DC OPERATING CONDITIONS**

| SYMBOL          | PARAMETER                     | MIN   | ТҮР | МАХ     | UNITS | NOTES                      |

|-----------------|-------------------------------|-------|-----|---------|-------|----------------------------|

| V <sub>CC</sub> | Supply Voltage                | 4.5   | 5.0 | 5.5     | V     |                            |

| V <sub>SS</sub> | Supply Voltage                | 0     | 0   | 0       | V     |                            |

| V <sub>IH</sub> | Input Logic "1" Voltage       | 2.0   |     | Vcc +.5 | V     | All inputs                 |

| V <sub>IL</sub> | Input Logic "0" Voltage       | -1.0* |     | 0.8     | V     | All inputs                 |

| T <sub>A</sub>  | Ambient Operating Temperature | 0     |     | 70      | °C    | 400 linear ft/min air flow |

\*  $V_{IL}$  Min = -3.0V for pulse width <20ns, note b.

#### DC ELECTRICAL CHARACTERISTICS (0°C $\leq T_A \leq 70^{\circ}C$ ) (V\_{CC} = 5.0V $\pm$ 10%) $^a$

| SYMBOL           | PARAMETER                                                                    | MIN | МАХ | UNITS | NOTES                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------|-----|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>CC1</sub> | Average $V_{CC}$ Power Supply Current                                        |     | 80  | mA    | $t_{AVAV} = t_{AVAV} (min)$                                                                                                                                                  |

| I <sub>CC2</sub> | V <sub>CC</sub> Power Supply Current (Standby,<br>Stable TTL Input Levels)   |     | 15  | mA    | $\begin{array}{l} \overline{E} \geq V_{\text{IH}} \\ \text{All other inputs } V_{\text{IN}} \\ \leq V_{\text{IL}} \text{ or } \geq V_{\text{IH}} \end{array}$                |

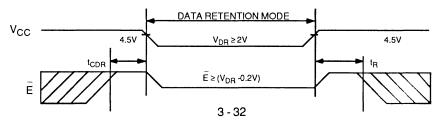

| I <sub>CC3</sub> | V <sub>CC</sub> Power Supply Current (Standby,<br>Stable CMOS Input Levels)  |     | 6   | mA    | $\label{eq:constraint} \begin{split} \overline{E} &\geq (V_{CC} - 0.2V) \\ \text{All other inputs at } V_{IN} \\ &\leq 0.2V \text{ or } \geq \\ (V_{CC} - 0.2V) \end{split}$ |

| I <sub>CC4</sub> | V <sub>CC</sub> Power Supply Current (Standby,<br>Cycling CMOS Input Levels) |     | 13  | mA    | $\begin{split} \overline{E} &\geq (V_{CC} - 0.2V) \\ \text{Inputs cycling at } V_{\text{IN}} \\ &\leq 0.2V \text{ or } \geq \\ (V_{CC} - 0.2V) \end{split}$                  |

| I <sub>ILK</sub> | Input Leakage Current (Any Input)                                            |     | ±1  | μA    | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                                              |

| Ι <sub>οικ</sub> | Off State Output Leakage Current                                             |     | ±5  | μA    | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                                              |

| V <sub>он</sub>  | Output Logic "1" Voltage                                                     | 2.4 |     | V     | $I_{OUT} = -4mA$                                                                                                                                                             |

| V <sub>OL</sub>  | Output Logic "0" Voltage                                                     |     | 0.4 | V     | $I_{OUT} = 12mA$                                                                                                                                                             |

Note a: I<sub>CC</sub> is dependent on output loading and cycle rate, the specified values are obtained with the output unloaded.

#### **AC TEST CONDITIONS**

| Input Pulse Levels | 1 |

|--------------------|---|

|--------------------|---|

#### $\textbf{CAPACITANCE} \ (T_A = 25^{\circ}C, \, f = 1.0 \; MHz)^{\, b}$

| SYMBOL | PARAMETER          | МАХ | UNITS | CONDITIONS           |

|--------|--------------------|-----|-------|----------------------|

| CIN    | Input Capacitance  | 4   | ρF    | $\Delta V = 0$ to 3V |

| COUT   | Output Capacitance | 4   | рF    | $\Delta V = 0$ to 3V |

Note b: This parameter is sampled and not 100% tested.

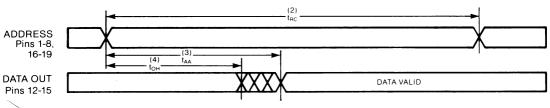

### RECOMMENDED AC OPERATING CONDITIONS (0°C $\leq$ T\_A $\leq$ 70°C) (V\_{cc} = 5.0V $\pm$ 10%) READ CYCLE<sup>g</sup>

|     | SYMBOL              |                  |                                  | 120 | 3-25 | 120 | 3-35 | 1203-45 |    | UNITO | NOTEO |

|-----|---------------------|------------------|----------------------------------|-----|------|-----|------|---------|----|-------|-------|

| NO. | Standard            | Alternate        | ate PARAMETER                    |     | MAX  |     |      |         |    | UNITS | NOTES |

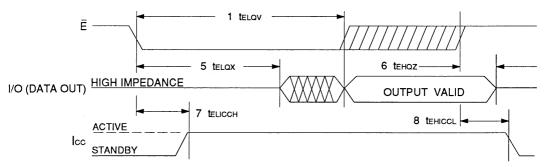

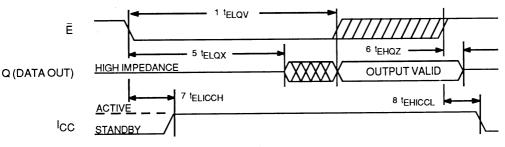

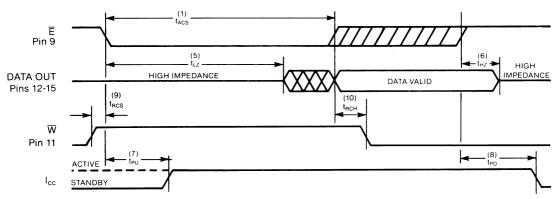

| 1   | t <sub>ELQV</sub>   | t <sub>ACS</sub> | Chip Enable Access Time          |     | 25   |     | 35   |         | 45 | ns    |       |

| 2   | t <sub>avav</sub>   | t <sub>RC</sub>  | Read Cycle Time                  | 25  |      | 35  |      | 45      |    | ns    | С     |

| 3   | t <sub>avav</sub>   | t <sub>AA</sub>  | Address Access Time              |     | 25   |     | 35   |         | 45 | ns    | d     |

| 4   | t <sub>AXQX</sub>   | t <sub>он</sub>  | Output Hold After Address Change | 3   |      | 3   |      | 3       |    | ns    |       |

| 5   | t <sub>ELQX</sub>   | t <sub>LZ</sub>  | Chip Enable to Output Active     | 5   |      | 5   |      | 5       |    | ns    | j     |

| 6   | t <sub>ehoz</sub>   | t <sub>HZ</sub>  | Chip Disable to Output Inactive  | 0   | 20   | 0   | 30   | 0       | 30 | ns    | f, j  |

| 7   | t <sub>ELICCH</sub> | t <sub>PU</sub>  | Chip Enable to Power Up          | 0   |      | 0   |      | 0       |    | ns    | j     |

| 8   | t <sub>EHICCL</sub> | t <sub>PD</sub>  | Chip Enable to Power Down        |     | 20   |     | 20   |         | 20 | ns    | j     |

|     |                     | t <sub>T</sub>   | Input Rise and Fall Times        |     | 50   |     | 50   |         | 50 | ns    | e, j  |

Note c: For READ CYCLE 1 & 2, W is high for entire cycle.

Note d: Device is continuously selected; E low.

Note e: Measured between VIL max and VIH min.

Note f: Measured ±200mV from steady state output voltage. Load capacitance is 5pF.

Note g:  $\vec{E}$  and  $\vec{W}$  must transition between V<sub>IH</sub> to V<sub>IL</sub> or V<sub>IL</sub> to V<sub>IH</sub> in a monotonic fashion.

Note j: Parameter guaranteed but not tested.

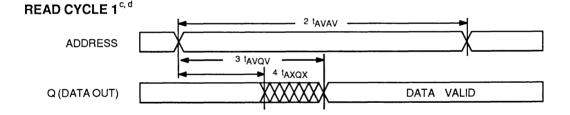

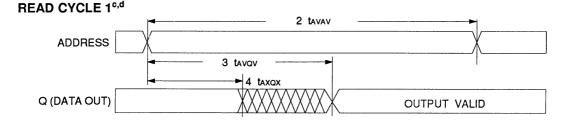

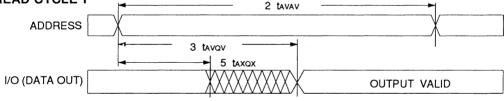

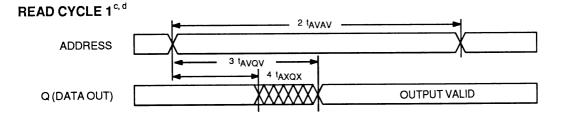

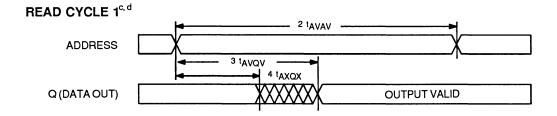

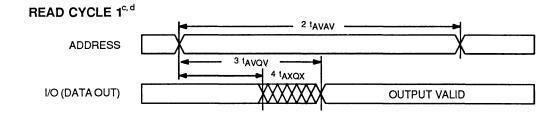

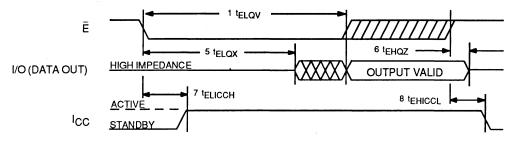

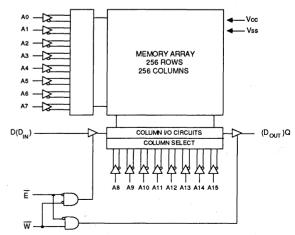

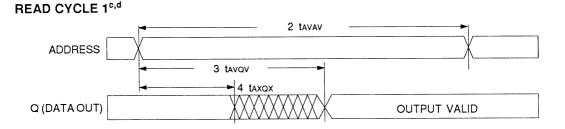

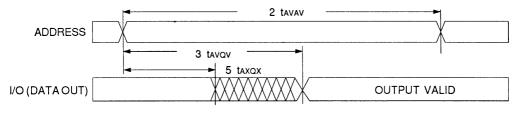

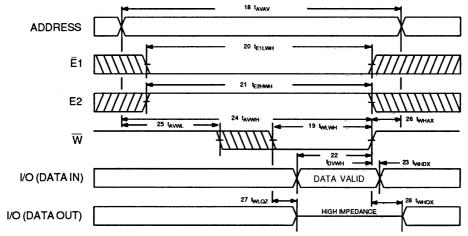

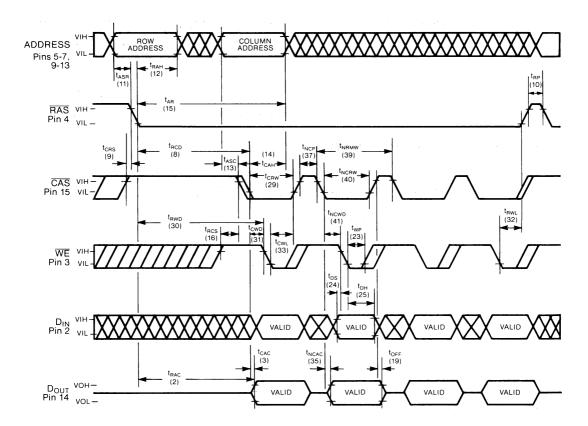

#### READ CYCLE 1<sup>c, d</sup>

#### **DEVICE OPERATION**

The IMS1203 has two control inputs, Chip Enable ( $\overline{E}$ ) and Write Enable ( $\overline{W}$ ), twelve address inputs (A<sub>0</sub>-A<sub>11</sub>), a data in (D<sub>IN</sub>) and a data out (D<sub>OUT</sub>). The  $\overline{E}$  input controls device selection as well as active and standby modes. With  $\overline{E}$  low, the device is selected and the twelve address inputs are decoded to select one memory cell out of 4096. Read and Write operations on the memory cell are controlled by  $\overline{W}$  input. With  $\overline{E}$  high, the device is deselected, the output is disabled, and the power consumption is reduced to less than one-third of the active mode power with TTL levels and even lower with CMOS levels.

#### **READ CYCLE**

A read cycle is defined as  $\overline{W} \ge V_{IH}$  min with  $\overline{E} \le V_{IL}$  max. Read access time is measured from either  $\overline{E}$  going low or from valid address.

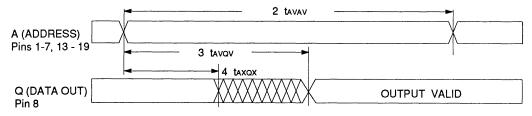

The READ CYCLE 1 waveform shows a read access that is initiated by a change in the address inputs while  $\overline{E}$  is low. The output remains active throughout READ CYCLE 1 and is valid at the specified address access time. The address inputs may change at access time and as long as  $\overline{E}$  remains low, the cycle time is equal to the address access time.

| RECOMMENDED AC OPERATING CONDITIONS (0°C $\leq$ T <sub>A</sub> $\leq$ 70°C) (V <sub>cc</sub> = 5.0V $\pm$ 10%) |  |

|----------------------------------------------------------------------------------------------------------------|--|

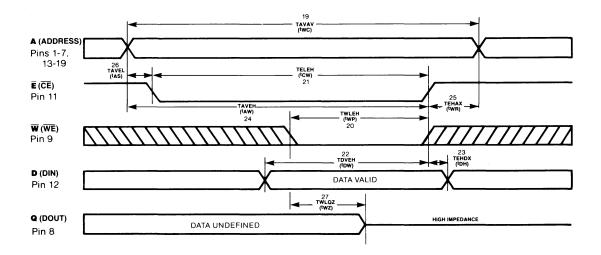

| WRITE CYCLE 1: W CONTROLLED <sup>g, h</sup>                                                                    |  |

| NO. | SYM               | BOL             | PARAMETER                            |     | 3-25 |     | 3-35 | 1203-45 |     | UNITS  | NOTES |

|-----|-------------------|-----------------|--------------------------------------|-----|------|-----|------|---------|-----|--------|-------|

| NO. | Standard          | Alternate       | FANAMEIEN                            | MIN | MAX  | MIN | MAX  | MIN     | MAX | 014113 | NOTES |

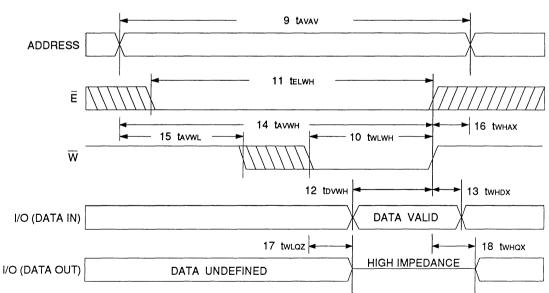

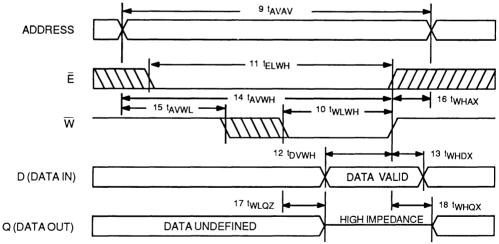

| 9   | t <sub>avav</sub> | t <sub>wc</sub> | Write Cycle Time                     | 25  |      | 35  |      | 45      |     | ns     |       |

| 10  | t <sub>wLWH</sub> | t <sub>wP</sub> | Write Pulse Width                    | 15  |      | 20  |      | 25      |     | ns     |       |

| 11  | t <sub>elwh</sub> | t <sub>cw</sub> | Chip Enable to End of Write          | 20  |      | 30  |      | 40      |     | ns     |       |

| 12  | t <sub>DVWH</sub> | t <sub>DW</sub> | Data Set-up to End of Write          | 15  |      | 20  |      | 25      |     | ns     |       |

| 13  | t <sub>wHDX</sub> | t <sub>DH</sub> | Data Hold After End of Write         | 0   |      | 0   |      | 0       |     | ns     |       |

| 14  | t <sub>avwh</sub> | t <sub>AW</sub> | Address Set-up to End of Write       | 20  |      | 30  |      | 40      |     | ns     |       |

| 15  | t <sub>avwl</sub> | t <sub>AS</sub> | Address Set-up to Beginning of Write | 0   |      | 0   |      | 0       |     | ns     |       |

| 16  | t <sub>whax</sub> | t <sub>wR</sub> | Address Hold After End of Write      | 0   |      | 0   |      | 0       |     | ns     |       |

| 17  | t <sub>wLQZ</sub> | t <sub>wz</sub> | Write Enable to Output Disable       | 0   | 15   | 0   | 20   | 0       | 20  | ns     | f, j  |

| 18  | t <sub>whax</sub> | t <sub>ow</sub> | Output Active After End of Write     | 0   |      | 0   |      | 0       |     | ns     | i     |

Note f: Measured ±200mV from steady state output voltage. Load capacitance is 5pF.

Note g:  $\overline{E}$  and  $\overline{W}$  must transition between V<sub>IH</sub> to V<sub>IL</sub> or V<sub>IL</sub> to V<sub>IH</sub> in a monotonic fashion.

Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\geq V_{IH}$  during address transitions.

Note i: If  $\overline{W}$  is low when  $\overline{E}$  goes low, the output remains in the high impedance state.

Note j: Parameter guaranteed but not tested.

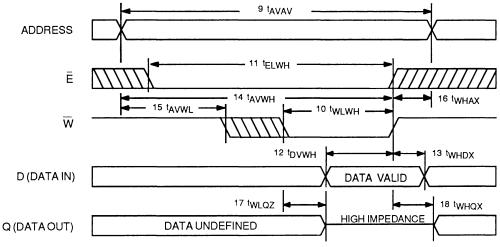

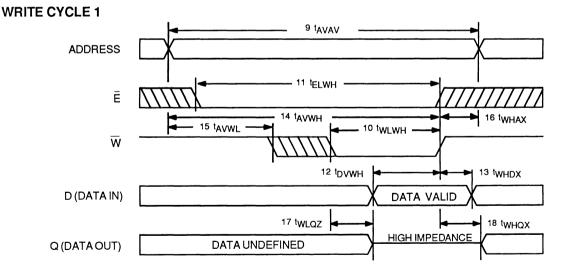

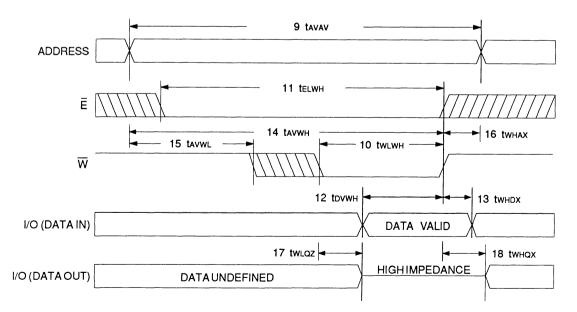

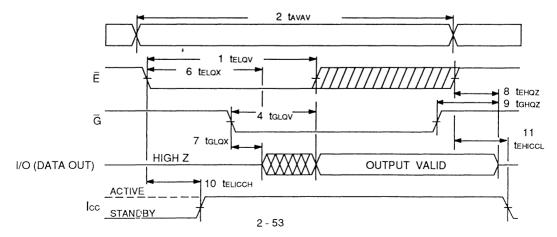

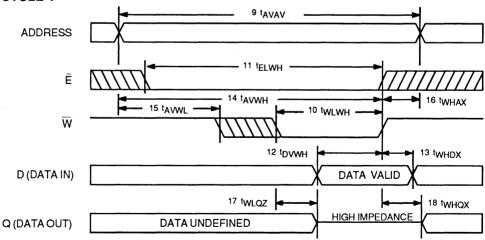

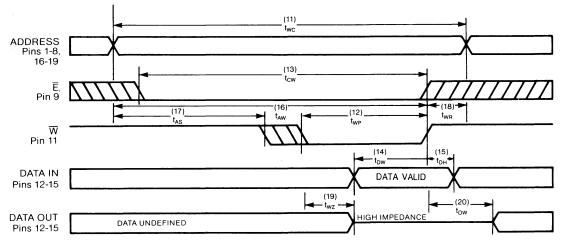

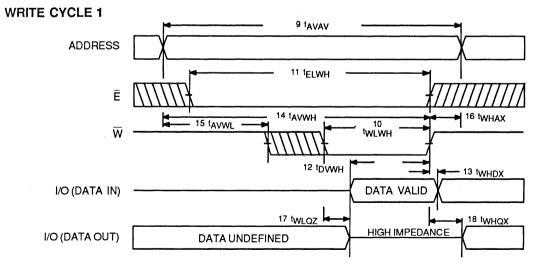

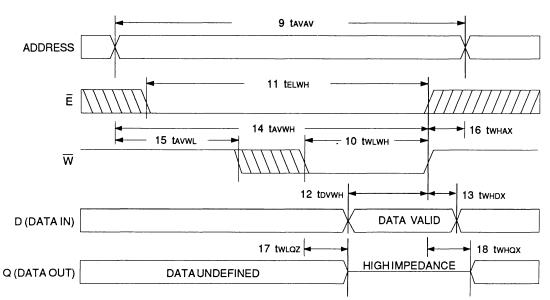

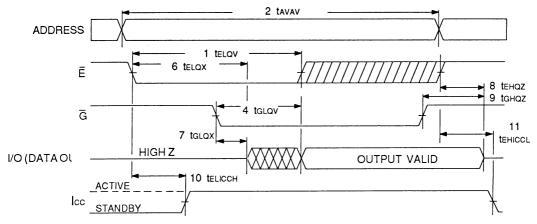

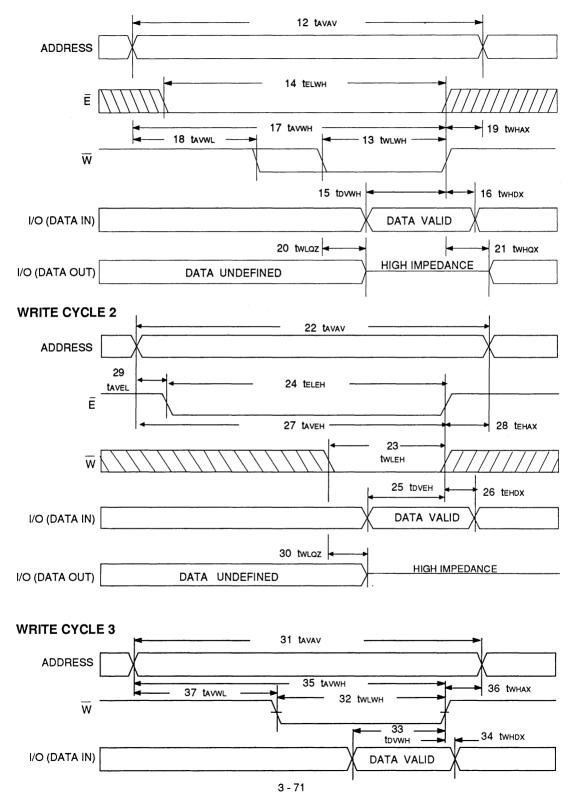

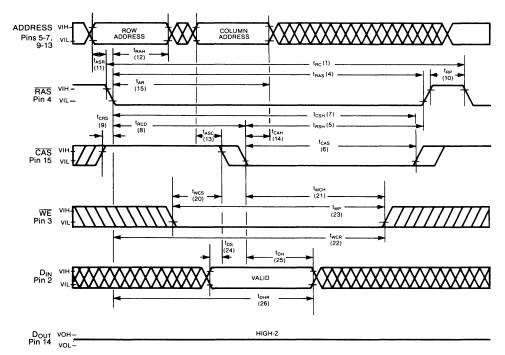

#### WRITE CYCLE 1

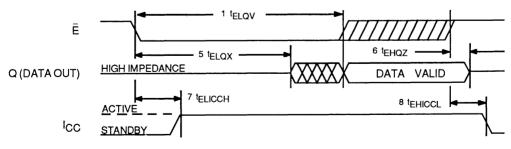

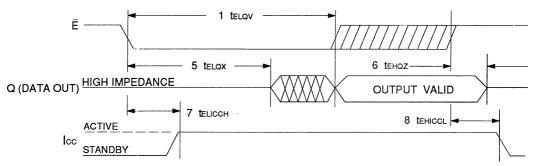

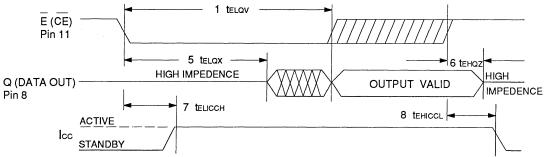

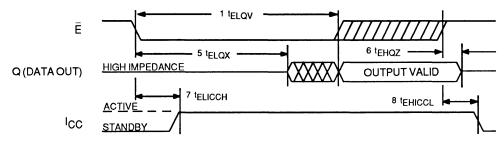

The READ CYCLE 2 waveform shows a read access that is initiated by  $\overline{E}$  going low. As long as address is stable when  $\overline{E}$  goes low, valid data is at the output at the specified Chip Enable Access time. If address is not valid when  $\overline{E}$  goes low, the timing is as specified in READ CYCLE 1. Chip Enable access time is not affected by the duration of the deselect interval.

#### WRITE CYCLE

The write cycle of the IMS1203 is initiated by the latter of  $\overline{E}$  or  $\overline{W}$  to fall. In the case of  $\overline{W}$  falling last, the output buffer will be turned on t<sub>ELQX</sub> after the falling edge of

$\overline{E}$  (just as in a read cycle). The output buffer is then turned off within  $t_{WLQZ}$  of the falling edge of  $\overline{W}$ . During this interval, it is possible to have bus contention between devices with D and Q connected together in a common I/O configuration. Contention can be avoided in a carefully designed system. During a write cycle, data on the input is written into the selected cells and the output is floating.

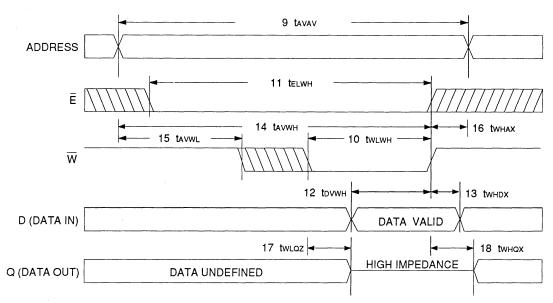

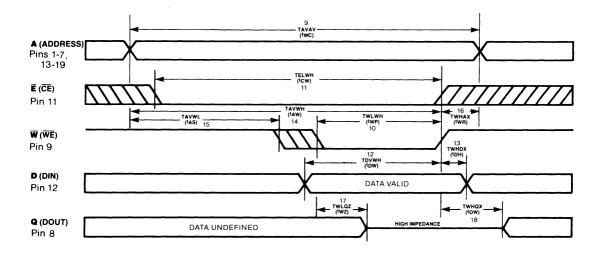

WRITE CYCLE 1 waveform shows a write cycle terminated by  $\overline{W}$  going high. Data set-up and hold times are referenced to the rising edge of  $\overline{W}$ . When  $\overline{W}$  goes high at the end of the cycle with  $\overline{E}$  active, the output of

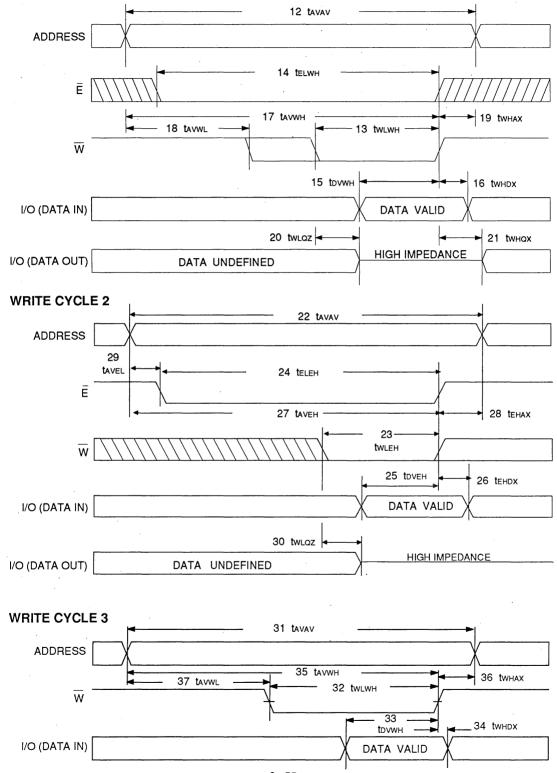

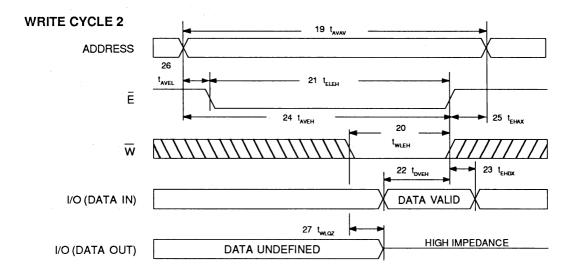

#### **RECOMMENDED AC OPERATING CONDITIONS** (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C) (V<sub>cc</sub> = 5.0V ± 10%) **WRITE CYCLE 2:** E CONTROLLED<sup>g, h</sup>

| NO. |                   | BOL             | PARAMETER                            |     | 3-25 |     | 03-35 1203-45 |         |    | UNITS | NOTES |

|-----|-------------------|-----------------|--------------------------------------|-----|------|-----|---------------|---------|----|-------|-------|

|     | Standard          | Alternate       |                                      | MIN | MAX  | MIN | MAX           | MIN MAX |    |       |       |

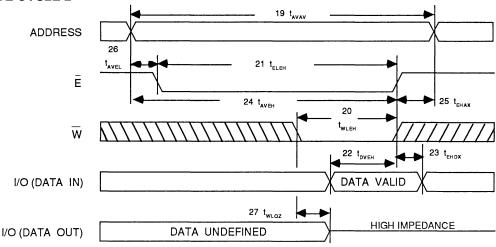

| 19  | t <sub>avav</sub> | t <sub>wc</sub> | Write Cycle Time                     | 25  |      | 35  |               | 45      |    | ns    |       |

| 20  | t <sub>wLEH</sub> | t <sub>wP</sub> | Write Pulse Width                    | 15  |      | 20  |               | 25      |    | ns    |       |

| 21  | t <sub>elen</sub> | t <sub>CW</sub> | Chip Enable to End of Write          | 20  |      | 30  |               | 40      |    | ns    |       |

| 22  | t <sub>DVEH</sub> | t <sub>DW</sub> | Data Set-up to End of Write          | 15  |      | 20  |               | 25      |    | ns    |       |

| 23  | t <sub>EHDX</sub> | t <sub>DH</sub> | Data Hold After End of Write         | 0   |      | 0   |               | 0       |    | ns    |       |

| 24  | t <sub>AVEH</sub> | t <sub>AW</sub> | Address Set-up to End of Write       | 20  |      | 30  |               | 40      |    | ns    | _     |

| 25  | t <sub>ehax</sub> | t <sub>wR</sub> | Address Hold After End of Write      | 0   |      | 0   |               | 0       |    | ns    |       |

| 26  | t <sub>AVEL</sub> | t <sub>AS</sub> | Address Set-up to Beginning of Write | 0   |      | 0   |               | 0       |    | ns    |       |

| 27  | t <sub>wLQZ</sub> | t <sub>wz</sub> | Write Enable to Output Disable       | 0   | 15   | 0   | 20            | 0       | 20 | ns    | f, j  |

Note f: Measured ±200mV from steady state output voltage. Load capacitance is 5pF.

Note g:  $\tilde{E}$  and  $\overline{W}$  must transition between V<sub>IH</sub> to V<sub>IL</sub> or V<sub>IL</sub> to V<sub>IH</sub> in a monotonic fashion.

Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\geq V_{IH}$  during address transitions.

Note i: If  $\overline{W}$  is low when  $\overline{E}$  goes low, the output remains in the high impedance state.

Note j: Parameter guaranteed but not tested.

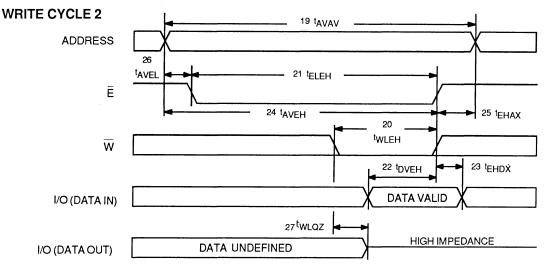

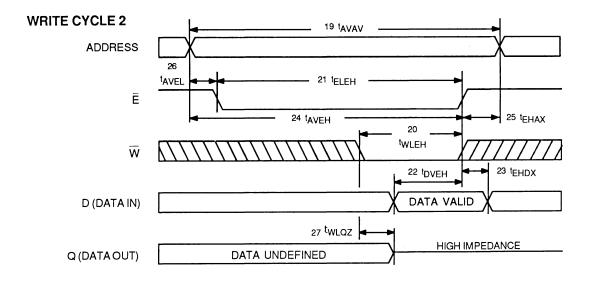

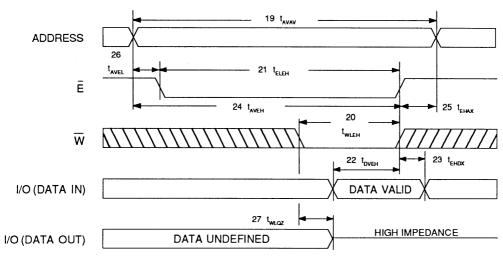

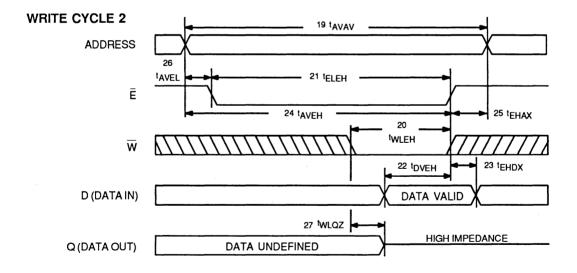

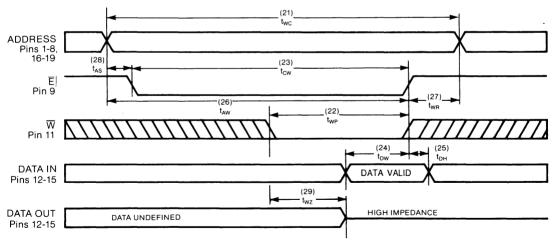

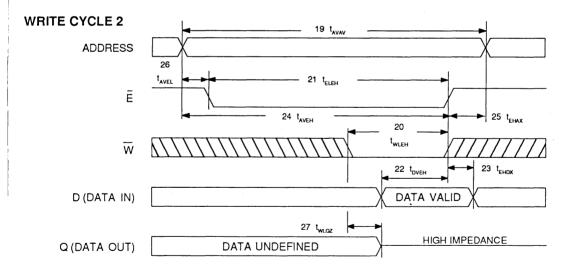

#### WRITE CYCLE 2

the memory becomes active. The data from the memory will be the same as the input data unless the input data or address changes.

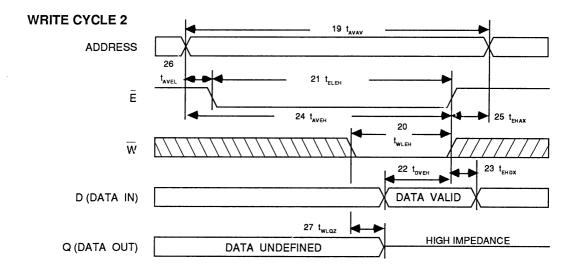

WRITE CYCLE 2 waveform shows a write cycle terminated by  $\overline{E}$  going high. Data set-up and hold times are referenced to the rising edge of  $\overline{E}$ . With  $\overline{E}$  high, the outputs remain in the high impedance state.

#### APPLICATION

It is imperative when designing with any very high speed memory, such as the IMS1203, that the fundamental rules in regard to memory board layout be followed to ensure proper system operation.

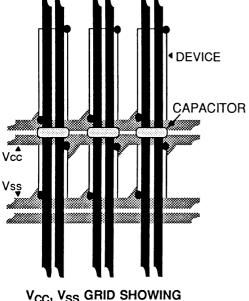

#### POWER DISTRIBUTION

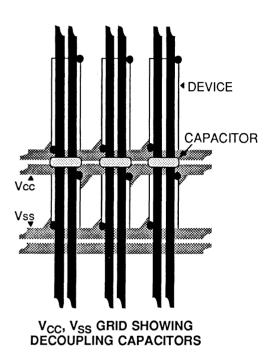

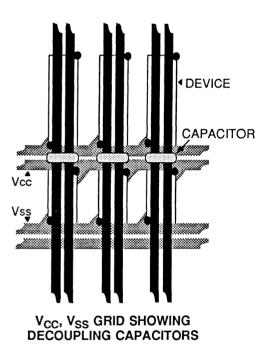

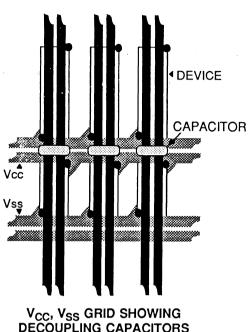

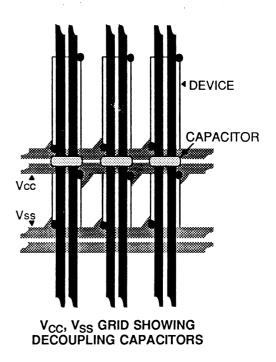

The recommended power distribution scheme combines proper power trace layout and placement of decoupling capacitors to maintain the operating margins of the IMS1203. The impedance in the decoupling path from the power pin (18) through the decoupling capacitor to the ground pin (9) should be kept to a minimum. The impedance of this path is determined by the series impedance of the power line inductance and the inductance and reactance of the decoupling capacitor.

Since the current transients associated with the operation of the high speed IMS1203 have very high frequency

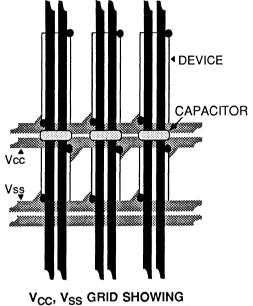

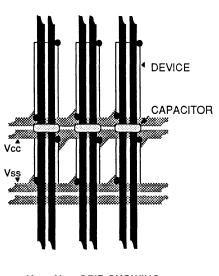

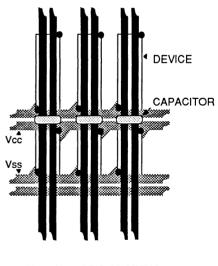

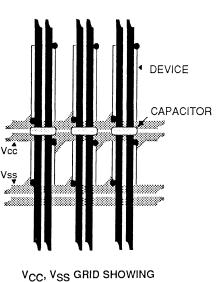

components, the line inductance is the dominating factor. To reduce the line inductance, the power trace and around trace should be gridded or provided by separate power planes. The decoupling capacitor supplies energy for high frequency current transients and should be located as close to the devices with as short lead length as possible. The high frequency decoupling capacitor should have a value of 0.1 microfarad, and be placed between each row of devices in the array (see drawing). A larger tantalum capacitor, with a sufficient value to eliminate low frequency ripple, should be placed near the memory board edge connection where the power traces meet the backplane power distribution system. These larger capacitors provide bulk energy storage to prevent voltage drop due to the main supply being located off the memory board and at the end of a long inductive path.

The ground grid of the memory array should extend to the TTL driver periphery circuit. This will provide a solid ground reference for the TTL drivers and prevent loss of operating margin of the drivers due to differential ground noise.

#### TERMINATION

Trace lines on a memory board in the array look to TTL driver signals like low impedance, unterminated transmission lines. In order to reduce or eliminate the reflections of the TTL signals propagating down the lines, especially low going TTL signals, line termination is recommended. The termination may be either series or parallel.

The recommended technique is to use series termination. The series termination technique has the advantage of drawing no DC current and using a minimum number of components. This is accomplished by placing a series resistor in the signal line at the output of the TTL driver to dampen the reflection on the line. The resistor should be placed as close to the driver package as is practical. The line should be kept short by placing the drivertermination combination close to the memory array.

Some experimentation will have to be done to find the proper value to use for the series termination to minimize reflections, but generally a series resistor in the 10 to 33 ohm range will be required. Because each design will result in a different signal impedance, a resistor of predetermined value may not properly match the signal path impedance. The proper value of resistance should therefore be selected empirically.

DECOUPLING CAPACITORS

| DEVICE  | SPEED | PACKAGE     | PART NUMBER |

|---------|-------|-------------|-------------|

|         | 25ns  | PLASTIC DIP | IMS1203P-25 |

|         | 25ns  | CERAMIC DIP | IMS1203S-25 |

| IMS1203 | 35ns  | PLASTIC DIP | IMS1203P-35 |

|         | 35ns  | CERAMIC DIP | IMS1203S-35 |

|         | 45ns  | PLASTIC DIP | IMS1203P-45 |

|         | 45ns  | CERAMIC DIP | IMS1203S-45 |

## IMS1223 CMOS High Performance 1K x 4 Static RAM

#### FEATURES

- INMOS' Very High Speed CMOS

- Advanced Process 1.6 Micron Design Rules

- 1K x 4 Bit Organization

- 25, 35, and 45 nsec Access Times

- · 25, 35, and 45nsec Chip Enable Access Times

- Fully TTL Compatible

- · Common Data Input and Output

- Three-state Output

- 18 Pin, 300-mil DIP

- Single +5V ± 10% Operation

- Power Down Function

#### DESCRIPTION

The INMOS IMS1223 is a high performance 1Kx4 CMOS static RAM. The IMS1223 allows speed enhancements to existing 1Kx4 applications with the additional benefit of reduced power consumption.

The IMS1223 features fully static operation requiring no external clocks or timing strobes, and equal address access and cycle times. Additionally, the IMS1223 provides a Chip Enable (/E) function that can be used to place the device into a low-power standby mode.

The IMS1223M is a MIL-STD-883 version intended for military applications.

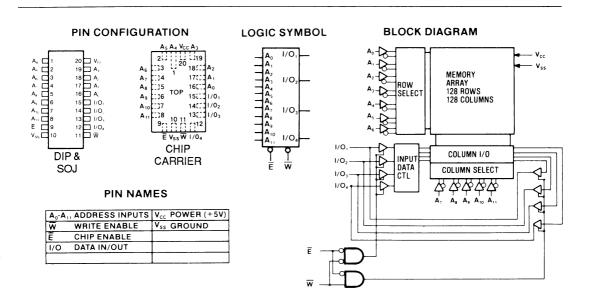

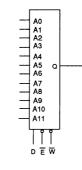

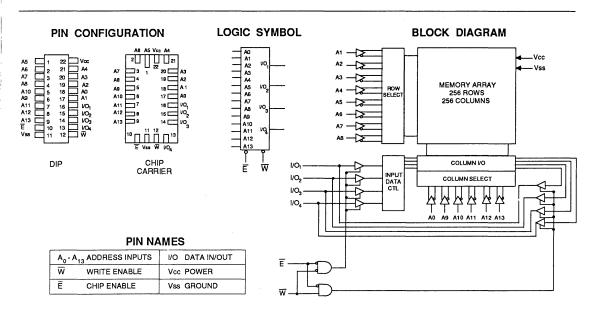

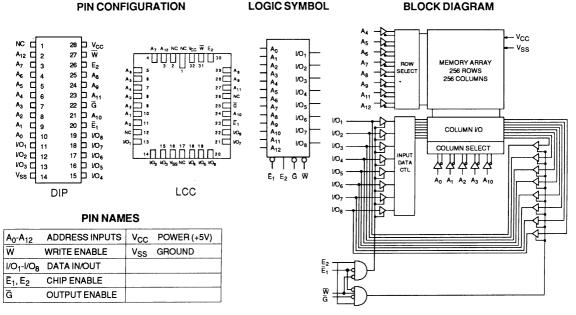

#### PIN CONFIGURATION

#### LOGIC SYMBOL

#### PIN NAMES

| A <sub>0</sub> - A <sub>9</sub> | ADDRESS INPUTS | Vcc POWER  |

|---------------------------------|----------------|------------|

| w                               | WRITE ENABLE   | Vss GROUND |

| Ē                               | CHIP ENABLE    |            |

| 1/0                             | DATA IN/OUT    |            |

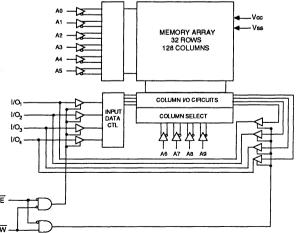

#### **BLOCK DIAGRAM**

#### IMS1223 ABSOLUTE MAXIMUM RATINGS\*

| Voltage on any pin relative to V <sub>ss</sub> | 2.0 to 7.0V    |

|------------------------------------------------|----------------|

| Voltage on Q $\ldots \ldots -1$ .              |                |

| Temperature Under Bias.                        | -55°C to 125°C |

| Storage Temperature                            |                |

| Power Dissipation                              | 1W             |

| DC Output Current                              |                |

| (One Second Duration)                          |                |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **DC OPERATING CONDITIONS**

| SYMBOL          | PARAMETER                     | MIN   | ТҮР | МАХ          | UNITS | NOTES                      |

|-----------------|-------------------------------|-------|-----|--------------|-------|----------------------------|

| V <sub>cc</sub> | Supply Voltage                | 4.5   | 5.0 | 5.5          | V     |                            |

| V <sub>SS</sub> | Supply Voltage                | 0     | 0   | 0            | V     |                            |

| V <sub>IH</sub> | Input Logic "1" Voltage       | 2.0   |     | $V_{CC}$ +.5 | V     | All inputs                 |

| V <sub>IL</sub> | Input Logic "0" Voltage       | -1.0* |     | 0.8          | V     | All inputs                 |

| T <sub>A</sub>  | Ambient Operating Temperature | 0     |     | 70           | °C    | 400 linear ft/min air flow |

\* VIL Min = -3.0V for pulse width <20ns, note b.

#### DC ELECTRICAL CHARACTERISTICS (0°C $\leq$ $T_{A}$ $\leq$ 70°C) (V\_{CC} = 5.0V $\pm$ 10%) $^{a}$

| SYMBOL           | PARAMETER                                                                    | MIN | MAX | UNITS | NOTES                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------|-----|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>CC1</sub> | Average $V_{CC}$ Power Supply Current                                        |     | 100 | mA    | $t_{AVAV} = t_{AVAV} (min)$                                                                                                                                                  |

| I <sub>CC2</sub> | V <sub>CC</sub> Power Supply Current (Standby, Stable TTL Input Levels)      |     | 15  | mA    | $\begin{array}{l} \overline{E} \geq V_{\text{IH}} \\ \text{All other inputs } V_{\text{IN}} \\ \leq V_{\text{IL}} \text{ or } \geq V_{\text{IH}} \end{array}$                |

| I <sub>CC3</sub> | V <sub>CC</sub> Power Supply Current (Standby,<br>Stable CMOS Input Levels)  |     | 6   | mA    | $\label{eq:constraint} \begin{split} \overline{E} &\geq (V_{CC} - 0.2V) \\ \text{All other inputs at } V_{IN} \\ &\leq 0.2V \text{ or } \geq \\ (V_{CC} - 0.2V) \end{split}$ |

| I <sub>CC4</sub> | V <sub>CC</sub> Power Supply Current (Standby,<br>Cycling CMOS Input Levels) |     | 8   | mA    | $\label{eq:constraint} \begin{split} \overline{E} &\geq (V_{CC} - 0.2V) \\ \text{Inputs cycling at } V_{IN} \\ &\leq 0.2V \text{ or } \geq \\ (V_{CC} - 0.2V) \end{split}$   |

| I <sub>ILK</sub> | Input Leakage Current (Any Input)                                            |     | ±1  | μA    | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                                              |

| I <sub>olk</sub> | Off State Output Leakage Current                                             |     | ±5  | μA    | $V_{cc} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                                              |

| V <sub>он</sub>  | Output Logic "1" Voltage                                                     | 2.4 |     | V     | $I_{OUT} = -4mA$                                                                                                                                                             |

| V <sub>OL</sub>  | Output Logic "0" Voltage                                                     |     | 0.4 | V     | I <sub>OUT</sub> = 8mA                                                                                                                                                       |

Note a: I<sub>CC</sub> is dependent on output loading and cycle rate, the specified values are obtained with the output unloaded.

#### AC TEST CONDITIONS

| Input and Output Timing Reference Levels |

|------------------------------------------|

|------------------------------------------|

#### **CAPACITANCE** $(T_A = 25^{\circ}C, f = 1.0 \text{ MHz})^{\circ}$

| SYMBOL           | PARAMETER          | MAX | UNITS | CONDITIONS           |

|------------------|--------------------|-----|-------|----------------------|

| C <sub>IN</sub>  | Input Capacitance  | 4   | рF    | $\Delta V = 0$ to 3V |

| C <sub>OUT</sub> | Output Capacitance | 4   | рF    | $\Delta V = 0$ to 3V |

Note b: This parameter is sampled and not 100% tested.

### RECOMMENDED AC OPERATING CONDITIONS (0°C $\leq$ T\_A $\leq$ 70°C) (V\_{cc} = 5.0V $\pm$ 10%) READ CYCLEg

|     | SYM                 | BOL              |                                  | 122 | 3-25 | 122 | 3-35 | 1223-45 |     | UNITS | NOTES |

|-----|---------------------|------------------|----------------------------------|-----|------|-----|------|---------|-----|-------|-------|

| NO. | Standard            | Alternate        | PARAMETER                        | MIN | MAX  | MIN | MAX  | MIN     | MAX | UNITS | NOTES |

| 1   | t <sub>ELQV</sub>   | t <sub>ACS</sub> | Chip Enable Access Time          |     | 25   |     | 35   |         | 45  | ns    |       |

| 2   | t <sub>avav</sub>   | t <sub>RC</sub>  | Read Cycle Time                  | 25  |      | 35  |      | 45      |     | ns    | С     |

| 3   | t <sub>avav</sub>   | t <sub>AA</sub>  | Address Access Time              |     | 25   |     | 35   |         | 45  | ns    | d     |

| 4   | t <sub>axox</sub>   | t <sub>OH</sub>  | Output Hold After Address Change | 0   |      | 0   |      | 0       |     | ns    |       |

| 5   | t <sub>ELOX</sub>   | t <sub>LZ</sub>  | Chip Enable to Output Active     | 5   |      | 5   |      | 5       |     | ns    | j     |

| 6   | t <sub>EHQZ</sub>   | t <sub>HZ</sub>  | Chip Disable to Output Inactive  |     | 15   |     | 20   |         | 20  | ns    | f, j  |

| 7   | t <sub>ELICCH</sub> | t <sub>PU</sub>  | Chip Enable to Power Up          | 0   |      | 0   |      | 0       |     | ns    | j     |

| 8   | t <sub>EHICCL</sub> | t <sub>PD</sub>  | Chip Enable to Power Down        |     | 20   |     | 20   |         | 20  | ns    | j     |

|     |                     | t <sub>T</sub>   | Input Rise and Fall Times        |     | 50   |     | 50   |         | 50  | ns    | e, j  |

Note c: For READ CYCLE 1 & 2,  $\overline{W}$  is high for entire cycle.

Note d: Device is continuously selected; E low.

Note e: Measured between  $V_{IL}$  max and  $V_{IH}$  min.

Note f: Measured ±200mV from steady state output voltage. Load capacitance is 5pF.

Note g:  $\vec{E}$  and  $\vec{W}$  must transition between  $V_{IH}$  to  $V_{IL}$  or  $V_{IL}$  to  $V_{IH}$  in a monotonic fashion.

Note j: Parameter guaranteed but not tested.

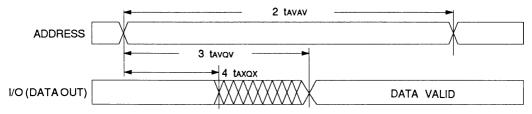

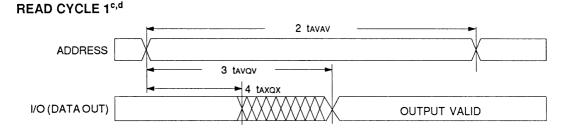

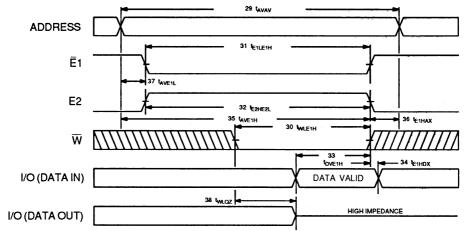

#### READ CYCLE 1<sup>c, d</sup>

#### **DEVICE OPERATION**

The IMS1223 has two control inputs: Chip Enable ( $\overline{E}$ ) and Write Enable ( $\overline{W}$ ), ten address inputs ( $A_0$ - $A_9$ ), and four data I/O lines. The  $\overline{E}$  input controls device selection as well as active and standby modes. With  $\overline{E}$  low, the device is selected and the ten address inputs are decoded to select one 4 bit word out of 1024. Read and Write operations on the memory cell are controlled by  $\overline{W}$  input. With  $\overline{E}$  high, the device is deselected, the outputs are disabled, and the power consumption is reduced to less than one-third of the active mode power with TTL levels and even lower with CMOS levels.

#### **READ CYCLE**

A read cycle is defined as  $\overline{W} \ge V_{IH}$  min with  $\overline{E} \le V_{IL}$  max. Read access time is measured from either  $\overline{E}$  going low or from valid address.

The READ CYCLE 1 waveform shows a read access that is initiated by a change in the address inputs while  $\overline{E}$  is low. The output remains active throughout READ CYCLE 1 and is valid at the specified address access time. The address inputs may change at access time and as long as  $\overline{E}$  remains low, the cycle time is equal to the adcress access time.

RECOMMENDED AC OPERATING CONDITIONS (0°C  $\leq$  T\_A  $\leq$  70°C) (V\_{CC} = 5.0V  $\pm$  10%)

| NO. | SYM                 | BOL             | PARAMETER                            | 122 | 3-25 | 122 | 3-35 | 122 | 3-45 | UNITS | NOTES |

|-----|---------------------|-----------------|--------------------------------------|-----|------|-----|------|-----|------|-------|-------|

| NO. | Standard            | Alternate       | FARAMETER                            | MIN | MAX  | MIN | MAX  | MIN | MAX  | UNITS | NULES |

| 9   | t <sub>avav</sub>   | t <sub>wc</sub> | Write Cycle Time                     | 25  |      | 35  |      | 45  |      | ns    |       |

| 10  | t <sub>wLWH</sub>   | t <sub>wP</sub> | Write Pulse Width                    | 20  |      | 25  |      | 35  |      | ns    |       |

| 11  | t <sub>elwh</sub>   | t <sub>cw</sub> | Chip Enable to End of Write          | 20  |      | 25  |      | 30  |      | ns    |       |

| 12  | t <sub>DVWH</sub>   | t <sub>DW</sub> | Data Set-up to End of Write          | 10  |      | 15  |      | 15  |      | ns    |       |

| 13  | t <sub>wHDX</sub>   | t <sub>DH</sub> | Data Hold After End of Write         | 0   |      | 0   |      | 0   |      | ns    |       |

| 14  | t <sub>avwh</sub>   | t <sub>AW</sub> | Address Set-up to End of Write       | 20  |      | 25  |      | 35  |      | ns    |       |

| 15  | t <sub>AVWL</sub>   | t <sub>AS</sub> | Address Set-up to Beginning of Write | 0   |      | 0   |      | 0   |      | ns    |       |

| 16  | t <sub>whax</sub>   | t <sub>wR</sub> | Address Hold After End of Write      | 0   |      | 0   |      | 0   |      | ns    |       |

| 17  | t <sub>wLQZ</sub> . | t <sub>wz</sub> | Write Enable to Output Disable       |     | 15   |     | 20   |     | 20   | ns    | f, j  |

| 18  | t <sub>whax</sub>   | t <sub>ow</sub> | Output Active After End of Write     | 5   |      | 5   |      | 5   |      | ns    | i     |

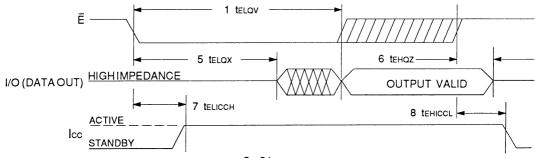

WRITE CYCLE 1: W CONTROLLED<sup>g, h</sup>

Note f: Measured ±200mV from steady state output voltage. Load capacitance is 5pF.

Note g:  $\overline{E}$  and  $\overline{W}$  must transition between V<sub>IH</sub> to V<sub>IL</sub> or V<sub>IL</sub> to V<sub>IH</sub> in a monotonic fashion.

Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\geq V_{||H}$  during address transitions.

Note i: If  $\overline{W}$  is low when  $\overline{E}$  goes low, the outputs remain in the high impedance state.

Note j: Parameter guaranteed but not tested.

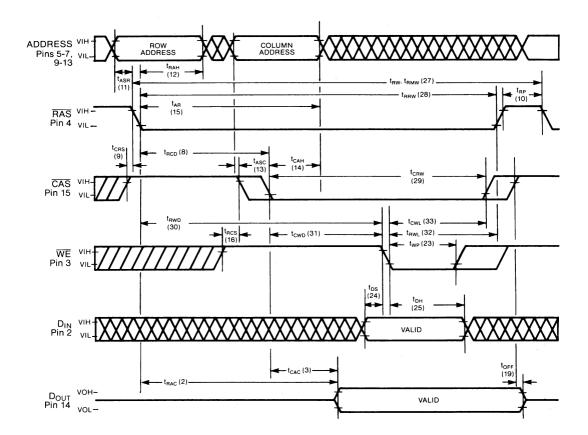

#### WRITE CYCLE 1

The READ CYCLE 2 waveform shows a read access that is initiated by  $\overline{E}$  going low. As long as address is stable when  $\overline{E}$  goes low, valid data is at the output at the specified Chip Enable Access time. If address is not valid when  $\overline{E}$  goes low, the timing is as specified in READ CYCLE 1. Chip Enable access time is not affected by the duration of the deselect interval.

#### WRITE CYCLE

The write cycle of the IMS1223 is initiated by the latter of  $\overline{E}$  or  $\overline{W}$  to transition from a high to a low. In the case of  $\overline{W}$  falling last, the output buffer will be turned on t<sub>ELQX</sub> after the falling edge of  $\overline{E}$  (just as in a read cycle).

The output buffer is then turned off within  $t_{WLQZ}$  of the falling edge of  $\overline{W}$ . During this interval, it is possible to have bus contention between devices with common I/O configurations. Contention can be avoided in a carefully designed system. During a write cycle, data on the input is written into the selected cells and the output is floating.

WRITE CYCLE 1 waveform shows a write cycle terminated by  $\overline{W}$  going high. Data set-up and hold times are referenced to the rising edge of  $\overline{W}$ . When  $\overline{W}$  goes high at the end of the cycle with  $\overline{E}$  active, the output of the memory becomes active. The data from the memory will be the same as the input data unless the input data or address changes.

### RECOMMENDED AC OPERATING CONDITIONS ( $-0^{\circ}C \le T_{A} \le 70^{\circ}C$ ) ( $V_{cc} = 5.0V \pm 10\%$ ) WRITE CYCLE 2: $\overline{e}$ controlled<sup>g, h</sup>

| NO. | SYM               |                 | PARAMETER                            | 1223-25<br>MIN MAX |     | 1223-35 |     | 1223-45 |     | UNITS | NOTES |

|-----|-------------------|-----------------|--------------------------------------|--------------------|-----|---------|-----|---------|-----|-------|-------|

|     | Standard          | Alternate       |                                      | MIN                | MAX | MIN     | MAX | MIN     | MAX |       |       |

| 19  | t <sub>avav</sub> | t <sub>wc</sub> | Write Cycle Time                     | 25                 |     | 35      |     | 45      |     | ns    |       |

| 20  | t <sub>wLEH</sub> | t <sub>wP</sub> | Write Pulse Width                    | 15                 |     | 25      |     | 35      |     | ns    |       |

| 21  | t <sub>eleh</sub> | t <sub>cw</sub> | Chip Enable to End of Write          | 20                 |     | 25      |     | 30      |     | ns    |       |

| 22  | t <sub>oven</sub> | t <sub>DW</sub> | Data Set-up to End of Write          | 10                 |     | 15      |     | 15      |     | ns    |       |

| 23  | t <sub>ehdx</sub> | t <sub>DH</sub> | Data Hold After End of Write         | 0                  |     | 0       |     | 0       |     | ns    |       |

| 24  | t <sub>AVEH</sub> | t <sub>AW</sub> | Address Set-up to End of Write       | 20                 |     | 25      |     | 35      |     | ns    |       |

| 25  | t <sub>ehax</sub> | t <sub>wR</sub> | Address Hold After End of Write      | 0                  |     | 0       |     | 0       |     | ns    |       |

| 26  | t <sub>AVEL</sub> | t <sub>AS</sub> | Address Set-up to Beginning of Write | 0                  |     | 0       |     | 0       |     | ns    |       |

| 27  | t <sub>wLQZ</sub> | t <sub>wz</sub> | Write Enable to Output Disable       |                    | 15  |         | 20  |         | 20  | ns    | f, j  |

Note f: Measured ±200mV from steady state output voltage. Load capacitance is 5pF.

Note g: E and W must transition between VIH to VII or VII to VIH in a monotonic fashion.

Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\geq V_{IH}$  during address transitions.

Note i: If W is low when E goes low, the outputs remain in the high impedance state.

Note j: Parameter guaranteed but not tested.

WRITE CYCLE 2 waveform shows a write cycle terminated by  $\overline{E}$  going high. Data set-up and hold times are referenced to the rising edge of  $\overline{E}.$  With  $\overline{E}$  high, the outputs remain in the high impedance state.

#### APPLICATION

It is imperative when designing with any very high speed memory, such as the IMS1223, that the fundamental rules in regard to memory board layout be followed to ensure proper system operation.

#### POWER DISTRIBUTION

The recommended power distribution scheme combines proper power trace layout and placement of decoupling capacitors to maintain the operating margins of the IMS1223. The impedance in the decoupling path from the power pin (18) through the decoupling capacitor to the ground pin (9) should be kept to a minimum. The impedance of this path is determined by the series impedance of the power line inductance and the inductance and reactance of the decoupling capacitor.

Since the current transients associated with the operation of the high speed IMS1223 have very high frequency components, the line inductance is the dominating factor. To reduce the line inductance, the power trace and ground trace should be gridded or provided by separate power planes. The decoupling capacitor supplies energy for high frequency current transients and should be located as close to the devices with as short lead length as possible. The high frequency decoupling capacitor should have a value of 0.1 microfarad, and be placed between each row of devices in the array (see drawing). A larger tantalum capacitor, with a sufficient value to eliminate low frequency ripple, should be placed near the memory board edge connection where the power traces meet the backplane power distribution system. These larger capacitors provide bulk energy storage to prevent voltage drop due to the main supply being located off the memory board and at the end of a long inductive path.

The ground grid of the memory array should extend to the TTL driver periphery circuit. This will provide a solid ground reference for the TTL drivers and prevent loss of operating margin of the drivers due to differential ground noise.

#### TERMINATION

Trace lines on a memory board in the array look to TTL driver signals like low impedance, unterminated transmission lines. In order to reduce or eliminate the reflections of the TTL signals propagating down the lines, especially low going TTL signals, line termination is recommended. The termination may be either series or parallel.

The recommended technique is to use series termination. The series termination technique has the advantage of drawing no DC current and using a minimum number of components. This is accomplished by placing a series resistor in the signal line at the output of the TTL driver to dampen the reflection on the line. The resistor should be placed as close to the driver package as is practical. The line should be kept short by placing the drivertermination combination close to the memory array. Some experimentation will have to be done to find the proper value to use for the series termination to minimize reflections, but generally a series resistor in the 10 to 33 ohm range will be required. Because each design will result in a different signal impedance, a resistor of predetermined value may not properly match the signal path impedance. The proper value of resistance should therefore be selected empirically.

#### **ORDERING INFORMATION**

| DEVICE    | SPEED | PACKAGE     | PART NUMBER |

|-----------|-------|-------------|-------------|

|           | 25ns  | PLASTIC DIP | IMS1223P-25 |

|           | 25ns  | CERAMIC DIP | IMS1223S-25 |

| IMS1223   | 35ns  | PLASTIC DIP | IMS1223P-35 |

| 111/31223 | 35ns  | CERAMIC DIP | IMS1223S-35 |

|           | 45ns  | PLASTIC DIP | IMS1223P-45 |

|           | 45ns  | CERAMIC DIP | IMS1223S-45 |

2-18

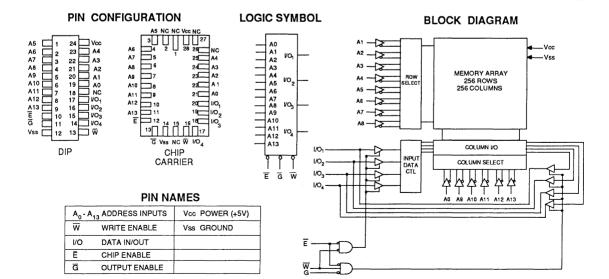

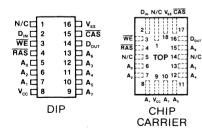

### CMOS High Performance 16K x 1 Static RAM

#### FEATURES

#### DESCRIPTION

- INMOS' Very High Speed CMOS

- Advanced Process 1.6 Micron Design Rules

- 16K x 1 Bit Organization

- 25, 35, 45 and 55 nsec Access Times

- Fully TTL Compatible

- Separate Data Input & Output

- Three-state Output

19

18

DIP

- Power Down Function

- Single +5V ± 10% Operation

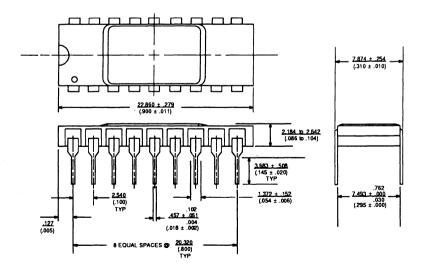

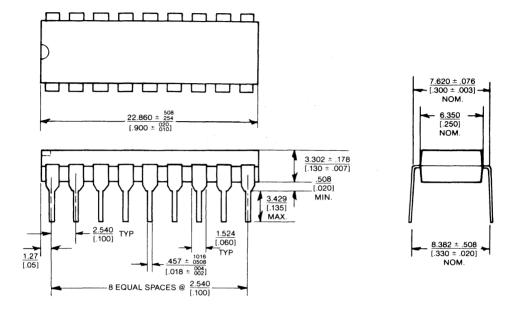

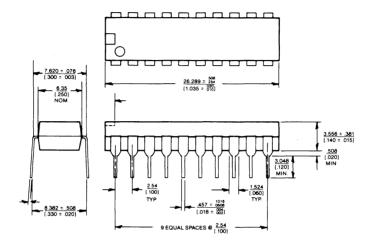

- 20-Pin, 300-mil DIP (JEDEC Std.)

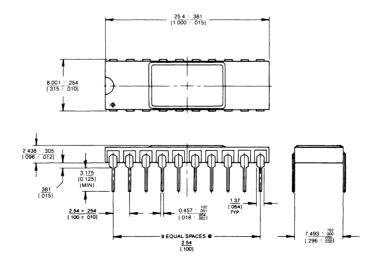

- 20-Pin Ceramic LCC (JEDEC Std.)

The INMOS IMS1403 is a high performance 16K x 1 CMOS Static RAM. The IMS1403 provides maximum density and speed enhancements with the additional CMOS benefits of lower power and superior reliability.

The IMS1403 features fully static operation requiring no external clocks or timing strobes, and equal address access and cycle times. Additionally, the IMS1403 provides a Chip Enable (/E) function that can be used to place the device into a low-power standby mode.

The IMS1403M and IMS1403LM are MIL-STD-883 versions intended for military applications.

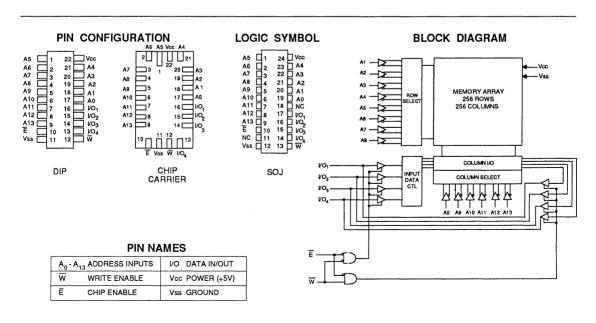

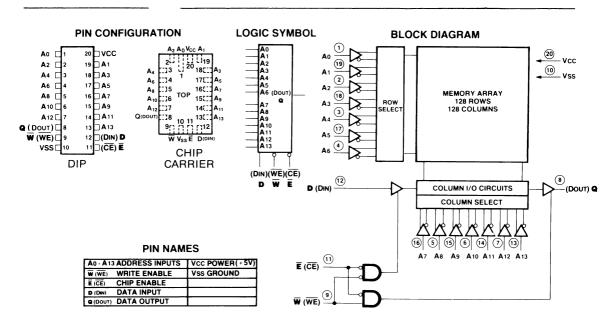

**PIN CONFIGURATION**

А<sub>6</sub> А<sub>8</sub>

A ...

A<sub>12</sub>

Q

13 A 13

A, V.

Ēſ

CHIP

CARRIER

A<sub>11</sub>

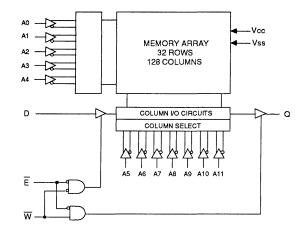

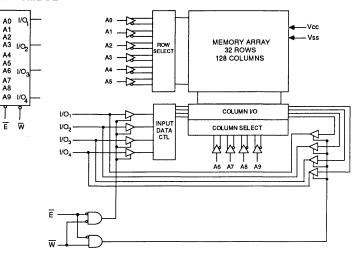

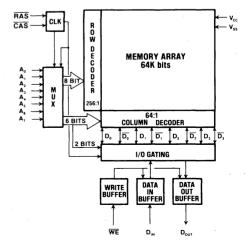

#### **BLOCK DIAGRAM**

|   | ADDRESS INPUTS | ٥   | DATA OUTPUT |

|---|----------------|-----|-------------|

| w | WRITE ENABLE   | Vcc | POWER       |

| Ē | CHIP ENABLE    | VSS | GROUND      |

| D | DATA INPUT     |     |             |

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin relative to V | /ss2.0 to 7.0V   |

|----------------------------------|------------------|

| Voltage on Q                     | 1.0 to (Vcc+0.5) |

| Temperature Under Bias           | 55° C to 125°C   |

| Storage Temperature              | 65° C to 150°C   |

| Power Dissipation                | 1W               |

| DC Output Current                |                  |

| (One Second Duration)            |                  |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### DC OPERATING CONDITIONS

| SYMBOL | PARAMETER                     | MIN   | ТҮР | MAX    | UNITS | NOTES                      |

|--------|-------------------------------|-------|-----|--------|-------|----------------------------|

| Vcc    | Supply Voltage                | 4.5   | 5.0 | 5.5    | v     |                            |

| Vss    | Supply Voltage                | 0     | 0   | 0      | V     |                            |

| Vін    | Input Logic "1" Voltage       | 2.0   |     | Vcc+.5 | V     | All inputs                 |

| Vil    | Input Logic "0" Voltage       | -1.0* |     | 0.8    | V     | All inputs                 |

| Ta     | Ambient Operating Temperature | 0     | 25  | 70     | °C    | 400 linear ft/min air flow |

\*VIL min = -3 volts for pulse width <20ns, note b.

#### **DC ELECTRICAL CHARACTERISTICS** $(0^{\circ}C \le T_A \le 70^{\circ}C)$ $(Vcc = 5.0V \pm 10\%)^a$

| SYMBOL | PARAMETER                                                        | MIN | МАХ | UNITS | NOTES                                                                                 |

|--------|------------------------------------------------------------------|-----|-----|-------|---------------------------------------------------------------------------------------|

| lcc1   | Average Vcc Power<br>Supply Current                              |     | 75  | mA    | tavav = tavav (min)                                                                   |

| lcc2   | Vcc Power Supply Current<br>(Standby,Stable TTL Input Levels)    |     | 15  | mA    | Ē ≿ Vi⊢ . All other inputs at<br>Vi⊵ ≤ Vi∟ or ≿ Vi⊢                                   |

| lcc3   | Vcc Power Supply Current<br>(Standby, Stable CMOS Input Levels)  |     | 5   | mA    | Ē ≿ (Vcc - 0.2). All other inputs at<br>Vi⊵ ≤ 0.2 or ≥ (Vcc - 0.2V)                   |

| lcc4   | Vcc Power Supply Current<br>(Standby, Cycling CMOS Input Levels) |     | 10  | mA    | $\overline{E} \ge$ (Vcc - 0.2). Inputs cycling at VIN $\le$ 0.2 or $\ge$ (Vcc - 0.2V) |

| lilk   | Input Leakage Current (Any Input)                                |     | ±1  | μA    | Vcc = max<br>ViN = Vss to Vcc                                                         |

| Іогк   | Off State Output Leakage Current                                 |     | ±5  | μA    | Vcc = max<br>ViN = Vss to Vcc                                                         |

| Vон    | Output Logic "1" Voltage                                         | 2.4 |     | v     | lo∟ = -4mA                                                                            |

| Vol    | Output Logic "0" Voltage                                         |     | 0.4 | v     | Іон = 16mA                                                                            |

Note a: Icc is dependent on output loading and cycle rate, the specified values are obtained with the output unloaded.

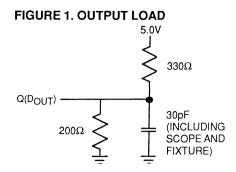

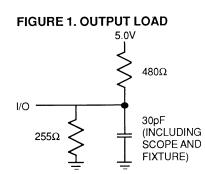

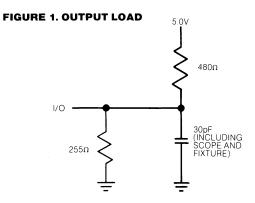

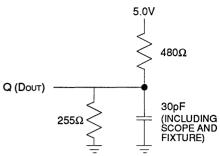

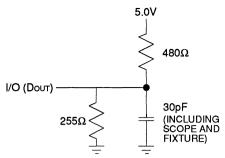

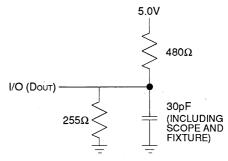

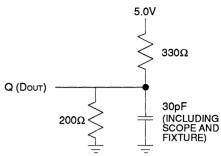

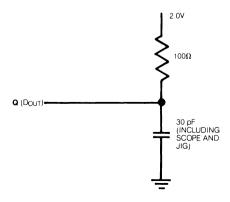

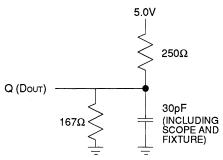

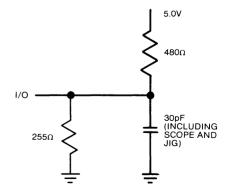

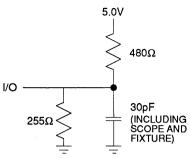

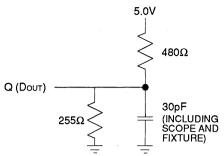

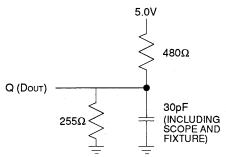

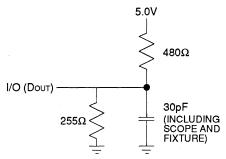

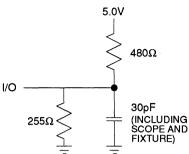

#### AC TEST CONDITIONS

| Input Pulse Levels              | Vss to 3V    |

|---------------------------------|--------------|

| Input Rise and Fall Times       | 5ns          |

| Input and Output Timing Referen |              |

| Output Load                     | See Figure 1 |

#### **CAPACITANCE**<sup>b</sup> (Ta=25°C, f=1.0MHZ)

| SYMBOL | PARAMETER          | МАХ | UNITS | CONDITIONS             |

|--------|--------------------|-----|-------|------------------------|

| Cin    | Input Capacitance  | 4   | рF    | $\Delta V = 0$ to $3V$ |

| Соит   | Output Capacitance | 4   | pF    | $\Delta V = 0$ to $3V$ |

Note b: This parameter is sampled and not 100% tested.

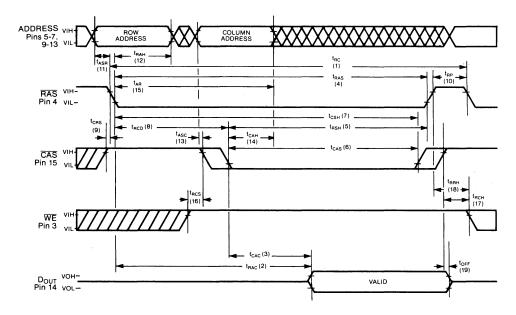

#### **RECOMMENDED AC OPERATING CONDITIONS** ( $0^{\circ}C \le T_A \le 70^{\circ}C$ ) ( $V_{cc} = 5.0V \pm 10\%$ ) **READ CYCLE**<sup>g</sup>

| NO. | SYM                 | BOL              | PARAMETER                        |     | 3-25 |     | 3-35 |     | 3-45 |     | 3-55 | UNITS | NOTES |

|-----|---------------------|------------------|----------------------------------|-----|------|-----|------|-----|------|-----|------|-------|-------|

| NO. | Standard            | Alternate        | FANAMETEN                        | MIN | MAX  | MIN | MAX  | MIN | MAX  | MIN | MAX  | 01113 | NOTES |

| 1   | t <sub>ELQV</sub>   | t <sub>ACS</sub> | Chip Enable Access Time          |     | 25   |     | 35   |     | 45   |     | 55   | ns    |       |

| 2   | t <sub>avav</sub>   | t <sub>RC</sub>  | Read Cycle Time                  | 25  |      | 35  |      | 40  |      | 50  |      | ns    | С     |

| 3   | t <sub>AVQV</sub>   | t <sub>AA</sub>  | Address Access Time              |     | 25   |     | 35   |     | 40   |     | 50   | ns    | d     |

| 4   | t <sub>axqx</sub>   | t <sub>on</sub>  | Output Hold After Address Change | 5   |      | 5   |      | 5   |      | 5   |      | ns    |       |

| 5   | t <sub>ELQX</sub>   | t <sub>LZ</sub>  | Chip Enable to Output Active     | 5   |      | 5   |      | 5   |      | 5   |      | ns    | j,    |

| 6   | t <sub>ehqz</sub>   | t <sub>HZ</sub>  | Chip Disable to Output Inactive  | 0   | 20   | 0   | 20   | 0   | 20   | 0   | 25   | ns    | f, j  |

| 7   | t <sub>ELICCH</sub> | t <sub>PU</sub>  | Chip Enable to Power Up          | 0   |      | 0   |      | 0   |      | 0   |      | ns    | j     |

| 8   | t <sub>EHICCL</sub> | t <sub>PD</sub>  | Chip Enable To Power Down        |     | 30   |     | 30   |     | 30   |     | 30   | ns    | j     |

|     |                     | t <sub>T</sub>   | Input Rise and Fall Times        |     | 50   |     | 50   |     | 50   |     | 50   | ns    | e, j  |

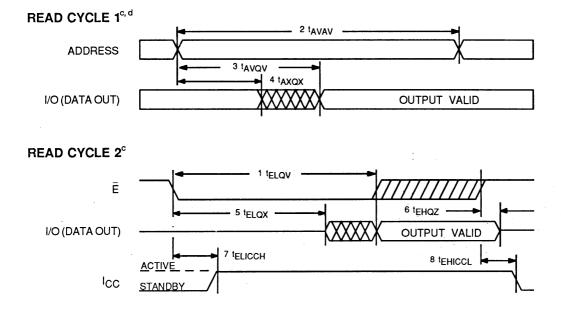

Note c: For READ CYCLE 1 & 2,  $\overline{W}$  is high for entire cycle.

Note d: Device is continuously selected, E low.

Note e: Measured between VIL max and VIH min.

Note f: Measured  $\pm$  200mV from steady state output voltage. Load capacitance is 5pF.

Note g:  $\overline{E}$  and  $\overline{W}$  must transition between V<sub>IH</sub> to V<sub>IL</sub> or V<sub>IL</sub> to V<sub>IH</sub> in a monotonic fashion. Note j: Parameter guaranteed but not tested.

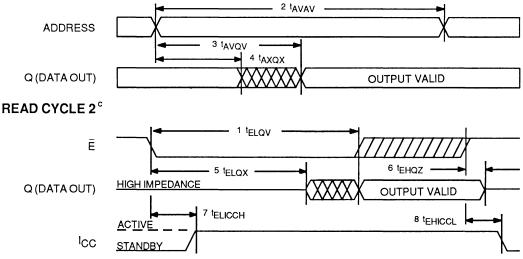

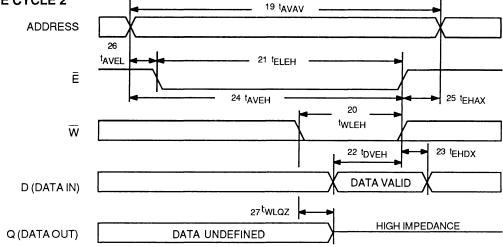

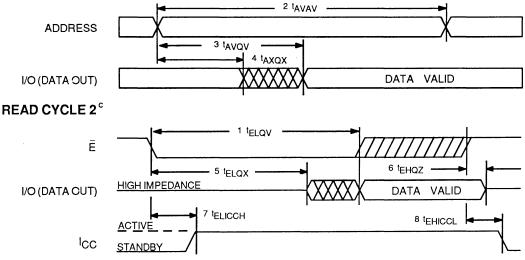

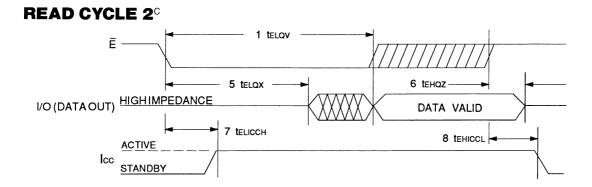

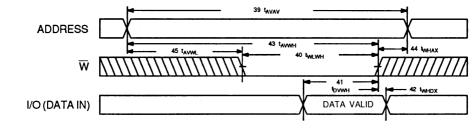

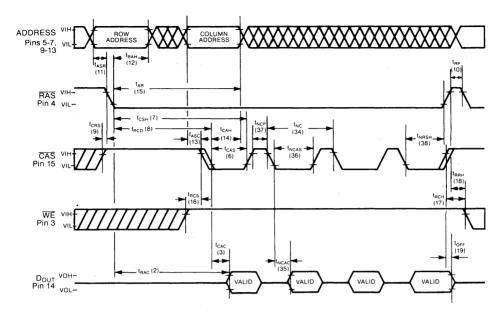

**READ CYCLE 2<sup>c</sup>**

#### **RECOMMENDED AC OPERATING CONDITIONS** ( $0^{\circ}C \le T_{A} \le 70^{\circ}C$ ) ( $V_{cc} = 5.0V \pm 10\%$ )

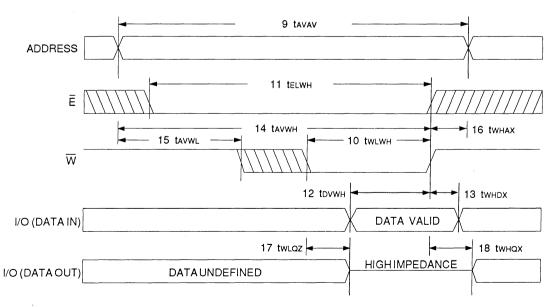

#### WRITE CYCLE 1: W CONTROLLED<sup>g, h</sup>

| NO. | SYM               |                  | PARAMETER                            |     | 3-25 |     | 3-35 |     | 3-45 |     | 3-55 | UNITS  | NOTES |

|-----|-------------------|------------------|--------------------------------------|-----|------|-----|------|-----|------|-----|------|--------|-------|

| NO. | Standard          | Alternate        |                                      | MIN | MAX  | MIN | MAX  | MIN | MAX  | MIN | MAX  | 011113 | NOTES |

| 9   | t <sub>avav</sub> | t <sub>wc</sub>  | Write Cycle Time                     | 20  |      | 30  |      | 40  |      | 50  |      | ns     |       |

| 10  | t <sub>wLWH</sub> | t <sub>wP</sub>  | Write Pulse Width                    | 15  |      | 20  |      | 20  |      | 25  |      | ns     |       |

| 11  | t <sub>ELWH</sub> | t <sub>cw</sub>  | Chip Enable to End of Write          | 20  |      | 30  |      | 35  |      | 45  |      | ns     |       |

| 12  | t <sub>DVWH</sub> | t <sub>DW</sub>  | Data Set-up to End of Write          | 15  |      | 15  |      | 15  |      | 20  |      | ns     |       |

| 13  | t <sub>wHDX</sub> | t <sub>DH</sub>  | Data Hold After End of Write         | 0   |      | 0   |      | 0   |      | 0   |      | ns     |       |

| 14  | t <sub>avwh</sub> | t <sub>AW</sub>  | Address Set-up to End of Write       | 20  |      | 30  |      | 35  |      | 45  |      | ns     |       |

| 15  | t <sub>avwl</sub> | t <sub>AS</sub>  | Address Set-up to Beginning of Write | 0   |      | 0   |      | 0   |      | 0   |      | ns     |       |

| 16  | t <sub>whax</sub> | t <sub>wR</sub>  | Address Hold After End of Write      | 0   |      | 0   |      | 0   |      | 0   |      | ns     |       |

| 17  | t <sub>wLQZ</sub> | ʻt <sub>wz</sub> | Write Enable to Output Disable       | 0   | 20   | 0   | 20   | 0   | 20   | 0   | 20   | ns     | f, j  |

| 18  | t <sub>wHQX</sub> | t <sub>ow</sub>  | Output Active After End of Write     | 0   |      | 0   |      | 0   |      | 0   |      | ns     | i     |

Note f: Measured ± 200mV from steady state output voltage. Load capacitance is 5pF.

Note g:  $\overline{E}$  and  $\overline{W}$  must transition between V<sub>IH</sub> to V<sub>IL</sub> or V<sub>IL</sub> to V<sub>IH</sub> in a monotonic fashion. Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\geq$  V<sub>IH</sub> during address transitions. Note i: If  $\overline{W}$  is low when  $\overline{E}$  goes low, the output remains in the high impedance state.

Note j: Parameter guaranteed but not tested.

#### RECOMMENDED AC OPERATING CONDITIONS (0°C $\leq$ T\_A $\leq$ 70°C) (V\_{cc} = 5.0V $\pm$ 10%)

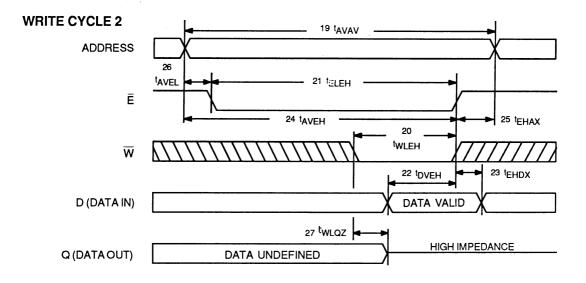

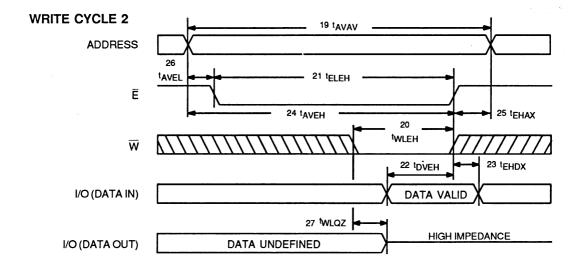

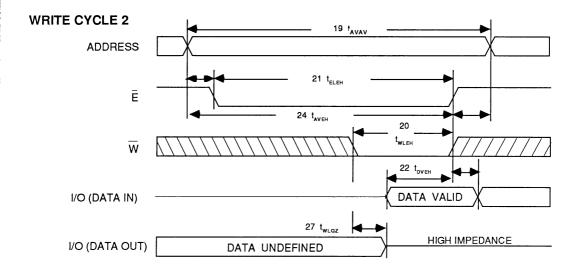

#### WRITE CYCLE 2: E CONTROLLED<sup>g, h</sup>

| NO. | SYM               |                 | PARAMETER                            |     | 3-25 |     | 3-35 |     | 3-45 |     | 3-55 | UNITS | NOTES |

|-----|-------------------|-----------------|--------------------------------------|-----|------|-----|------|-----|------|-----|------|-------|-------|

| NO. | Standard          | Alternate       |                                      | MIN | MAX  | MIN | MAX  | MIN | MAX  | MIN | MAX  |       | NOTES |

| 19  | t <sub>AVAV</sub> | t <sub>wc</sub> | Write Cycle Time                     | 20  |      | 30  |      | 40  |      | 50  |      | ns    |       |

| 20  | t <sub>wLEH</sub> | t <sub>wP</sub> | Write Pulse Width                    | 15  |      | 20  |      | 20  |      | 25  |      | ns    |       |

| 21  | t <sub>ELEH</sub> | t <sub>cw</sub> | Chip Enable to End of Write          | 20  |      | 30  |      | 35  |      | 45  |      | ns    |       |

| 22  | t <sub>DVEH</sub> | t <sub>DW</sub> | Data Set-up to End of Write          | 15  |      | 15  |      | 15  |      | 20  |      | ns    |       |

| 23  | t <sub>EHDX</sub> | t <sub>DH</sub> | Data Hold After End of Write         | 0   |      | 0   |      | 0   |      | 0   |      | ns    |       |

| 24  | t <sub>AVEH</sub> | t <sub>AW</sub> | Address Set-up to End of Write       | 20  |      | 30  |      | 35  |      | 45  |      | ns    |       |

| 25  | t <sub>EHAX</sub> | t <sub>wR</sub> | Address Hold After End of Write      | 0   |      | 0   |      | 0   |      | 0   |      | ns    |       |

| 26  | t <sub>AVEL</sub> | t <sub>AS</sub> | Address Set-up to Beginning of Write | 0   |      | 0   |      | 0   |      | 0   |      | ns    |       |

| 27  | t <sub>wLQZ</sub> | t <sub>wz</sub> | Write Enable to Output Disable       | 0   | 20   | 0   | 20   | 0   | 20   | 0   | 25   | ns    | f, j  |

Note f: Measured ± 200mV from steady state output voltage. Load capacitance is 5pF.

Note g:  $\overline{E}$  and  $\overline{W}$  must transition between V<sub>IH</sub> to V<sub>IL</sub> or V<sub>IL</sub> to V<sub>IH</sub> in a monotonic fashion. Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\geq$  V<sub>IH</sub> during address transitions. Note i: If  $\overline{W}$  is low when  $\overline{E}$  goes low, the output remains in the high impedance state.

Note i: Parameter guaranteed but not tested.

#### **DEVICE OPERATION**

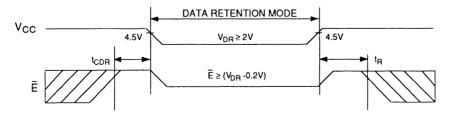

The IMS1403 has two control inputs, Chip Enable  $(\overline{E})$  and Write Enable  $(\overline{W})$ , fourteen address inputs  $(A_0 - A_{13})$ , a Data in (D) and a Data out (Q). The  $\overline{E}$  input controls device selection as well as active and standby modes. With  $\overline{E}$  low, the device is selected and the fourteen address inputs are decoded to select one bit out of 16K bits. Read and Write operations on the memory cell are controlled by  $\overline{W}$  input. With  $\overline{E}$  high, the device is deselected, the output is disabled, and power consumption is reduced to less than one-fourth of the active mode power with TTL levels and even lower with CMOS levels.

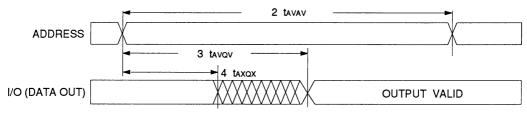

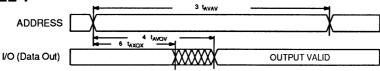

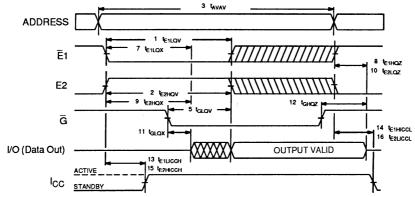

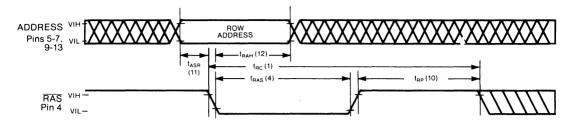

#### **READ CYCLE**

A read cycle is defined as  $\overline{W} \ge V_{IH}$  min with  $\overline{E} \le V_{IL}$  max. Read access time is measured from either  $\overline{E}$  going low or from valid address.

The READ CYCLE 1 waveform shows a read access that is initiated by a change in the address inputs while E is low. The output remains active throughout READ CYCLE 1 and is valid at the specified address access time. The address inputs may change at access time as long as E remains low, the cycle time is equal to the address access time.

The READ CYCLE 2 waveform shows a read access that is initiated by  $\overline{E}$  going low. As long as address is stable when  $\overline{E}$  goes low, valid data is at the output at the specified Chip Enable Access time. If address is not

valid when  $\overline{E}$  goes low, the timing is as specified in READ CYCLE 1. Chip Enable access time is not affected by the duration of the deselect interval.

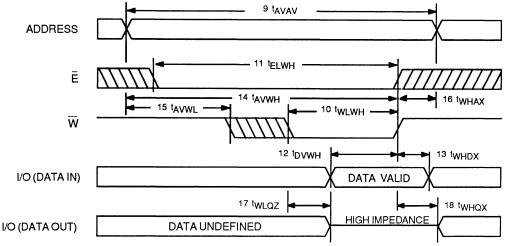

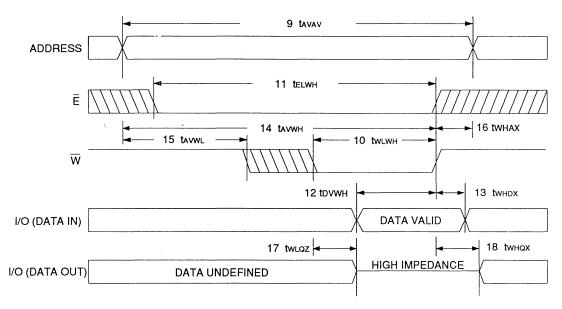

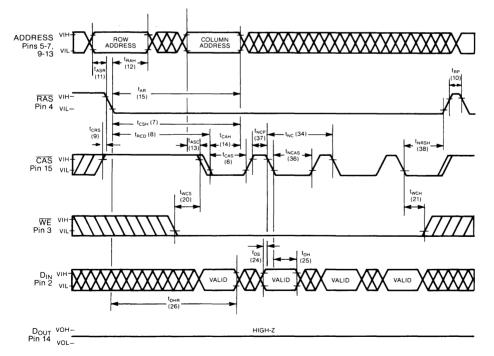

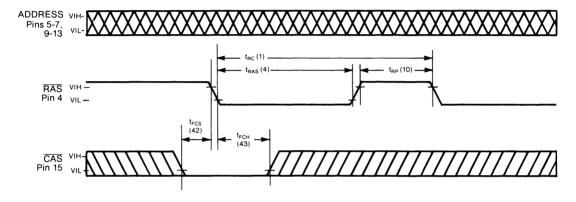

#### WRITE CYCLE

A write cycle of the IMS1403 is initiated by the latter of  $\overline{E}$  or  $\overline{W}$  to transition from a high to a low. In the case of  $\overline{W}$  falling last, the output buffer will be turned on  $t_{ELOX}$  after the falling edge of  $\overline{E}$  (just as in a read cycle). The output buffer is then turned off within  $t_{WLOZ}$  of the falling edge of  $\overline{W}$ . During this interval, it is possible to have bus contention between devices with D and Q connected together in a common I/O configuration. Contention can be avoided in a carefully designed system. During a write cycle, data on the input is written into the selected cells and the output is floating.

WRITE CYCLE 1 waveform shows a write cycle terminated by  $\overline{W}$  going high. Data set-up and hold times are referenced to the rising edge of  $\overline{W}$ . When  $\overline{W}$  goes high at the end of the cycle with  $\overline{E}$  active, the output of the memory becomes active. The data from the memory will be the same as the input data unless the input data or address changes.

WRITE CYCLE 2 waveform shows a write cycle terminated by E going high. Data set-up and hold times are referenced to the rising edge of E. With E high, the outputs remain in the high impedance state.

#### APPLICATION

It is imperative when designing with any very high speed memory, such as the IMS1403, that the fundamental rules in regard to memory board layout be followed to ensure proper system operation.

#### POWER DISTRIBUTION

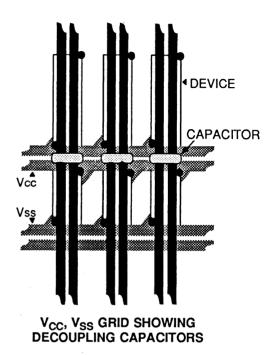

The recommended power distribution scheme combines proper power trace layout and placement of decoupling capacitors to maintain the operating margins of the IMS1403. The impedance in the decoupling path from the power pin through the decoupling capacitor, to the ground pin should be kept to a minimum. The impedance of this path is determined by the series impedance of the power line inductance and the inductance and reactance of the decoupling capacitor.

Since the current transients associated with the operation of the high speed IMS1403 have very high frequency components, the line inductance is the dominating factor.

DECOUPLING CAPACITORS

To reduce the line inductance, the power trace and ground trace should be gridded or provided by separate power planes. The decoupling capacitor supplies energy for high frequency current transients and should be located as close to the devices with as short lead length as possible. The high frequency decoupling capacitor should have a value of  $0.1\mu$ F, and be placed between each row of devices in the array (see drawing). A larger tantalum capacitor, with a sufficient value to eliminate low frequency ripple, should be placed near the memory board edge connection where the power traces meet the backplane power distribution system. These larger capacitors provide bulk energy storage to prevent voltage drop due to the main supply being located off the memory board and at the end of a long inductive path.

The ground grid of the memory array should extend to the TTL periphery circuit. This will provide a solid ground reference for the TTL drivers and prevent loss of operating margin of the drivers due to differential ground noise.

#### TERMINATION

Trace lines on a memory board in the array look to TTL driver signals like low impedance, unterminated transmission lines. In order to reduce or eliminate the reflections of the TTL signals propagating down the lines, especially low going TTL signals, line termination is recommended. The termination may be either series or parallel.

The recommended technique is to use series termination. The series termination technique has the advantage of drawing no DC current and using a minimum number of components. This is accomplished by placing a series resistor in the signal line at the output of the TTL driver to dampen the reflection on the line. The resistor should be placed as close to the driver package as is practical. The line should be kept short by placing the drivertermination combination close to the memory array.

Some experimentation will have to be done to find the proper value to use for the series termination to minimize reflections, but generally a series resistor in the 10 to 33 ohm range will be required. Because each design will result in a different signal impedance, a resistor of predetermined value may not properly match the signal path impedance. The proper value of resistance should therefore be selected empirically.

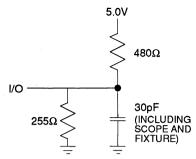

#### FIGURE 1. OUTPUT LOAD 5.0V 250Ω Q (Dout) 167Ω T T T SCOPE AND FIXTURE)

#### **ORDERING INFORMATION**

| DEVICE  | SPEED | PACKAGE     | PARTNUMBER  |

|---------|-------|-------------|-------------|